Performance Simulation with the Coconut Multicore Framework for the Cell/B.E.

.

Performance Simulation with the Coconut Multicore Framework for the Cell/B.E.

By

Kevin Browne B.Sc. (Hons) IBM Center for Advanced Studies Fellow

### A Thesis

Submitted to the School of Graduate Studies in Partial Fulfillment of the Requirements for the Degree Master of Science

McMaster University © Copyright by Kevin Browne, September 21, 2009

#### MASTER OF SCIENCE(2009) COMPUTING AND SOFTWARE

McMaster University Hamilton, Ontario

TITLE: Performance Simulation with the Coconut Multicore Framework for the Cell/B.E.

AUTHOR: Kevin Browne B.Sc. (Hons)(McMaster University)

SUPERVISOR: Dr. Christopher Anand

NUMBER OF PAGES: xvii, 136

LEGAL DISCLAIMER: This is an academic research report. I, my supervisor, defence committee, and university, make no claim as to the fitness for any purpose, and accept no direct or indirect liability for the use of algorithms, findings, or recommendations in this thesis.

#### Abstract

The multicore revolution in chip design has fundamentally altered the demands placed on developers. Thread-level parallelism is critical to optimizing software performance on multicore chips. However thread-level parallelism presents challenges with respect to optimization, safety and program representation. Program models and compiler technologies must act as a bridge from applications to efficient hardware usage.

Coconut (COde CONstructing User Tool) is an ongoing project at Mc-Master to develop a platform for experimenting with novel ideas in reliable and high performance code generation, currently targeting the Cell/B.E.. The Coconut Multicore Framework uses a virtual machine abstraction layer to model multicore layer parallelism on the Cell/B.E.. The abstraction creates a correspondence between ILP and multicore layers of parallelism. The abstraction also allows us to perform efficient static analysis of virtual machine programs; with this ability we have developed a tool to automatically check for parallel bugs in linear time with respect to the atomic virtual machine instructions.

In this thesis we will discuss the creation of a performance simulation tool developed to simulate the execution of our virtual machine instructions on a Cell/B.E.. The tool has scalability to future many-core architectures, due to its linearly bounded runtime complexity. The tool allows for Coconut developers to contrast the performance of different scheduling algorithms. It provides meaningful feedback as to optimization opportunities by identifying data transfer latencies which cause execution to stall. The design and performance testing results of the performance simulation tool are presented.

#### Acknowledgments

I would like to thank my supervisors Dr. Christopher Anand and Dr. Wolfram Kahl for their wonderful support and guidance throughout my degree. Thanks to Dr. Anand in particular for encouraging me to discuss my research at many conferences and workshops. Thanks to Dr. Kahl in particular for introducing me to the wonderful Monad.

I would like to thank the IBM Toronto Lab Center for Advanced Studies, and Robert Enenkel, for their support of my research work thus far.

I would also like to thank my fellow students in the Coconut project. In particular Shiqi Cao for teaching me how to Haskell properly, and Gabriel Grant for coding the wonderful Runtime System.

I would also like to thank my parents, family and friends for their support and encouragement.

## Contents

| A        | bstra                 | $\operatorname{ct}$ |                                           | iii             |

|----------|-----------------------|---------------------|-------------------------------------------|-----------------|

| A        | cknow                 | vledgn              | nents                                     | v               |

| Li       | st of                 | Figure              | es                                        | xi              |

| Li       | st of                 | Tables              | 5                                         | xiii            |

| A        | crony                 | m Ind               | lex                                       | xv              |

| 1        | $\operatorname{Intr}$ | oducti              | ion                                       | 1               |

|          | 1.1                   | Docum               | nent Structure                            | 3               |

| <b>2</b> | Para                  | allel C             | omputing                                  | <b>5</b>        |

|          | 2.1                   | Motiva              | ations                                    | 5               |

|          |                       | 2.1.1               | Performance Increases                     | 6               |

|          |                       | 2.1.2               | Frequency, Memory and Power Walls         | 7               |

|          | 2.2                   | Flynn               | 's Taxonomy                               | 9               |

|          |                       | 2.2.1               | Single Instruction Single Data (SISD)     | 10              |

|          |                       | 2.2.2               | Single Instruction Multiple Data (SIMD)   |                 |

|          |                       | 2.2.3               | Multiple Instruction Single Data (MISD)   |                 |

|          |                       | 2.2.4               | Multiple Instruction Multiple Data (MIMD) | 11              |

|          | 2.3                   |                     | elism Levels                              | 13              |

|          |                       | 2.3.1               | Bit-level Parallelism                     |                 |

|          |                       | 2.3.2               | Instruction-level Parallelism             |                 |

|          |                       | 2.3.3               | Thread-level Parallelism                  |                 |

|          |                       | 2.3.4               | Process-level Parallelism                 |                 |

|          | 2.4                   | Task 1              | Parallelism vs. Data Parallelism          |                 |

|          |                       | 2.4.1               | Task Parallelism                          |                 |

|          |                       | 2.4.2               | Data Parallelism                          |                 |

|          | 2.5                   |                     | bry Classifications                       | $\frac{20}{20}$ |

2

|   | 2                                                         | -2.5.1                                                                                                                                        | Shared Memory                                | 21                                                                                                                                 |

|---|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                           | 2.5.2                                                                                                                                         | Distributed Memory                           | 21                                                                                                                                 |

|   |                                                           | 2.5.3                                                                                                                                         | Distributed Shared Memory                    | 22                                                                                                                                 |

|   |                                                           | 2.5.4                                                                                                                                         | Uniform Memory Access (UMA)                  | 22                                                                                                                                 |

|   |                                                           | 2.5.5                                                                                                                                         | Non-Uniform Memory Access (NUMA)             | 22                                                                                                                                 |

|   | 2.6                                                       | Proces                                                                                                                                        | ssing Element Communication                  | 22                                                                                                                                 |

|   |                                                           | 2.6.1                                                                                                                                         | Computation Bound vs. Communication Bound    | 23                                                                                                                                 |

|   |                                                           | 2.6.2                                                                                                                                         | Processing Element Coupling                  | 24                                                                                                                                 |

|   |                                                           | 2.6.3                                                                                                                                         | Parallelism Granularity                      | 24                                                                                                                                 |

|   |                                                           | 2.6.4                                                                                                                                         | Performance Measurement                      | 25                                                                                                                                 |

|   |                                                           | 2.6.5                                                                                                                                         | Network Topologies                           | 26                                                                                                                                 |

|   | 2.7                                                       | Perfor                                                                                                                                        | mance Measurement                            | 26                                                                                                                                 |

|   |                                                           | 2.7.1                                                                                                                                         | Floating Point Operations Per Second (FLOPS) | 26                                                                                                                                 |

|   |                                                           | 2.7.2                                                                                                                                         | Benchmarks                                   | 27                                                                                                                                 |

|   | 2.8                                                       | Multip                                                                                                                                        | processor Parallelism Software Challenges    | 27                                                                                                                                 |

|   |                                                           | 2.8.1                                                                                                                                         | Program Models                               | 28                                                                                                                                 |

|   |                                                           | 2.8.2                                                                                                                                         | Program Correctness                          | 29                                                                                                                                 |

|   |                                                           | 2.8.3                                                                                                                                         | Optimal Scheduling                           | 31                                                                                                                                 |

| 0 | a                                                         |                                                                                                                                               |                                              | 07                                                                                                                                 |

| 3 |                                                           |                                                                                                                                               | dband Engine                                 | 37                                                                                                                                 |

|   | 3.1                                                       |                                                                                                                                               | S                                            | 37                                                                                                                                 |

|   |                                                           | Hander                                                                                                                                        | na na Ornanziana                             | 20                                                                                                                                 |

|   | 3.2                                                       |                                                                                                                                               | vare Overview                                | 38<br>20                                                                                                                           |

|   | $3.2 \\ 3.3$                                              | Proces                                                                                                                                        | sor Element Design                           | 39                                                                                                                                 |

|   |                                                           | Proces<br>3.3.1                                                                                                                               | sor Element Design                           | 39<br>40                                                                                                                           |

|   | 3.3                                                       | Proces<br>3.3.1<br>3.3.2                                                                                                                      | sor Element Design                           | 39<br>40<br>41                                                                                                                     |

|   |                                                           | Proces<br>3.3.1<br>3.3.2<br>Comm                                                                                                              | ssor Element Design                          | 39<br>40<br>41<br>42                                                                                                               |

|   | 3.3                                                       | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1                                                                                                     | ssor Element Design                          | 39<br>40<br>41<br>42<br>42                                                                                                         |

|   | 3.3<br>3.4                                                | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2                                                                                            | ssor Element Design                          | <ol> <li>39</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>45</li> </ol>                                                 |

|   | 3.3                                                       | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm                                                                                    | ssor Element Design                          | <ol> <li>39</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>42</li> <li>45</li> <li>49</li> </ol>                         |

|   | 3.3<br>3.4                                                | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1                                                                           | ssor Element Design                          | <ol> <li>39</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>45</li> <li>49</li> <li>49</li> </ol>                         |

|   | 3.3<br>3.4                                                | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2                                                                  | ssor Element Design                          | <ol> <li>39</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>45</li> <li>49</li> <li>49</li> <li>52</li> </ol>             |

|   | <ul><li>3.3</li><li>3.4</li><li>3.5</li></ul>             | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2<br>3.5.3                                                         | ssor Element Design                          | <ol> <li>39</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>45</li> <li>49</li> <li>49</li> <li>52</li> <li>54</li> </ol> |

|   | 3.3<br>3.4                                                | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2<br>3.5.3<br>Overce                                               | sor Element Design                           | 39<br>40<br>41<br>42<br>42<br>45<br>49<br>49<br>52<br>54<br>57                                                                     |

|   | <ul><li>3.3</li><li>3.4</li><li>3.5</li></ul>             | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2<br>3.5.3<br>Overce<br>3.6.1                                      | ssor Element Design                          | 39<br>40<br>41<br>42<br>42<br>45<br>49<br>52<br>54<br>57<br>58                                                                     |

|   | <ul><li>3.3</li><li>3.4</li><li>3.5</li></ul>             | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2<br>3.5.3<br>Overce<br>3.6.1<br>3.6.2                             | sor Element Design                           | 39<br>40<br>41<br>42<br>42<br>45<br>49<br>52<br>54<br>57<br>58<br>58                                                               |

|   | <ul><li>3.3</li><li>3.4</li><li>3.5</li><li>3.6</li></ul> | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2<br>3.5.3<br>Overce<br>3.6.1<br>3.6.2<br>3.6.3                    | sor Element Design                           | 39<br>40<br>41<br>42<br>45<br>49<br>49<br>52<br>54<br>57<br>58<br>58<br>58                                                         |

|   | <ul><li>3.3</li><li>3.4</li><li>3.5</li></ul>             | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2<br>3.5.3<br>Overce<br>3.6.1<br>3.6.2<br>3.6.3<br>Curren          | sor Element Design                           | 39<br>40<br>41<br>42<br>42<br>45<br>49<br>52<br>54<br>57<br>58<br>58<br>58<br>58<br>58                                             |

|   | <ul><li>3.3</li><li>3.4</li><li>3.5</li><li>3.6</li></ul> | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2<br>3.5.3<br>Overce<br>3.6.1<br>3.6.2<br>3.6.3<br>Curren<br>3.7.1 | sor Element Design                           | 39<br>40<br>41<br>42<br>42<br>45<br>49<br>49<br>52<br>54<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58                     |

|   | <ul><li>3.3</li><li>3.4</li><li>3.5</li><li>3.6</li></ul> | Proces<br>3.3.1<br>3.3.2<br>Comm<br>3.4.1<br>3.4.2<br>Comm<br>3.5.1<br>3.5.2<br>3.5.3<br>Overce<br>3.6.1<br>3.6.2<br>3.6.3<br>Curren          | sor Element Design                           | 39<br>40<br>41<br>42<br>42<br>45<br>49<br>52<br>54<br>57<br>58<br>58<br>58<br>58<br>58                                             |

|          |      | 3.7.4          | Cēll/B.E. 32 SPE Concept Design 6          | 0            |

|----------|------|----------------|--------------------------------------------|--------------|

|          |      | 3.7.5          | Dual Processor Systems    6                | 0            |

|          | 3.8  | Applic         | ations                                     | 0            |

|          |      | 3.8.1          | Video Game Consoles                        | 1            |

|          |      | 3.8.2          | Cell/B.E. Blade Servers                    | 1            |

|          |      | 3.8.3          | Supercomputing                             | 2            |

|          |      | 3.8.4          | Cluster Computing                          | 3            |

|          |      | 3.8.5          | Grid Computing 6                           | 3            |

| <b>4</b> | Cell | /B.E.          | Program Models, Frameworks and Solutions 6 | <b>5</b>     |

|          | 4.1  | ,              |                                            | 5            |

|          | 4.2  |                |                                            | 6            |

|          | 4.3  | Cell St        |                                            | 6            |

|          | 4.4  | CoreP          |                                            | 7            |

|          | 4.5  |                |                                            | 8            |

|          | 4.6  |                |                                            | 8            |

|          | 4.7  |                |                                            | 9            |

|          |      | 4.7.1          |                                            | 0            |

|          |      | 4.7.2          |                                            | 0            |

|          | 4.8  | Rapidl         |                                            | 0            |

|          | 4.9  | Sequoi         | a                                          | 2            |

|          | 4.10 | SysCel         | llC                                        | $^{\prime}2$ |

|          | 4.11 |                |                                            | 73           |

|          |      | 4.11.1         | Manticore                                  | 73           |

|          |      | 4.11.2         | Open Computing Language (OpenCL)           | 73           |

|          |      |                |                                            | 74           |

| 5        | Cor  | onut N         | Aulticore Framework 7                      | <b>5</b>     |

| 0        | 5.1  |                |                                            | 75           |

|          | 5.2  |                | <b>9</b>                                   | 76           |

|          | 0.4  |                |                                            | 76           |

|          |      | 5.2.2          | Description                                | 77           |

|          |      | 5.2.2          |                                            | 79           |

|          | 5.3  |                |                                            | 33           |

|          | 0.0  | 5.3.1          |                                            | 33           |

|          |      | 5.3.1<br>5.3.2 |                                            | 33<br>36     |

|          |      | 5.3.2<br>5.3.3 |                                            | 30<br>38     |

|          |      | 5.3.3          |                                            | 50<br>89     |

|          |      | 5.3.4<br>5.3.5 |                                            |              |

|          |      | 5.3.0          |                                            | 89<br>91     |

|          |      |                | renormance annualor                        | 11           |

|   | 5.4 | Comparison with                         | Other Framewor    | cks . |     |     |  |  |     |   | 92  |

|---|-----|-----------------------------------------|-------------------|-------|-----|-----|--|--|-----|---|-----|

|   | 5.5 | Current Status                          |                   |       | • • | • • |  |  | • • | • | 94  |

| 6 | Per | formance Simula                         | ation             |       |     |     |  |  |     |   | 95  |

|   | 6.1 | Motivation                              |                   |       |     |     |  |  |     |   | 95  |

|   | 6.2 | Simulator Design                        |                   |       |     |     |  |  |     |   | 98  |

|   |     |                                         | Types             |       |     |     |  |  |     |   | 98  |

|   |     |                                         | Accuracy vs. Sp   |       |     |     |  |  |     |   | 99  |

|   |     |                                         | omputer Simulat   |       |     |     |  |  |     |   | 99  |

|   | 6.3 | Similar Tools .                         |                   |       |     |     |  |  |     |   | 100 |

|   |     |                                         | essor Simulators  |       |     |     |  |  |     |   | 100 |

|   |     |                                         | Simulators        |       |     |     |  |  |     |   | 100 |

|   |     |                                         | Simulators        |       |     |     |  |  |     |   | 101 |

|   |     |                                         | e Performance A   |       |     |     |  |  |     |   | 102 |

|   | 6.4 | Performance Sim                         |                   |       |     |     |  |  |     |   | 102 |

|   |     |                                         | d Usage           |       |     |     |  |  |     |   | 102 |

|   |     |                                         |                   |       |     |     |  |  |     |   | 106 |

|   |     | Sector Contractor Contractor Contractor | verview           |       |     |     |  |  |     |   | 107 |

|   |     |                                         | alysis            |       |     |     |  |  |     |   | 122 |

|   |     |                                         | tation and Unit ' |       |     |     |  |  |     |   | 124 |

|   |     |                                         | nce Testing       |       |     |     |  |  |     |   | 124 |

| 7 | Com | alusian and Dut                         | <b>X</b> 71-      |       |     |     |  |  |     |   | 105 |

#### 7 Conclusion and Future Work

135

# List of Figures

| 2.1  | Data dependency example                                       |

|------|---------------------------------------------------------------|

| 2.2  | Single Instruction Single Data                                |

| 2.3  | Single Instruction Multiple Data                              |

| 2.4  | Multiple Instruction Single Data                              |

| 2.5  | Multiple Instruction Multiple Data                            |

| 2.6  | Register renaming                                             |

| 2.7  | Problem category classification                               |

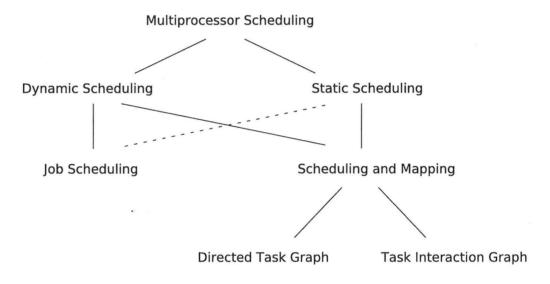

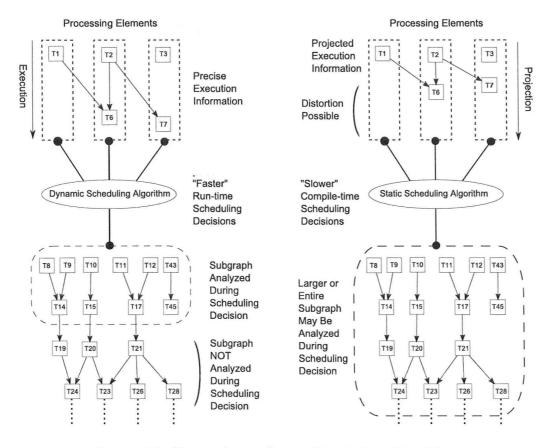

| 2.8  | Dynamic vs. Static Scheduling Algorithms                      |

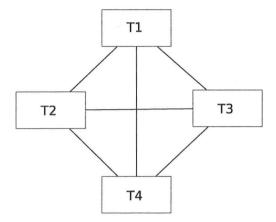

| 2.9  | Task interaction graph example                                |

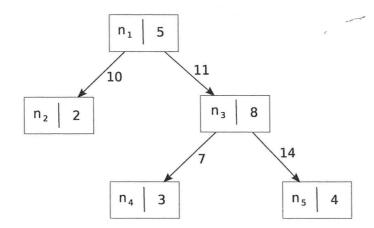

| 2.10 | Directed acyclic task graph example                           |

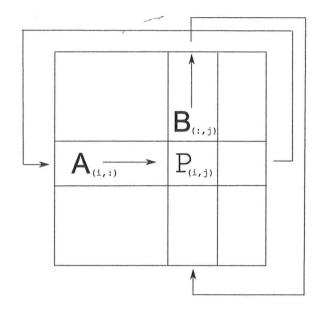

| 2.11 | Cannon's algorithm computes block $C(i, j)$ at each processor |

|      | P(i,j)                                                        |

| 0.1  |                                                               |

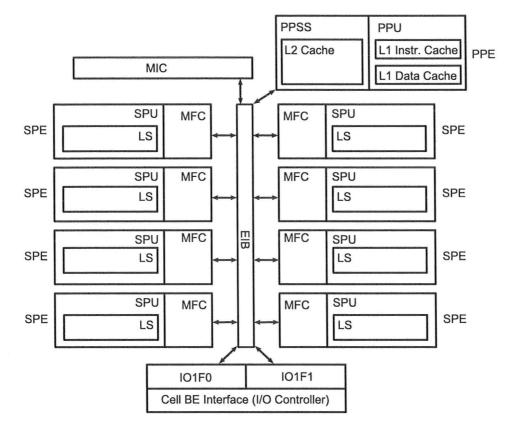

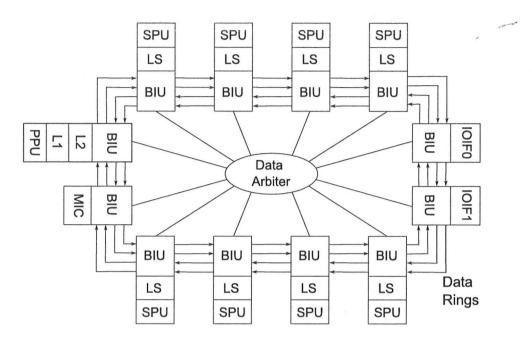

| 3.1  | Cell Broadband Engine Overview                                |

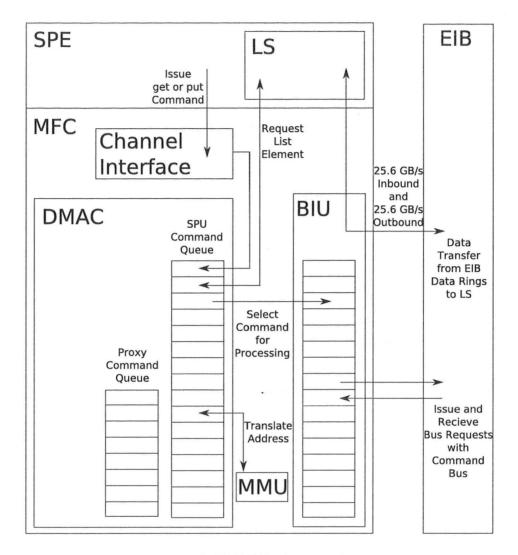

| 3.2  | SPE DMA Transfer Internals                                    |

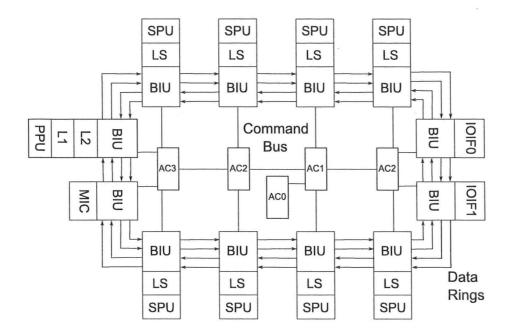

| 3.3  | EIB Command Bus                                               |

| 3.4  | EIB Data Arbiter                                              |

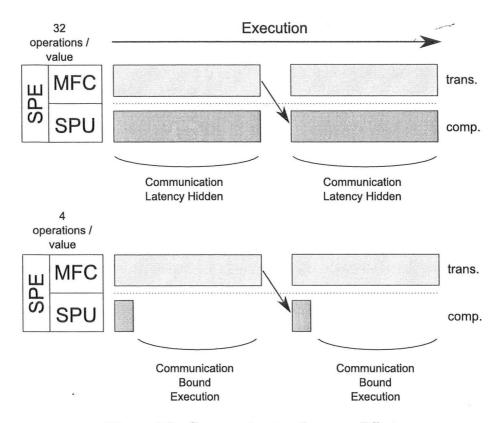

| 3.5  | Communication Latency Effect                                  |

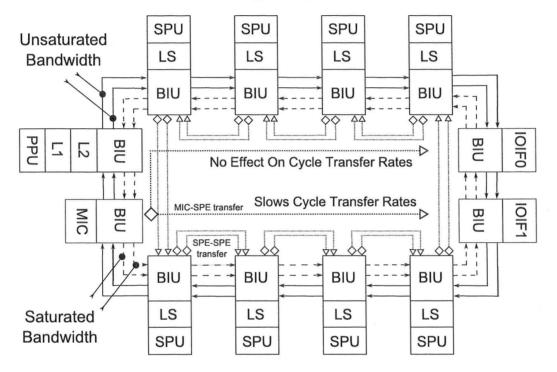

| 3.6  | Inefficient Cycle Communication Pattern                       |

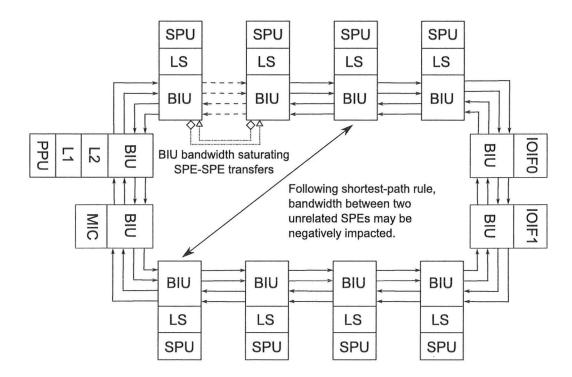

| 3.7  | Inefficient Heavy Inter-SPE Communication Pattern 54          |

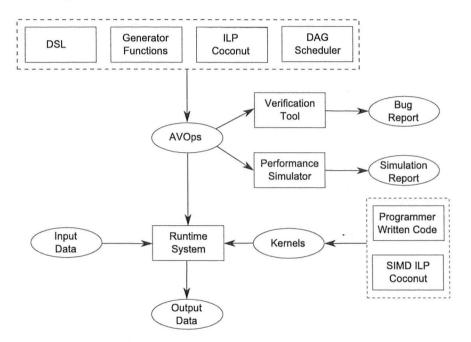

| 5.1  | Coconut Multicore Framework Overview                          |

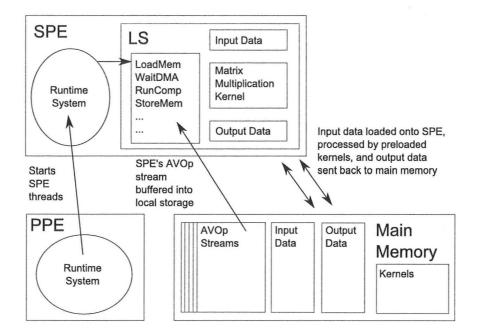

| 5.2  | Coconut Multicore Framework Runtime View 80                   |

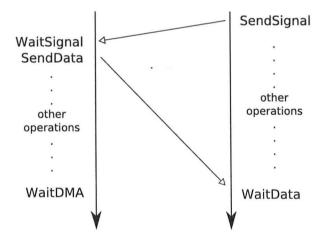

| 5.3  | Exposed Communication Latency                                 |

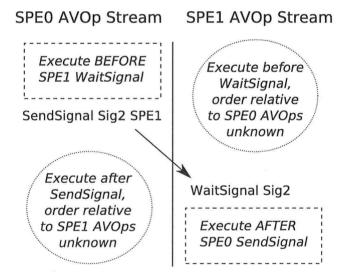

| 5.4  | AVOp partial execution order induction                        |

|      |                                                               |

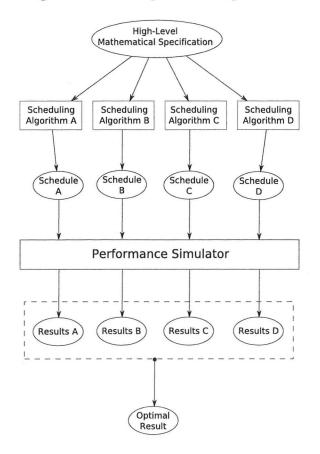

| 6.1  | Automated Schedule Selection                                  |

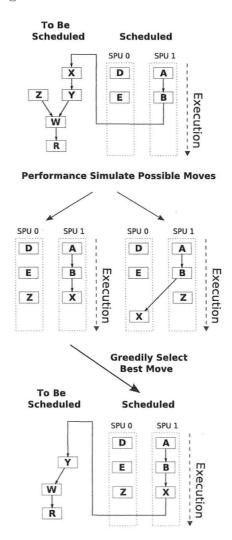

| 6.2  | Simulation Enhanced DAG Scheduling 105                        |

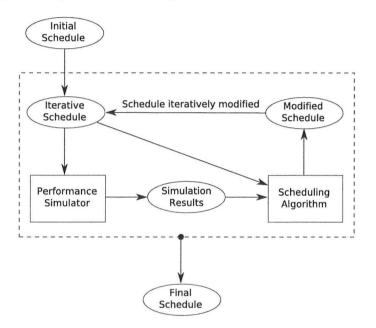

| 6.3  | Iterative Simulation Result Driven Scheduling 106             |

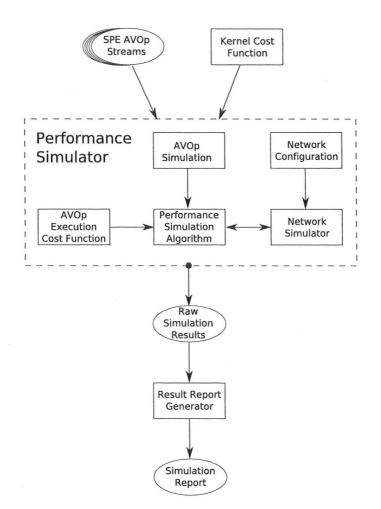

| 6.4  | Performance Simulation Design Overview                        |

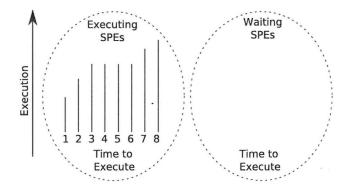

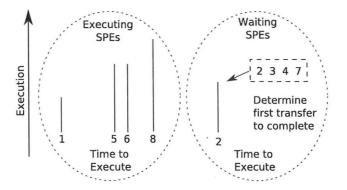

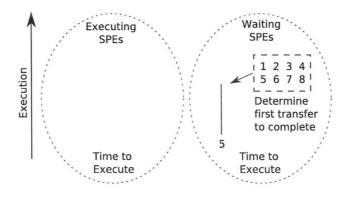

| 6.5  | All SPEs Executing 112                                        |

| 6.6  | Some SPEs Executing, Some SPEs Waiting | 113 |

|------|----------------------------------------|-----|

| 6.7  | All SPEs Waiting                       | 113 |

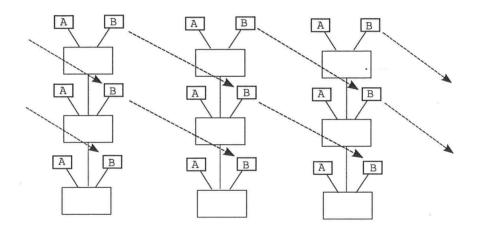

| 6.8  | Data Sharing Communication Pattern     | 126 |

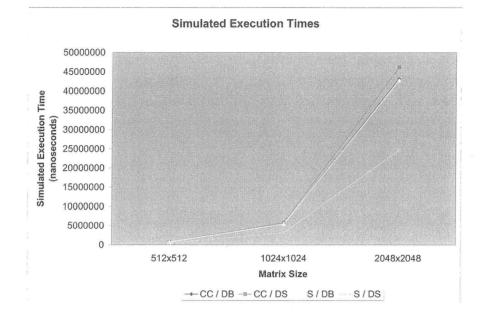

| 6.9  | Simulated Execution Time               | 130 |

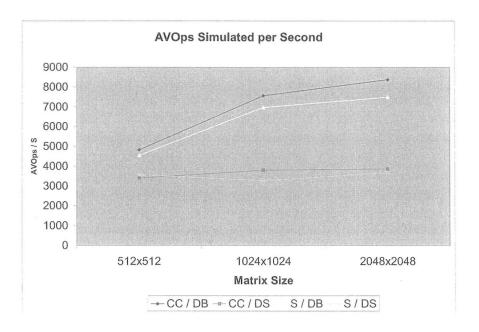

| 6.10 | AVOps Simulated per Second             | 131 |

## List of Tables

| 2.1                                       | Flynn's Taxonomy                                                                                                        | 9        |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------|

| $3.1 \\ 3.2$                              | Operations/Value Effect on Transfer vs. Computation Time .<br>RAM Capacity Effect on Square Matrix Mult. Problem Size . | 50<br>62 |

|                                           | Parallelism Correspondence                                                                                              |          |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Matrix Multiplication Performance Simulation Results<br>Network Bandwidth Simulation Test                               |          |

## Acronym Index

AC Address Concentrator **ALF** Accelerated Library Framework AVOp Atomic Virtual Operation **BIU** Bus Interface Unit Cell/B.E. Cell Broadband Engine Cell/B.E. SDK Cell/B.E. Software Development Kit CellSs Cell Superscalar **CMF** Coconut Multicore Framework Coconut COde COnstructing User Tool **DMA** Direct Memory Access **DMAC** DMA Controller **DSL** Domain Specific Language **EIB** Element Interconnect Bus FLOPS Floating Point Operations Per Second **IBM** International Business Machines Corporation **IDE** Integrated Development Environment **ILP** Instruction-Level Parallelism **IU** Instruction Unit

LAN Local Area Network

LQCD Lattice Quantum Chromodynamics

LS Local Store

MASS Mathematical Acceleration Subsystem

MFC Memory Flow Controller

MIC Memory Interface Controller

MIMD Multiple Instruction Multiple Data

MISD Multiple Instruction Single Data

**MPI** Message Passing Interface

MPMD Multiple Program Multiple Data

ns Nanoseconds

NUMA Non-Uniform Memory Access

**OpenCL** Open Computing Language

**OpenMP** Open Multi-Processing

**PDT** Performance Debugging Tool

**PE** Processing Element

**PPE** PowerPC Processor Element

**PPSS** Power Processor Storage Subsystem

**PPU** Power Processor Unit

**RAW** Read-After-Write

SCEI Sony Computer Entertainment Incorporated

**SIMD** Single Instruction Multiple Data

**SISD** Single Instruction Single Data

**SOI** Silicon on Insulator

**SPE** Synergistic Processor Element

SPMD Single Program Multiple Data

SPU Synergistic Processor Unit

**STI** SCEI-Toshiba-IBM

**TLB** Translation Lookaside Buffer

**UMA** Uniform Memory Access

**VSU** Vector Scalar Unit

WAN Wide Area Network

WAR Write-After-Read

WAW Write-After-Write

**XU** Fixed Point Execution Unit

$M.Sc. \ Thesis - Kevin \ Browne - McMaster - Computing \ and \ Software$

### Chapter 1

## Introduction

Since about 2004, chip manufacturers have increasingly turned to multicore architectures to increase performance. This paradigm shift has been dubbed the "multicore revolution" [HL08; GNS07]. Diminishing returns from frequency scaling, a critical technique used to increase processor performance in decades previous, were a major factor behind this technology shift.

One such architecture is the Cell Broadband Engine (Cell/B.E.), developed by Sony, IBM and Toshiba[KDH<sup>+</sup>05]. The Cell/B.E. is currently being used in the Playstation 3[BLK<sup>+</sup>07], and as such optimal usage of the processor is of high interest due to the userbase of over 20 million[Son09]. The Cell/B.E. is particularly interesting to computer scientists, some have referred to it as revolutionary[Hof06; Gsc07], due to its network-on-a-chip interprocessor communication and processor heterogeneity. While Cell/B.E. is not the first chip to have either of these properties, it is perhaps the first chip with these features to be so widely adopted.

These new architectures present novel challenges to software developers wishing to use them safely, optimally and easily. Safety is a difficult challenge due to race conditions that emerge when multiple processors use shared resources. These parallel bugs are difficult to diagnose using dynamic runtime tools, due to their occurrence being dependent upon small timing variations[RD00]. Static detection of these bugs at compile-time is an NP-hard problem, assuming the synchronization method is as powerful as semaphores[CMS01]. Optimization of parallel code is unfortunately no easier, as the general multiprocessor scheduling problem is NP-Complete[KA99]. There is also a lack of consensus as to which parallel programming model is best to represent a parallel program[ABC<sup>+</sup>06], with not much research done to analyze them empirically[HB06].

As a result of the daunting challenges facing developers wishing to take

advantage of these new architectures, new programming models and tools are being developed. For the Cell/B.E. in particular many tools such as RapidMind[McC06] and Cell Superscalar[BPBL06], amongst others[CHKW08; SYR<sup>+</sup>08; MML07; OIS<sup>+</sup>06], have been developed to overcome these challenges.

Coconut (COde CONstructing User Tool) is a compiler-technology project at McMaster, which is currently targeting the Cell/B.E. [AK07c]. Coconut was inspired largely by a desire to produce software that is both fast and safe, for applications such as medical imaging. Though strictly speaking it is more of a research platform than a fully developed commercial solution, Coconut can be thought of as another solution competing to overcome the challenges of developing for the Cell/B.E.. Coconut has had great success at delivering safe and optimal code at the ILP level on the Cell/B.E.; the Cell/B.E. SDK 3.0 SPU-MASS library currently includes code using Coconut ILP optimization techniques that is 4x faster than the alternative SIMDMath library created in C.

The Coconut Multicore Framework (CMF) is the current focus of Coconut research efforts; it targets multicore level parallelism on the Cell/B.E.. The framework design is made up of a virtual machine abstraction. Atomic virtual machine instructions execute on each processing element. These instructions are very high level, with only that information necessary to express multicore parallelism exposed. The instructions control all processor-level synchronization, and execute pre-loaded computations on data to produce results. The virtual machine and instruction abstraction purposely corresponds with ILP, so that Coconut ILP optimization techniques already developed may be re-used at the multicore level. A key feature of the CMF is the ability to perform static analysis with linearly bounded complexity, to analyze code safety and efficiency at compile-time. This has allowed us to design and implement a verification tool[AK08] capable of checking for parallel bugs; as a result we have not yet experienced a parallel bug at runtime in our virtual machine programs thus far.

Performance simulation is a potentially useful tool for the CMF for several reasons. Primarily because it allows developers to quickly contrast the performance of different scheduling algorithms, on a workstation instead of less easily accessible Cell/B.E. hardware, and with deeper information with respect to specific execution stalls and transfer latencies that would not be as easily available with other methods. Other reasons include that we can simulate theoretical architectures, both to analyze what architectures we may think *should* be produced and to be able to meaningfully experiment with scheduling on future or concept architectures before they become generally available. Finally, due to the efficient runtime of the performance simulator, it may actually become a useful tool in scheduling algorithms themselves, as others in the literature have either done themselves or proposed[JSK<sup>+</sup>06; CHB07].

The primary goal of this thesis is to present the Performance Simulator tool created entirely by the author as part of the CMF. To do this, we will present the design of the simulator itself, as well as performance testing of the tool.

As part of developing the Performance Simulator, the author played a role in developing the CMF itself. The author implemented the Verification Tool after acting as an internal reviewer of its design, as well as helping to design the virtual machine abstraction and debug its implementation. This required a great deal of background knowledge and research with respect to parallel computing, the Cell/B.E. architecture, as well as similar multicore parallelism solutions targeting the Cell/B.E.. As a result, this thesis will have a secondary purpose of documenting the research done into these areas as well, so it may be leveraged by future Coconut project team members.

### 1.1 Document Structure

In Chapter 2, we discuss parallel computing as a field, and attempt to define the most important concepts and elaborate on the most important issues. Those issues most relevant to multiprocessor computing are emphasized.

In Chapter 3, we introduce the Cell/B.E. and overview its design, architectural variants and current usage. Particular attention is paid to the design of the on-chip communication network, due to its importance in performance simulation.

In Chapter 4, we survey other multiprocessor program models and solutions targeting the Cell/B.E.. Both commercial and research focused solutions are discussed.

In Chapter 5 we discuss the design of the CMF, going over its specifics, features and advantages. We also contrast the CMF with other Cell/B.E. program models.

In Chapter 6 we explain the Performance Simulator design and present performance test results. We also further discuss the motivation to build the simulator, envisioned usage and some background information regarding performance simulation specifically.

Finally in Chapter 7 we overview the results of the thesis and suggest future avenues for Coconut project research based on the thesis results.

## Chapter 2

## Parallel Computing

Parallel computing is defined as computation which involves multiple simultaneous computations taking place. Parallel computing is becoming increasingly relevant to the undergraduate computer science curriculum due to the increasing prevalence of multicore and multiprocessor systems that demand more skill in concurrency-related programming[Fek09]. As a result, the need to modify the standard computer science curriculum to prepare students to reason about parallel computing problems has been recognized[Has03]. One problem however, is that there has not yet emerged a clear consensus as to how to properly classify these new multiprocessor systems that have driven this new interest in parallel computing[Mar07].

As a result of the great confusion regarding parallel computing, that is, how to classify it, what we mean by it, how to teach it and whether it is being taught properly or taught enough at the undergraduate level, this chapter will attempt to provide an overview of some of the most important concepts of parallel computing. Any terminology used by subsequent chapters will then be clearly defined in this chapter. The chapter will focus on the motivations for parallelism, the different ways of classifying different aspects of parallel computing, measuring the performance of a parallel program, and the unique challenges the parallelism presents.

### 2.1 Motivations

There are several motivations for parallel computing, mostly relating to the fact that we would like to be able to compute tasks quicker. It is intuitive that if one can split a task into several subtasks that can be processed concurrently, the task could theoretically be completed quicker than it could sequentially.

Amdahl's law, presented in Section 2.1.1, helps to quantify this potential speed up of parallelization for a given program. The other obvious way to speed up a computational task would be to process it quicker sequentially. This was what was done by chip manufacturer's until about 2004, when a series of frequency, memory and power walls finally forced chip manufacturers to turn to parallel multicore architectures to increase performance as outlined in Section 2.1.2.

#### 2.1.1 Performance Increases

Only certain portions of a sequential algorithm or program may be parallelized due to **data dependencies**. Data dependencies occur when an algorithm or program portion refers to the data of a preceding program portion. For instance, in the simple program in Figure 2.1, lines 1 and 2 do not have a data dependency and could be executed in parallel. In contrast line 3 depends on the results of lines 1 and 2, and so could not begin execution until both lines 1 and 2 have been processed without the potential for an erroneous result. If for instance line 3 was executed before line 2, unless Y happened to equal 10, an incorrect Z value would be the result. These hazards arise from race conditions and are discussed further in Section 2.8.2.

1:

$$X = 4;$$

2:  $Y = 10;$

3:  $Z = X + Y;$

Figure 2.1: Data dependency example

#### Amdahl's Law

With the understanding that only certain portions of a program may be parallelized, it would be useful to be able to quantify the potential gain from concurrently executing program fragments that are parallelizable. Amdahl's Law[Amd67] expresses this concept very simply in Theorem 2.1.

Theorem 2.1 (Amdahl's Law)

speed

$$up = \frac{1}{r_s + \frac{r_p}{n}}$$

where  $r_p + r_s = 1$ , n is the number of processors,  $r_s$  represents the sequential portion of a program and  $r_p$  represents the parallel portion of a program.

Notice that as  $n \to \infty$  we have that the speed up is  $\frac{1}{r_s} = \frac{1}{(1-r_p)}$ . This is interesting because it tells us that there exists a hard limit on how much parallelism can help speed up the runtime of a program. At a certain point, adding more processors is not going to make the program run any faster according to Amdahl's Law.

#### Gustafson's Law

The problem with Amdahl's Law is that it implies there is a theoretical point where adding parallelism will not increase performance, calling the sustainability of parallel architectures as a means to increase performance into question. **Gustafson's Law** was formed in response to Amdahl's Law by noting that it is virtually never the case that the portion of the code that is sequential is independent of the number of processors[Gus88]. What this means is that according to Gustafson's Law, as we scale the number of processors up, the sequential portion of the program will decrease in size — breaking through the limitation inherent in Amdahl's Law.

Gustafson's Law is important to parallel computing as a field, because for a long time pessimism surrounding parallel computing was at least partially due to Amdahl's Law, and Gustafson's Law helped to end this pessimism[Kri01]. It is presented in Theorem 2.2.

#### Theorem 2.2 (Gustafson's Law)

speed

$$up = n - r_s \times (n - 1)$$

where n is the number of processors, and  $r_s$  represents the sequential portion of the program.

#### 2.1.2 Frequency, Memory and Power Walls

The other motivation for parallel computing is that as hardware based on sequential computation has reached hard physical limits impeding further performance gains, parallel computation has effectively become *necessary* for reaping further performance gains. These hard physical limits are typically referred to as the frequency, memory and power walls. How the Cell/B.E. in particular overcomes these walls is discussed Section 3.6.

#### Frequency Wall

In order to increase the CPU frequency in modern processors, designers have been required to make instruction pipelines deeper (see Section 2.3.2 for a brief

description of instruction pipelining). The problem is that we have reached a point of diminishing returns for increasing pipeline depth[SBG+02]. When the number of pipeline stages is increased for the benefit of having the ability to process more instructions concurrently, it necessarily increases instruction latencies. When data dependencies on previous instructions combine with hard to predict branching behaviour in a program, a performance penalty is incurred which increases with the depth of the pipeline. At a certain pipeline depth, the negative effect of these penalties on program performance outweigh the positive effect of a longer pipeline (especially when power consumption is also taken into account).

A parallel architecture can overcome this problem by creating heterogeneous processing elements optimized for situations which involve a heavy amount of branching and for situations which involve a heavy amount of floating point computations. For instance, an architecture with different processing elements with different pipeline lengths to optimally handle each situation.

#### Memory Wall

The memory wall refers to the fact that processor speeds have been increasing faster than memory bandwidth, such that in modern processors DRAM latency can be measured in the hundreds of CPU cycles [KDH+05]. In his 1997 ACM Turing Award lecture, John Backus used the term "Von Neumann bottleneck" to refer to the fact that in the Von Neumann architecture the CPU is separated from memory, and that properly managing the bandwidth of this separation was key to programming[Bac78]. This essentially identified the potential for a memory wall, however the issue that caused this potential to be fulfilled was the divergence in performance between the CPU and memory bandwidth in unicore architectures. This problem was recognized and popularly identified by William Wulf and Sally McKee in 1994 when they noticed that the exponential growth in processor speed was far greater than the exponential growth in memory bandwidth[WM95]. If the trend continued, they realized that eventually a key impediment to program performance increases would be memory access latency. This wall would be hit at different times for different algorithms due to differing memory access characteristics [McK04], making a precise definition of when the memory wall was hit, or will be hit, difficult to specify in a general sense. Much effort has been exerted by hardware and algorithm designers on optimally using sophisticated hardware, such as multi-level caches, to lessen the effects of this wall[LRW91].

However parallel architectures can effectively alleviate this memory bottleneck by using a layered memory structure with asynchronous data trans-

fers between processing units — allowing for simultaneous data transfer and computation[Mud06].

#### Power Wall

Power density in processors has doubled roughly every 3 years since the early 1970s[SSS+04]. This trend was economically and technically infeasible to continue. It is economically infeasible because at a certain point consumers wouldn't be able to afford to run the processors if power consumption increased exponentially. It is technically infeasible because energy used in processors is often converted into heat which would at a certain point cause chips to fracture; without new technologies or expensive cooling systems (which would also increase power usage). Indeed, in 2004 Intel cancelled its Tejas and Jayhawk chips that were set to replace the Pentium 4 for these reasons[BKP07]. This event, along with Apple switching to Intel chips after its failure to develop a G5-based laptop, could be considered the microprocessor industry officially hitting the power wall.

Parallel architecture is capable of breaking through the power wall. When one considers that power usage scales exponentially relative to increases in clock frequency, it is correct to conclude that with the same power usage multiple processors running at a slower frequency could achieve greater performance than a single processor running at a higher frequency[Naf06]. Heterogeneous architectures that specialize processors for certain tasks[KDH<sup>+</sup>05], can provide further increases in power efficiency.

### 2.2 Flynn's Taxonomy

An important point about parallel computing is that it can take place in several different conceptual forms. In this section we seek to overview a common terminology for making distinctions between the different forms of parallelism found in hardware.

|                      | Single Data | Multiple Data |

|----------------------|-------------|---------------|

| Single Instruction   | SISD        | SIMD          |

| Multiple Instruction | MISD        | MIMD          |

Table 2.1: Flynn's Taxonomy

Flynn's taxonomy is a simple but widely used parallel computing classification proposed by Michael Flynn in 1966[M.J72]. The taxonomy classifies computer architectures according to the amount of data and instruction streams that are processed concurrently by processing elements (PEs). The acronyms for Flynn's taxonomy are more typically used in describing a classification and are found in Table 2.1.

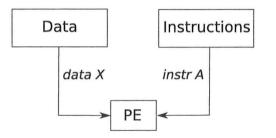

#### 2.2.1 Single Instruction Single Data (SISD)

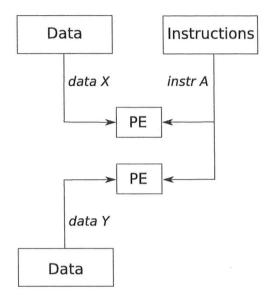

Single Instruction Single Data (SISD) computing occurs when a single stream of instructions works with a single stream of data. The von Neumann architecture is an example of SISD, as well as early personal computer microprocessors such as the Intel 8088. The inclusion of a concurrent feature such as pipelining in an architecture does not preclude a processor from being categorized as SISD; what matters is that there is one stream of instructions operating on one stream of data. An example of SISD is shown in Figure 2.2.

Figure 2.2: Single Instruction Single Data

#### 2.2.2 Single Instruction Multiple Data (SIMD)

A single stream of instructions operating on multiple streams of data is called Single Instruction Multiple Data (SIMD) parallelism; also referred to as "Vector Processing" in the literature. There are abundant examples of SIMD parallelism in hardware, dating back to the TI-ASC and CDC Star 100 in the 1970s and the MMX instruction set made popular in the Pentium chipsets of the 1990s[EVS98]. The Cell/B.E. in particular derives much of its raw floating point computing power from its SPEs optimized for SIMD performance[KDH<sup>+</sup>05]. SIMD is very useful with computations that can be conceptualized as vectors, such as problems in linear algebra and multimedia applications. Scheduling code for SIMD processors is a current area of exper-

tise within the Coconut project[AK07a; Tha06; AK07c]. An example of SIMD is shown in Figure 2.3.

Figure 2.3: Single Instruction Multiple Data

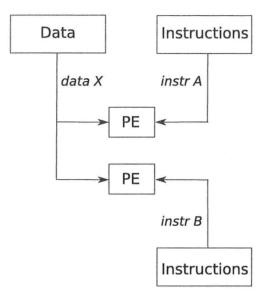

### 2.2.3 Multiple Instruction Single Data (MISD)

In Multiple Instruction Single Data (MISD) parallelism, multiple streams of instructions operate on a single stream of data. This type of parallelism is virtually non-existent in existing hardware [FR96]. It could be useful as a fault-tolerance measure in hardware design, and it has been proposed that MISD architectures would be ideal for pattern matching on data streams [HSN+04]. An example of MISD is shown in Figure 2.4.

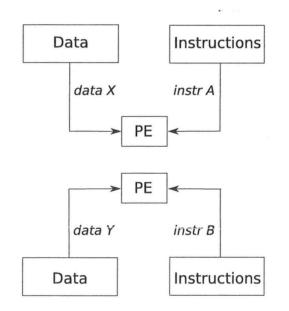

#### 2.2.4 Multiple Instruction Multiple Data (MIMD)

Multiple processing elements asynchronously executing different streams of data is referred to as Multiple Instruction Multiple Data (MIMD) parallelism. Networks of workstations under different topologies are an example of MIMD parallelism [FR96]. Multicore level parallelism is another example of MIMD parallelism in hardware [AL07]. Scheduling and verifying the correctness of MIMD-level parallelism is the newest focus of the Coconut project, and the focus of this thesis. An example of MIMD is shown in Figure 2.5.

Figure 2.4: Multiple Instruction Single Data

Figure 2.5: Multiple Instruction Multiple Data

#### Single Program Multiple Data (SPMD)

A subdivision of MIMD parallelism where multiple processing elements execute different parts of the same program on multiple data streams is defined as Single Program Multiple Data (SPMD) parallelism[CDG<sup>+</sup>93].

#### Multiple Program Multiple Data (MPMD)

Another subdivision of MIMD parallelism is referred to as Multiple Program Multiple Data (MPMD) parallelism, it occurs when multiple programs operate on multiple data streams[RSB94].

### 2.3 Parallelism Levels

The different levels of parallelism that may exist within hardware will be outlined in this section. Interestingly, the history of the modern microprocessor can be roughly divided into eras according to which level of parallelism was being exploited to increase chip performance at the time[MSVV00], with increases in bit-level parallelism giving way to increases in instruction-level parallelism followed by the task-level parallelism increases in modern multicore processors.

#### 2.3.1 Bit-level Parallelism

**Bit-level parallelism** refers to the parallelism associated with the width in bits of registers in a processor. By going from 16-bit to 32-bit registers, one has in some cases doubled the computing power by operating concurrently on 32 instead of 16 bits. For instance if one was adding two 32-bit unsigned integers, in the case of the 16-bit architecture, one would have to add the lowest bits first, and then the highest afterwards in a separate operation (plus any carry over from the addition of the lowest bits). If one had the ability to operate on 32 bits in parallel however, this could be done in a single operation. Up until about 1985, increasing bit-level parallelism was an important way in which processing power was increased[MSVV00]. Since this time, the market has been dominated largely by 32-bit architectures and some 64-bit architectures. Exploiting other forms of parallelism started to make more sense at this time, as for most applications 32-bit or 64-bit precision is sufficient.

#### 2.3.2 Instruction-level Parallelism

Instruction-level parallelism occurs when we execute the instructions of a sequential binary program concurrently. This form of parallelism takes many forms itself, with optimizations to exploit it taking place at the hardware level at runtime, but also by compilers and potentially by crafty programmers. The period of the late 1980s to the early 2000s is strongly associated with increasing levels of instruction-level parallelism as a means to increase performance in hardware design[MSVV00]. The different ways in which instructions can execute in parallel will be briefly defined in the remainder of this section, though it should be noted these are expansive fields of study with much published research.

#### **Out-of-order** Execution

**Out-of-order execution** occurs when instructions are executed in a different order than is presented in the compiled binary file of the program. Normally if an instruction is set to be executed, but its input operands are unavailable, the instruction will stall and computation will cease until the operands are available. With out-of-order execution, instructions are first collected in a queue, and execute when input operands are available. The key point being that an instruction in the queue that occurs *after* another instruction in the queue may be dispatched ahead of it to a processing element for execution; and so the execution is out-of-order. The results of the instructions are themselves queued, and are then put into the correct program order as given in the binary file as more instructions complete. As a result the program appears to have executed in the correct order, though this may not have been the case. The speed-up of out-of-order execution derives from hiding the latency of fetching data for instructions to operate on by executing other instructions where a stall in execution would otherwise occur.

Data dependencies may prevent out-of-order execution from being possible in all cases. Also, it should be noted that maintaining the behaviour of hardware exceptions was a key hurdle to overcome in enabling out-of-order execution to become a more common hardware ability [SP88]. Out-of-order execution became very common in processors starting in the 1990s, for instance in the Pentium Pro[KPH<sup>+</sup>98] and AMD-K5[Chr96].

#### Instruction Pipeline

An instruction pipeline allows for multiple instructions to execute concurrently. The key idea is that each instruction executing concurrently is executing a different stage in the set of stages required to execute an instruction. An instruction pipeline is somewhat analogous to an assembly line in automotive manufacturing. Instead of producing one automobile at a time, the steps are broken down, for instance as: obtain all parts, assemble frame, attach wheels and place vehicle in truck for shipment. By doing all of these steps concurrently, a manufacturer could have four cars being built at once instead of one.

Instruction pipelines in processors divide the processing of an instruction into independent steps. The steps may include: fetch instruction from memory, decode instruction and read registers, execute the instruction, access memory, and write the result into a register. In the same way that all the steps of an assembly line can be run concurrently, so can the stages of an instruction pipeline. If a CPU were to process one instruction at a time, its clock frequency would be limited to the time it takes to do all of these steps. However if a CPU were to use pipelining, its clock frequency could be increased to the time it takes to do the longest step in the pipeline.

As discussed in Section 2.1.2, hard to predict branching behaviour limits the performance of an instruction pipeline. An example of an architecture which used instruction pipelining is the Pentium 4[ZR04], which had a 20stage instruction pipeline.

#### Superscalar Execution

Superscalar execution works by simultaneously dispatching instructions for execution. This can be done because the instructions are dispatched to different computational units within the processor, for instance an ALU and an FPU. In order for this to work, the processor hardware has to check for data dependencies that would create hazards before executing instructions concurrently. One can see that data dependencies will place an upper bound on the effectiveness of superscalar execution, with studies showing that for instance 8-way superscalar is likely to provide little benefit[MSVV00]. It is important to note that pipelining and superscalar execution could be occurring at once within the same processor, the instructions could be concurrently sent to pipelined execution units which also execute instructions concurrently in different stages.

Early processor designs contributing to superscalar concepts included the CDC-6600 and IBM-360/91[FB92]. In the 1990s pipeline execution was found in more mainstream computers, such as the AMD K5 and the MIPS R10000[SS95b].

#### Other Important Techniques

Other techniques may be used in conjunction with out-of-order execution, instruction pipelining and superscalar execution to better exploit instruction level parallelism. These techniques do not create a new conceptual form of instruction level parallelism, but instead allow the existing techniques to be used more effectively.

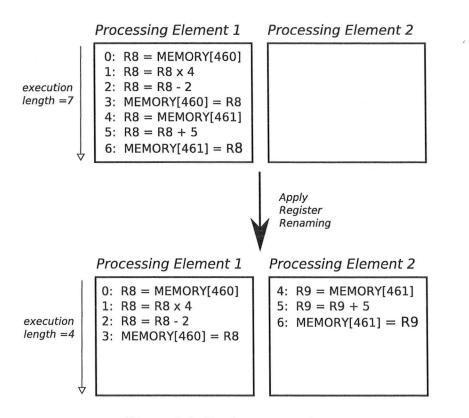

**Register renaming** is a technique which removes unnecessary data dependencies from serial code in order to remove any hazard of running them in parallel. This allows for instructions which would previously be run in serial to be run in parallel[SP88]. In Figure 2.6 an example of register renaming is shown. In this example we see that if instructions 4-6 could be performed using a different register than register 8, it would eliminate the dependency these instructions have on instructions 0-3, without effecting the correctness of the results. Eliminating these dependencies allows us to operate on these groups of instructions in parallel, which reduces the total execution time. Register renaming is thus a technique which allows us to exploit superscalar execution (and potentially out-of-order execution) more effectively by removing unnecessary data dependencies. It turns out that the only dependencies [SP88]. Register renaming cannot eliminate are *read-after-write* dependencies[SP88]. Register renaming can be done by a compiler or by hardware (the first instance of which being the floating point unit of the IBM 360/91[MPV93]).

Speculative execution and branch prediction are also important techniques for helping to exploit instruction level parallelism [GG97]. Speculative execution refers to execution for which the results may not actually be used. For example, load instructions may have somewhat predictable behaviour and the memory locations which they reference may be computed ahead of time. If the speculative execution turns out to be incorrect, say for instance the load memory instruction actually references a different address, a stall will be required while the proper computation is executed. Branch prediction refers to speculative execution where the instructions following a potential path of the branch are executed. If the speculation is correct, then instructions which have already entered the instruction pipeline can proceed, otherwise a stall will be required while the correct instructions begin to execute. Speculative execution and branch prediction thus help to exploit instruction pipelines in particular. This is done by speculatively allowing instructions for which we are not certain we will need the results for to execute, at the penalty of a stall if the speculation is incorrect. These techniques are common place in modern processors, for instance in the Intel Pentium Pro and SUN Ultrasparc[MSVV00].

Figure 2.6: Register renaming

## 2.3.3 Thread-level Parallelism

In contrast to instruction-level parallelism, where instructions from a single stream of instructions are executed in parallel, **thread-level parallelism** occurs when more than one stream of instructions from the same program (or process) are executed concurrently[ACVP06]. The definition of what constitutes thread-level parallelism beyond this is less clear. Partially because what differentiates a thread, process and program is dependent upon the hardware and operating system of the machine. On a single core machine, a multithreaded program does not necessarily have threads executing concurrently, but instead multiple threads forked from the same program may take turns executing individually (time-sliced). However on a multicore or multiprocessor machine, a multithreaded program may have each thread assigned to a different core or a different processor, in which cases threads could be executing concurrently. It should be noted that even though in the case of a single

core the threads do not execute concurrently, they share access to common resources, and from the point of view of the programmer who may not have control over how hardware and the operating system is switching between threads, they might as well be concurrently executing. We say this because the programmer will have to worry about the same issues as they would if the threads were executing concurrently.

Thread-level parallelism is also the first level of parallelism whose efficiency and correctness is largely dependent upon software and the programmer, and not by hardware. With instruction-level parallelism, optimizations are often made by a compiler or programmer with knowledge of the underlying hardware, but concurrency based hazards are protected against at the hardware level. With thread-level parallelism however, not only is optimization highly dependent upon skilled program implementation, often at the level of program source code and not at the automated level of the compiler, but hazards due to concurrent execution must be handled by the programmer as well. Competition between threads for resources, thread synchronization overhead, context-switching overhead and sometimes conflicting performance vs. correctness goals all must be considered by a programmer[JFL98]. This makes optimizing and verifying the correctness of thread-level programming a particularly difficult problem for programmers[ACVP06].

Advantages of multithreaded programs include increased performance on multicore or multiprocessor systems[Eng00]. As well, multithreaded programs allow for computation heavy tasks to run on a thread separate from another thread which handles user I/O, which prevents the entire program from freezing from the vantage point of the user and improves performance by overlapping I/O and computation[JFL98].

Examples of architectures and operating systems capable of threadlevel parallelism are common in modern computer systems. For example, Intel Core Duo processors running Windows XP are capable of thread-level parallelism[ACVP06].

## 2.3.4 Process-level Parallelism

**Process-level parallelism**, which occurs in multiprocessing systems, is the parallelism that occurs when we have two processes or programs executing concurrently[HNO97]. It is different from thread-level parallelism in the sense that in thread-level parallelism the concurrent streams of instructions are forked from the same process[ONH<sup>+</sup>96]. Process-level and thread-level parallelism can both occur in multicore systems, but only process-level parallelism can occur when the multiple CPUs of a machine architecture do not share re-

sources that may be required for thread-level parallelism, such as a cache. This can happen when the multiple CPUs are not on the same chip, but instead we have multiple processes interacting across an Ethernet network. One way to distinguish multiprocessor architectures is by the symmetry of the processors. Different classifications of multiprocessor hardware can also be made based on the type of communication infrastructure between the processors.

#### **Processor Symmetry**

The processing elements in a process-level parallelism capable multiprocessor system do not necessarily have to be the same, or have access to the same system resources.

A symmetric multiprocessing system is one in which two or more (identical) processors have equal access to the same memory[CG08], sometimes referred to as homogenous multiprocessing. It is characterized by the ability of a computing system with multiple processors to treat them like a single processor[IY00]. The Intel Core 2 Duo is an example of a symmetric multiprocessor[CG08].

In contrast an **asymmetric multiprocessing** system, sometimes referred to as heterogeneous multiprocessing, is one in which the multiple processors have different characteristics such as resource access, performance, power consumption and instruction sets[Mar07]. There is no such requirement that an asymmetric multiprocessor is able to treat its multiple processors as a single processor. An example of an asymmetric multiprocessor is the Tensilica Xtensa LX, which allows individual cores to be configured differently before processing different applications[Mar07].

#### Multiprocessor Architectures

Multiprocessor architectures themselves are roughly classified into different categories based on the way in which the CPUs communicate. Multicore systems, though containing multiple processors, are referred to as such because the multiple processors are contained on the same physical chip[Mar07]. In contrast systems referred to as multiprocessor systems are generally those with levels of communication between processing elements that are higher up than chip-level. These different levels of communication can themselves be more abstractly described to classify different types of multiprocessor systems, and this is done so in Section 2.6.2.

# 2.4 Task Parallelism vs. Data Parallelism

Parallel computing can also be divided conceptually into two very broad categories: task parallelism and data parallelism. This section will outline what is meant by this distinction.

# 2.4.1 Task Parallelism

Task parallelism, also referred to as functional parallelism[GP95], focuses on concurrent execution of tasks with multiple processes or threads on multiple computing nodes, operating on the same or different data, with explicit communication between the computing nodes[SSOG93]. An example of a task could be a C language function for matrix multiplication. Task parallelism can be thought of as a way of looking at parallelism, where we look at a computation as a series of interacting, perhaps order dependent tasks. This can take place at different layers in hardware, with the process/thread level of parallelism in hardware being a potential layer for task parallelism. One could also consider task parallelism at the level of a disturbed system, with each processing element executing a task. The important idea in considering task parallelism is that the task, and dependencies and interactions between tasks, is the emphasis of reasoning about concurrency.

## 2.4.2 Data Parallelism

In contrast to task parallelism, **data parallelism** is parallelism where there is concurrent execution of the *same* task on data, and with identical tasks the focus is then on the distributed nature of the data[HS86]. Data parallelism thus roughly equates to SIMD parallelism. As with task parallelism, data parallelism can occur at different levels of hardware. Data parallelism can be said to occur if a single thread or process, or multiple threads or processes, operate on the same or different data, from the same or different source. The key point concerning data parallelism is that we reason about the distribution of data, as the task is known to be the same across all processing elements.

# 2.5 Memory Classifications

Memory in parallel computing systems can be classified in several ways, perhaps most importantly as shared or distributed memory. The way in which the memory of a parallel computer works defines which types of parallel computation are possible. A hybrid between shared and distributed memory exists and is called distributed shared memory. The type of memory model may effect which algorithms are possible, and whether processing elements access data in uniform time or not.

#### 2.5.1 Shared Memory

In a shared memory system, all of the processing elements have access to the same shared memory address space[PZOL01]. An example of such a system would be a dual core microprocessor where each core has access to the same large block of random access memory. Scalability is a problem with shared memory systems, as it increases the effects of the memory wall discussed in Section 2.1.2. Adding additional processing elements to access the same shared memory won't increase performance if the pipeline bandwidth is already completely consumed fulfilling the data requirements of existing processing elements. The fact that memory is shared between two cores or computational units, does not necessarily imply that some lower-level of memory is shared, such as cache. Examples of shared memory processors include the Intel Pentium D, where two cores don't share a cache, or the Intel Core Duo, where the two cores do share a cache[FVP06].

# 2.5.2 Distributed Memory

In a distributed memory system, each of the processing elements can access only a portion of the total system memory. For instance each processing element could have its own local memory. If a processing element wishes to operate on data located in another processor's private memory, the data is exchanged through some communication mechanism. As large shared memory systems are expensive to build, an advantage of distributed memory systems is that they have a significant cost-performance advantage over shared memory systems[CK88]. The performance of distributed memory systems also scales better when increasing the number of processing elements as discussed in Section 2.1.2. However the systems are considered much harder to program for than shared memory systems, as for instance one cannot have shared memory data structures[KMVR90]. A distributed memory system's performance can also be highly dependent upon effective usage of whatever communication mechanism exists between processing elements[CK88]. The BlueGene/L supercomputer is an example of a system with distributed memory[AAA<sup>+</sup>02].

# 2.5.3 Distributed Shared Memory

Distributed shared memory systems have processing elements with private memory that can also access memory shared between processors. This shared memory access can be implemented through hardware, or it can be done through some software abstraction to give the illusion of physically shared memory[NL91]. Distributed memory systems can offer the advantage of shared data structures (and thus portability with code programmed for shared memory architectures), while allowing for scalability by alleviating the memory wall hardware bottleneck. An example of a software level abstraction to provide for shared memory access in a distributed system would be the OpenSSI single system image clustering system which allows a cluster of computers to share resources such as memory[LGV+05].

# 2.5.4 Uniform Memory Access (UMA)

Uniform memory access (UMA) parallel computing systems have the property that the time to access data is not affected by its location in shared memory, or by the processing element requesting the data[ZSLW92].

## 2.5.5 Non-Uniform Memory Access (NUMA)

In contrast, **non-uniform memory access (NUMA)** parallel computing systems have the property that the location of the data accessed relative to the processing element can have an order of magnitude effect on the time required to access the data[BTK06].

# 2.6 Processing Element Communication