# A POWER ANALYSIS OF THE COMBINED INPUT AND CROSSPOINT QUEUED SWITCH

# A POWER ANALYSIS OF THE COMBINED INPUT AND CROSSPOINT QUEUED SWITCH

BY

JIAN WANG, B.Sc.

### A THESIS

## SUBMITTED TO THE DEPARTMENT OF ELECTRICAL & COMPUTER

### ENGINEERING AND THE SCHOOL OF GRADUATE STUDIES

### OF MCMASTER UNIVERSITY

### IN PARTIAL FULFILMENT OF THE REQURIEMTNS

### FOR THE DEGREE OF

### MASTER OF APPLICED SCIENCE

© Copyright by Jian Wang, August 2009

All Rights Reserved

Jian Wang

Master of Applied Science

McMaster University - ECE

McMaster University

(Electrical & Computer Engineering)

Hamilton, Ontario, Canada

TITLE:A Power Analysis of the Combined Input and Crosspoint<br/>Queued SwitchAUTHOR:Jian Wang<br/>B. Sc., (Computer Engineering)<br/>McMaster University, Hamilton, ON, CanadaSUPERVISOR:Dr. T. H. SzymanskiNUMBER OF PAGES:139

Ì

## Abstract

Crossbar switches are fundamental building blocks of digital networks, such as the Internet. An *Input-Queued (IQ)* switch with a set of queues at the input side is the most widely used crossbar switch due to the scalability and low design complexity. While *IQ* switches are used in commercial routers, the schedulers are relatively complex. An alternative switch design is to insert a FIFO queue in each crosspoint of an *IQ* switch. This architecture is named the Combined Input and Crosspoint Queued switch, denoted as *CIXQ*. The use of crosspoint queues simplifies the scheduling of traffic through the switch, at the cost of adding  $N^2$  FIFO queues to the switch fabric.

In recent years, considerable research has been made to study the capability and flexibility of the *CIXQ* switch over high-speed networks. In this thesis, we will review the *CIXQ* switch by focusing on the switching performance, design implementation and power consumption. The switching performance is first evaluated using MATLAB. The analysis results show that the *CIXQ* switch with a simple Round Robin scheduling can achieve a high performance under various traffic patterns. In an attempt to analyze the power consumption, a *CIXQ* switch is then implemented in VHDL based on a broadcast-and-select architecture and a DEMUX-MUX architecture. The designs are tested and simulated on Altera Cyclone II FPGAs. The simulation results illustrate that the switches are operational correctly as specified in Chapter 4. As power has become a critical design issue, a power analysis for *IQ* and *CIXQ* switches is finally presented. Analytic power models for the switches in an FPGA environment are developed. As the major

contribution of this thesis, we are the first to develop power models for the *CIXQ* switch. The power models allow the designers to explore the power efficiency of various crossbar switches in the early stages of design process. The verification indicates that the power models are quite accurate with an average error of less than 10%. The analysis also shows that a *CIXQ* switch with  $N^2$  crosspoint queues consumes about three times as much power as the *IQ* switch for modest size switches (4x4, 8x8, and 16x16) in an FPGA environment.

In conclusion, we present an analysis of the design implementation and power consumption of the *CIXQ* switch. The discussions illustrate a fact that the *CIXQ* switch with a FIFO queue in each crosspoint increases the cost and hardware complexity even though it will simplify the scheduling problem. The designers must analyze this trade-off when making architectural design decisions.

### Acknowledgements

I would like to thank all those people who helped me throughout this work. First of all, I would like to express enormous appreciation to my supervisor, Dr. Ted. H. Szymanski, for his encouragement, guidance, patience, and support during the period of my studies. Dr. Szymanski provides me with the opportunity to work on such an interesting and exciting project. Without his priceless suggestions, this project would not have reached this stage.

Second of all, I would also like to thank Dr. Dave Gilbert, who not only helps me to organize and improve the thesis, but also give me valuable suggestions and encouragements during my research. Besides, I would like to thank my committee members, Dr. T. Todd and Dr. N. Nicolici, for their support, kindness, and insightful suggestion throughout this thesis.

I would like to extend my special thank to all the administrative and technical staff at the department of Electrical and Computer Engineering that made the completion of this project possible, especially to Terry Greenlay and Cosmin Coroiu for setting up the hardware and software for the experimental purpose, and Steve Spencer and Tyler Ackland for providing the experimental devices for my research. Furthermore, I would also like to thank the members of Altera support team for patiently answering my numerous questions about the design devices and tools.

Finally, I wish to thank my parents for their encouragement and support throughout all my academic years. I also thank my younger sisters and little brother for their understanding. Most importantly, I would like to dedicate this thesis to my beloved grandma, who passed away recently. Thanks you grandma for everything you have done for me.

# Notation and Abbreviation

| I <sub>SW</sub>              | Switching current                                           |

|------------------------------|-------------------------------------------------------------|

| $C_{ m int}$                 | Intrinsic capacitance                                       |

| $C_{load}$                   | Load capacitor                                              |

| $V_{DD}$                     | Core voltage                                                |

| I <sub>SC</sub>              | Short circuit current                                       |

| $f_{clk}$                    | Clock frequency                                             |

| $f_{duty}$                   | Duty cycle                                                  |

| $N_{trans}$                  | Average number of transitions per clock cycle               |

| μm                           | Micron                                                      |

| $P_{static\_per\_component}$ | Static power dissipated by each component in the design     |

| Κ                            | Power coefficient                                           |

| $K_{DEMUX1m}$                | Power constant for 1-to-m DEMUX cell                        |

| K <sub>DEMUX12</sub>         | Power constant for 1-to-2 DEMUX cell                        |

| K <sub>MUXm1</sub>           | Power constant for m-to-1 MUX cell                          |

| $K_{MUX21}$                  | Power constant for 2-to-1 MUX cell                          |

| $K_{_{FIFO}}$                | Power constant for a FIFO queue                             |

| $K_{Bus1N}$                  | Power constant for broadcast bus power in an NxN switch     |

| $S_i$                        | Average switching activity                                  |

| $S_{DEMUX1m}$                | Synthesis efficiency for 1-to-m DEMUX cell                  |

| S <sub>DEMUX12</sub>         | Synthesis efficiency for 1-to-2 DEMUX cell                  |

| $S_{MUX 21}$                 | Synthesis efficiency for 2-to-1 MUX cell                    |

| $C_i$                        | Capacitance related to the particular logic block or module |

| N <sub>LE-DEMUX</sub>        | Logic elements used in the 1-to-N DEMUX                     |

| N <sub>LE-MUX</sub>            | Logic elements used in the N-to-1 MUX                       |

|--------------------------------|-------------------------------------------------------------|

| $V_{swing}$                    | Swing voltage                                               |

| $V_{ m supply}$                | Supply voltage                                              |

| P <sub>total</sub>             | Total power                                                 |

| P <sub>static</sub>            | Static power                                                |

| $P_{\it static-per-component}$ | Static power dissipated by each component                   |

| P <sub>dynamic</sub>           | Dynamic power                                               |

| P <sub>MAX</sub>               | Maximum allowed power dissipation in the device             |

| P <sub>DEMUX-MUX</sub>         | Power of the CIXQ switch in the DEMUX-MUX design            |

| P <sub>DEMUX</sub>             | DEMUX power                                                 |

| P <sub>MUX</sub>               | MUX power                                                   |

| $P_{BUS}$                      | Broadcast bus power                                         |

| $P_{(Bus1N)}$                  | Broadcast bus power in an NxN switch                        |

| $P_{XQ}$                       | Crosspoint queue power                                      |

| $P_{B\&S}$                     | Power of the CIXQ switch in the broadcast-and-select design |

| P(XQ)                          | Crosspoint queued switch power                              |

| P(IQ)                          | Input queued switch power                                   |

| P <sub>DEMUX1N</sub>           | 1-to-N DEMUX power                                          |

| P <sub>DEMUX1m</sub>           | 1-to-m DEMUX power                                          |

| P <sub>MUXN1</sub>             | N-to-1 MUX power                                            |

| P <sub>MUXm1</sub>             | m-to-1 MUX power                                            |

| P <sub>(FIFONw)</sub>          | FIFO power with N w-bit words                               |

| P(I)                           | Probabilities of being in IDEL state of a FIFO queue        |

| P(W)                           | Probabilities of being in WRITE state of a FIFO queue       |

|                                |                                                             |

| P(R)              | Probabilities of being in READ state of a FIFO queue             |

|-------------------|------------------------------------------------------------------|

| P(RW)             | Probabilities of being in READ and WRITE state of a FIFO queue   |

| $T_A$             | Ambient temperature                                              |

| $	heta_{_{J\!A}}$ | Thermal resistance                                               |

| $T_{C}$           | Case temperature                                                 |

| $	heta_{_{JC}}$   | Junction-to-case thermal resistance                              |

| р                 | Input traffic load                                               |

| f(x)              | Probability function                                             |

| x                 | Bernoulli process                                                |

| $p_{ij}$          | The traffic load for a cell at input $i$ destined for output $j$ |

| ASIC              | Application Specific Integrated Circuit                          |

| B&S               | Broadcast-and-Select structure                                   |

| BMX               | Bus Matrix Switch                                                |

| CAD               | Computer-Aid Design                                              |

| CDFG              | Control Data Flow Graph                                          |

| CES               | Chip Estimation System                                           |

| CIXQ              | Combined Input and Crosspoint Queued switch                      |

| CMOS              | Complementary Metal-Oxide Semiconductor                          |

| CoS               | Classes of Service                                               |

| DEMUX             | Demultiplexer                                                    |

| DEMUX-MUX         | Demultiplexer-and-Multiplexer structure                          |

| DRRM              | Dual Round-Robin Matching                                        |

| DSP               | Digital Signal Processing                                        |

| FIFO              | First Input and First Out                                        |

| FPGA              | Field Programmable Gate Array                                    |

| Gpbs              | Gigabits per second                                              |

| HOL               | Head of Line                                                     |

| i.i.d             | Independent and identical distribution                           |

| IP      | Input Port                           |

|---------|--------------------------------------|

| IQ      | Input Queue or Input-Queued switch   |

| k       | Crosspoint Queue Size                |

| LB      | Logic Block                          |

| LE      | Logic Element                        |

| LQF     | Longest Queued First                 |

| LQFS    | Longest Queue First Served           |

| LUT     | Look up table                        |

| m       | 1-to-m DEMUX cell                    |

| MUX     | Multiplexer                          |

| MWM     | Maximum Weighted Matching            |

| Ν       | Switch size                          |

| n       | Number of Iterations in iSLIP        |

| NAP-NET | Network Access Processor Network     |

| OCF     | Oldest Cell First                    |

| OP      | Output Port                          |

| OQ      | Output Queue or Output-Queued switch |

| PDSS    | Profile Driven Synthesis System      |

| PFA     | Power Factor Approximation           |

| PIM     | Parallel Iterative Matching          |

| QoS     | Quality of Service                   |

| RR      | Round Robin scheduling               |

| RTL     | Register-Transfer Level              |

| RTT     | Long Round-Trip Time                 |

| S       | Speedup factor                       |

| SAR     | Segmentation and Reassembly          |

| SoC     | System-on-a-Chip                     |

| Т       | Time Interval                        |

| Tbps    | Terabits per second                  |

|         |                                      |

| TDM   | Time Division Multiplexer                    |

|-------|----------------------------------------------|

| U     | Unbalanced probability                       |

| VHDL  | VHSIC Hardware Description Language          |

| VHSIC | Very High Speed Integrated Circuits          |

| VLSI  | Very-Large-Scale Integration                 |

| VOQ   | Virtual Output Queue                         |

| w     | Data path width                              |

| WRR   | Weighted Round-Robin                         |

| XP    | Crosspoint                                   |

| XQ    | Crosspoint Queue or Crosspoint-Queued Switch |

# **Table of Contents**

| ABSTRACT                                                                                                                                                                                                                                         | III                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                 | V                          |

| NOTATION AND ABBREVIATION                                                                                                                                                                                                                        | VII                        |

| CHAPTER 1 INTRODUCTION                                                                                                                                                                                                                           | 1                          |

| <ul> <li>1.1 Background</li> <li>1.2 Research Motivation and Objective</li> <li>1.3 Contributions</li> <li>1.4 Thesis Organization</li> </ul>                                                                                                    | 4                          |

| CHAPTER 2 LITERATURE REVIEW                                                                                                                                                                                                                      | 7                          |

| <ul> <li>2.1 INTRODUCTION</li> <li>2.2 UNBUFFERED CROSSBAR SWITCHES: OQ AND IQ SWITCHES</li> <li>2.3 HISTORY</li> <li>2.4 DESIGN AND IMPLEMENTATION</li></ul>                                                                                    | 7<br>11<br>14              |

| <ul> <li>2.6 POWER ANALYSIS</li></ul>                                                                                                                                                                                                            | 20<br>22<br>28<br>33       |

| CHAPTER 3 PERFORMANCE EVALUATION                                                                                                                                                                                                                 | 38                         |

| <ul> <li>3.1 INTRODUCTION</li></ul>                                                                                                                                                                                                              | 39<br>41<br>42<br>43       |

| <ul> <li>3.4 TRAFFIC MODEL</li> <li>3.4.1 Bernoulli Arrivals</li> <li>3.4.2 Uniform Traffic</li> <li>3.4.3 Unbalanced Traffic</li> <li>3.4.4 Log-diagonal Traffic</li> <li>3.5 SIMULATION METHODOLOGY</li> <li>3.6 SIMULATION RESULTS</li> </ul> | 44<br>45<br>45<br>46<br>46 |

| 3.6.1 Uniform Traffic and Log-diagonal Traffic<br>3.6.2 Unbalance Traffic                                                                                                                                                                        | 49                         |

| 3.8 CONCLUSIONS                               | 53  |

|-----------------------------------------------|-----|

| CHAPTER 4 DESIGN AND IMPLEMENTATION           | 55  |

| 4.1 Introduction                              | 55  |

| 4.2 Design Features                           |     |

| 4.3 Overview of Switch Designs                | 57  |

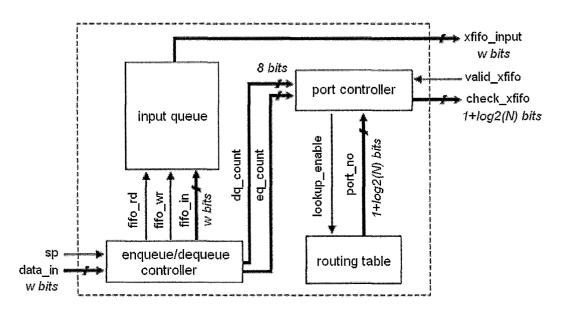

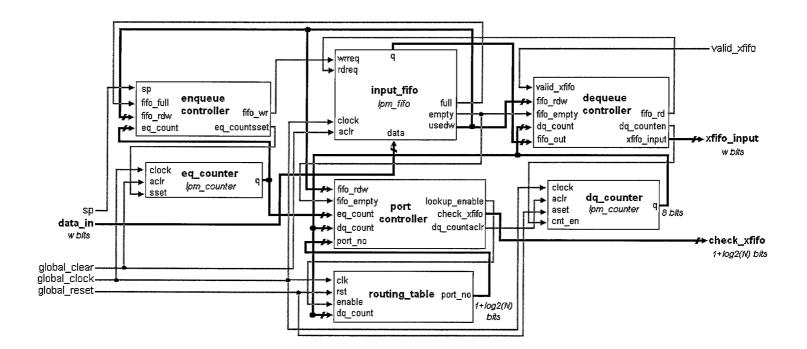

| 4.4 Input Port Design                         | 61  |

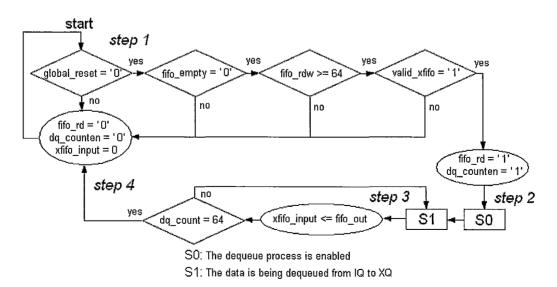

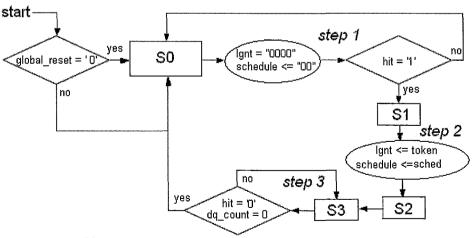

| 4.4.1 Enqueue controller state machine        | 64  |

| 4.4.2 Port controller state machine           | 65  |

| 4.4.3 Dequeue controller state machine        | 65  |

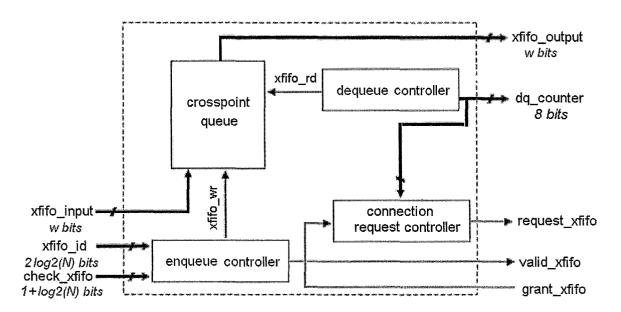

| 4.5 CROSSPOINT QUEUE DESIGN                   | 66  |

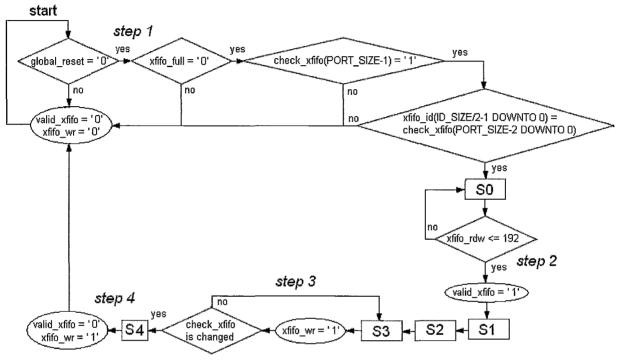

| 4.5.1 Enqueue controller state machine        | 70  |

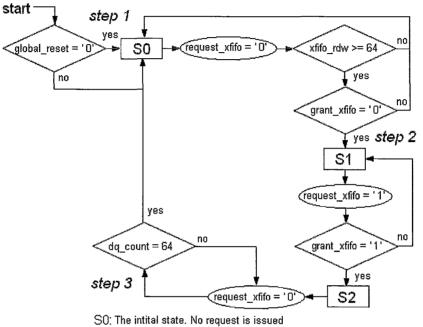

| 4.5.2 Output request controller state machine | 71  |

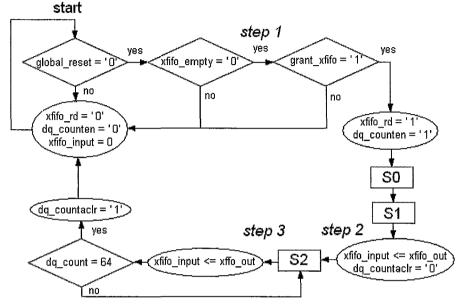

| 4.5.3 Dequeue controller state machine        |     |

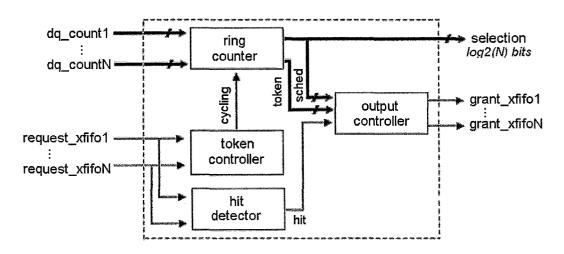

| 4.6 Arbiter Design                            | .72 |

| 4.6.1 A hit detector process                  | 75  |

| 4.6.2 Token controller process                | 75  |

| 4.6.3 A ring counter process                  |     |

| 4.6.2.4 Output controller state machine       | 76  |

| 4.7 INTEGRATION OF THE SWITCH COMPONENTS      | .77 |

| 4.7.1 A Row Connection                        | 78  |

| 4.7.2 A Column Connection                     |     |

| 4.7.3 Integration of the Switch               | .79 |

| 4.8 ACHIEVING 100% THROUGHPUT                 |     |

| 4.8.1 The existence of HOL blocking           | .81 |

| 4.8.2 A TDM Scheme for 100% throughput        | .82 |

| 4.8.3 Implementation of the TDM scheme        |     |

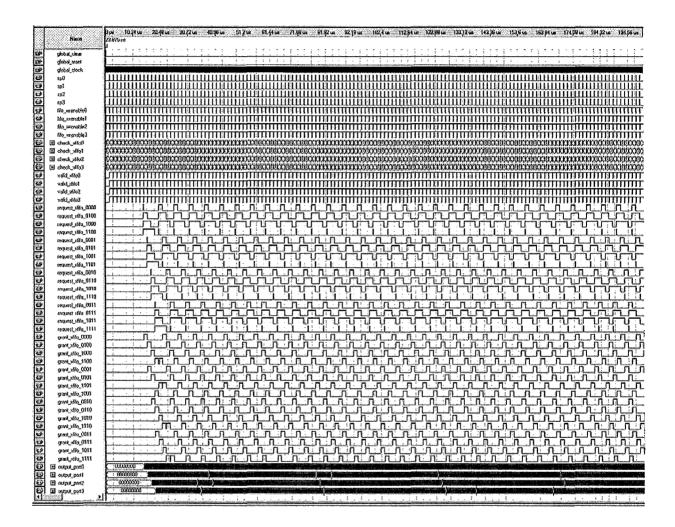

| 4.9 Simulation Results                        | .83 |

| 4.9.1 Simulator                               | .83 |

| 4.9.2 Device                                  | .85 |

| 4.9.3 Discussion                              | .86 |

| CHAPTER 5 POWER MODELS                        | .87 |

| 5.1 Introduction                              | .87 |

| 5.2 Experimental Methodology                  |     |

| 5.2.1 Design Tools                            |     |

| 5.2.2 Assumptions                             |     |

| 5.2.3 Experimental Setup                      |     |

| 5.2.5 Modelling Method                        |     |

| 5.3 Power Models for Basic Components         |     |

| 5.3.1 Demultiplexer Logic Block               |     |

| 5.3.2 Multiplexer Logic Block                 |     |

| 5.3.3 Crosspoint Queue Logic Blocks           |     |

| 5.3.4 Broadcast Busses                        |     |

|                                               |     |

| 5.4 Power Models for IQ and CIXQ Switches<br>5.4.1 Broadcast-and-Select Design |     |

|--------------------------------------------------------------------------------|-----|

| 5.4.2 DEMUX-MUX Design                                                         |     |

| 5.5 VERIFICATION AND DISCUSSION                                                |     |

| CHAPTER 6 CONCLUSIONS                                                          | 113 |

| 6.1.1 Performance                                                              | 115 |

| 6.1.2 Implementation                                                           |     |

| 6.1.3 Power Dissipation                                                        |     |

| 6.2 FUTURE WORK                                                                | 120 |

| 6.3 FINAL CONCLUSION                                                           | 122 |

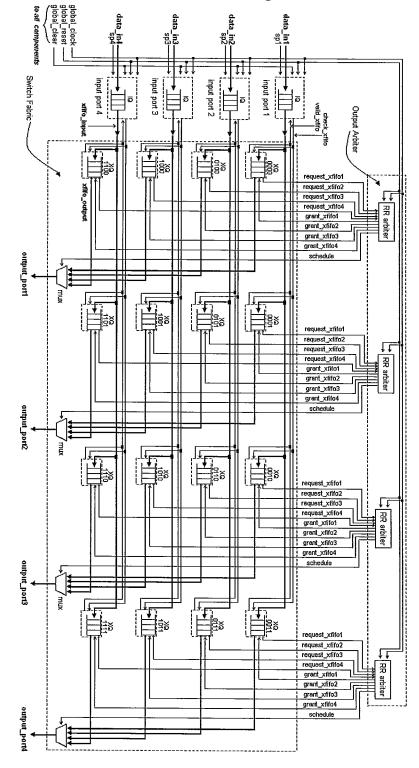

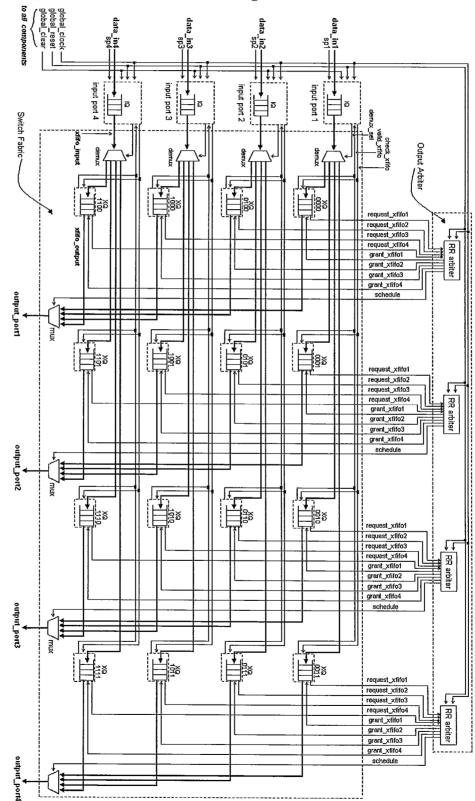

| APPENDIX A: HIGH-LEVEL SCHEMATIC OF CIXQ SWITCH                                | 123 |

| A.1: A CIXQ Switch in Broadcast-and-Select Design                              | 123 |

| A.2: A CIXQ SWITCH IN DEMUX-MUX DESIGN                                         |     |

| APPENDIX B HIGH-LEVEL SCHEMATIC OF AN INPUT PORT                               | 125 |

| APPENDIX C: HIGH-LEVEL SCHEMATIC OF A CROSSPOINT QUEUE.                        | 126 |

| APPENDIX D: HIGH-LEVEL SCHEMATIC OF A RR ARBITER                               | 127 |

| APPENDIX E: DESIGN STATE DIAGRAMS                                              |     |

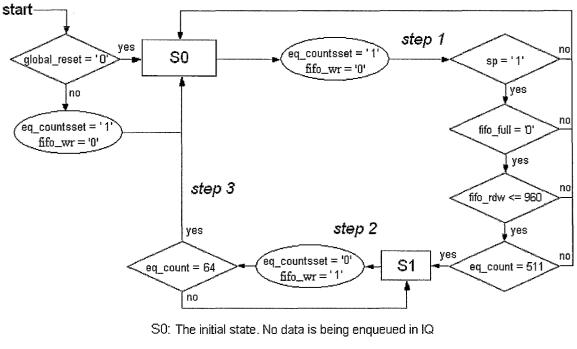

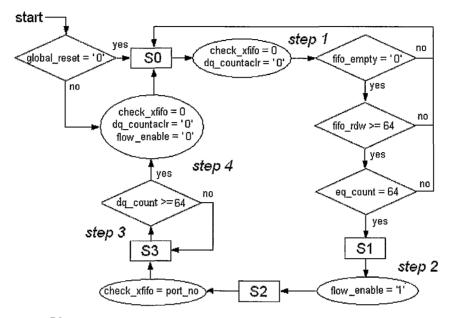

| E.1: ENQUEUE CONTROLLER STATE MACHINE FOR INPUT PORT                           | 128 |

| E.2: PORT CONTROLLER STATE MACHINE FOR INPUT PORT                              |     |

| E.3: DEQUEUE CONTROLLER STATE MACHINE FOR INPUT PORT                           |     |

| E.4: ENQUEUE CONTROLLER STATE MACHINE FOR XQ                                   |     |

| E.5: OUTPUT REQUEST CONTROLLER STATE MACHINE FOR XQ                            |     |

| E.6: DEQUEUE CONTROLLER STATE MACHINE FOR XQ                                   |     |

| E.7: STATE DIAGRAM FOR SCHEDULER                                               | 132 |

| APPENDIX G: SIMULATION RESULT OF 4X4 CIXQ SWITCH                               |     |

|                                                                                | 133 |

# **Table of Figures**

| FIGURE 1.1: Rearch focus of CIXQ switches          | 2 |

|----------------------------------------------------|---|

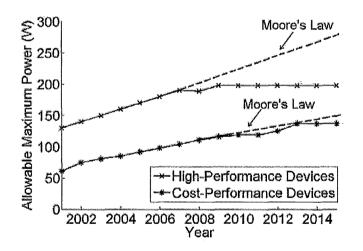

| FIGURE 1.2: Power density trends of microprocessor | 3 |

| FIGURE 2.1: An OQ switch with speedup N                                 | 8  |

|-------------------------------------------------------------------------|----|

| FIGURE 2.2: Input-queued crossbar switch with VOQs                      |    |

| FIGURE 2.3: Crosspoint-queued crossbar switch with VOQs                 |    |

| FIGURE 2.4: Generic Switch Architecture                                 | 14 |

| FIGURE 2.5: Transmission paths in (a) IQ switches and (b) CIXQ switches | 18 |

| FIGURE 2.6: Power dissipation in an inverter                            | 21 |

| FIGURE 2.7: An overview of power analysis techniques                    | 23 |

| FIGURE 2.8: Power estimation flow in CAD tools                          | 31 |

| FIGURE 2.9: Power estimation tools                                      | 32 |

| FIGURE 2.10: The research distribution about CIXQ switches              | 37 |

| FIGURE 3.1: A RR/RR CIXQ-k switch                                                 | 40   |

|-----------------------------------------------------------------------------------|------|

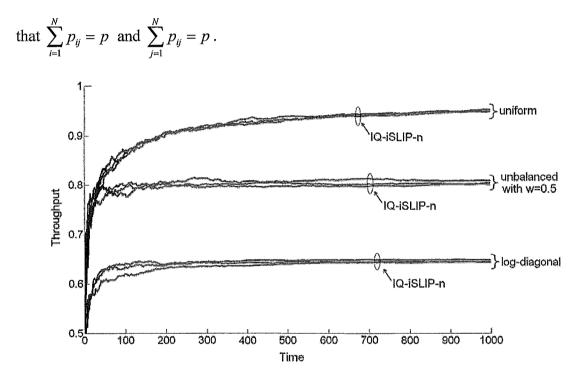

| FIGURE 3.2: Transient throughput performance of IQ switch with n iterations of is | SLIP |

| under various traffic patterns, where $n = 4, 8$ , and 16                         | 46   |

| FIGURE 3.3: MATLAB Code for moving cells from input to XQ                         | 47   |

| FIGURE 3.4: MATLAB Code for moving cells from XQ to output                        | 48   |

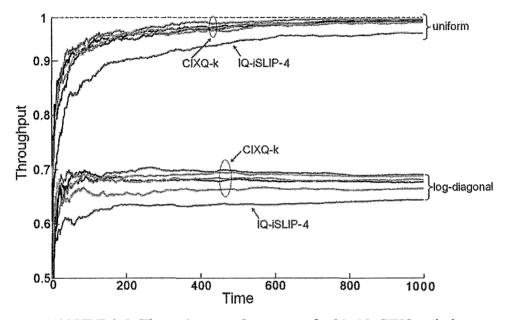

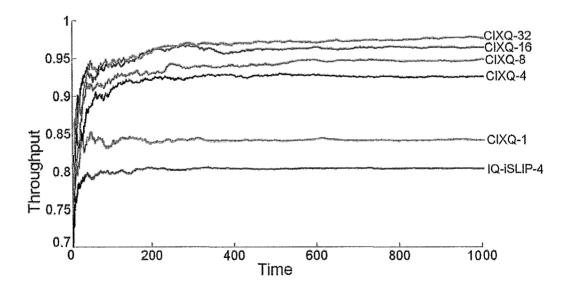

| FIGURE 3.5: Throughput performance of a 32x32 CIXQ switch                         | 49   |

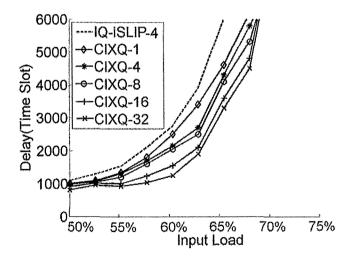

| FIGURE 3.6: Delay performance under log-diagonal traffic                          | 50   |

| FIGURE 3.7: Throughput performance under unbalanced traffic when $u = 0.5$        | 51   |

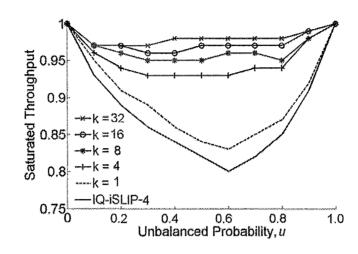

| FIGURE 3.8: Throughput of CIXQ-k under unbalanced traffic, N=32                   | 52   |

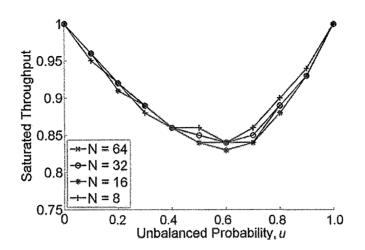

| FIGURE 3.9: Throughput of CIXQ-1 under unbalanced traffic                         |      |

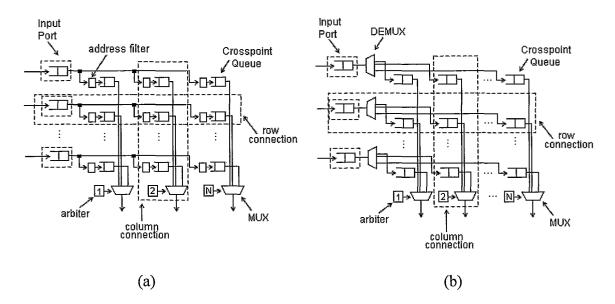

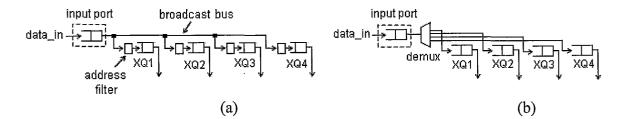

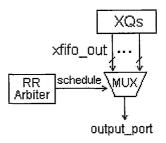

| FIGURE 4.1: (a) Switch architecture overview; (b) broadcast-and-select design; | 57 |

|--------------------------------------------------------------------------------|----|

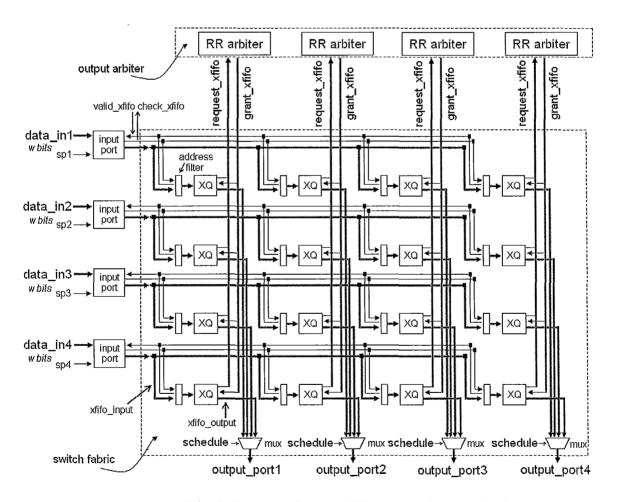

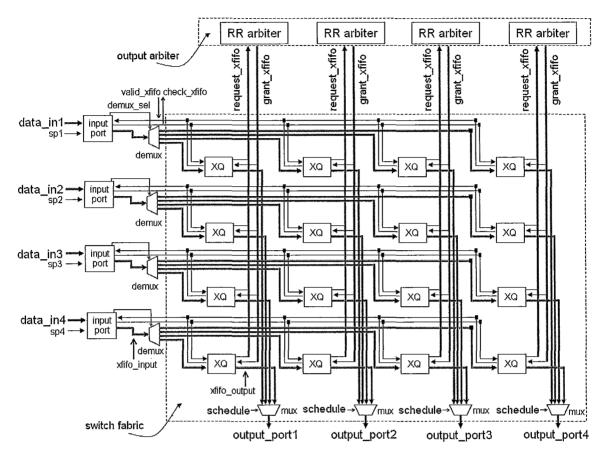

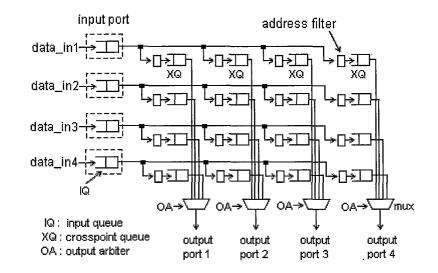

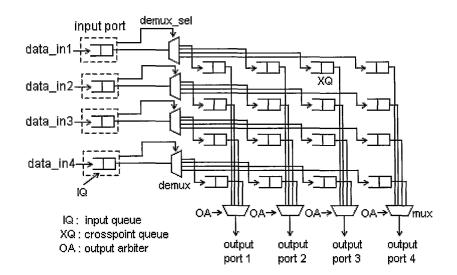

| FIGURE 4.2: Block diagram of a 4x4 CIXQ switch in B&S design                   | 58 |

| FIGURE 4.3: Block diagram of a 4x4 CIXQ switch in DEMUX-MUX design             | 59 |

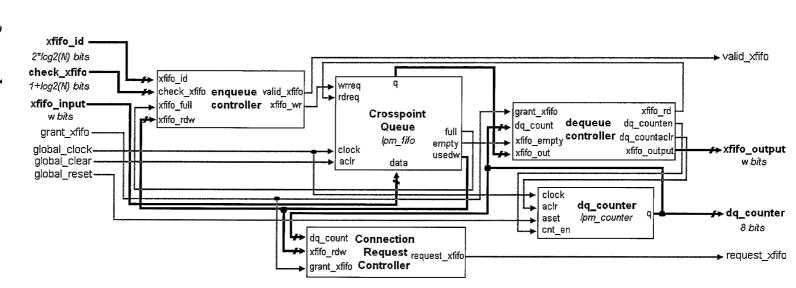

| FIGURE 4.4: Input port architecture for an NxN CIXQ switch                     | 61 |

| FIGURE 4.5: The inputs and outputs of a crosspoint queue design                | 66 |

| FIGURE 4.6: A XQ in 4x4 CIXQ switch                                            | 67 |

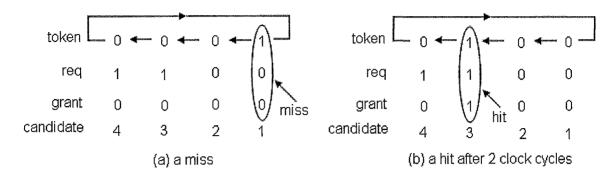

| FIGURE 4.7: A hit and a miss in a round-robin arbiter                          | 73 |

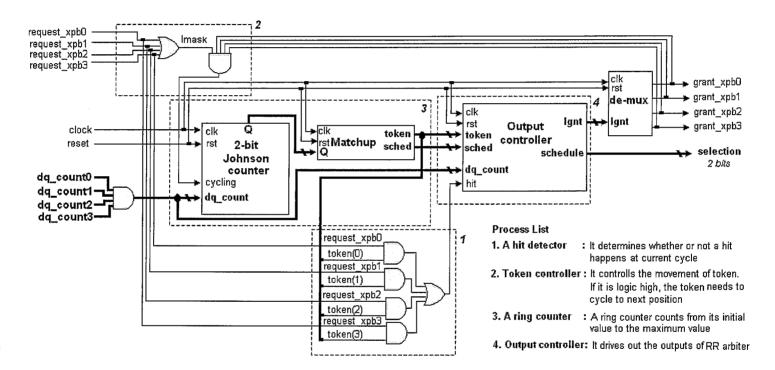

| FIGURE 4.8: Block diagram of a round-robin arbiter                             | 74 |

| FIGURE 4.9: A row connection and a column connection of the CIXQ switch in     | 78 |

| FIGURE 4.10: Block diagram of a row connection in                              | 79 |

| FIGURE 4.11: A column connection in a 4x4 CIXQ switch                          | 79 |

| FIGURE 4.12: A full body of 4x4 CIXQ switch in the broadcast-and-select design | 80 |

| FIGURE 4.13: A full body of 4x4 CIXQ switch in the DEMUX-MUX design | 80 |

|---------------------------------------------------------------------|----|

| FIGURE 4.14: HOL blocking in a CIXQ switch without VOQs             | 81 |

| FIGURE 4.15: Detail schematic of a routing table                    |    |

| FIGURE 4.16: Quartus II simulation flow                             | 84 |

| FIGURE 4.17: A logic element in FPGA                                |    |

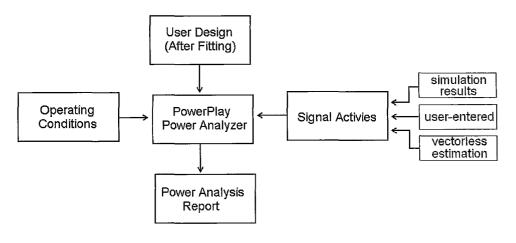

| FIGURE 5.1: PowerPlay power analysis flow                                   | 89      |

|-----------------------------------------------------------------------------|---------|

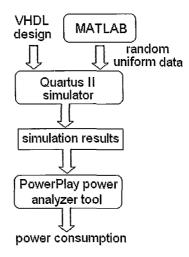

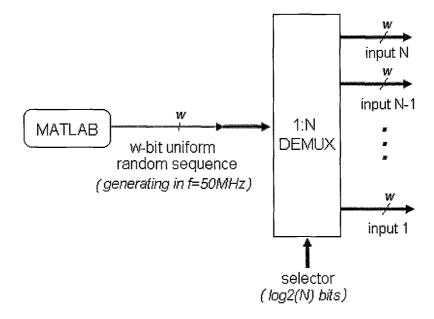

| FIGURE 5.2: Power measurement flow                                          | 91      |

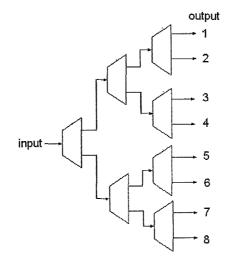

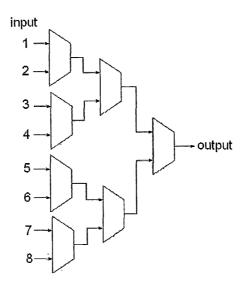

| FIGURE 5.3: An example of 1-to-8 DEMUX                                      | 94      |

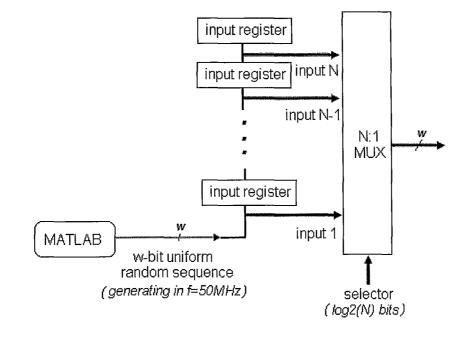

| FIGURE 5.4: Testing circuit for DEMUX power                                 | 95      |

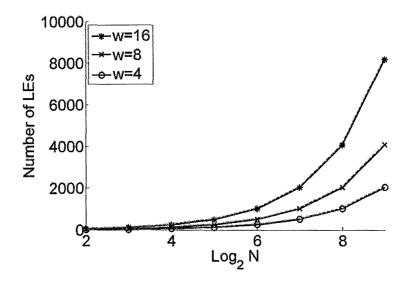

| FIGURE 5.5: The number of LEs used in 1-to-N DEMUX                          | 96      |

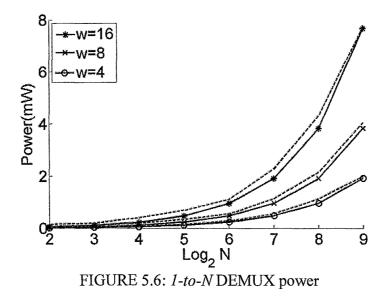

| FIGURE 5.6: 1-to-N DEMUX power                                              | 96      |

| FIGURE 5.7: An example of 8-to-1 MUX                                        | 97      |

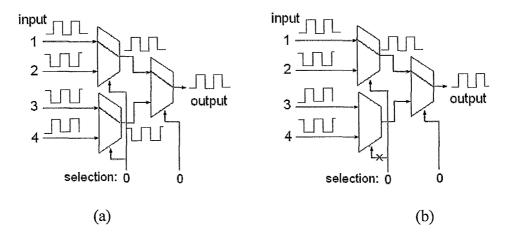

| FIGURE 5.8: Power in 4-to-1 MUX: (a) full power mode; (b) low power mode    | 98      |

| FIGURE 5.9: Testing circuit for MUX power                                   | 99      |

| FIGURE 5.10: The number of LEs used in N-to-1 MUX                           | 100     |

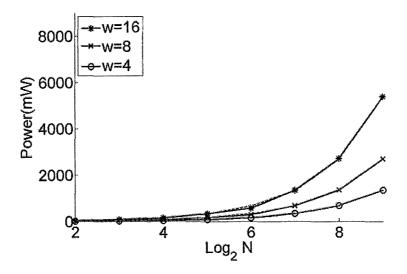

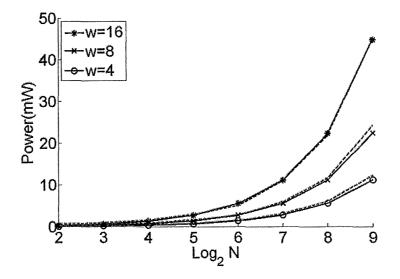

| FIGURE 5.11: N-to-1 MUX power in full power model                           | 100     |

| FIGURE 5.12: N-to-1 MUX in low power model                                  | 101     |

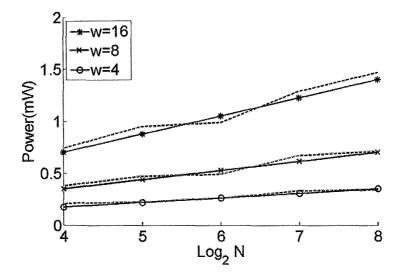

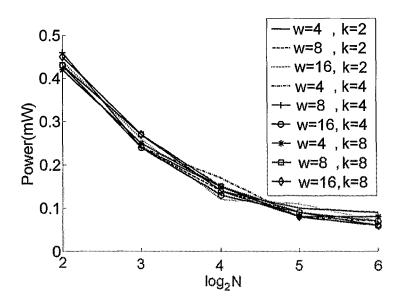

| FIGURE 5.13: Power consumption of a single crosspoint queue in NxN CIXQ-k s | witches |

| with various datapath widths                                                | 104     |

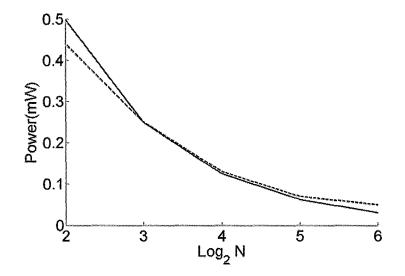

| FIGURE 5.14: Power consumption of a single crosspoint queue in NxN switches | 105     |

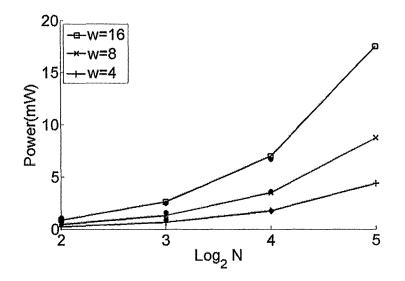

| FIGURE 5.15: A broadcast bus power in NxN switches                          | 107     |

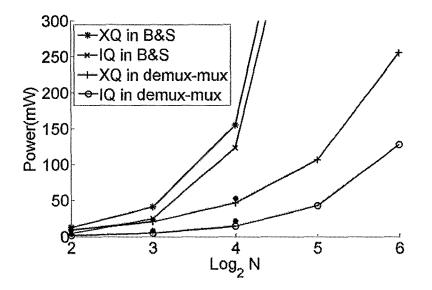

| FIGURE 5.16: Power consumption of IQ and CIXQ switches                      | 110     |

|                                                                             |         |

# List of Tables

| Table 4. 1: Truth table of a Johnson counter                            | .76 |

|-------------------------------------------------------------------------|-----|

| Table 4.2: Device Resources of Cyclone II FPGAs                         | .85 |

| Table 4.3 Summary of resource usage for $CIXQ$ switch with $w = 4$ bits | .85 |

| Table 5.1: Power Factors for the basic components                        |  |

|--------------------------------------------------------------------------|--|

| Table 5.2: Estimation Error in 1-to-N DEMUX Power                        |  |

| Table 5.3: Estimation Error of <i>N-to-1 MUX</i> Power in Low Power Mode |  |

| Table 5.4: Estimation Error of a FIFO Power in NxN Switches              |  |

| Table 5.5: Power comparison between IQ and CIXQ switches                 |  |

| Table 6.1: Possible implementations of NxN CIXQ-k switch in Cyclone II FPGAs   | 117  |

|--------------------------------------------------------------------------------|------|

| Table 6.2: Device Resources of Stratix III FPGAs                               | 117  |

| Table 6.3: Possible implementations of NxN CIXQ-k switch in Stratix III FPGAs  | 117  |

| Table 6.4: DC and switching characteristic of Statrix III EP3SL340             | 118  |

| Table 6.5: Sample Power Evaluation for an implementation of 16x16 CIXQ-k switc | h in |

| Statrix III EP3SL340 device                                                    | 119  |

### **Chapter 1 Introduction**

### **1.1 Background**

Crossbar switches have been widely used in packet switching networks due to their internally non-blocking capability and the ability to support multicast. Queues are use to resolve the contention that remains in the crossbar switches [1]. In general, the crossbar switches are categorized into three classes based on the location of queueing functions. They are Input-Queued (IQ) switches, Output-Queued (OQ) switches and Crosspoint-Queued (XQ) switches with a queueing function at the input port (IP), output port (OP) and crosspoint (XP), respectively.

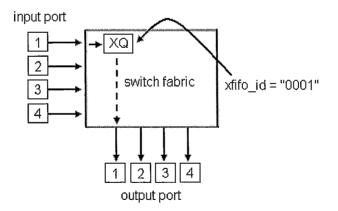

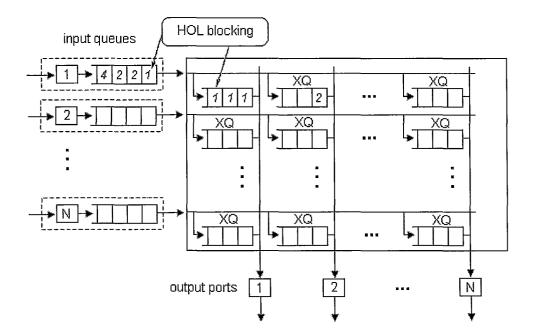

OQ switches with speedup N are the ideal packet switching architecture for providing *Quality of Service (QoS)* guarantees [2]. However, the implementation is not scalable due to the required speedup. IQ switches place a queueing function at each input port to overcome the scalability problem. Many papers prove that IQ switches with appropriate scheduling algorithms can achieve 100% throughput [7, 8, 9, 10, 11, 12]. While IQ switches are used in commercial routers, the schedulers are relatively complex. XQ switches with making a *First-In-First-Out* (FIFO) queue in each crosspoint have been introduced to simplify the scheduling since they can schedule the packets at the input and outputs independently and in parallel. A special version of XQ switches that combines crosspoint queueing and input qeueueing, denoted as *CIXQ*, has recently been proposed to lower the memory required in the crossbar and maximize throughput [19].

FIGURE 1.1: Rearch focus of CIXQ switches

*CIXQ* switches have been the subject of considerable research over the last decade. The research focus in *CIXQ* switches lies in three areas: the performance, design feasibility and power consumption (see FIGURE 1.1). The majority of the literature is focused on the performance in terms of throughput and delay. The simulations results in [19, 20, 21, 22, 23, 24, 25, 26] indicate *CIXQ* switches exhibit a marginally lower delay than *IQ* switches while providing a comparably high throughput. These studies claim that *CIXQ* switches with less complex scheduling have great potential to complement or even replace *IQ* switches in the future high-speed networks.

Unfortunately, the technology to build *CIXQ* switches appears to be an obstacle because it is difficult and expensive to deploy a queue in each crosspoint. *CIXQ* switches were only considered theoretical architectures before the *Complementary Metal-Oxide Semiconductor* (CMOS) technology allowed the integration of a large amount of memory inside a single chip [19]. The advancement of CMOS technology significantly reduces the cost associated with the development and construction of a buffered crossbar. Recently, a number of groups have analyzed the feasibility of building *CIXQ* switches on a CMOS *Very-Large-Scale Integration* (VLSI) chip, such as *System-on-a-Chip* (SoC), *Application Specific Integrated Circuit* (ASIC) or *Field Programmable Gate Array* (FPGA). The analysis in [68, 70] reveal that the *CIXQ* switch architectures are feasible, and should be available for use in the switching networks.

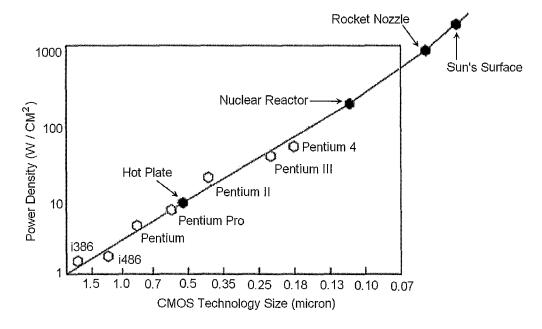

FIGURE 1.2: Power density trends of microprocessor

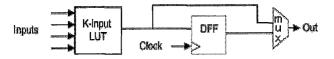

Power has become a first-class design constraint in the digital circuits, especially in the CMOS VLSI circuits [3]. The power dissipation rises exponentially while the CMOS technology continues to use smaller manufacturing process. The microprocessor is a VLSI device. FIGURE 1.2 depicts the power density trends of the Pentium microprocessor versus the transistor size [4]. The Pentium 4 has a power density of about  $50 W/cm^2$ , which is seven times more than the Intel 486. The trend cannot continue because it is not practical to remove heat from a chip built using the 0.10-micron process with current design methods. Although it is crucial to develop techniques to reduce the power consumption, it is also essential to have power estimation tools to explore the power efficiency when the circuit designers make architecture trade-offs in the early design stages. Today, many semiconductor vendors have embedded power estimators in the *Computer-Aid Design* (CAD) tools, for example, Xilinx's *Xpower* [55] and Altera's *PowerPlay* [57].

As *CIXQ* switches are feasible to implement in a CMOS VLSI circuit, the question of whether they will have a power consumption problem becomes a very important concern. Excessive power consumption will not only limit the use of *CIXQ* switches, but will also degrade the performance due to overheating. A sophisticated power analysis tool needs to be developed for investigating the *CIXQ* switches. Accordingly, the designers can determine how well the devices meet the power specifications without a costly redesign process. Recently, researchers have focused on this goal, but only a limited number of publications are available. To our best knowledge, D. G. Simos [70] was the first person to measure the power consumption of an ASIC implementation of *CIXQ* switch. To date, no power model has been developed for any *CIXQ* switch. This is a major contribution made by this thesis.

### **1.2 Research Motivation and Objective**

The purpose of this thesis is to analyze the power consumption of *CIXQ* switches using current CMOS technology. The performance of *CIXQ* switches will be studied using

MATLAB under various traffic conditions. Different hardware architectures of *CIXQ* switches are also created and analyzed in FPGA environment. In particular, we wish to study the power consumption of *CIXQ* switches realized in an FPGA. Analytical models are developed to estimate the power of the designs at Register-Transfer Level (RTL). To verify the analytical models, the actual power of several switches is measured by Altera<sup>TM</sup> *PowerPlay* power tool. The models should be accurate and flexible to explore the power in the early stage of design process.

#### **1.3 Contributions**

The contributions of this thesis are summarized as follows:

- 1. A preliminary performance evaluation of *CIXQ* switches using MATLAB. The experiments indicate that the *CIXQ* switch with round robin arbitration has marginally better performance than an *IQ* switch with iSLIP, which is consistent to the discussions in [21, 22]. However, no thorough study of scheduling algorithm was undertaken, and no conclusion should be drawn from these simulations. A thorough study of scheduling algorithms is beyond the scope of this thesis.

- 2. A VHDL implementation of *CIXQ* switches employing the Broadcast-and-Select architecture and DEMUX-MUX architecture are described. The simulation results show the designs are functional properly as described in this thesis.

× .

- 3. Analytic power models for the *CIXQ* switch in an FPGA environment are developed and have been published at the 22<sup>nd</sup> Canada Conference on Electrical and Computer Engineering [5]. To the best of our knowledge, no power model for the *CIXQ* switch has been made prior to our work.

- 4. The power models are accurate with an average error of about 10%. They can allow the designers to check the power efficiency of different implementations and make architectural design decisions early in the design process, without actually going through chip fabrication.

### **1.4 Thesis Organization**

The rest of the thesis is organized as follows. Chapter 2 provides a literature review of CIXQ switches considering the switching performance, design implementation and power consumption. It also reviews the unbuffered crossbar switches, which include *Input-Queued* (*IQ*) switches and *Output-Queued* (*OQ*) switches. Chapter 3 presents a preliminary performance evaluation of the CIXQ switch using Round Robin (RR) arbitration in comparison of the *IQ* switch using the iSLIP scheduler. Chapter 4 describes a VHDL implementation of the *CIXQ* switch using Altera Cyclone II FPGAs. Chapter 5 proposes the analytical power models for *IQ* and *CIXQ* switches. Finally, Chapter 6 draws the conclusion of the thesis and presents possible direction of the future research.

### **Chapter 2 Literature Review**

### **2.1 Introduction**

The Combined Input- and Crosspint-Queued (CIXQ) switches simplify the scheduling by adding  $N^2$  crosspoint queues to the basic crossbar switch. Their performance, implementation and power consumption have recently captured the interest of many researchers. In this chapter, we present a review of CIXQ switches in the literature. The chapter is organized as follows: first we review the traditional Input-Queued (IQ) switch as well as the Output-Queued (OQ) switch. Next, we describe the history and development of the CIXQ switch followed by a discussion about its implementation using current CMOS technology. Then, we discuss the advantages and disadvantages of having  $N^2$  crosspoint queues in CIXQ switches. We also provide a survey about the techniques and CAD tools for estimating the power consumption of CMOS VLSI designs; we particularly review the publications that have been done so far to analyze the power consumption of crossbar switches. Finally, we present a summary about the research focus of CIXQ switches.

#### 2.2 Unbuffered Crossbar Switches: OQ and IQ Switches

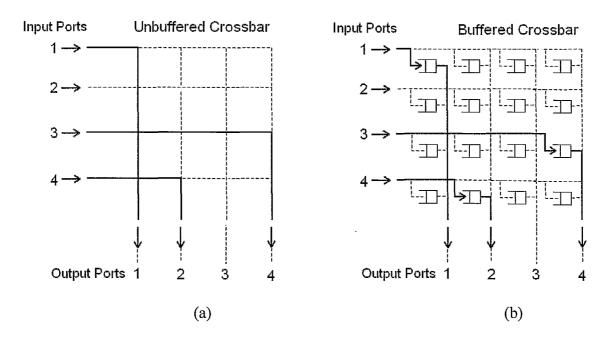

Before Bakka and Dieudonne [13] proposed the idea of employing a FIFO queue in each crosspoint, *OQ* and *IQ* switches were the two main crossbar switch designs discussed in

the literature. In an OQ switch, each output port maintains a queue to store the incoming packets. This architecture requires an internal bandwidth or speedup that is equal to the number of ports (S = N), i.e. an NxN OQ switch is able to move up to N packets from Ninputs to a single output port in one packet time slot (see FIGURE 2.1). S is defined as the speedup factor. The speedup requirement not only limits the scalability of OQ switches but also makes them too expensive to build for large N. Consequently, OQ switches are not practical for packet switching network.

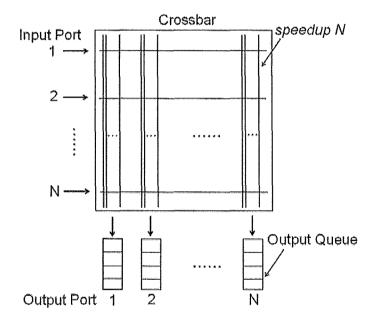

FIGURE 2.1: An OQ switch with speedup N

*IQ* switches overcome the scalability problem by having a queueing function at each input port. In fact, they are dominant in high speed switching. The performance of *IQ* switches depends very much on the use of the input queues. If a FIFO queue is applied at each input port, the throughput is limited to about 58.6% due to the *Head of Line* (HOL) blocking problem for the random uniform traffic with *independent and identical*

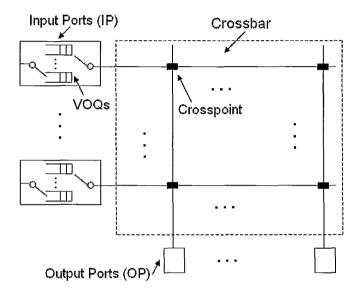

*distribution* (i.i.d) [6]. In fact, the HOL blocking can be eliminated entirely using a scheme of *Virtual Output Queues* (VOQs) in which each input port maintains a separate queue for each output. It has been shown that the throughput of an *IQ* switch with VOQs can be increased up to 100% [10]. The block diagram of an *NxN IQ* switch with *N* VOQs at the input side is illustrated in FIGURE 2.2.

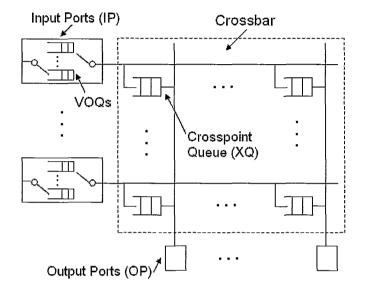

FIGURE 2.2: Input-queued crossbar switch with VOQs

In an NxN IQ switch, the packets are typically fragmented into fixed-size cells at the input side. The cells are transmitted through the switch while attempting to meet *Quality of Service* (QoS) constraints. A scheduling algorithm is required to direct the transmission of cells from the input side to output side. According to [7, 8, 9, 10], scheduling in IQ switches is a difficult problem. In each cell time slot, the scheduler must identify up to N cells to transmit through the switch, while simultaneously meeting three constraints: 1) no input port transmits more than one cell per time-slot, 2) no output port receives more than one cell per time-slot, and 3) each traffic flow receives relatively fair service.

The scheduling in an IQ switch can be formulated a *Bipartite Graph Matching* problem [7]. During each time slot, a scheduling algorithm determines the transmission of cells through the switch by finding a matching on a bipartite graph. It has been established that the *Maximum Weighted Matching (MWM)* algorithm can provide 100% throughput in IQ switches with unity speedup for all admissible i.i.d arrivals [10]. However, the complexity of such algorithms renders them impractical. Given a line rate of 40 Gbps and a cell size of 64 bytes, the time-slot duration is 12.8 nanoseconds. The time complexity of MWM algorithm is  $O(N^3)$ . This requirement renders MWM far too computationally complex for current IP switches or routers. A number of algorithms have been proposed to approximate the performance of MWM, for example, *Parallel Iterative Matching* (PIM) [9], iSLIP [7] and *Dual Round-Robin Matching* (DRRM) [8]. These historic scheduling algorithms do not have as good performance as MWM.

The recent theoretical result [11, 12] shows that IQ switches with a speedup of S (where S is the speedup factor) can achieve optimal performance as OQ switches. These switch designs can remove up to S cells from each input and move up to S cells to each output in a cell time slot. They are generally called Combined Input and Output Queued (*CIOQ*) switches because a queue is required at each output port. S. T. Chuang *et al.* [11] and I. Stocia *et al.* [12] both stated that a *CIOQ* switch with a speedup of two (S = 2) can exactly emulate an OQ switch. The scheduling problem remains complicated, and the use of CIOQ switches is thus discouraged in the packet switching networks.

### 2.3 History

The switches with a FIFO queue in each crosspoint have been proposed to simplify the scheduling problem. Prior to discussing the design difficulties of *CIXQ* switches, it is important to understand how they were developed. The idea of inserting a queue at each crosspoint of a crossbar switch was first introduced by Bakka and Dieudonne [13] in 1982, and these switch architectures are called Crosspoint-Queued (*XQ*) switches. Nojimma *et al.* [14] were the first to study the performance of *XQ* switches in packet switching networks. In 1987, they implemented a *Bus Matrix* (BMX) switch, where the crosspoint queues were made from dual-port memories allowing asynchronous and individual operation at input and output ports. The performance of BMX switch was evaluated under the *Network Access Processor Network* (NAP-NET). The end-to-end delay of voice packets was measured in the experiments. The voice delay was less than 20 ms for the 64-byte packets after five-hop transmission. The experimental results demonstrated that the BMX switch had high performance.

The memory required at the crosspoints can be effectively reduced if FIFO queues are employed at the input side of XQ switches [15]. A significant amount of work has been done to investigate the performance of XQ switches with FIFO queues at the input side. A. Gupta *et al.* [16] claimed that a XQ switch could achieve 87.5% throughput for uniform traffic with the effect of *HOL* blocking. The same authors increased the throughput to 91% by proposing a *HOL* priority selection scheme at the input sides [17]. The performance of XQ switches was further studied by R. Fantacci *et al.* [18]. These researchers proved that a random selection scheme at the input side can establish 100% throughput in *XQ* switches for uniform traffic.

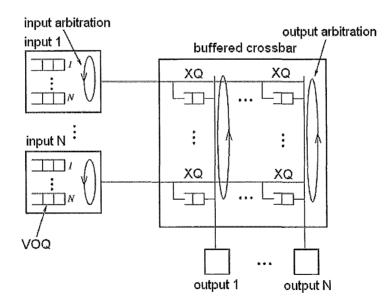

FIGURE 2.3: Crosspoint-queued crossbar switch with VOQs

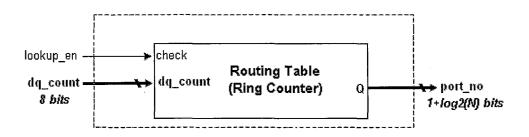

In 2000, switches combining IQ switches with VOQs and XQ switches were first proposed by Nabeshima [19], and he referred to such architectures as *Combined Inputand Crosspoint-Queued switches*, short for *CICQ*. In this thesis, we use the terminology "*CIXQ*" instead. FIGURE 2.3 illustrates a *CIXQ* switch, which differs from an IQ switch by putting a FIFO queue in each crosspoint of the crossbar. *CIXQ* switches entirely eliminate *HOL* blocking with the use of VOQs at the input side. More importantly, they reduced the amount of memory required in the crossbar significantly. Several scheduling algorithms for *CIXQ* switches have been introduced in the past ten years. K. Yoshigoe *et al.* [20] used *Round-Robin* (RR) arbitration at the inputs and outputs of a *CIXQ* switch. The simulation results showed that the *CIXQ* switch obtained a lower queueing delay than an *IQ* switch using the iSLIP scheduler for the fixed-size and variable-size packets. A *CIXQ* switch with one-cell crosspoint queues and RR arbitration at inputs and outputs was proposed by Rojas-Cessa *et al.* [21, 22]. This switch design provides a 100% throughput under uniform traffic, but it has a relatively low performance for non-uniform traffic. Y. Zheng *et al.* [23] then applied a *Dual Round-Robin* (DRR) algorithm to increase the performance of *CIXQ* switches under non-uniform traffic. The *CIXQ* switch with DRR achieved a satisfactory performance under both uniform and non-uniform traffics.

The impact of different scheduling algorithms on the performance of CIXQ switches were analyzed by M. Pejanovic *et al.* [24]. The scheduling algorithms at inputs and outputs of the switch were designed with the combinations of RR, *Longest Queued First* (LQF), and *Oldest Cell First* (OCF). The comparison results demonstrated that the *CIXQ* switches with various scheduling algorithms resulted in almost the same performances under various traffics. The results also implied that RR arbitration is a better solution for scheduling scheme in a *CIXQ* switches can be improved with the use of speedup. L. Mhamdi et al. [25] and R. B. Magill [26] had proved that a *CIXQ* switch with speed up of two can exactly emulate an *OQ* switch.

*CIXQ* switches have a 25 year history. The complexity of constructing buffered crossbars is reduced by maintaining a set of queues at each input port. Moreover, they are proven to obtain high throughput with reasonable delay under uniform and non-uniform traffic according to the studies in [14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26].

13

#### 2.4 Design and Implementation

*CIXQ* switches show promises for future networks because they can simplify the scheduling algorithm. However, the feasibility of implementing  $N^2$  crosspoint queues remains an open question. Although the enhancement of CMOS technology makes the queueing design problem less difficult, the designers still face a lot of challenges in making a buffered crossbar switch.

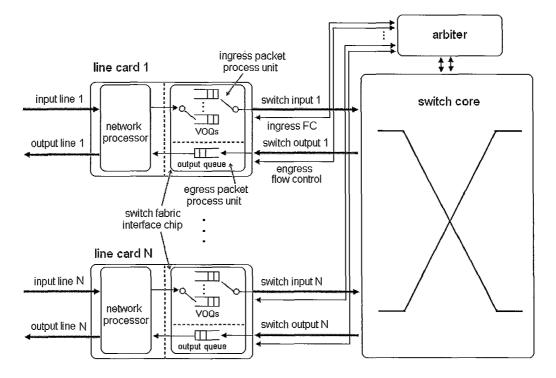

FIGURE 2.4: Generic Switch Architecture

From the hardware perspective, a network switching device normally consists four parts: 1) the ingress packet process unit, 2) the egress packet process unit, 3) the arbitration unit (arbiter), and 4) the switch core. FIGURE 2.4 shows the block diagram of switch/router architecture [27]. Each Input-Output (IO) port with the OQs and VOQs is

typically realized on one line-card, which has several Gigabytes of queueing memory and one or more network processors to manage and schedule the traffic. The crossbar switching functions of IP routers are typically implemented on a separate "switch-core" VLSI substrate [28, 29]. In a large IP router, crossbar switch substrates with capacities of hundreds of Gigabits per second (Gpbs) up to several Terabits per second (Tbps) are required.

A crossbar switch can be made with one or more System-on-a-Chip (SoC) substrates or a large array of parallel Field Programmable Gate Arrays (FPGAs) in a state-of-the-art CMOS process. In the past decade, a number of groups analyzed the feasibility of buffered crossbar switches in silicon SoC and FPGA. Kariniemi *et al.* [30] designed a 4x4 XQ switch with output queueing in FPGA for ATM Cable TV backbone networks. The crossbar and outputs were both buffered using the dual port SRAM. The XQ switch assumes RR arbitration for the crosspoint queueing and Longest Queue First Served (LQFS) scheme for the output queueing. The probability distribution of the occupancy of the buffers was measured, and the experimental results indicated that the XQ switch had a high performance under the ATM networks. Moreover, the performance measurements implied that the FPGA technology could provide sufficient logic and memory capacity for the XQ switch.

An IBM research group presented an ASIC implementation of a single-stage CIXQ switch [27]. The switch core was created to handle an aggregate throughput of 4 Tb/s resulted from multiple OC-192 (10Gb/s) interfaces or OC-768 (40Gb/s) interfaces. RR arbitration is used at the inputs and the *Weighted Round-Robin* (WRR)

algorithm is employed at the outputs. This combination allowed the switch to support up to 8 different *Classes of Service* (CoS). The chip was built in 0.11 micron CMOS process. The standard cell design methodologies, processes and packages were applied to keep the design time short. The testing results showed that the *CIXQ* switch can support cables of up to 100 feet between the line cards and the switch core, without performance degradation under any traffic patterns. This feature removed the effect of *Long Round-Trip Times* (RTT) when the switch was distributed over multiple shelves and racks. The proposed switch was proved to be valid in the CMOS technology under the requirements of a) a die size of up to  $250mm^2$ , b) up to 1000 signal inputs and outputs (totally 1500-pin package), and c) allowable maximum power consumption of 25W.

In 2003, Yoshigoe *et al.* [31] developed a *CIXQ* switch in FPGA. *Round-Robin* (RR) arbitration was used for the input and output ports with a priority encoder based RR poller scheme. The target technology was the Xilinx Virtex II Pro Series. The switch was formed by six line cards, a crossbar and a bus motherboard. The crossbar consisted of four crossbar slices, each of which was connected to the line cards over the bus motherboard. The fully synchronized dual port memory on Virtex II Pro devices, named *BlockRAM*, was configured to implement VOQs and crosspoint queues of the switch. The authors suggested that the off-the-shelf FPGA chips can provide sufficient resources for a *CIXQ* switch with up to 24 ports and 10Gb/s line speed. In addition, they expected that large *CIXQ* switch would become feasible in the future because the next generation of FPGAs presented larger amount of fast I/O circuits and memory resources.

M. Katevenis *et al.* [32] proposed another *CIXQ* switch in CMOS technology. The purpose of their work was to evaluate the performance of *CIXQ* switches operating directly on variable-size packets. A 32x32 *CIXQ* switch with simple RR arbitration at the inputs and outputs was built in a 0.13 micron CMOS process. The input scheduler was realized at each ingress line card to minimize the scheduler latency. The design was synthesized using Synopsys [33] and placed and routed using Silicon Encounter [34]. After the layout and implementation cost of the circuit were analyzed, the authors concluded that a 32x32 *CIXQ* switch with an aggregate capacity of 300Gbps was possible using the modern CMOS technology.

In short, the cost of producing *CIXQ* switches is more affordable as the CMOS technology is continuingly improving. Moreover, this author projects that a large buffered crossbar with hundreds of Gigabit or even Terabit line rate would be buildable in the future.

### 2.5 Advantages and Disadvantages

The *CIXQ* switches are configured with a FIFO queue in each crosspoint of the crossbar. Many studies have pointed out that *CIXQ* switches provide good performance in highspeed networks. According to [27, 28, 29, 30, 31, 32], the future CMOS technology should come with enough logic resources to build the buffered crossbar. These features suggest that *CIXQ* switches have great potential to be applied in future networks.

Considering the previous, traditional *IQ* switches, *CIXQ* switches have significant advantages as following:

The scheduling is simplified. FIGURE 2.5 depicts the transmission paths in the IQ and CIXQ switch. An IQ switch transmits data only if a connection between the input port and output port is established. The input and output matching depend on each other since each input can only be paired to a single output and vise versa. Instead, the CIXQ switch has two independent paths to move data through the switch: (1) data is forwarded from input port to crssspoint queue; and (2) data is transferred from corsspoint queues to output ports. Thus, no exchange of flow control information between the input and output scheduler is needed, therefore, simplifying the scheduling algorithm.

FIGURE 2.5: Transmission paths in (a) IQ switches and (b) CIXQ switches

2. Variable-size packets are supported [33, 35]. In an *IQ* switches, the variable-size packets must be first segmented into fixed-size cells at the input side, and then reassembled at the output side. But the *Segmentation and Reassembly* (SAR)

circuits increase the design difficulty and switching delay. The CIXQ switch can forward the variable-size packets without SAR processing at the expense of long queues required at the  $N^2$  crosspoints.

For the disadvantages of having a FIFO in each crosspoint, they can be listed as following:

- 1. The design complexity is increased. *CIXQ* switches can simplify the scheduling at the expense of maintaining  $N^2$  crosspoint queues in the crossbar. The memory required in the crosspoint queues is proportional to the square of the number of ports (O( $N^2$ )). Therefore, it is expensive and difficult to build a large *CIXQ* switch.

- 2. The *CIXQ* switch must maintain a large crosspoint queue to support the variablesize packets. While *CIXQ* operates directly on the variable-sized packets, the crosspoint queue needs to be large enough to store the largest size packets on the networks.

# 2.6 Power Analysis

Power Consumption posses a major problem in VLSI design. This section provides a survey about the power estimation techniques and CAD tools for the CMOS VLSI designs as well as a review of power study for crossbar switches.

#### 2.6.1 Power Consumption in CMOS circuits

It is important to understand how CMOS circuits consume power when performing a power analysis. The total power dissipation in a CMOS circuit is generally comprised of three major components:

- (1) Static power: the power due to leakage current when the circuit is idle. Thus, it is sometimes called leakage power. The amount of leakage current varies with die size, junction temperature, and process variations [36].

- (2) Dynamic power: the power required for charging and discharging the load capacitance during signal transitions (when the circuit is switching). The main factors affecting dynamic power are load capacitance, supply voltage, and clock frequency [36].

- (3) Short-circuit power: the power due to short-circuit current during switching of transistors.

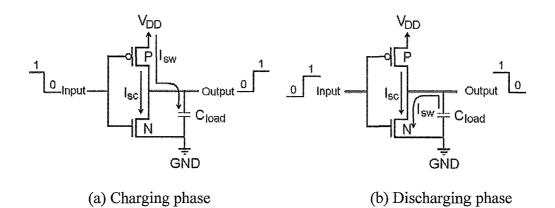

The power dissipation in a CMOS circuit is illustrated in FIGURE 2.6 [37] through the example of a CMOS inverter during a signal transition. The load capacitor  $C_{load}$  represents the sum of parasitic capacitance of the nMOS and pMOS transistors, the capacitance associated with internal and external wires of the inverter cell, and the input capacitance of the circuits driven by the inverter. Assuming the circuit is initially in a steady state, when an input signal changes from high to low, i.e. a zero voltage is applied at the input, the P-type transistor turns on and the N-type transistor turns off. The load capacitor is charged up due to the switching current  $(I_{SW})$  flowing from the P-type

Jian Wang

transistor to ground, as it is depicted in FIGURE 2.6 (a). During this charging phase, the energy drawn from power supply is  $C_{load} \cdot V_{DD}^2$  and the output makes a transition from low to high.

FIGURE 2.6: Power dissipation in an inverter

As shown in FIGURE 2.6 (b), when an input changes from low to high, only the N-type transistor is active. The energy stored in the load capacitor is discharged through the N-type transistor. The discharging phase gives an output transition from high to low. For a particular time in the transition, both P- and N- type transistors are switched on simultaneously and the short circuit current ( $I_{SC}$ ) can flow from power supply to ground, causing the dissipation of the short-circuit power.

Therefore, the dynamic power consumed by a CMOS inverter over a time interval [0, T] can be expressed by (from [37])

$$P_{dynamic} = C_{load} \cdot V_{DD}^2 \cdot N_{0 \to 1} \cdot \frac{1}{T} \quad (2.1)$$

where  $N_{0\to 1}$  is the number of times that the output changes from 0 to 1, i.e., the number of times that  $C_{load}$  is charged over the period [0, T]. If the inverter operates at a clock frequency  $f_{clk}$ , Eq. 2.1 can be rewritten as (from [37])

$$P_{dynamic} = C_{load} \cdot V_{DD}^2 \cdot N_{trans} \cdot f_{clk} \quad (2.2)$$

where  $N_{trans}$  is the average number of transitions per clock cycle at the output, referred to as switching activity.

In summary, the power dissipation in CMOS circuits comes from three major parts: dynamic power caused by the switching activity, static power due to the leakage currents and short-circuit power due to the short-circuit current. The dynamic power is the dominant component. For CMOS technologies up to  $0.35\mu m$ , the dynamic power is about 80% of the total power [37]. As the technology scales further down, the contribution of dynamic power increases because the functionality requirements and clock frequencies are increased [38]. As a result, the majority of existing power estimation techniques focuses on the dynamic power dissipation in CMOS circuits.

# 2.6.2 Power Analysis Techniques

Power analysis is defined as the problem of evaluating the average power dissipation in a digital circuit [39]. Power analysis tools are required to help with the power management tasks. More importantly, they can help the designers to determine how well a design meets the power specifications in early stages of the design process. In general, power

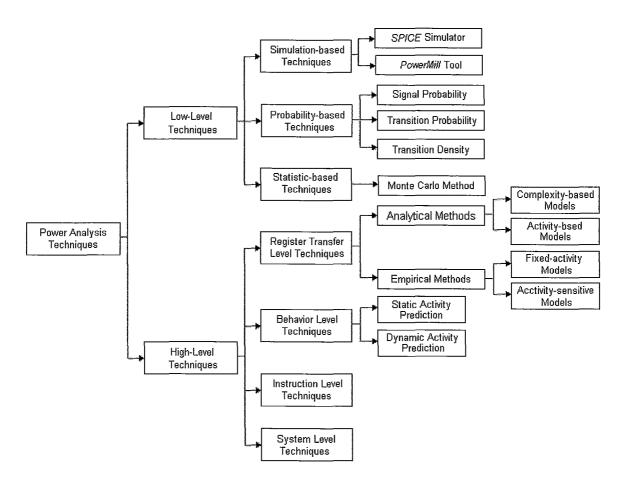

analysis techniques fall into two main categories based on the levels of design abstraction: *low-level* and *high-level techniques*, as it is summarized in FIGURE 2.7.

FIGURE 2.7: An overview of power analysis techniques

#### 2.6.2.1 Low-Level Techniques

The low-level techniques estimate the power from an analysis of switching activities of a design. They are also called gate-level techniques because the design is typically at the gate level. Refer to FIGURE 2.7, the low-level techniques can be categorized into three groups:

- 1. Simulation-based techniques: these approaches estimate the power through a computer simulation. The circuit is first simulated with a large number of input signals. During the simulations, all possible switching activities inside the circuit are captured. The power is then measured based on the simulation results. Even though the simulation based techniques are simple and straight-forward, the accuracy of the estimated power directly depends on the specific input signals used to drive the simulator. So they are considered strongly pattern-dependents. *SPICE* and *PowerMill* are two examples of power estimation tools using circuit simulation.

- 2. Probability-based techniques: these approaches analyze the power using transition probability to overcome the pattern-dependent problem exists in the simulation based techniques. The transition probability describes all possible logic signal transitions in the design. Instead of simulating the whole circuit with specific input signals in the simulation-based techniques, the probability-based approaches first compute the probability that a signal transition occurs at internal nodes. Then they propagate the probabilistic information into specialized circuit models to evaluate the power drawn by the circuit. The probability-based approaches determine the signal and transition probability that logic signals at specific nodes are logic high, or (2) the average transition probability from the probability waveforms, which describes the probability that logic signals make low-to-high transition at specific time points [39], or (3) the transition density, which is

defined as the average number of transitions per second at a node in the circuit [40]. (as it is depicted in FIGURE 2.7)

3. Statistic-based techniques: these approaches analyze the power with use of statistical estimation strategies. The statistic-based techniques employ traditional simulation models to test the circuit for a limited number of randomly generated input signals. The power consumption is monitored during the repeated simulations, and the process is only stopped if the measured power satisfies a specified error bound. For example, R. Burch *et al.* [41] adopt a Monte Carlo method to compute the power of ASIC designs.

The low-level techniques generally provide high estimation accuracy at the cost of long computation time. Furthermore, they require a complete circuit design at the gate level. In order to avoid costly redesign process, other techniques are needed to analyze the power of a design at higher levels of abstraction than the gate level.

# 2.6.2.2 High-Level Techniques

A number of high-level techniques have been proposed to estimate the power at high levels of abstraction design. As shown in FIGURE 2.7, the high-level techniques can be divided into four categories: register-transfer level (RTL) techniques, behaviour level techniques, instruction level techniques and system level techniques.

1. Register-transfer level (RTL) techniques: these approaches calculate the power at the architecture, or register-transfer level. At this stage, the primitives are

functional blocks such as adders, multipliers, controller, and SRAM. The RTL techniques can be subdivided into two classes: (1) analytical methods and (2) empirical methods, and they are descried as follows.

- (1) The analytical methods evaluate the power of a design in RTL description by indentifying the factors that affect the power dissipation in the circuits, such as the physical capacitance and activity information. These factors can be checked based on two different schemes: the complexity-based schemes and activity-based schemes. The complexity-based schemes compute the total power by summing up the power consumption of basic logic components required in the design. An example of these approaches is the Chip Estimation System (CES) discussed in [42]. The activity-based schemes first measure the design's average activity using the concept of entropy from information theory. The activity information is then applied to evaluate the power. These approaches are described in [43, 44]. The analytical methods which include the complexity-based schemes and activity-based schemes require very little information for the power calculation, such as technology parameters, memory sizes, and the number of logic components. However, they normally results in a low accuracy.

- (2) The empirical methods are other RTL estimation techniques that employ a macro-modeling scheme to obtain higher accuracy than the analytical methods. These methods produce an analytical model from the power measurement of the basic building blocks. The empirical methods can further

be subdivided into fixed-activity schemes, which ignore the power caused by the data activities, and activity-sensitive schemes, which account for the power of data activity, see FIGURE 2.7. The Power Factor Approximation (PFA) tool [45] is one example of fixed-activity schemes. The power estimation tool called ESP [46] and SPA [47] are examples of activity-sensitive schemes.

- 2. Behaviour-level techniques: these approaches predict the signal activity of the design, such as the access frequencies for different hardware resource, and use that information to analyze the power. Two methods are suggested to predict signal activity: (1) static activity prediction and (2) dynamic activity prediction, as it is described in FIGURE 2.7. The static activity prediction method determines the access frequencies from an analysis of the desired behaviour of the design. For example, the power model proposed by R. Mehra [48] was based on the study of a control-data flow graph (CDFG) for a high-level synthesis system. In contrast, dynamic activity prediction method analyzes the access frequencies by gathering the activity statistics from a design simulation. One example of this method is the Profile-Driven Synthesis System (PDSS) [49].

- 3. Instruction-level techniques: these approaches compute the power by realizing a given behaviour in software on a programmable instruction set processor. The model for embedded general-purpose and DSP process [50] is one example of these techniques.

4. System-level techniques: these approaches get a rough power accounting for all the components in a system at the earliest stage of design specification, for instance, the web power estimation tool *PowerPlay* [51].

In conclusion, the power analysis techniques are divided into two categories for the VLSI designs: the low-level techniques, which estimate the power of a digital circuit in the gate-level abstraction, and the high-level techniques, which compute the power in a level higher than gate-level, as it is illustrated in FIGURE 2.7. Compared to the low-level techniques, the high-level methods obtain a lower accuracy, but they require a shorter operation time for the power estimation. In the literature, a lot of power estimation models and tools for the crossbar switches are derived from one of the techniques discussed in this section. The previous work which is proposed to estimate the power dissipation in crossbar switches is presented in Section 2.6.4.

# 2.6.3 Commercial Power Analysis Tools

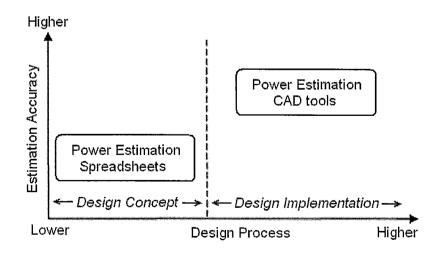

With the rapid growth of power-sensitive and high-density programmable devices, such as the portable electronics, power dissipation has become an important factor. Power analysis tools are essential for designers to check the power consumption of circuits during the design process. Today, semiconductor vendors have two different approaches to investigate the power in the stages from early concept to late design implementation: spreadsheets [52, 53, 54, 55], and CAD tools [56, 57, 58].

#### 2.6.3.1 The Spreadsheets

The designers need to provide the activity information for the power estimation using the spreadsheets. These spreadsheets analyze the power in three parts: static power, dynamic power and the maximum allowed power. The static power of each component is given in the device family datasheet. Designers can determine the total static power based on the number of specific components used in the design. To calculate the dynamic power, the average switching frequencies for the logic blocks or each module are defined by the designers, while the other coefficients or parameters are usually available in the device datasheet. The total power is measured as a summation of the static and dynamic power. Furthermore, the maximum allowed power in the device is computed to prevent any violation of power budget. If the estimated power is less than the maximum allowed power, the design is considered valid. Otherwise, the designers have to go back to solve the high power problem.

The power estimation flow used in spreadsheets can be summarized in following steps [53, 59]:

To identify the components used in the design and determine the total static power from the static power of specific components. The static power is described as

$$P_{static} = \sum_{all \text{ components}} P_{static\_per\_component} \quad (2.3)$$

where  $P_{static\_per\_component}$  is the static power dissipated by each component in the design, and it is given in the device datasheet.

To find out the switching activity of the logic blocks or each module in the design, and the dynamic power can be calculated by following equation

$$P_{dynamic} = \sum_{all \text{ modules}} Kf_i(\max)S_iC_iV_{swing}V_{supply} \quad (2.4)$$

where K is the power coefficient provided in the datasheet;  $f_i(\max)$  and  $S_i$  are the maximum frequency and average switching activity;  $C_i$  reflects the capacitance related to the particular logic block or module;  $V_{swing}$  and  $V_{supply}$ represent the swing voltage and supply voltage.

3) The total estimate power can be expressed as:

$$P_{total} = P_{static} + P_{dynamic} \quad (2.5)$$

4) The maximum allowed power  $(P_{MAX})$  for a device is determined by

$$P_{MAX} = \frac{T_J - T_A}{\theta_{JA}} = \frac{T_J - T_C}{\theta_{JC}} \quad (2.6)$$

where  $T_J$  is the maximum allowed junction temperature of the device;  $T_A$  and  $T_C$ represent the ambient temperature and the case temperature of device respectively;  $\theta_{JA}$  and  $\theta_{JC}$  stand for the thermal resistance and the junction-to-case thermal resistance. The values of  $T_J$ ,  $\theta_{JA}$  and  $\theta_{JC}$  are both specified in the device family datasheet, while designers give the values of  $T_A$  and  $T_C$ .

5) To ensure  $P_{total} < P_{MAX}$ . If  $P_{total} > P_{MAX}$ , the design is considered invalid, and a redesign process is required.

Spreadsheets can be used in the early design phases, such as the board design and layout phase, to develop proper power management. They are simple to use, but results normally have low estimation accuracy.

### 2.6.3.2 The CAD Tools

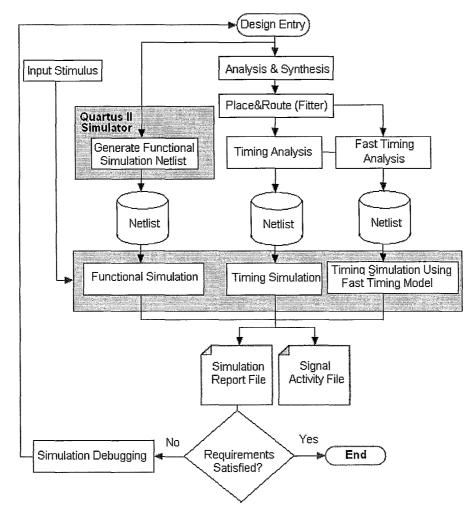

Compared to spreadsheets, CAD tools capture the switching activities of the designs based on the simulations instead of the switching information defined from the designers. Therefore, the estimated results from the CAD tools should have a higher accuracy. However, the CAD tools typically require a complete circuit design before a power analysis can be performed. Xilinx's *Xpower* [58] and Altera's *PowerPlay* [57] tools are two well known commercial tools for power estimation.

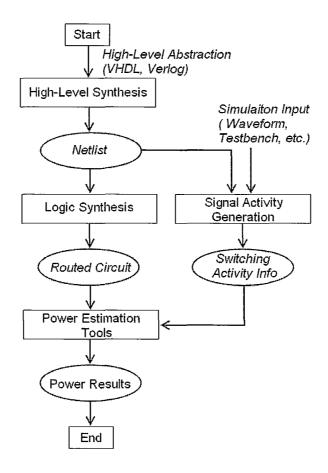

FIGURE 2.8: Power estimation flow in CAD tools

The approach for the CAD tools to estimate the power consumption is illustrated in FIGURE 2.8 (from [60]). The complete design specified in a high-level description language, like VHDL or Verilog, is first synthesized to a *netlist* during synthesis. The designers run circuit simulations with test input signals represented as waveforms or testbenches. In the simulations, the signal activity generation software collects the switching activity information inside the circuit. Finally, the estimator concludes the power from the routing information in *Logic Synthesis* and the switching activity information in simulations.

In short, there are two popular design tools in the industry to estimate the power consumption of a VLSI design: the spreadsheets and the CAD tools. FIGURE 2.9 compares these tools regarding the design process and the accuracy of estimation. A power measurement in later stage of the design process causes a higher accuracy. Therefore, depending on which stage the design is in and the required accuracy, the designers can use either the spreadsheets or the CAD tools.

FIGURE 2.9: Power estimation tools

#### 2.6.4 Power Estimation of Crossbar Switches

Many techniques have been suggested to analyze the power for general CMOS VLSI designs. The analysis can be performed at various abstraction levels as described in Section 2.6.2. So far, only a handful of studies have been done to analyze the power dissipation in crossbar switches.

In early 1997, a simple analytic model [61] was introduced to evaluate the power dissipation of multiprocessor interconnection networks under a fixed power constraint. This simple model could not perform power analysis of other interconnect designs at higher abstraction levels. Moreover, it is not sufficiently detailed because the analysis is just based on a counting of transistors required in the designs, but ignoring the wires. Recently, many models have been created to address the power problem of crossbar interconnects at various levels. H. Zhang *et al.* [62] derived an analytical model for the energy consumption of a crossbar interconnect network on the transistor level. Their study pointed out that a hierarchical interconnect network had the best energy efficiency.

With the development of SoC technology, a large number of device components like microprocessors, memory, and interfaces can be integrated into a single microchip. Hence, the power consumption of on-chip interconnects becomes an important design issue. A gate-level model was proposed in [63] for the power of the crossbar switches in standard cell ASIC processes. With a double metal 0.6 micron CMOS technology, the experimental results showed the power model had an average error less than 10%. A. G. Wassal *et al.* [64] proposed a system-level approach to compute the power consumption of VLSI packet switching fabric. By taking the traffic patterns into account, a traffic model was introduced to generate the switching activity inside the circuit. This approach delivers a high accuracy compared to other methods that did not include traffic models and statistics. The power estimated from this approach had an error of about 14%. Another power model for crossbar interconnects was also presented in [65] at architectural level. The model was shown to be quite accurate with an average error of 5.8%, but it is not suitable for crossbar switches bigger than 16x16.

There were several power models proposed in the past for network routers [66, 67] and switches [68, 69]. In [66], the authors introduced a framework at the architecture level to estimate the power of four widely-used switch fabric architectures in network routers: crossbar, fully connected, Banyan and Batcher-Banyan. This framework improved the accuracy of estimation to bit level by introducing "*Bit Energy*", which describes the energy consumed by a single bit travelling through the switch fabrics. Their results showed that a 32x32 bufferless crossbar switch fabric consumed approximately 300 mW, under uniform traffic conditions and load almost 60%. Another architectural-level power model were developed in [67] for the network routers. The authors broke down a router into three building blocks: the memories, crossbars and arbiters, and proposed a power model for each of them. The power models were verified by two commercial routers, the *Alpha 21364* router and the *IBM InfiniBand 8-port 12X* router. The experimental results shows the estimation results were very close to the values estimated by designers of these two products with an error of less than 15%.

A detailed analysis of multiplexer-based crossbar switches is presented in [68, 69]. T. Wu *et al.* [68] estimated the power consumption of a 256x256 crossbar switch