NL-91 (10-68)

## NATIONAL LIBRARY OTTAWA

# BIBLIOTHÈQUE NATIONALE OTTAWA

| NAME OF AUTHOR. SORAYA MOHAMMED EL-SAGIR                      |

|---------------------------------------------------------------|

| TITLE OF THESIS. Design and Hardware Implementation           |

| of a Celor-Coded Display System                               |

| for Radar Sugnals                                             |

| UNIVERSITY Mc Alaster Univ                                    |

| DEGREE FOR WHICH THESIS WAS PRESENTED                         |

| YEAR THIS DEGREE GRANTED                                      |

| Permission is hereby granted to THE NATIONAL LIBRARY          |

| OF CANADA to microfilm this thesis and to lend or sell copies |

| of the film.                                                  |

| The author reserves other publication rights, and             |

| neither the thesis nor extensive extracts from it may be      |

| printed or otherwise reproduced without the author's          |

| written permission.                                           |

| (Signed). S. M. El. Jagr.                                     |

| PERMANENT ADDRESS:                                            |

| Elect. Eng. Det.                                              |

| M. Master. University                                         |

| . Manni Hora, Ont                                             |

| DATED: O.t319 7 7                                             |

National Library of Canada

Cataloguing Branch Canadian Theses Division

Ottawa, Canada K1A 0N4

NOTICE

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité suférieure de repro-

S'il manque des pages, veuillez communiquer avec Luniversité qui a conféré le grade

La qualité d'impression de certaines pages peut laisser à desirer, surtout si les pages originales ont été dactylographiées a l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de mauvaise qualité

Les documents qui font déja l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30 'Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse

LA THÈSE A ÉTÉ

MICROFILMÉE TELLE QUE

NOUS L'AVONS REÇUE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming Every effort has been made to ensure the highest quality of reproduction possible

If pages are missing, contact the university which granted the degree

. Some pages may have indistinct print especially if the original pages were typed with a spoor typewriter ribbon or if the university sent us a poor photocopy

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30 Please read the authorization forms which accompany this thesis

> THIS DISSERTATION HAS BEEN MICROFILMED **EXACTLY AS RECEIVED**

**AVIS**

Bibliothèque nationale du Canada

Division des thèses canadiennes

Direction du catalogage

duction

A CCLOR-CODED FADAR DISPLAY

# DESIGN AND HARDWARE IMPLEMENTATION OF A COLOR-CODED DISPLAY SYSTEM FOR RADAR SIGNALS

bу

Soraya Mohammed El-sagir, B.Eng. & B.Sc. (Mathematics)

A Thesis

Submitted to the Faculty of Graduate Studies

in Partial Fulfilment of the Requirements

for the Degree

Master of Engineering

McMaster University

September, 1977

Master of Engineering (1977)

McMa ter University Hamil on, Ontario

TITLE: Design and Hardware Implementation of a Color-Goded Display System for Radar Signals.

AUTHOR: Soraya Mohammed El-sagir,

B. Eng. (Cairo University, Cairo) &

B. Science (Ain Shams University, Cairo)

SUPERVISOR: Dr. C.R. Carter\*

NUMBER OF PAGES: 137 , xi

#### ABSTRACT

This thesis gives the design and hardware implementation of a display system for the synthetic presentation of real time radar signals. A color coding technique is applied in the system, where a color code of sixteen different colors is employed to encode the signal amplitude. The system consists of a color television monitor, a large scale random access memory and digital interfaces to buffer the real time input to the display.

A general study of the different types of display devices followed by a review of the common radar displays is presented.

Then, a detailed investigation and a presentation of a color coding technique and its application is given.

The details of the system design and operation are given in addition to the experimental work for testing the system performance. The presentation of radar signals by the color coded display system is demonstrated.

#### ACKNOWLEDGEMENTS

The author gratefully acknowledges the guidance, encouragement, help and excellent supervision given by her supervisor, Dr. C.R. Carter.

She also wishes to thank Mr. Currie and the research personnel of the Communications Research Laboratory at McMaster, for their cooperation.

The author would like to express her acknowledgements to the National Research Council of Canada for financial support.

\*Finally, a special thank you goes to her husband, Elsayed Orady, for his encouragement, understanding and help throughout this work.

### CONTENTS

|                                                      | PAGE |

|------------------------------------------------------|------|

| ABSTRACT                                             | 111  |

| ACKNOWLEDGEMENTS                                     | iv   |

| LIST OF FIGURES .                                    | viii |

| LIST OF TABLES                                       | хi   |

| CHAPTER 1 - INTRODUCTION                             | 1    |

| CHAPTER 2 - SURVEY OF DISPLAY DEVICES                | 6.   |

| 2.1 LIGHT EMITTING DIODE DISPLAYS                    | 6    |

| 2.2 LIQUID CRYSTAL DISPLAYS                          | 7    |

| 2.3 PLASMA DISPLAYS                                  | 10   |

| 2.4 MONOCHROMATIC CATHODE RAY TUBE                   | t    |

| DISPLAYS                                             | 13   |

| 2.5 COLOR TELEVISION DISPLAYS                        | . 16 |

| CHAPTER 3 - AIR TRAFFIC CONTROL RADAR AND RADAR DIS- |      |

| PLAYS                                                | 18   |

| 3.1 FUNDAMENTALS OF PULSED RADAR                     | 18   |

| 3.2 AIR TRAFFIC CONTROL RADAR                        | 24   |

| 3.3 COMMON DISPLAYS FOR RADAR                        | 25   |

| 3.4 COLOR-CODED TELEVISION DISPLAY FOR               | · ·  |

| RADAR                                                | 28   |

| 3.4.1 Color-Coding Technique                         | . 28 |

| 3.4.2 Color-Coded Display                            | 29   |

| 3.4.3 Advantages of Color-Coded                      |      |

| Display.                                             | 29   |

| CHAPTER | 4  | THE  | DESIGN A | AND CONSTRUCTION OF THE COLOR- | ,    |

|---------|----|------|----------|--------------------------------|------|

| 4       | •  | CODE | D DISPLA | AY SYSTEM                      | 33   |

|         |    | 4.1  | SYSTEM   | FUNCTION AND BASIC CON-        | -    |

|         |    |      | CEPTS    |                                | ·33  |

|         |    | 4.2  | SYSTEM   | DESCRIPTION AND OPERATION      | 36   |

|         | •  | •    | 4.2.1    | General Description .          | 36   |

|         |    |      | 4.2.2    | System Capacity, and Sampling  |      |

|         |    |      |          | Area                           | 37   |

|         |    |      | 4.2.3    | Timing and Modes of Operation  | 43   |

|         | •  |      | 4.2.4    | Hardware Implementation of     |      |

|         |    |      |          | the Display System             | 45   |

| • • •   |    | 4.3  | THE DIS  | SPLAY SET                      | 45   |

| •       |    | ,    | 4.3.1    | Type and Specifications        | 45   |

| •       | ٠  |      | 4.3.2    | Sync Signals for Color Tele-   |      |

|         |    | ,    |          | vision Monitor                 | 47.  |

| , ,     |    |      | 4.3.3    | Sync Signal Generator          | 49   |

| ,       |    | 4.4  | RANDOM   | ACCESS MEMORY                  | 50   |

|         |    | *    | 4.4.1    | RAM System Specifications      |      |

| `       |    | ,    | ,        | and Operation                  | 53   |

| •       | ٠, |      | 4.4.2    | Memory Organization            | ,58. |

|         | •  | 4.5  | INPUT-N  | MEMORY INTERFACE               | 61   |

| v       |    |      | 4.5.1    | Analog-to-Digital Converter    |      |

| \$      |    | •    |          | (ADC)                          | 61   |

| ٠ سر    |    |      | 4.5.2    | Interface Between the ADC and  |      |

| ****    |    |      |          | the Memory                     | 65   |

|         | `  | 11 6 | 4 DOBES  | THE AND DIMINE CIRCLIA         | 60   |

| ,            | 4.7 MEMOFY-DISPLAY INTERFACE               | 74    |

|--------------|--------------------------------------------|-------|

| • • •        | 4.7.1 Interface Between the                |       |

|              | Memory and the Color-Encoder               | 7 h   |

|              | 4.7.2 Color-Encoder                        | 79    |

| CHAPTEP 5 -  | - COLOR CODE SELECTION AND SYSTEM TEST = . | •     |

|              | ING                                        | 86    |

| •            | 5.1 COLOR CODE SELECTION .                 | 86    |

|              | 5.2 SYSTEM ADJUSTING AND TESTING           | . 95  |

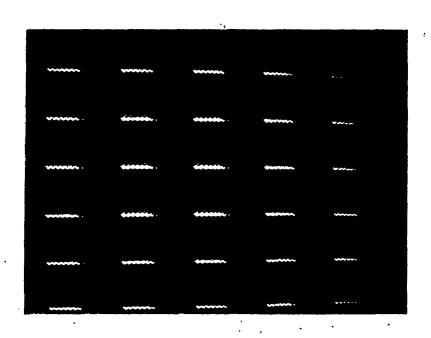

|              | 5.2.1 Test Card and Test Pattern           | 95    |

|              | 5.2.2 Color Convergence Adjustment         | 95    |

| CHAPTER 6 -  | THE PRESENTATION OF RADAR SIGNALS BY THE   | •     |

|              | COLOR CODED DISFLAY SYSTEM                 | 101   |

| CFAPTER 7 -  | - CONCLUSIONS AND RECOMMENDATIONS          | 112   |

| •            | 7.1 CONCLUSIONS                            | 112   |

| •            | 7.2 RECOMMENDATIONS                        | . 115 |

| REFERENCES   | •                                          | 1,14  |

| APPENDIX 1 - | - COLOR TELEVISION MONITOR                 | 1 1,7 |

| •            | CTM2/51 TECHNICAL SPECIFICATIONS           | `117  |

| APPENDIX 2 - | - RAM SYSTEM SPECIFICATION AND OPERATION   | 121   |

| APPENDIX 3 - | - HARDWARE DETAILS FOR THE DISPLAY SYSTEM  | 127   |

#### LIST OF FIGURES

| FIGURE |                                                                                                                     | PAGE |

|--------|---------------------------------------------------------------------------------------------------------------------|------|

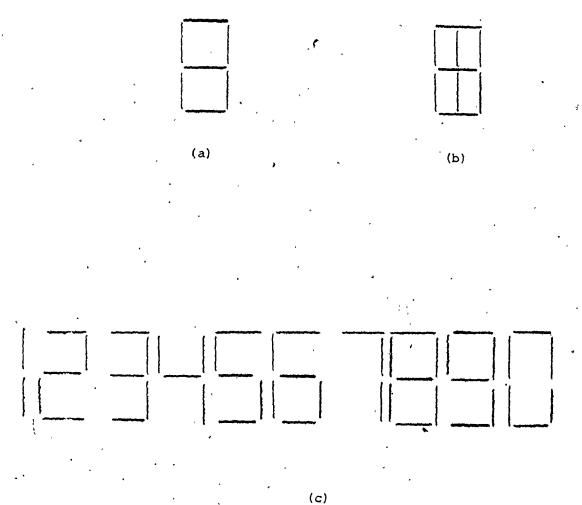

| 2.1    | Seven and nine segments light emit-<br>ting diode displays                                                          | 8    |

| 2.2    | Alpha-numeric displays                                                                                              | 9    |

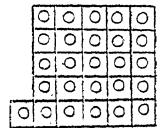

| 2.3    | Examples of character construction by selecting dots from a dot matrix of displays                                  | 9    |

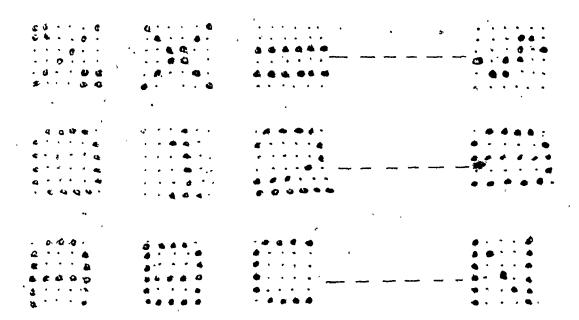

| 2.4    | A plasma display terminal for computer general information and an example of the display capabilities               | 12   |

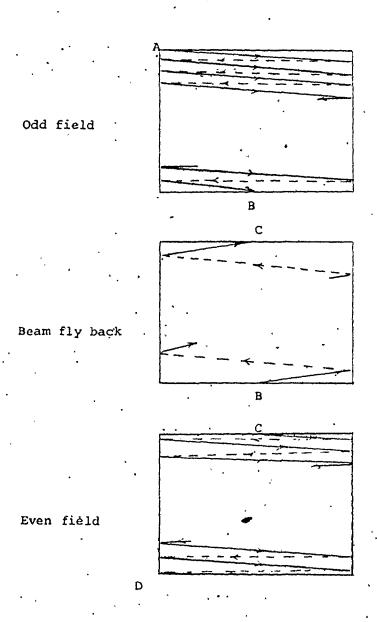

| 2.5    | The odd and even interlaced scanning procedure for television display                                               | 15   |

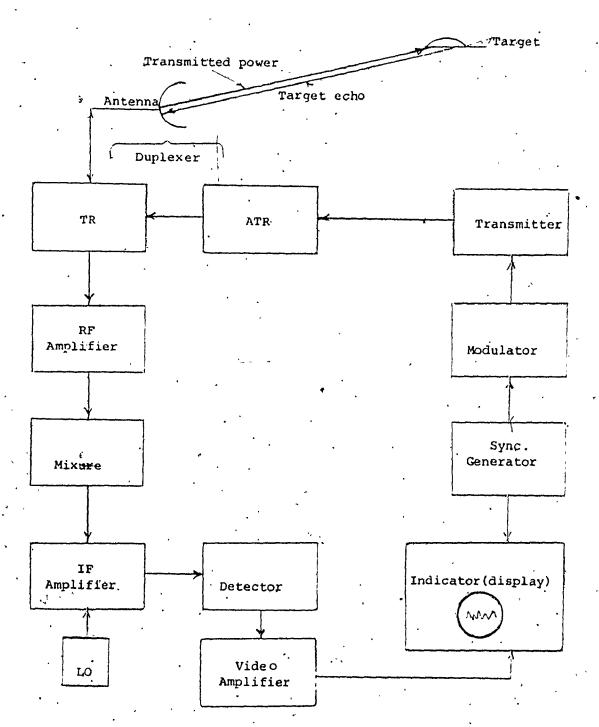

| 3.1    | Block diagram of a pulsed radar                                                                                     | 19   |

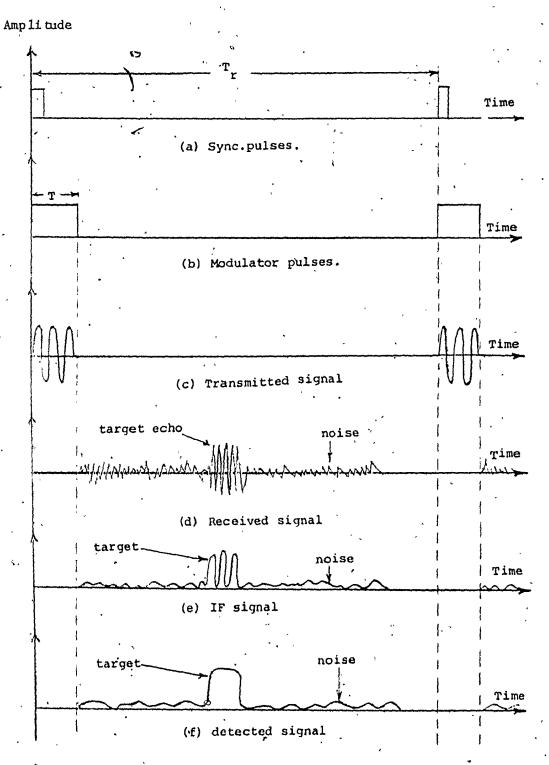

| 3.2    | Typical pulsed radàr timing diagram (same time scale)                                                               | 21   |

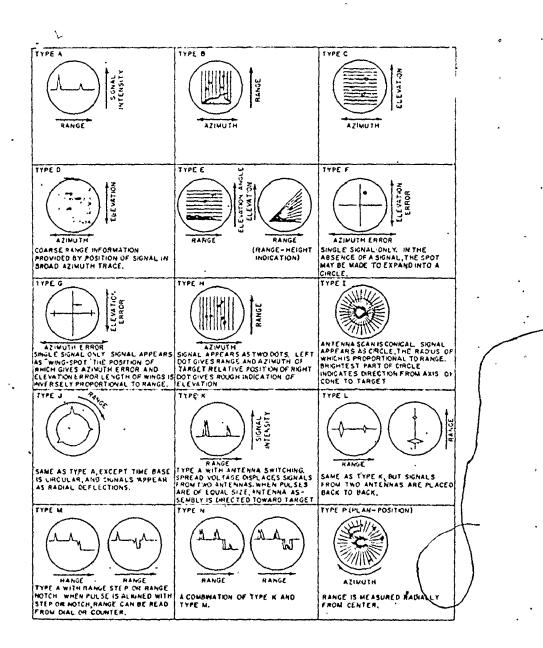

| 3.3    | Common CRT radar displays                                                                                           | 27   |

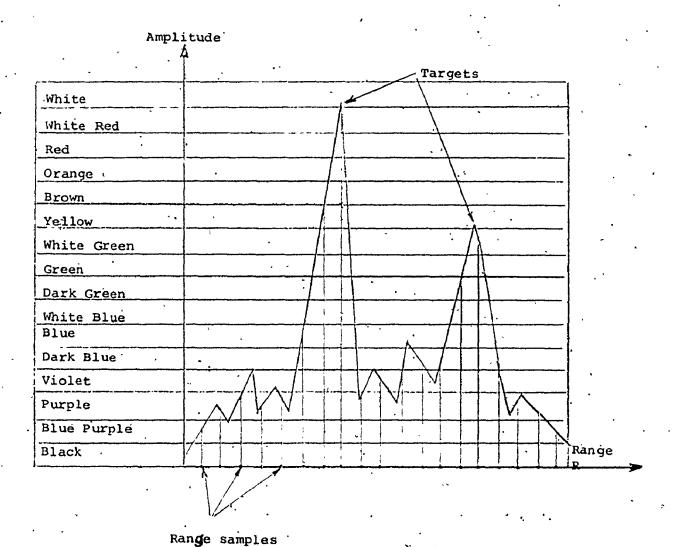

| 3.4    | Color-coding technique for radar signal and an example of the color code                                            | 30   |

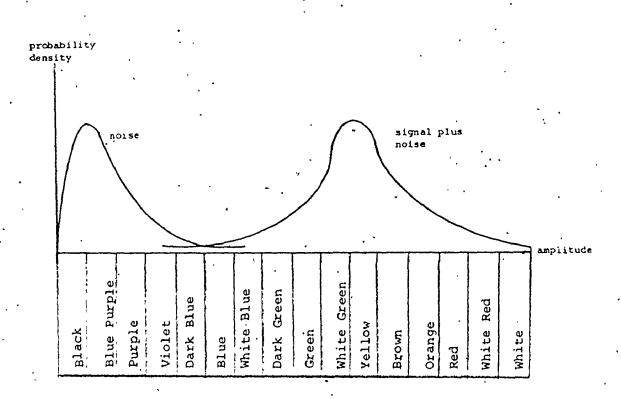

| 3.5    | Probability density functions for typical radar signal with color coding showing sixteen colors                     | 31   |

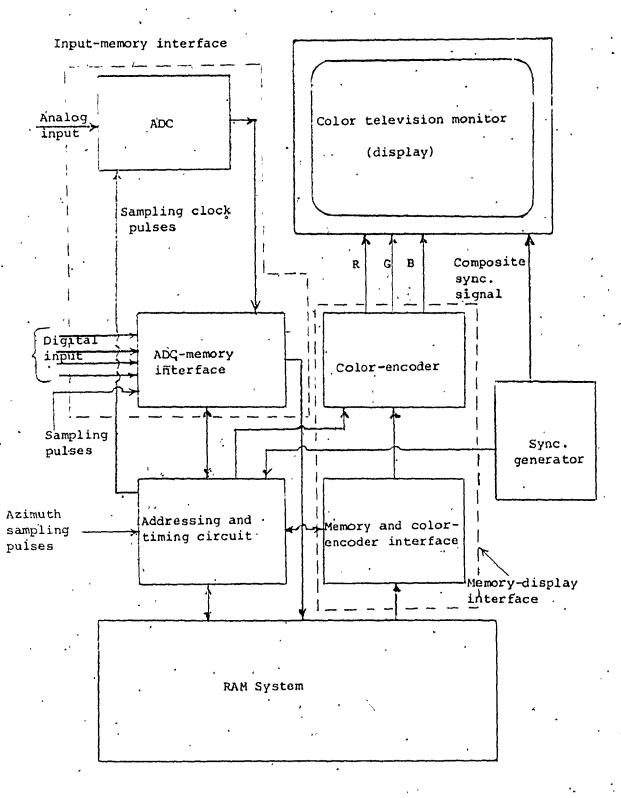

| 4.1    | Block Diagram for the color-coded display system for radar signal :                                                 | 34   |

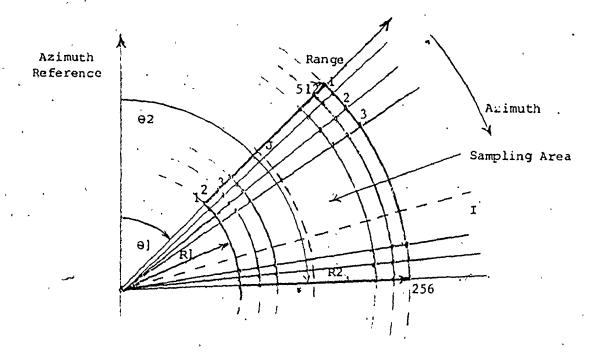

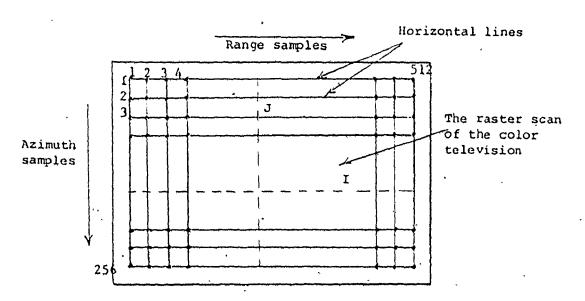

| 4.2    | Sampling area and output format                                                                                     | 38   |

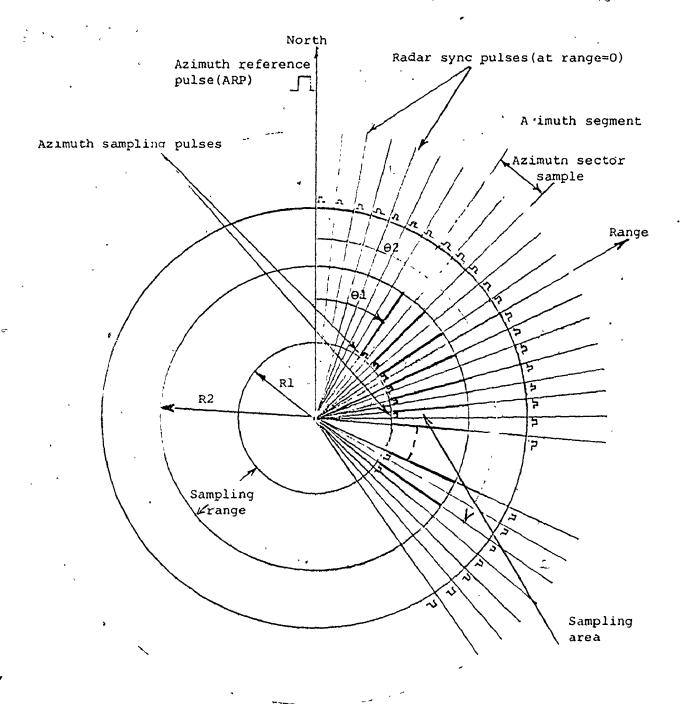

| 4.3    | Radar sync pulses, azimuth sampling pulses and sampling area                                                        | 4,0  |

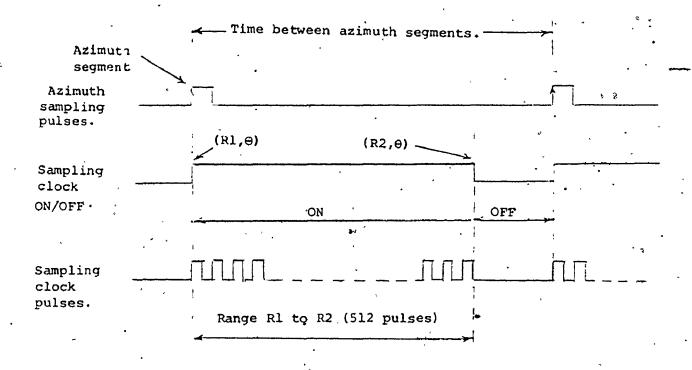

| 4.4    | Sampling in range                                                                                                   | 42   |

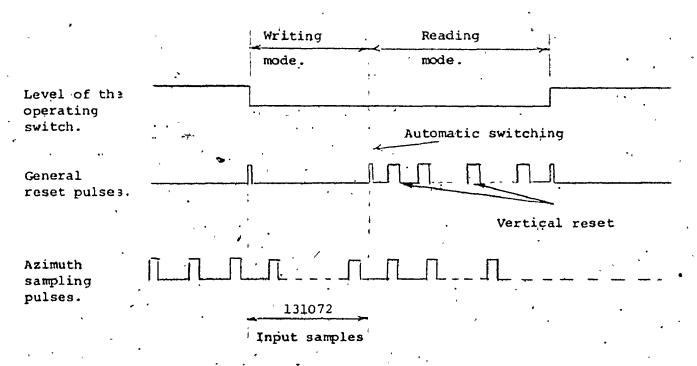

| 4.5    | Switching between modes of operation and its relation with azimuth sampling and general reset of the display system | 42   |

| •  |              |                                                                                                    |           |

|----|--------------|----------------------------------------------------------------------------------------------------|-----------|

|    | •            |                                                                                                    | ē.        |

| •  | FIGURE       | •                                                                                                  | PAGE      |

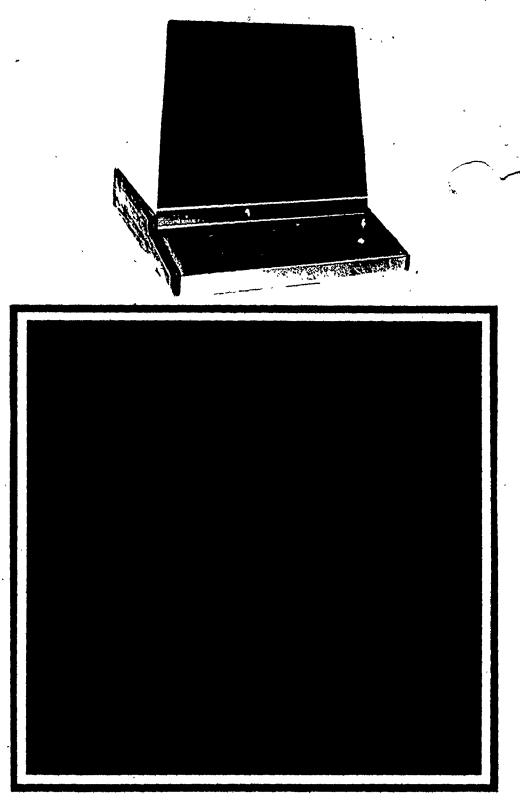

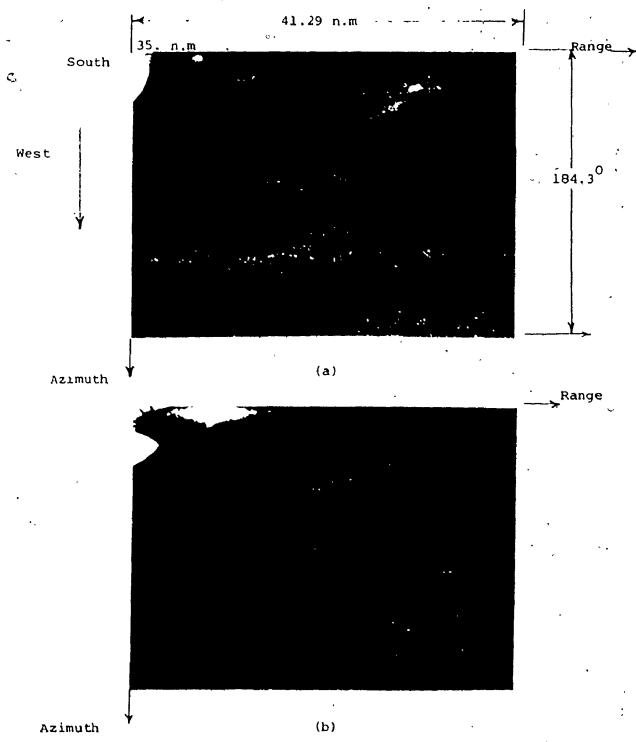

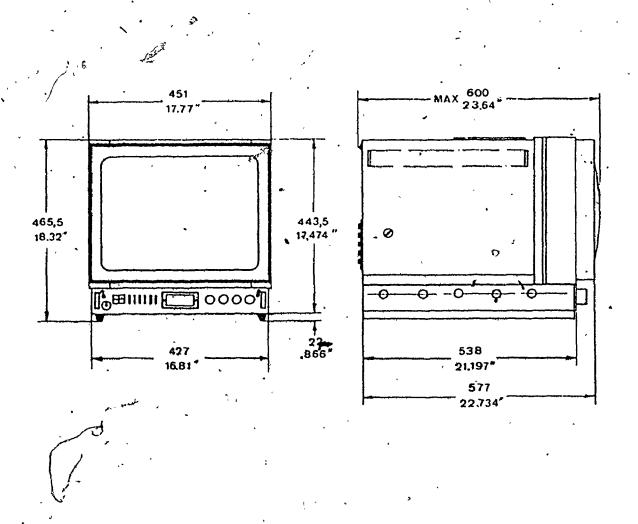

|    | 4.6          | Photographs of the front and back views of the color television monitor                            | 46        |

|    | 4.7          | Synchronization signals for the color television                                                   | 48        |

|    | 4.8.a        | Sync signal generator circuit diagram                                                              | 51        |

| دم | 4.8.6        | Divide by 109 circuit diagram                                                                      | 52        |

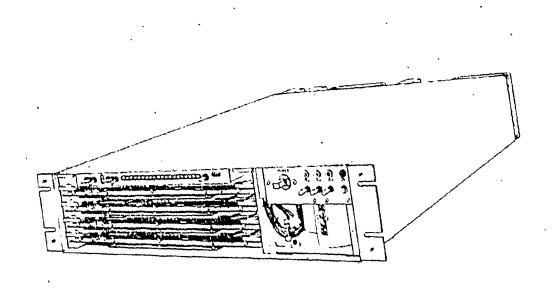

| ·  | 4.9          | MICRORAM Semiconductor system (front panel removed)                                                | 54        |

|    | 4.10         | Interface circuitry between the memory and the external system                                     | 56        |

|    | 4:11         | RAM system 3400 N interface signals timing diagram                                                 | . ´<br>57 |

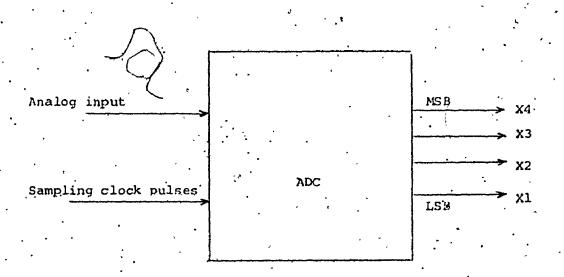

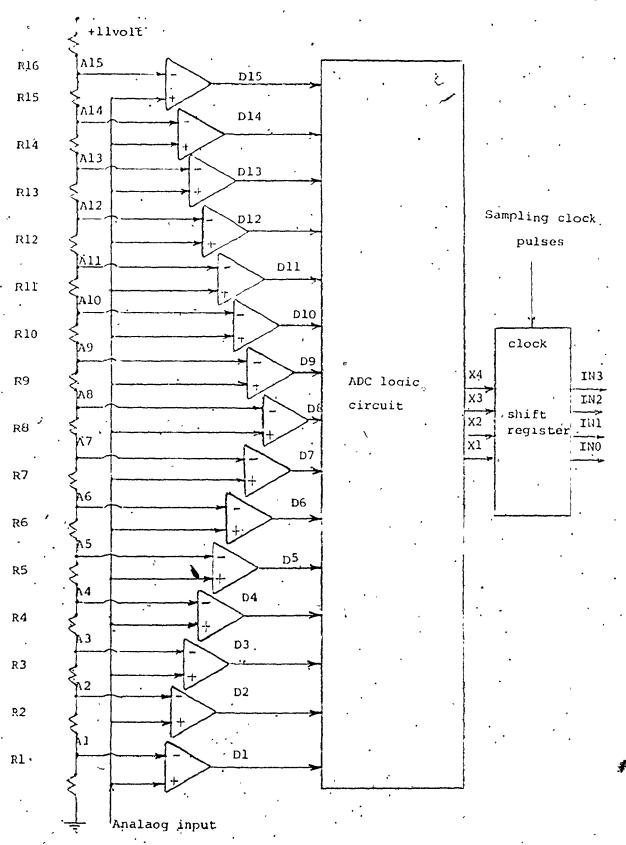

|    | 4.12         | ADC Block diagram                                                                                  | 62        |

| ٠  | 4.13         | ADC Circuit diagram                                                                                | 63        |

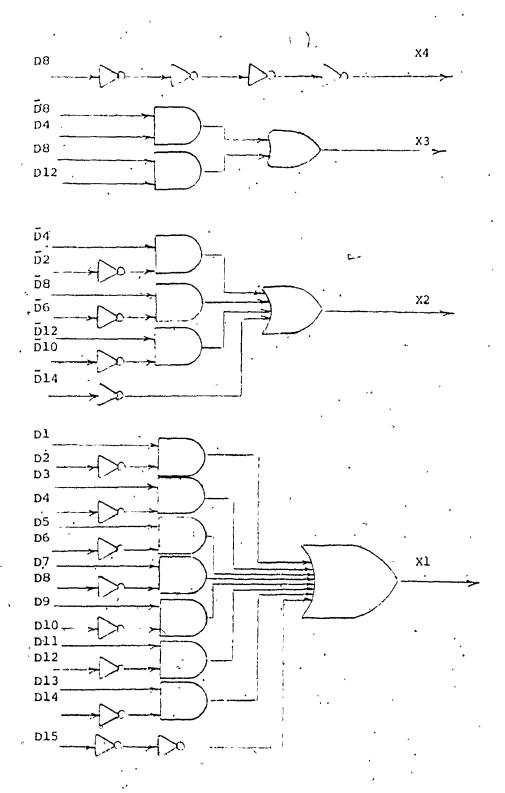

|    | 4.14<br>4.14 | ADC Logic circuit diagram                                                                          | 64        |

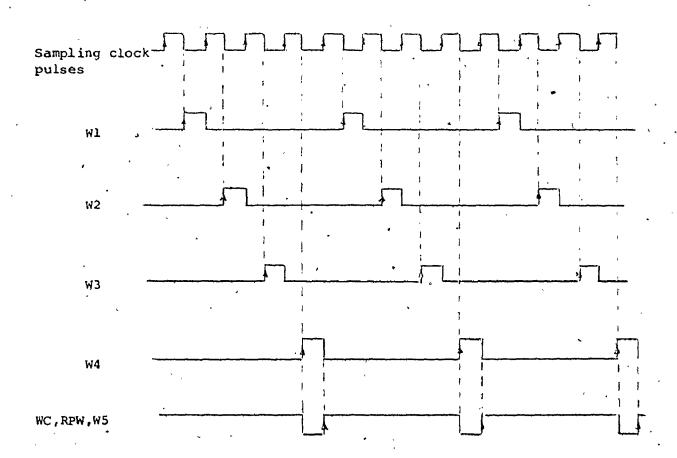

|    | 4.15         | Timing diagram for writing mode of operation                                                       | 68        |

| ٠, | 4.16         | Circuit diagram for the ADC-memory inter-<br>face                                                  | 70        |

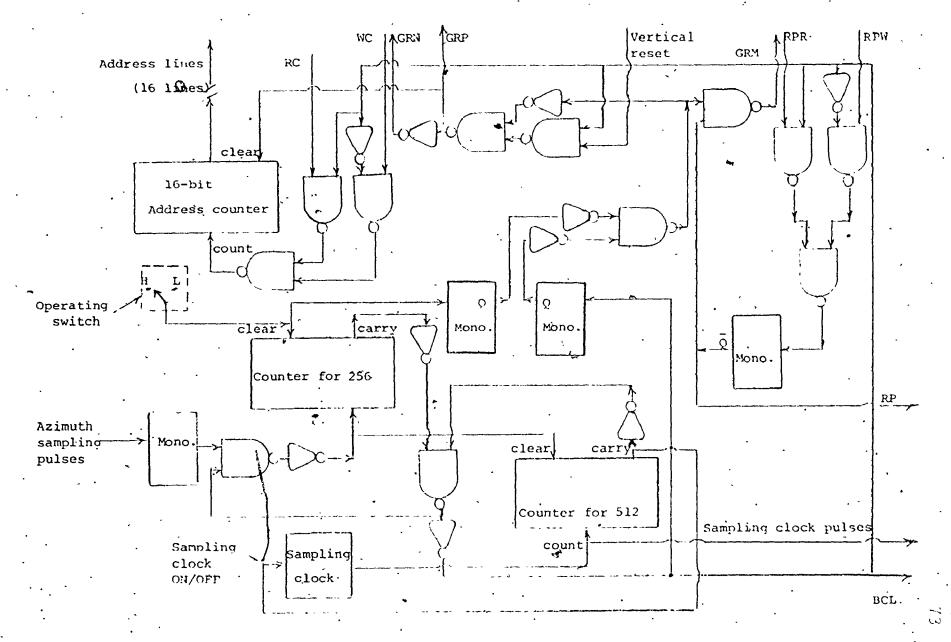

|    | 4.17         | Logic circuit diagram for addressing and timing circuit                                            | 73        |

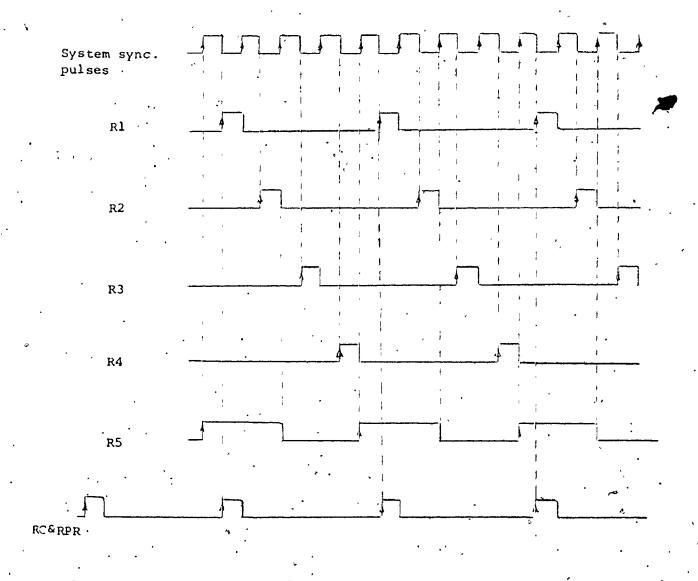

|    | 4.18         | Timing diagram for reading mode of operation                                                       | 76        |

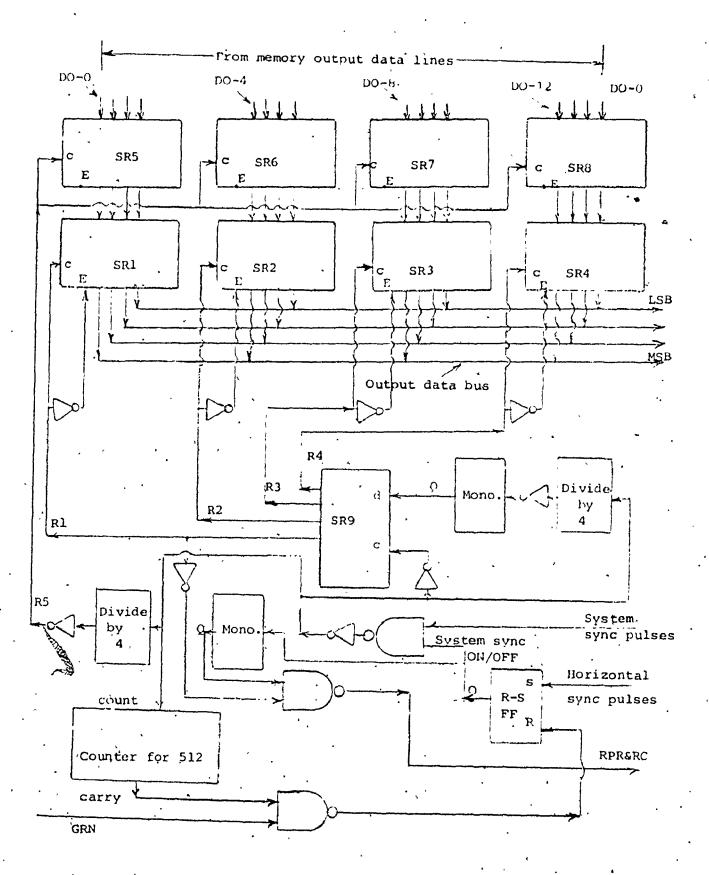

|    | 4.19         | Memory-color encoder interface circuit dia-<br>gram                                                | 77        |

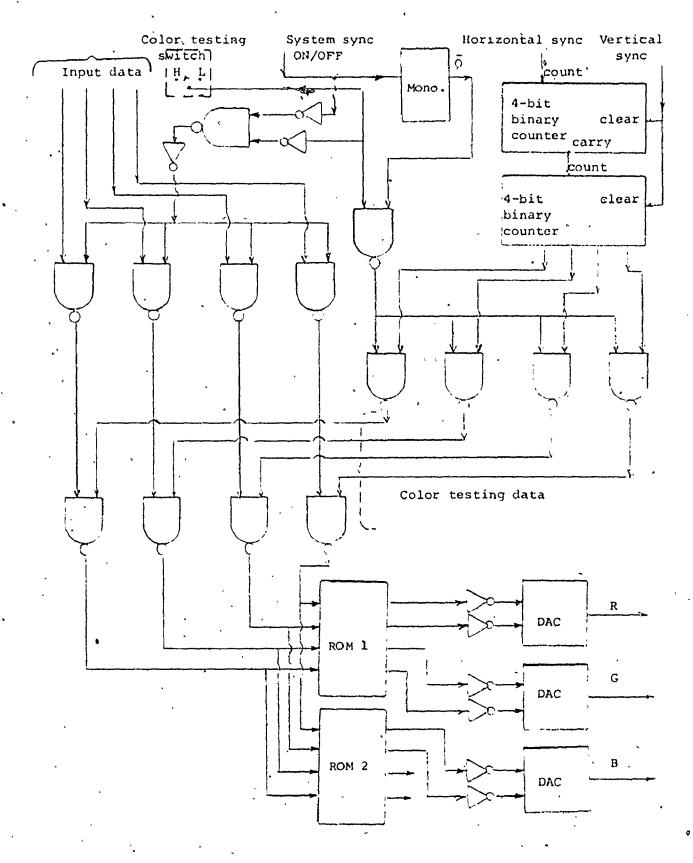

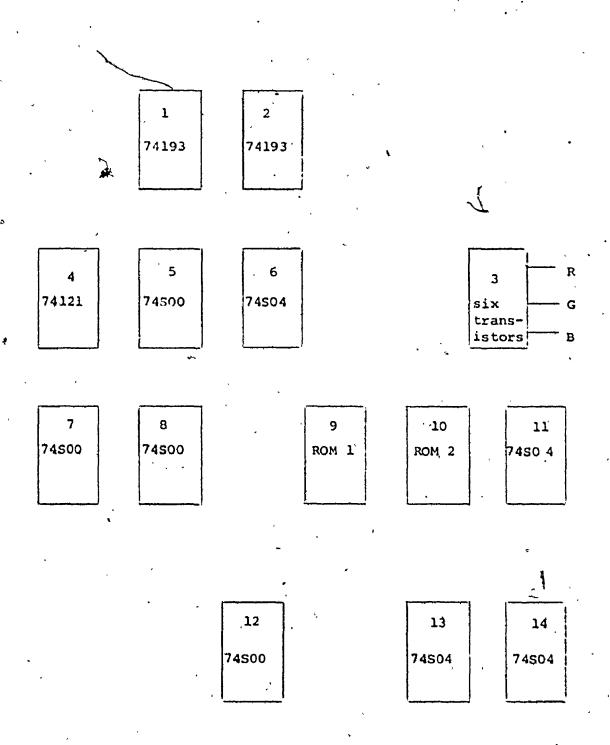

|    | 4.20 -       | Color-encoder circuit diagram                                                                      | 80        |

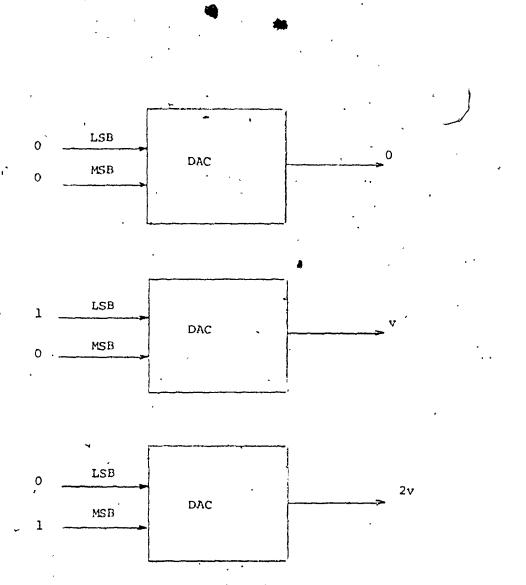

|    | 4.21         | Digital to analog conversion code                                                                  | 81        |

|    | 4.22         | The implementation of the color coding technique                                                   | 83        |

|    | 5.1          | Testing the response of the output color on the color TV screen to the change in the input voltage | 87        |

|    | •            | ix                                                                                                 |           |

|       | ٠      |                                                                                                                                                                          | , •             | . , |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|

|       |        | •                                                                                                                                                                        | ·               | *   |

|       | •      | •                                                                                                                                                                        | •               | 6   |

| •     | FIGURE |                                                                                                                                                                          | PAGE            |     |

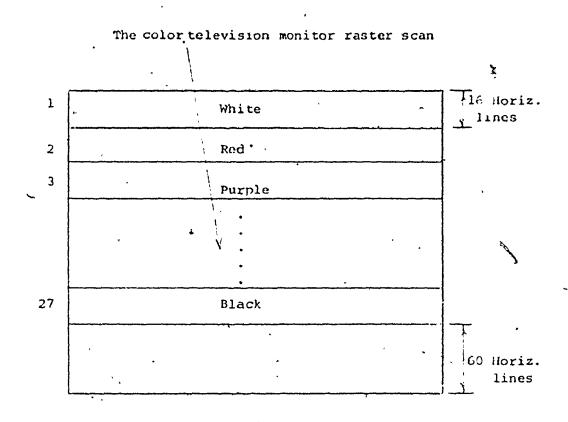

| • •,  | .5.2   | The display of 27 color bands                                                                                                                                            | . 89            |     |

|       | 5.3    | The Logic circuit of the color testing signal generator                                                                                                                  | 90 <sub>.</sub> | ·   |

|       | 5.4    | Photograph of the 27 color bands produced by the color television monitor                                                                                                | 92              | ٠,  |

|       | 5.5    | Photograph of the selected color code                                                                                                                                    | .93             |     |

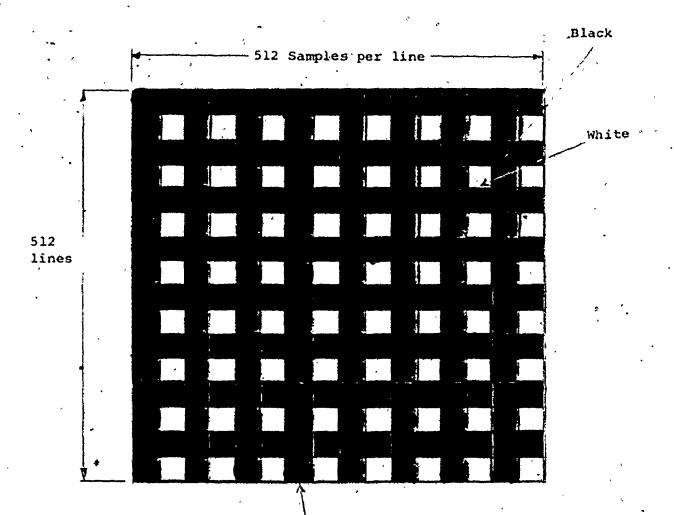

| c     | 5.6    | Test pattern                                                                                                                                                             | 96              |     |

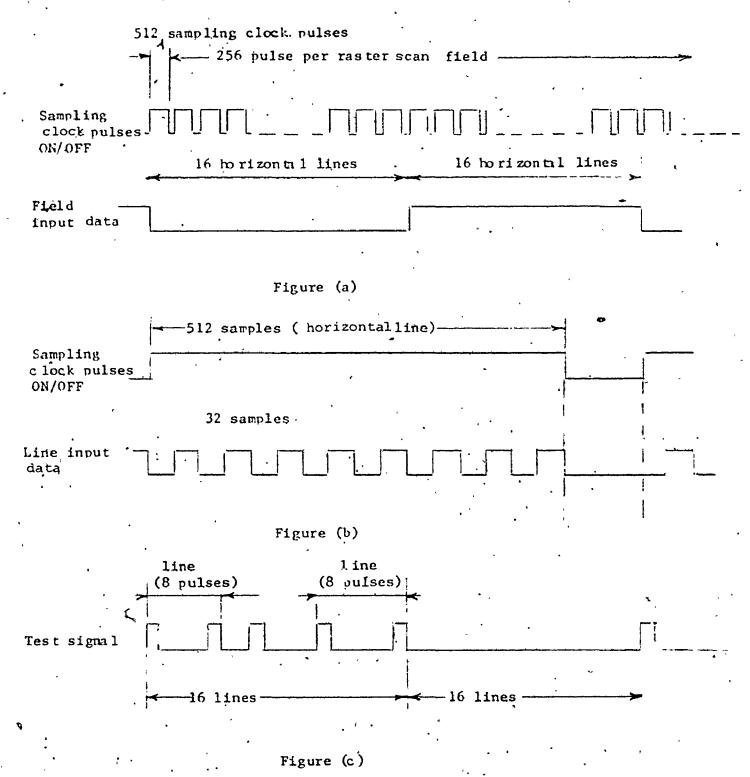

| , , , | 5.7    | Test signal and its relation with the timing pulses                                                                                                                      | 97              |     |

|       | 5.8 .  | Test card circuit diagram                                                                                                                                                | . 98            | •   |

| •     | 5.9    | Photograph of the test pattern as displayed                                                                                                                              | 99              |     |

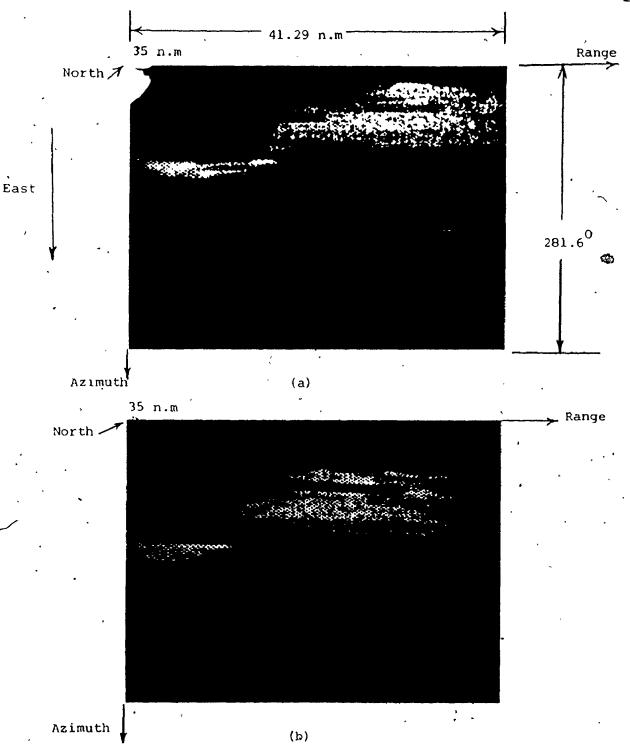

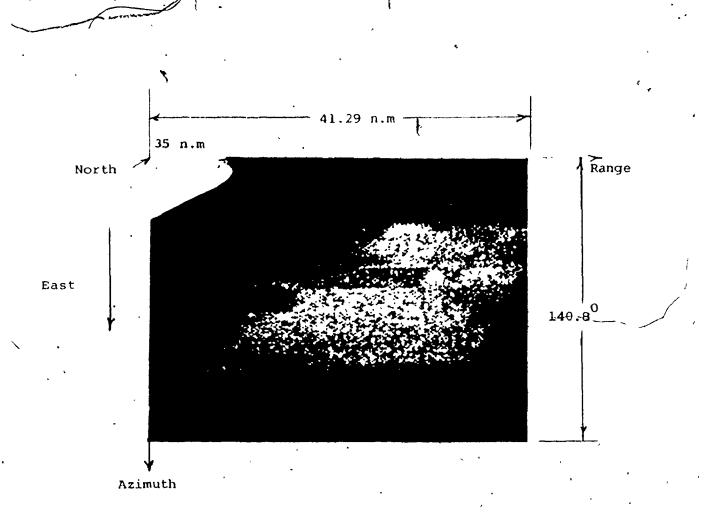

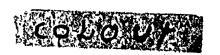

|       | 6.1    | The presentation of the rain storm by the display when the total sector angle is 281.6 degrees                                                                           | 103             | ٠,  |

| •     | 6.2    | The presentation of the rain storm by the display when the total sector angle is 140.8 degrees with the area covered by the storm cloud is expanded showing more details |                 | ,   |

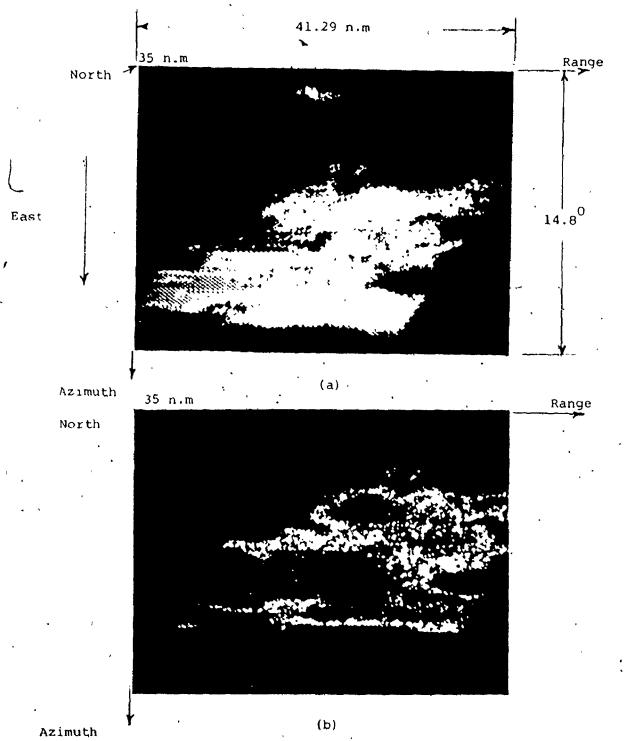

|       | 6.3    | The effect of changing the maximum digitizing levels with respect to the maximum video level on the color presentation of data                                           | 106             | e.  |

| ·     | 6.4    | The presentation of the rain storm by the display when the total sector angle is 70.4 degrees and the north-most part of the storm clous is expanded                     | 107             | 1   |

|       | 6.5    | The presentation of the rain storm when the total sector angle is 35.2 degrees showing two parts of storm cloud magnified by decreasing the sector angle                 | . 108           | ,   |

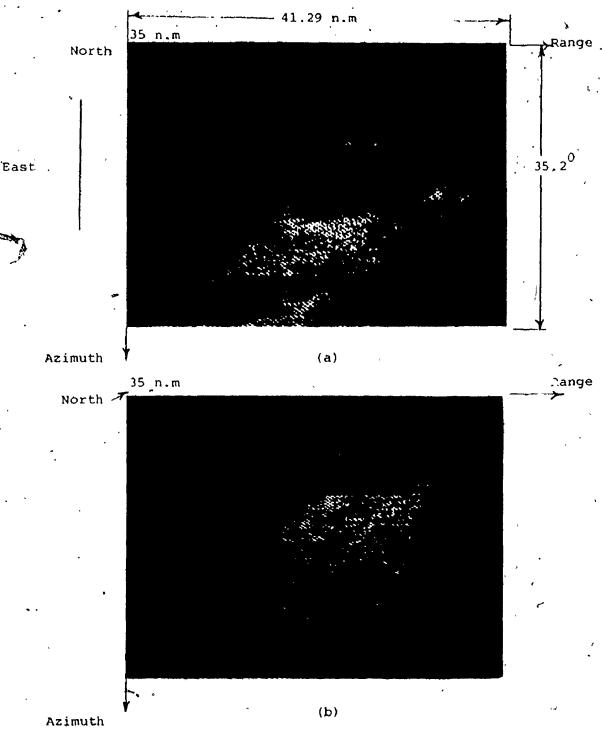

|       | 6.6    | Two video segments of the freezing rain storm as presented by the display when the total sector angle is 184.3 degrees                                                   | 109             |     |

|       |        |                                                                                                                                                                          | •               |     |

|       |        | . <b>x</b>                                                                                                                                                               | •               |     |

| ,     | :      |                                                                                                                                                                          | • , •           | ••, |

|       |        |                                                                                                                                                                          |                 |     |

## LIST OF TABLES

| TABLE |                                                        | PAGE   |

|-------|--------------------------------------------------------|--------|

| 4.1   | Memory system 3400N specifications                     | 55     |

| 4.2   | Description of the RAM system inter-<br>face signal    | <br>59 |

| 4.3   | ADC digitizing levels and their binary representations | 66     |

| 4.4   | Truth Table of the ADC logic circuit                   | 67     |

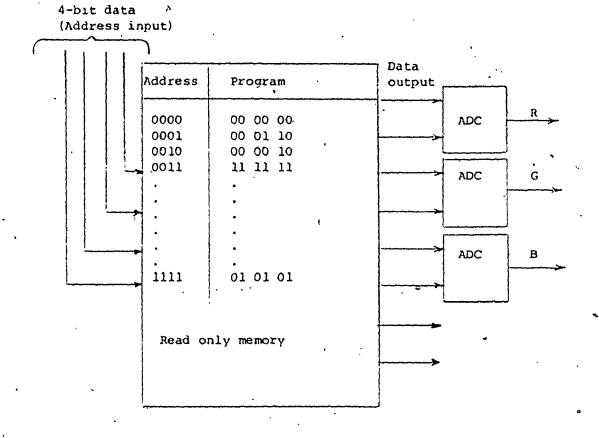

| 4.5   | ROM Program for the selected color code                | 8,4    |

| 5.1   | ROM Program to generate 27 different colors            | , 91,  |

| 5.2   | ROM Program for the selected color code                | 94     |

#### CHAPTER 1

#### INTRODUCTION

The interface between human observer and electronic equipment is of major importance, especially when a large quantity of irrelevant information is being presented. Such is the case in radar where the operator has to be responsive to target detection. In case of air traffic control radar, the targets of primary interest are aircraft. However, radar echoes are also received from a variety of other objects within the operating environment of the radar. These include objects on the ground such as buildings, trees, hills; those in sea such as waves, and floating objects; birds and weather conditions such as rain, snow, clouds, and air turbulence.

This means that aircraft are not the only objects to be displayed by the radar indicator. These extraneous echoes tend to mask the appearance of the display. For example, birds during migration can cover areas of the display, or, in a small group can give an indication similar to an aircraft. Air turbulence also has a similar effect on the indicator. Thus, it is extremely important to reduce the risk of aircraft disaster due to severe weather turbulence and the bird strike problem.

There have been many disastrous aircraft crashes due to problems caused by storms. Recently, on April 4, 1977 a Douglas DC-9, with its engines deadened due to hail stones in

a severe thunder storm, crashed in Georgia [1]. Reuter news agency reported 72 deaths and 28 injuries, many critical, when the plane attempted to land on a highway but instead hit a pole, trees, cars, and grocery store before it explained and burned.

Birds have also caused a number of commercial and military aircraft crashes in various countries. The main problem occurs when birds get caught in aircraft engines since one or two large birds can destroy an engine. In the United States, birds caused the engine of a DC-10 to explode causing \$25-million damage. In Canada, the average bill for such damage is now of the order of \$150,000 a year and in some years runs as high as half a million dollars [2]. (The total for New York Kennedy Airport in 1975 was about \$40-million).

It has been reported that the avoidance of birds is a major problem for pilots [3]. The Canadian Armed Forces lost a dozen CF-104 Star Fighters worth \$1.5 million each in the last eight years. In West Germany, sixteen Luftwaffe planes have crashed since 1958 after striking birds [5]. In the latest accident on April 19, 1977 a Star-Fighter fell into the Baltic Sea after a sea-gull was sucked into the jet engine. The West German airforce intended action against birds and issued special warnings to its pilots.

The bird hazard has been sufficient to maintain a group in Ottawa called the National Research Council Associate Committee on Bird Hazards to Aircraft. The objectives of the group are to find means for excluding birds from airports and planes

in flight. Lately, National Research Council (NRC) has disbanded its bird committee because, in 14 years, it has created enough momentum for other Federal agencies to take over [4]. The committee contributed greatly to 'people safety' in the air. It also inspired inventors from far and wide to come forward with ideas for solving the costly and even potentially disastrous threat posed by mid-air collisions between birds and aircraft. A major problem is due to migrating birds in the area surrounding airports and methods for getting rid of them, nave ranged from ultra-sonic sounds to blasts from shot-gun. The bird hazard committee also pioneered the method of predicting migration patterns as an aid, to pilots, and its efforts over the years led to the creation of the Bird Strike Committee (Europe).

One of the main solutions to the problem of detecting and identifying aircraft; in the presence of interfering objects, is to improve the capabilities of the radar equipment especially in the area of display systems. This can be achieved by increasing the capacity for displaying large amounts of data with easier interpretation of the displayed information. A possible technique which can assist in this aspect is the use of color [6]. The phenomenon of seeing light and color has always been fascinating. Through the ages, people learned the properties of colors and the natural color mixing possibilities [7], and the color has been used in many different fields to provide useful discrimination properties.

In the area of information displays, presentation of

data using only a monochrome display conveys information in an incomplete form. Strong signals and weak signals yield essentially the same bright-up spot. The eye accepts and interprets the information despite its limitations but the display has a missing dimension, lacking all the variables provided by that which the eye recognizes as color. As a matter of fact, scientifically controlled tests showed that color-coding at any level yielded an improvement in time scores [8,9]. Color coding can further enhance the data presentation and make the interpretation easier. Also, an excellent selection of color devices exists (as shown in Chapter 2).

#### Scope of Thesis

The main objective of this thesis is the design and construction of a display system, in which a color coding technique is implemented. The display system employs a color television monitor and a large scale random access memory. The system function is to develop a synthetic presentation of real time radar signals, using sixteen different colors to encode the signal amplitude.

A survey of the different types of display devices is presented in Chapter 2. The advantages, disadvantages and the compatibility of these devices with this kind of application are also discussed.

Chapter 3 is devoted to a theoretical background review of the radar systems, and a description of the common radar displays. The last section of the chapter discusses the color-coding.

technique, and its application in the raster scan color television display .

A presentation of the system function and general description is given in Chapter 4, followed by the details of the system design and operation.

The experimental procedure for color-code selection, system testing and color convergence adjusting are described in Chapter 5.

Chapter 6 gives the significant results of using the display system for the presentation of radar signals, together with a detailed discussion.

Finally, Chapter 7 contains the conclusions of this work and recommendations for further investigations.

#### CHAPTER 2

#### SURVEY OF DISPLAY DEVICES

#### 2.1 LIGHT EMITTING DIODE DISPLAYS:

The light emitting diode (LED) is a solid state device which is capable of emitting electromagnetic radiation in the visible light region. Devices which emit in the red region of the spectrum are now commercially available and the ability to produce bi- or tri- colors (red; green and yellow) has been also shown [11, 12].

Although LED devices have a role as individual lamps for "on-off" logic indicators, their use in arrays offers a wider range of application. An addressable matrix or a series of addressable elements can be formed using LED devices with each diode representing a location (element). This addressable nature and the high resolution, which can be achieved by these devices, make it possible to construct quite complex alphanumeric and graphic displays. The semi-conductor nature of the LED offers very high reliability and the life of the display device is more than 100,000 hours. Conversely, the LED type of display requires digital signal processing to obtain the correct form of matrix or element address.

A widely-expressed opinion is that LED devices are unlikely to offer an economical large panel display. However, advances in LED displays are not so much related to semi-conductor technology, as to the problems of connecting to the device and to the heat dissipation, when operating in an "all on" mode. Whilst the heat problem is solvable, the connection problem seems to dictate a practical limit to the complexit, of LED displays.

A typical LED matrix could consist of say, an array of 100, by 100 individual diodes controlled by 200 wires [11]. The representation of characters by selecting from an array of straight lines is illustrated by Fig. 2.1. The characters can also be constructed by selection of dots from a dot-matrix as shown in Fig. 2.2 and Fig. 2.3, which illustrates the alpha numeric LED displays.

#### 2.2 LIQUID CRYSTAL DISPLAYS

There has been much interest in the application of the light scattering properties of liquid crystals to the displays required in high ambient light conditions. This could be relevant to a number of radar display requirements.

A liquid crystal display is a monochromatic type which is viewed by scattering incident illumination when it is in the 'on' state (liquid crystals do not emit light), and there is no viewed light when it is in the 'off' state. Construction is achieved quite simply by sandwiching a layer of organic liquid crystal, of approximately 15 µm thickness, between transparent conducting plates typically glass equated on the inner surface with thin oxide. The liquid is normally clear but when a voltage is applied between the plates, turbulence is induced in

Figure 2.1 Seven and nine segments light emitting diode displays.

(a) Seven segment display.(b) Nine segment display.(c) Typical figures.

Figure 2.2 Alpha-numeric displays.

Figure 2.3 Examples of characters construction by selecting dots from a dot matrix of displays.

the liquid, which then appears milky white since it scatters any incident illumination. There are various other effects which may be used, but they all rely on ambient illumination.

The main advantages of a liquid crystal display are that it operates on very low power, it can be viewed under bright lighting, and it can be made as a flat panel for use, as display. The device lifetime is greater than 10,000 hours and although ten times less than that of an LED display, is still adequate. The size of the display is only limited by the fabrication requirements of the glass sandwich construction.

The liquid crystal display device is of a digital nature and a display panel can be addressed using the matrix addressing technique. The complexity of this addressing technique limits the size of the display panel. However, new techniques and materials are emerging and within the characteristics represented above, it is likely that liquid crystals may be in use for special radar displays in the near future [13]. The use of liquid crystal displays to construct different characters is the same as LED displays (Fig. 2-1, Fig. 2-2 and Fig. 2-3)

#### 2.3 PLASMA DISPLAYS:

The plasma display panel is a two dimensional array of bistable light-emitting gas-discharge elements, that exhibit inherent memory and are separated from the orthogonal exciting electrodes by thin transparent dielectric materials. This device is capable of receiving, storing, and displaying digital information in a random-access fashion and is one of the addressable

display devices [ 14 ].

At present, the plasma display is available only in one color which is red. An example of a commercially available plasma display is an alpha/graphic plasma display panel, which has been specially designed for computer-generated information. The plasma display screen (a matrix panel) is actually a thin glass "sandwich" consisting of two glass sheets, each with parallel conductive electrodes applied to their inner surface. The electrodes on the two sheets, intersecting at right angles, form a matrix of potential intersection. glass spacers separate the sheets of glass, and this narrow intervening space is filled with a neon gas mixture. When a voltage pulse is superimposed on any two intersecting electrodes, a gas discharge occurs, forming a spot light. The light dot remains until another voltage signal is applied in a manner to produce cancellation. An additional AC voltage is continuously applied to all electrodes in the matrix panel, providing the "flicker-free" display image with inherent memory.

The display matrix with a total depth of only 0.5 inch is completely transparent, and therefore can be used to display rear projection images. The active display area is 8.5 inches x 8.55 inches with maximum character capacity of 4284 characters. The total number of individually addressable points is 262,144 and the addressing rate is up to 833 characters per second. The display panel is available in the form of 5 x 7 matrix; 7 x 9 matrix; and 10 x 14 matrix. The light spectrum of the plasma display is neon orange. Fig. 2.4 illustrates an alpha/graphic

Figure 2.4 A plasma display terminal for computer general information and an example of the display capabilities.

plasma display terminal and examples of the display capabilities [15].

#### 2.4 MONOCHROMATIC CATHODE RAY TUBE DISPLAYS

The cathode ray tube (CRT) is the most common display device used for radar indicators because of its flexibility, resolution, dynamic range, and simplicity of hardware relative to other display techniques. In particular, the CRT display lends itself ideally to the display of large amounts of information in general, and can be used for a wide number of different types of radar information [3, 10, 11, 13, 16-23]. The display has large capacity and is commercially available at relatively low cost.

The CRT consists of an electron-emitting element, or cathode, with an electronic beam-forming and control structure. The electron beam is focused and positioned on a phosphor by either electrostatic or magnetic fields. The energy of the electron excites the particles of a phosphor screen which reemits the energy as light. The color of light and storage (or decay rate of emission) depend on the properties of the phosphor. Brightness of the spot may vary smoothly over the range from zero light output to the maximum available from the tube, which means that the CRT is wholly an analog device [10].

An example of the monochromatic CRT display is the plan position indicator (PPI) which is the most commonly used display in radar. Other examples of the monochromatic CRT displays used

in radar are the A-scan, the B-scan and the raster scan displays. The first two displays will be discussed in detail in Section 3.3.

An example of the monochromatic CRT displaysis the raster scan black and white (BW) television display. The picture is produced by scanning the face of the CRT. The scanning procedure used employ horizontal linear scanning with the standard scanning pattern including a total of 525 horizontal scanning lines in a rectangular frame having an aspect ratio of 4 to 3. The frames are repeated at a rate usually 30 per second. Two fields are interlaced in each frame; the first containing all the odd-number scanning lines and the second containing all the even-number scanning lines.

The geometry of the standard odd-line interlaced scanning pattern is illustrated in Fig. 2.5. The scanning beam starts at the upper left corner of the frame and sweeps across the frame with uniform velocity to cover all the picture elements in one horizontal line. At the end of each trace, the beam is rapidly returned to the left side of the frame as shown by the dashed line. The horizontal lines slope downward in the direction of scanning. The slope of the horizontal line trace from left to right is greater than the slope of the retrace from right to left. Thus, the beam is continuously deflected downwards as the scanning proceeds. At the bottom of the field, the vertical retrace begins, and the beam returns to the top of the frame to begin the even-numbered field. The vertical "fly-back"time is very fact compared to the trace, but slow compared

Figure 2.5 The odd and even interlaced scanning procedure for television display.

to the horizontal scanning speed, therefore, some horizontal lines are produced during the vertical fly back.

All odd-number fields begin at point A and all evennumber fields begin at point C as shown in Fig. 2.5. With

a separation of one-half line, and the slope of all lines

being the same, the even-number lines in the even fields fall

exactly between the odd-number lines in the odd field [24].

#### №.5 COLOR TELEVISION DISPLAYS:

Visible light consists of a small interval in the spectrum of electromagnetic radiation with all visible colors contained in a spectrum ranging in wavelength from 400 to 700 millimicrons. Although we name the colors of the rainbow red, orange, yellow, green, blue, indigo, and violet, these are merely the most obvious hues. Several huncred variations in color can be distinguished, even by a comparatively untrained observer.

A beam of white light passed through a prism, splits up into a color spectrum. Conversely, if a color spectrum is passed through a prism, the reverse process takes place and the spectral colors are recombined to form a beam of white light.

A beam of white light can also be formed by combining a minimum of three colored lights, which are called additive primaries. The most useful additive primaries are red, green and blue, and these are the primary hues that are utilized in color television. These three primaries allow the formation of the maximum range of hues when blended in various proportions. Additive primaries must not be confused with the subtractive

primaries used in printing processes and in paintings. Subtractive primaries are viewed by reflected light, and the most useful subtractive primaries are red, yellow, and blue colors.

Technically, white is not a color, but rather is light that is free cf color. Black is defined as the absence of light [25].

The Color CRT used for the color television monitor, employs three independent guns, called the 'red', 'green' and 'blue' guns. Three input signals are applied to them and controlled by the horizontal and vertical deflection systems. All of the guns produce an electron beam, that is focused to the phosphor screen such that each beam produces one of the three colors at certain point, where the mixing of the three colors forms other colors.

Up to now, the color television monitor is the only display device which can provide a large number of colors, a large capacity and a relatively low cost. In addition, the color television monitor is recommended, in most of the cases, for the presentation of large amounts of information in color [3, 11, 12, 16].

#### CHAPTER 3

# AIR TRAFFIC CONTROL RADAR AND RADAR DISPLAYS

#### 3.1. FUNDAMENTALS OF PULSED RADAR

Radar is an electromagnetic technique for detecting and locating objects. It operates by transmitting a particular type of electromagnetic waveform and detecting the nature of the echo signal. The word radar is a contraction of the word radio detection and ranging.

A pulsed radar [ 19, 20, 26, 27] transmits a relatively short burst of electromagnetic energy, after which the receiver is turned on to listen for the echo. The echo not only indicates that a target is present, but the time that elapses between the transmission of the pulse and the reception of the echo is a measure of the distance between the radar and the target which is called the range (R). Comparison between the returned signal and the transmitted signal also yields information about the size and relative motion of the target with respect to the radar.

The basic principles of a pulsed radar system may be demonstrated by describing the operation of a typical system, shown by the block diagram Fig. 3.1. The synchronizing generator generates a series of narrow sync pulses, or timing pulses, at a rate called the pulse repetition rate (Fig. 3.2 a). The time interval, T, is called the pulse repetition interval (PRI), and

Figure 3.1 Block diagram of a pulsed radar.

the corresponding frequency is called the pulse repetition frequency (PRF). These sync pulses turn on the modulator which pulses the transmitter with a series of pulses with certain pulse width Tas shown in Fig. 3.2.b. For example, a pulsed radar for aircraft surveillance may generate a repetitive train of short pulses, each of approximately one microsecond duration, at a PRF of several hundred per second. If an accurate range measurement is required, the transmitted signal should occupy a wide spectral bandwidth, as does, for example, a short pulse.

The transmitter generates a modulated RF pulse (Fig. 3.2.c) and sends the pulses through the transmit-receive switch to a narrow beam antenna where they are radiated. The narrow beam characteristic of the radar antenna not only permits more energy to be concentrated on the target but also permits a measurement of the target azimuth because of the localization of the energy in space. A common antenna is usually used for both transmitting and receiving.

Reflecting objects, or targets, intercept and re-radiate a portion of the radar signal and a small amount returns in the direction of radar. Some of the returned signal is collected by the antenna and detected by the receiver.

. If the radar transmitted power is denoted by  $P_t$ , and the antenna has a transmitting gain equal to  $G_t$ , then the power density at a range R from radar is equal to  $(P_tG_t/4\pi\,R^2)$ . Assuming that the target cross section is  $\sigma$ , then the power re-radiated in the direction of the radar is  $(\sigma P_tG_t/4\pi\,R^2)$ . This means that the

Figure 3.2 Typical pulsed radar timing diagram (same time scale).

reflected power density at the radar antenna is  $(\sigma P_t G_t/(4\pi R^2)^2)$ . Finally, if the antenna has an effective aperture area equal to  $A_r$ , then the received power  $(P_r)$  is given by the equation:

$$P_{\mathbf{r}} = \frac{P_{\mathbf{t}} G_{\mathbf{t}} \sigma A_{\mathbf{r}}}{(4 \pi R^2)^2}$$

(3.1)

This equation is one form of what is called "radar equation" which can take other different forms such as:

$$R_{\text{max}}^{4} = \frac{P_{t} G_{t} c A_{r}}{(4 \pi)^{2} S_{\text{min}}}$$

(3.2)

where R is the maximum radar range and  $S_{\min}$  denotes the minimum detectable signal power of the radar receiver.  $R_{\max}$  is defined as the distance beyond which a target can no longer be detected.

Another form of the radar equation can be obtained by relating  $G_t$  and  $A_r$  in the case of using a common antenna for both transmitting and receiving. If  $\lambda$  is the wave length of the transmitted signal, then  $G_t = 4\pi A_r / \lambda^2$ , since the effective aperture area is the same for transmitting and receiving. By introducing this into equation (3.2), another form of the radar equation can be obtained:

$$R_{\text{max}} = \frac{P_{\text{t}} A_{\text{r}}^2 \sigma}{4 \pi \lambda^2 S_{\text{min}}}$$

(3.3)

The above equations are actually simplified forms for describing the range performance which do not include the various losses which can occur in a radar. The mirimum detectable signal can be expressed in terms of the signal-in-noise ratio (S/N) required for reliable detection and the receiver noises. If P is the power level of the noise in the receiving system, then the signal-to-noise power ratio can be defined as:

$$\frac{S}{N} = \frac{P}{P}$$

which implies

$$P_r = \left(\frac{S}{N}\right)^P n$$

and the minimum value of  $P_r$  that can be detecte; is the value of  $S_{\min}$  which means that  $S_{\min}$  can be expressed as:

$$S_{\min} = (\frac{S}{N}) P_{\min}$$

A fast acting switch called the transmit-receive (TR) switch (Fig. 3.1) disconnects the receiver during transmission. After the passage of the transmitted signal, the TR switch reconnects the receiver to the antenna. Another switch called anti-transmit-receive (ATR) switch acts on reception to channel the received signal power in to the receiver. In the absence of the ATR, a portion of the received power would be dissipated in the transmitter rather than enter the receiver. The TR and the ATR are together called the duplexer. If separate antennas are employed for transmitting and receiving, a duplexer may not be

necessary if the isolation between the two separate antennas is sufficiently large.

The RF amplifier is the first stage of the radar receiver. The mixer and local oscillator (LO) convert the RF signal to an intermediate frequency (IF) since it is easier to build high gain narrow band amplifiers at the lower frequencies. A typical if amplifier might have a centre frequency of 30 or 60 MHZ and a bandwidth of one or two MHZ.

The received and IF signals are illustrated by Fig. 3.2 (d, e, f). The RF pulse modulation is extracted by the detector and amplified by the video amplifier to a level where it can operate the indicator. Sync pulses are also applied to the indicator. Target positional information is obtained from the direction of the antenna and is used to properly display the co-ordinates of the target location. Two of the most common forms of indicators (19, 20) using the CRT are the A-scope and the plan position indicator (PPI), as described in Section 3.3.

#### 3.2 AIR TRAFFIC CONTROL RADAR:

The air traffic control radar is a pulsed air search radar which is assigned to cover a given volume of space and is expect—. ed to detect and locate aircraft within this volume and those entering it [ 26 ].

The airport and airways surveillance radar (AASR) is one kind of an air traffic control radar. A typical example of AASR system is the Raytheon Company Airport and Air Ways Surveillance Radar AASR-1 [28, 29]. AASR-1 system is an air search radar

system with a maximum range of 150 miles and a frequency range of 1220-1350 MHZ. The pulse repetition rate is 400 pulses per second with a pulse length of a 2 micro seconds. The search for returning echoes is accomplished by continuous rotation of the antenna at one of several speeds such as 6.9 and 12 rpm. The antenna beamwidth at half-power points is 1.35 degrees horizontal and 6.50 degrees vertical.

A second example of air traffic control radar is the airport surveillance radar (ASR). Usually, ASR has less range than AASR since ASR is assigned for the detection and location of aircraft around the airport only, but the operating environment of AASR includes airways in addition to the airport. A typical ASR is the ASR-803 which is also a Raytheon Company radar [29]. The frequency range is 1250-1350 MHZ and the pulse repetition frequency is 800 HZ with a pulse length of 1.1 microsecond. The antenna rotation speed is 12 rpm and the antenna beam width is 1.25 degrees horizontal. The radar maximum range for aircrafts is 80 miles.

#### 3.3 COMMON DISPLAYS FOR RADAR:

The purpose of a radar display is to present the information contained in the radar echo signal in a form suitable for interpretation by the operator. The display may be connected directly to the video output of the radar receiver. However, if the information available from the radar signal is obtained at a rate which is greater than the operator can assimilate, automatic data processors such as digital computers may be needed to

interpret the radar data, and display only the condensed information. This is what is called the synthetic display of radar signal [10, 30]. Signals which are displayed when they become available are called real time signals.

The most common form of radar display is usually some form of CRT. There are two basic methods of displaying information on a CRT. The first method is the deflection modulated CRT such as the A-scope. In this type of display, targets are indicated by the deflection of the electron beam. The second display method is the intensity-modulated CRT. An example of the second type is the PPI scope which is normally dark in the absence of a target, and the target is indicated by intensifying the beam and presenting a luminous spot on the face of the CRT. In general, deflection modulated scopes are better adapted to making range or angle measurements. On the other hand, intensity-modulated displays have the great advantages of presenting data in a convenient and more easily interpreted form.

The various forms of displays which are used in radar systems [10, 13, 19, 20] are illustrated in Fig. 3.3. The common displays are the FPI, the A-scope and the B-scope. The FPI, which is the most commonly used display in radar, maps the target in angle and range on a polar display. The target echo amplitude is used to modulate the electron beam intensity as the electron beam is made to sweep outward from the centre with range. The ceam rotates in angle in response to the antenna position and targets are indicated as bright spots (called blips). The A-scan display is similar in operation to the normally-used

Figure 3.3 Common CRT radar displays.

oscilloscope. It displays the target amplitude (y-axis) vs-range (x-axis), as shown in Fig. 3.3, and no angle information is shown. Signals are applied to the vertical deflection circuit, so that radar targets appear as vertical spikes alon, a horizontal line, which represents the range. The B-scan display is an intensity-modulated display and it is sometimes used with sector scanning radar. The vertical deflection is proportional to the range and the horizontal deflection is proportional to the azimuth. Targets are presented as bright spots (Fig. 3.3)

## 3.4 COLOR-CODED TELEVISION DISPLAY FOR RADAR:

#### 3.4.1 Color-Coding Technique:

A color-coding technique can be designed to encode the signal amplitude to a set of different distinguishable eclors. Each color can represent an interval on the amplitude scale depending on the code size and the type of application. A possible technique is to divide the signal level between the zero and the maximum possible amplitude into equal intervals, and to assign a color for each interval. This is the same as digitizing the signal amplitude with each color corresponding to a digital number, and the number of bits being determined by code size. For the binary number system, 2<sup>n</sup> colors (code size) corresponds to nobit binary numbers starting at zero and rangingupto(2<sup>n</sup> - 1) as the signal level increases from zero to the maximum value. The set of colors employed in the color-coding technique is called the "color code".

## 3.4.2 Cclor-Coded Display

A display system which applies the previously described color coding technique, using a color television monitor, is presented in this thesis. The color-coded display system employs sixteen different colors as the color code. The design and construction of the system is described in Chapter 4, and the presentation of radar signals by the display system is demonstrated in Chapter 6. Fig. 3.4 illustrates the color coding technique applied to radar signal and one selection for the color code.

The wide range of colors provided by the color television monitor makes it easy to select the best sixteen distinguishable colors available. A unique color represents every sample of the input signal (Fig. 3.4). This provides the ability to recognize the level interval in which the signal belongs at certain time or range. This range, in turn, corresponds to positions on the raster scan of the color television monitor.

# 3.4.3 Advantages of Color-Coded Display:

The color-code can be selected and arranged to suit the nature of the displayed information, or to reflect certain features to make the data interpretation easier. This concept is illustrated by the example shown in Fig. 3.5 where the low signal levels are represented by dark colors such as black, purple and blue, while the high levels are represented by the bright colors such as white, orange, red and yellow. This aids in the discrimination between noise and targets since noise will

Figure 3.4Color-coding technique for radar signal and an example of the color code

Figure 3.5 Probability density functions for typical radar signal with color coding showing sixteen colors.

Ç.

be represented by a known set (range) of colors, and signal due to target will fall in a different range of colors.

This technique, with the previously mentioned advantages; can improve the performance of radar systems especially air traffic control radar. It makes the detection and identification of aircraft, in the existence of noise, easier since targets and noise are represented by colors which belong to different color ranges. In addition, the use of color in the presentation of radar information assists in making data interpretation and operator response faster which is essential in air traffic control radar.

#### CHAPTER 4

# THE DESIGN AND CONSTRUCTION OF THE COLOR-CODED DISPLAY SYSTEM

## 4.1 SYSTEM FUNCTION AND BASIC CONCEPTS:

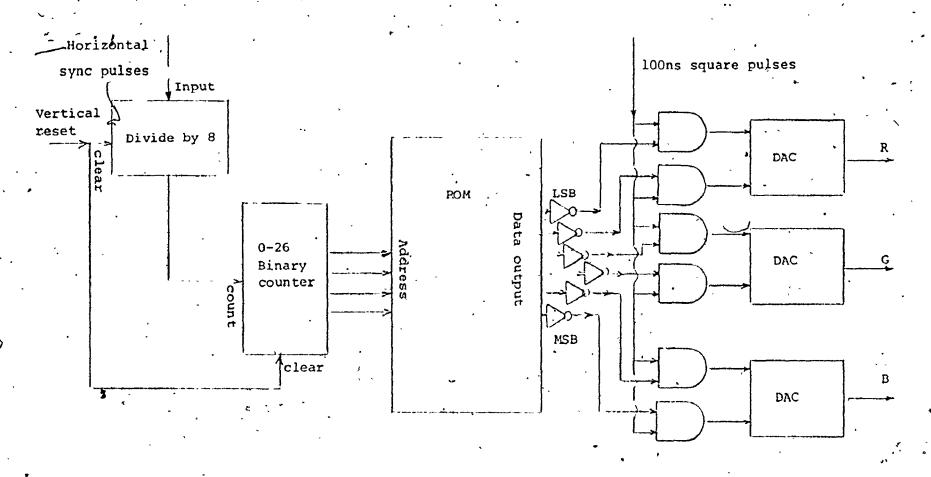

The function of the display system (Fig. 4.1) is the synthetic display of signals from sources such as radar, sonar and meteorological satellites, in real time, employing a color-coding technique. The signal is encoded in amplitude using sixteen different colors to present information on the raster scan of the color television monitor. Features are added to the system to display the colors employed in color coding in order to compare the displayed data with the color code.

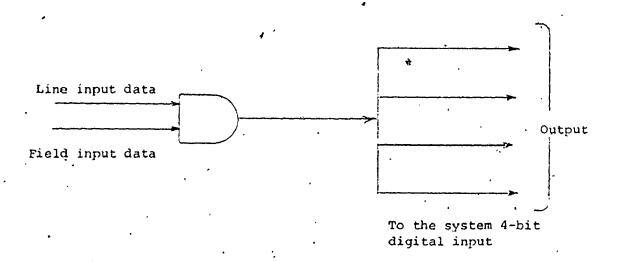

The interfacing function between the input signal, in real time, and the display is performed by five major subsystems (Fig. 4.1). These subsystems are input-memory interface; addressing and timing circuit; random access memory (hAM) system; memory-display interface and sync generator. The memory stores data and allows the interface between the real time processes and the synthetic display of data. The other mentioned subsystems perform three duties: 1) it controls the flow of data from the input to the memory and from the memory to the output; 2) it provides the interfacing signals required between the memory and the external circuitry; and 3) it color encodes

ころからる でんしゅかのだいかないではないないないないない

Figure 4.1 Block diagram for the color-coded display system for radar signal.

the input signal amplitude according to certain selectable coding arrangement.

Digital circuitry and digital random access memory are employed in the system design. The digital system, in this type of application, is capable of providing a picture of definable quality and within the constraints imposed by storage capacity, theoretically, any required resolution can be achieved. The digital memory is perfectly uniform and the stored signal can be read out at high signal to noise ratio. With all these advantages, the digital system provides a high quality stored display [22].

The flexibility of digital storage allows the same memory to be alternately used for different resolution, codes and different system modes. Also, a fast digital memory makes the transformation of the input data format to the TV raster scan format a straight forward process.

Digital signal processing can be achieved if a processor can communicate with the stored data. This can be attained in the display system by introducing a microcomputer which receives instructions by the operator. A selectable signal processing technique can be applied by executing one of several stored routines. The microcomputer can also contribute by controlling the system and adding more flexibility to the system function. This is because the digital system is easy to expand and simple to integrate with existing computer installations [31].

#### 4.2 SYSTEM DESCRIPTION AND OPERATION

#### 4.2.1 General Description

A detailed block diagram of the color-coded display system is shown in Fig. 4.1. The system incorporates a color television menitor as a display and a large scale RAM system. The input-memory interface is divided into two blocks, the analog to digital converter (ADC), and the ADC-memory interface. The color-encoder and the memory-color encoder interface perform the function of the memory-display interface. The addressing and timing circuit is interconnected with the other blocks to address the stored data and control the system operation. The sync generator supplies sync pulses to the color television monitor, the memory-color encoder interface, and the addressing and timing circuit.

The input real time signal can be either in analog or digital format. In the first case, it is sampled and digitized by the ADC at a selectable sampling rate. This sampling rate is controlled by sampling clock pulses fed to the ADC. In the second case, digital data and its associated sampling clock pulses are applied directly to the ADC-memory interface.

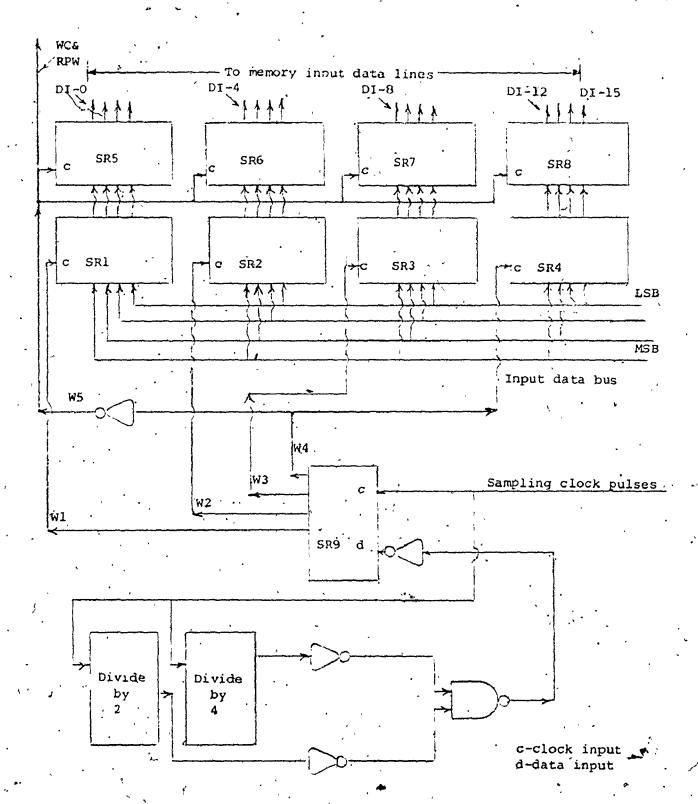

The ADC-memory interface facilitates the storing of data fed to the memory with the help of the addressing and timing circuit. The latter performs the addressing function for toth writing data in, and reading data from the RAM system. In addition, the addressing and timing circuit controls the switching between different modes of operation and provides the required interfacing signals to the memory.

The direct memory access (DMA) technique is used to store the data in the RAM system. The same technique is used to read the data from the RAM system through the memory-color encoder interface. The data are then fed to the color-encoder which encodes the data into a set of colors, called the color code, which represents information on the raster scan of the color television monitor. The output format is described in details in the next section.

A sync generator provides the required scanning sync signals for the color television monitor, and clock pulses controlling reading the data from the memory (system sync). It also contributes in generating general reset pulses for the display system.

## 4.2.2 System Capacity and Sampling Area

The system capacity is defined as the total number of input samples represented on the raster scan of the color television monitor. In the case of displaying radar data, the capacity is equal to the number of azimuth segments multiplied by the number of range samples as shown in Fig. 4.2. The area covered by these samples is called the sampling area, which is bounded by the range values  $R_1$  and  $R_2$ ; and azimuth values  $\theta_1$  and  $\theta_2$ . This sampling area can be expanded and presented on the raster scan of the color television monitor with the azimuth segments represented by horizontal data lines (horizontal data lines means the horizontal lines representing different information on the raster scan of the color television monitor).

できるとは、大きなないのでは、大きなないのでは、大きなないのできないのできない。

Sampling area boundries

Representation of radar signal samples on the raster scan of the color television monitor.

Figure 4.2 Sampling area and output format.

The range samples (4-bit words) in each azimuth segment are represented by data points on the corresponding data line (Fig. 4.2). Thus, the system capacity determines the maximum memory capacity requirements and the display resolution. (The display resolution is defined as the number of data horizontal lines multiplied by the number of data points of every data line.)

The maximum capacity of the display system described here is 512 x 512, but construction was based on capacity of 256 x 512 as determined by the available memory capacity. The 256 azimuth segments are represented by 256 horizontal data lines. Data represented by horizontal lines are repeated for the odd and even interlaced fields. Thus the two fields are identical.

Another input signal, which is called azimuth sampling pulses is applied to the system to control the sampling process. This signal is generated from radar system timing pulses illustrated by Fig. 4.3. These pulses are the azimuth reference pulses (ARP) and the radar sync pulses (transmission pulses). The radar sync pulses are fed to an external circuit [29] which can be used to reduce the frequency by any selectable integer as described later. This output, from the circuit, is referred to as the modified radar sync pulses. The external circuit is also used to generate the azimuth sampling pulses which sample the azimuth sector between the values  $\theta_1$  and  $\theta_2$  into equiangular segments (The number of azimuth segments in

Figure 4.3 Radar sync pulses, azimuth sampling pulses and sampling area.

our case is 256). The azimuth sampling pulses are generated such that they are synchronous with the modified radar sync pulses but delayed by the time corresponding to range  $R_{\gamma}$ .

The selectable integer mentioned above depinds on the required increment of angle between two consecutive azimuth segments, and on the speed of the rotation of the radar Also, the antenna beamwidth affects the selection of the value of the increment of angle between the azimuth segments. As an illustrative example, let the radar PRF be 1000 pulses/second and the antenna beamwidth be 2.4 degrees. If the speed of rotation is 60 degree/second, then the antenna will rotate an angle of  $\underline{60} = 0.06$  degrees, between any two sync pulses (two transmissions). Thus, the beamwidth is 40 times the increment 0.06 degrees. In other words, 40 transmissions will occur while the radar antenna beam crosses certain point. If the increment between azimuth segments is chosen to be half that of the antenna beamwidth (i.e. the beam hits each point twice) then the modified radar sync pulse frequency must be 1 that of the radar sync pulses. This corresponds to dividing the radar PRF by the integer number 20.

For every azimuth segment, the range between the value R<sub>1</sub> and R<sub>2</sub> is sampled 512 times at the rising edges of the sampling clock pulses. The relation between sampling clock pulses and azimuth sampling pulses is illustrated in Fig. 4.4. The rate of the sampling clock pulses is adjustable according to the band width of the input signal in order to satisfy the

Range samples

Figure 4.4 Sampling in range.

Figure 4.5 Switching between modes of operation and its relation with azimuth sampling and general reset of the display system.

sampling theorem [32].

· The sampling area boundaries are determined and specified to the display system by the ARP, the azimuth sampling pulses, and the sampling clock pulses. This is since the delay time between the azimuth sampling pulses and the radar sync pulses determines the value of R1. Also, the azimuth value at which the azimuth sampling pulses starts is the The angle  $\theta_2$  is equal to the azimuth value corresponding to the last pulse of the azimuth sampling pulses. The range R, is determined by R, and the time required to store 512 range samples in the system (this time corresponds to certain range value), which depends on the rate of the sampling clock pulses. This means that the sampling area can be changed by adjusting the delay and rate of the azimuth change pulses and the rate of the sampling clock pulses, for the same system capacity. In addition, the sampling area can be moved in radial and angular directions by changing  $R_1$  and  $\theta_1$ . This is possible by adjusting the external circuit which generates the azimuth sampling pulses. The total area covered by the samples can be changed by changing range and azimuth sampling rates.

# 4.2.3 Timing and Modes of Operation

System timing and display sync pulses are controlled by a crystal oscillator of frequency 25 MHZ, called the master clock. It provides a highly stable frequency which is necessary for this type of system. By using a master clock, the television raster scanning pulses are synchronized with data which

are read out of the memory to the color-television monitor input. This synchronization process is important for a stable and flicker free picture.

There are two modes of the system operation, the first is the writing mode of operation in which fresh data are stored in the memory. The operator starts this mode using a manual operating switch which has two different positions. The first position is for starting the system operation, which automatically starts the writing mode of operation. The second is for stopping the system operation. The writing mode of operation ends automatically after the proper number of input samples are stored in the memory which is  $256 \times 512 = 131072$  samples, in our case. The second mode is the reading mode of operation in which data are displayed on the raster scan of the color television monitor by reading data out of the memory. This mode starts automatically at the end of the writing mode of operation and continues until the operator switches the system to the writing mode of operation.

Fig. 4.5 illustrates the timing of the writing and reading modes of operation, and the relation between the azimuth sampling pulses and the automatic switching from the writing mode to the reading mode of operation. A general reset signal is generated with the switching between the two modes of operation, and during the time of flyback of the television raster scanning beam (called the vertical reset) in the reading mode of operation. The vertical reset is necessary for

system synchronization and picture stability.

## 4.2.4 Hardware Implementation of the Display System:

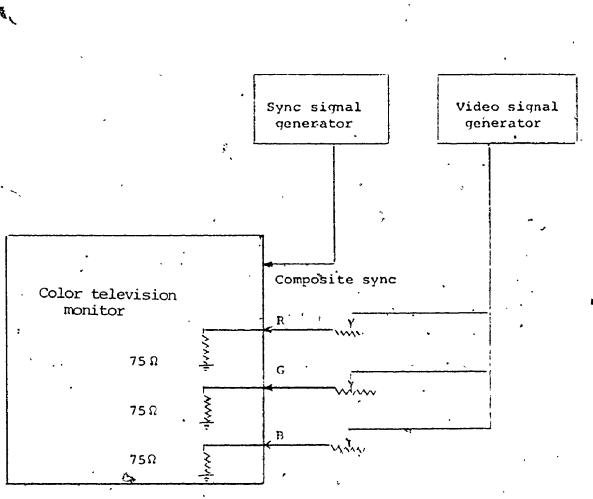

The system is constructed using wire wrapping technique on circuit boards 4.5 inch x 6.5 inch with 42 input/ output terminals, in addition to grounding and power supply terminals. Every block of the block diagram Fig. 4.1, except the display and RAM system, is constructed on a circuit board. The boards are plugged in to one chassis which provides connectors for the interconnections between the boards inputs/ outputs, and +5 volt power supply with external on/off switch. Two external power supplies (+11 and -6 volt) are used for the ADC circuit.

The chassis connectors are connected with the memory interfacing pins through twisted pair wires. Coaxial cables carry the red, green and blue gun input signals to the color television monitor, in addition to the composite sync input. Two external switches are used in the system construction, one for starting the data refreshing and the other to switch between displaying the data or the color code. The hardware details can be found in Appendix 3.

#### 4.3 THE DISPLAY SET:

## 4.3.1 Type and Specifications:

The color television monitor has been chosen for this application since it provides a wide range of colors. This is necessary for implementing a color coding technique. The display system employs a studio color television monitor wdth the screen diagonal of 51 cm. Fig. 4.6 is a photograph of the

Front view

Back view

Figure 4.6 Photographs of the front and back views of the color television monitor

front and back views of the color television monitor. Access to color electron guns and external sync signal input are available in the back through BNC jacks (Fig. 4.6). Detailed characteristics of the color television monitor, according to the operation and maintenance manual, can be found in impendix.

### 4.3.2 Sync Signals for Color Television Monitor:

The standard scanning pattern, for a television system [24] includes a total of 525 horizontal lines. The frames are repeated at a rate of 30 per second with two fields interlaced in each frame. The first field consists of all the odd number scanning lines and the second consists of all even, number scanning lines. This means that the field repetition rate is 60 per second which is the same as the vertical scanning rate.

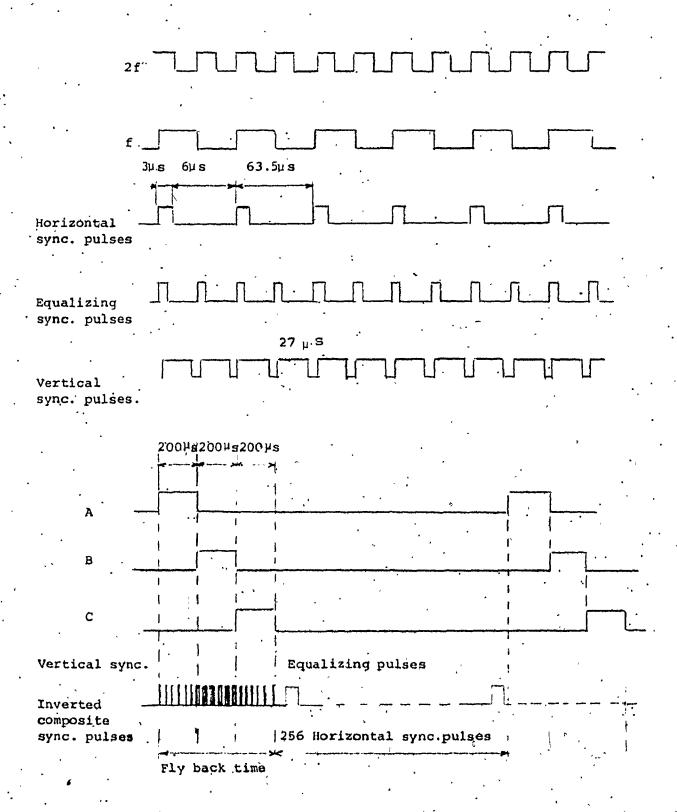

The sync pulses (Fig. 4.7) are timing pulses which control the horizontal and vertical scanning generators. The vertical sync pulses have a frequency of 60 HZ to provide 60 fields per second and 30 frames per second. The sync pulses are designed in this system to employ only 512 horizontal lines of the 525 available lines which makes each field consists of 256 horizontal lines. This means that 256 horizontal sync pulses must be applied to the horizontal scanning generator between each two vertical sync pulses. There is a 5.5 µS duration horizontal pulse every 63.5 µS. Six pulses immediately precede, and six pulses immediately follow the

Figure. 4.7 Synchronization signals for the color television.

vertical sync pulses to compensate for half line intervals. They are called the equalizing pulses and their standard frequency is double the horizontal sync pulse frequency with a standard pulse width half the horizontal sync pulse width. The vertical sync pulses have a total width of approximately 200  $\,\mu S$  and the complete pulses are divided in to 6 individual pulses that provide  $\,$  horizontal sync during the vertical retrace time. The individual pulse has a pulse width of approximately 27  $\,\mu S$ .

Finally, the horizontal, equalizing and vertical sync pulses are combined to form the composite sync pulse train (Fig. 4.7). This composite sync pulse train is then fed to the color television monitor sync input, where the horizontal and vertical sync pulses are separated internally and applied to the corresponding deflection generator.

# 4.3.3 Sync Signal Generator:

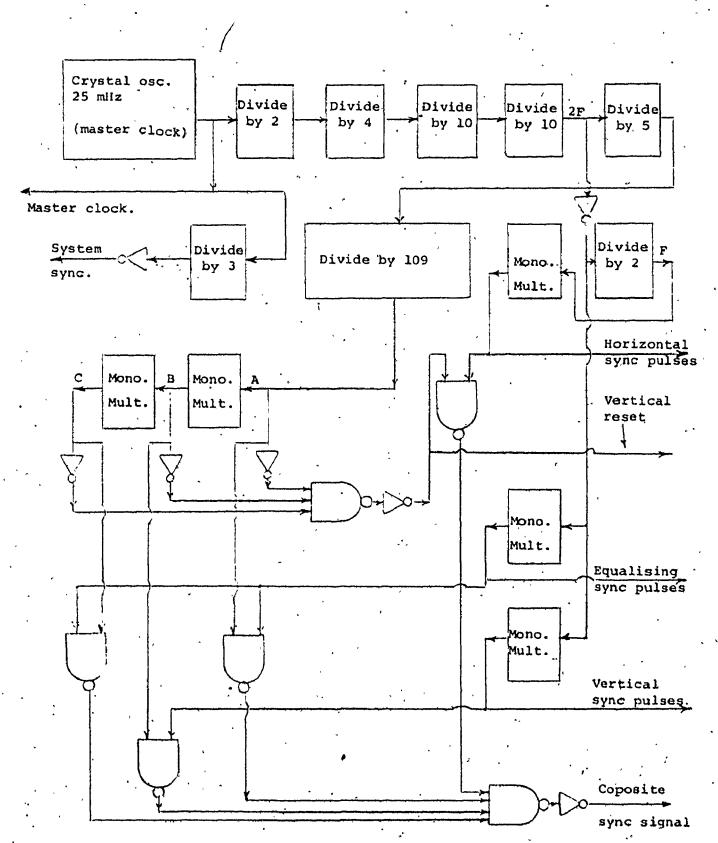

The sync signal generator contains the master clock used to generate all of the sync pulses for the color tele-vision monitor as illustrated by Fig. 4.7. These include the horizontal, the equalizing and the vertical sync pulses. These pulses are combined to form the standard composite sync pulse signal which activates the scanning of the color television monitor.

One of the circuit outputs is the vertical reset pulse signal shown in Fig. 4.7, which is used as a general reset for the display system during the time of the beam fly-back. Also, the clock pulses, which control reading the data

from the memory (system sync pulses), are generated from the master clock pulses by dividing 25 MHZ by three to meet the required data rate.

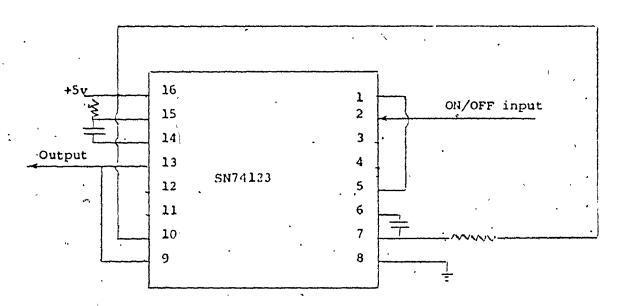

The sync signal generator circuit diagram is illustrated by Fig. 4.8.a. The signal starts at the master clock output and goes through series of frequency dividers. The frequency divide by 109 circuit is shown in Fig. 4.8.b. The different sync signals are generated by the circuit, then the pulse width of each signal is adjusted by means of a monostable multivibrators are used to generate the pulses B and C from A (Fig. 4.8.a).

## 4.4 RANDOM ACCESS MEMORY SYSTEM

Considering the existing commercial storage systems such as discs, shift registers and random access memory systems, it was found that the solid state RAM system is compatible with the writing speed of the display. The access cycle time of the RAM system which is used in the display system is approximately 400 ns while the access cycle time of discs or shift registers are of the order of several milliseconds [16]. The RAM system also has the advantage of inherent addressing flexibility [34] and its non-sequential data access capability reduces the required control circuitry [33]. From the economy point of view, it would seem that since the computer industry is concerned almost exclusively with RAM system for scratch pad memories, further development will concentrate on these devices.

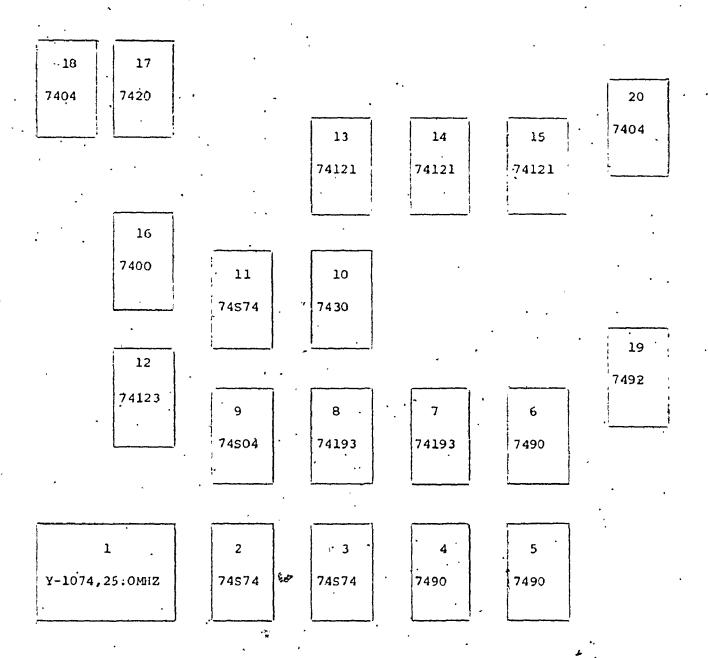

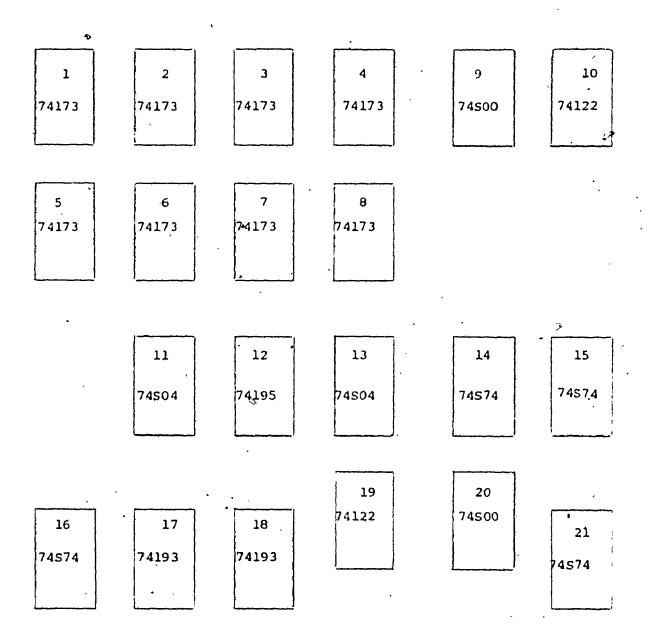

Figure 4.8.a Sync signal generator circuit diagram.

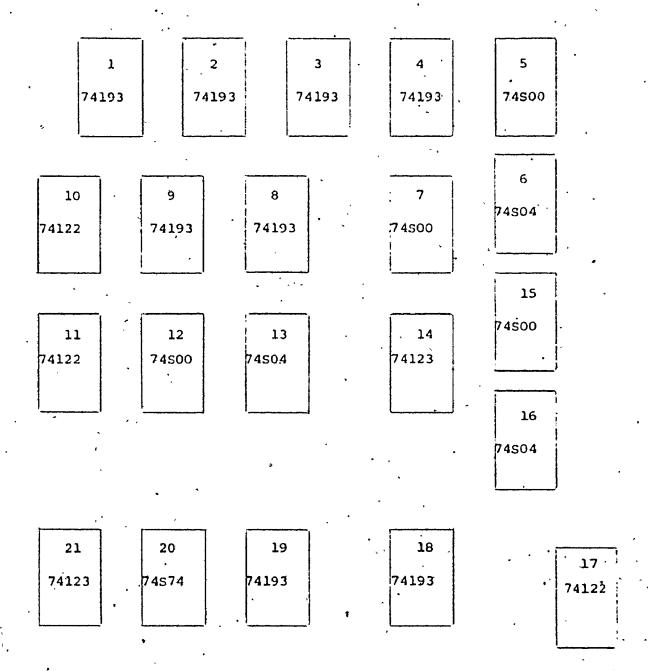

Figure 4.8.b Divide by 109 circuit diagram.

Two new memory technologies may alter the selection of RAM as the optimum memory in the near future. These are the bubble memories and charge coupled devices. Both of these technologies promise high bit packages, high densities and low cost, but they are serial agreess memories. Therefore, more complex associated addressing circuitry is required for their operation in this type of application, offsetting come of their advantages [22]. As well, bubble memories are slower than semi-conductor memories in general; they bridge the gap between the access time in electronic and electromagnetic storage systems [35]. The difference between the access time in electronic and electromagnetic storage system is called the "access gap".

#### 4.4.1 RAM System Specifications and Operation:

The memory system used is a self contained random access semiconductor memory, shown in Fig. 4.9, employing the 3400 N type of RAM unit. The memory system consists of up to four Memory Card Assemblies with a maximum capacity of 32,768 of 18 bit words. Only two cards are available to our display system and each card can be accessed independently.

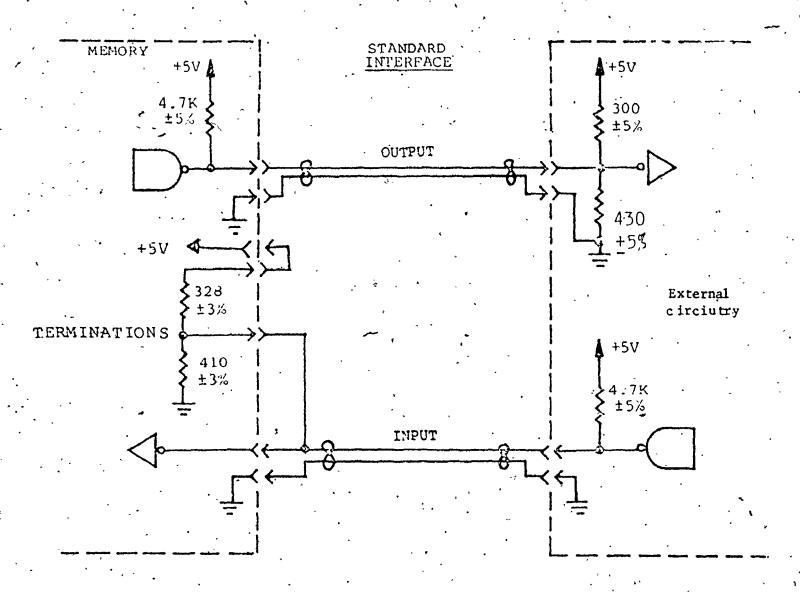

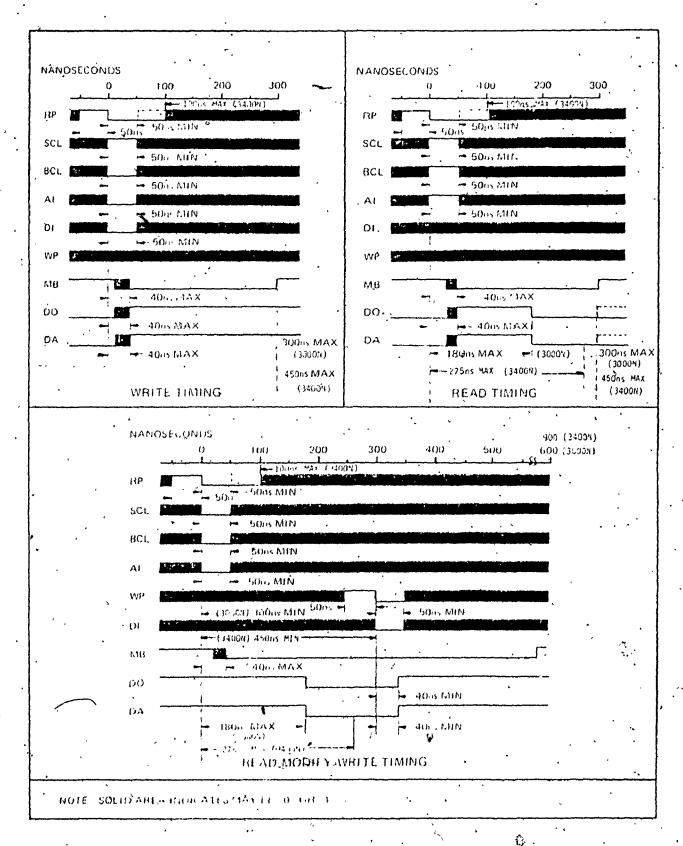

The modes of operation for a card are Read, Write, and Read/Modify/Write (Split-Cycle). Table 4.1 is a list of general specifications of the memory. The interface circuitry is shown in Fig. 4.10.

Fig. 4.11 is the timing diagram of the interface signals with times shown measured at the 50% point of signal transmission. A list of interface signal functions and line

Figure 4:9 MICRORAM semiconductor system

(front panel removed)

Table 4.1 Memory system 3400N Specifications

|     | ITEM                 | SPECIFICATIONS                   |

|-----|----------------------|----------------------------------|

| *   | Type of Memory       | Random access NMOS Semiconductor |

| *   | .Card Configurations | 32, 768 words by 18 bits         |

| *   | Modes of Operation   | Read                             |

|     | •                    | Write '                          |

| •   | <b>.</b>             | Read/Modify/Write (Split Cycle)  |

| *   | Timing:              |                                  |

|     | Read Cycle           | 450 ns                           |

| ;   | Write Cycle          | 450 ns                           |

|     | Read/Modify/Write    | 900 ns                           |

| •   | Access               | 275 ns max                       |

| * , | Interface Circuitry  | Open Collector Output-74S 38TTL  |

| *   | Logic Levels:        | Input-75S XX Series              |

|     | Logic zero           | + 2.5 to 5.0 volts               |

| ,   | Logic One            | 0.0 to 0.5 volts.                |

|     |                      |                                  |

Figure  $4 \cdot 10$  Interface circuitry between the memory and the external system.

Figure 4.11 RAM system 3400N interface signals timing diagram.

loading characteristics is given in Table 4.2. The interface signals are described in more detail with the design of the other circuits which are interconnected with the memory. Appendix 2 contains the details of the RAM specifications, and the connection of the interface connector pins with the external circuitry.

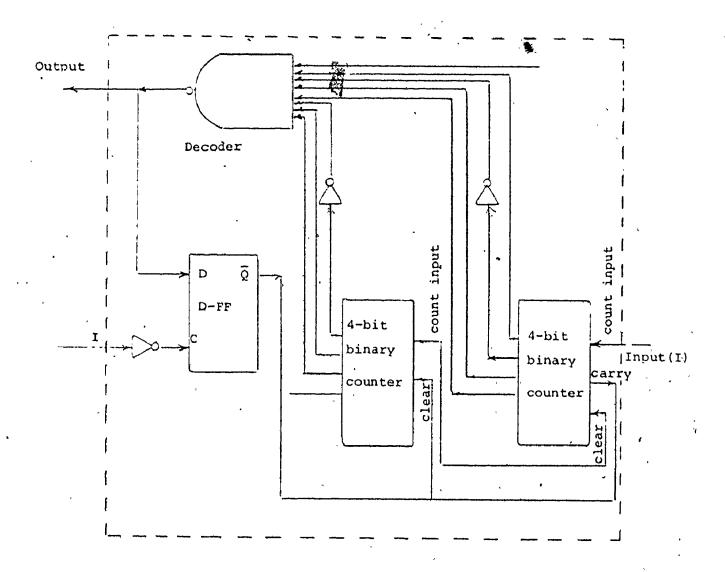

## 4.4.2 Memory Organization:

The memory is organized as a matrix of 16 bit words (two bits left for other purposes) with each word encoded so as to include four adjacent spots of a given TV raster scan lines. Every spot represents a 4-bit data word which is the digital value of an input sample. By handling four parallel channels of data words the data rate is increased four times over that of the maximum rate of the memory. The location of the word to be accessed is specified by the address applied to the memory address lines by the external circuitry.

The required capacity of the memory is determined by the display resolution in terms of the number of samples displayed by the TV raster scan. The display system is designed for the capacity of 256 x 512 = 131072 samples which requires a storage of 37,768 of 16-bit words. One memory card is used by the system and the other card is left for future extension such as to increase the system capacity or to store processed data.

Table 4.2 Descriptions of the RAM system interface signal

| Signal .        | ABBR #        | Type/*per                        | Description                                                                                                                                               |

|-----------------|---------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|