# Fabrication and Characterization of $Si/Si_{1-x}Ge_x$ -Based Double Heterojunction OptoElectronic Switches (DOES) and

Heterojunction Field Effect Transistors (HFET)

by

Stephen J. Kovacic, B.Sc., M.Eng.

#### A Thesis

Submitted to the School of Graduate Studies

in Partial Fulfilment of the Requirements

for the Degree

Doctor of Philosophy

McMaster University

1993

DOCTOR OF PHILOSOPHY (1993) (Engineering Physics)

McMASTER UNIVERSITY Hamilton, Ontario

TITLE:

Fabrication and Characterization of Si/Si<sub>1-x</sub>Ge<sub>x</sub> -Based Double

Heterojunction OptoElectronic Switches (DOES) and Heterojunction

Field Effect Transistors (HFET)

**AUTHOR:**

Stephen J. Kovacic, B.Sc. (University of Waterloo),

M.Eng. (McMaster University)

SUPERVISORS:

Dr. J.G. Simmons

Dr. P.E. Jessop

NUMBER OF PAGES:

xvi, 160

The Si/Si1- $_{x}$ Ge $_{x}$ -Based DOES and HFET

#### Abstract

The fabrication and characterization of the double heterojunction optoelectronic switch (DOES) and the heterojunction field effect transistor (HFET) in the Si/Si<sub>1-X</sub>Ge<sub>X</sub> materials system is described. The significant achievements of this work are summarized below.

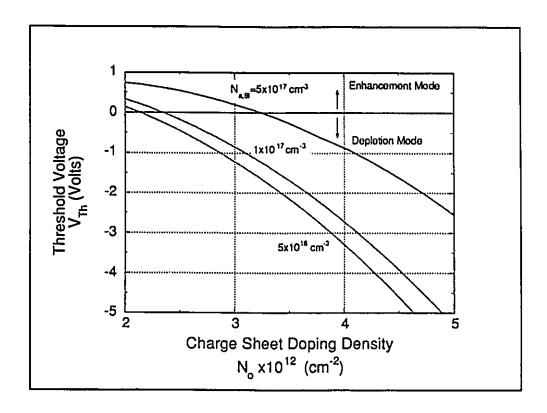

The theory of operation of the DOES and HFET are reviewed. A computer-based, one-dimensional, analytical model is used to calculate the current-voltage characteristics and operational parameters of the DOES. From this, the design of the inversion-channel Si/Si<sub>1-x</sub>Ge<sub>x</sub> heterostructure is shown to contain a manifold parameter space. For example, the switching voltage of the DOES is shown to be extremely sensitive to the magnitude of doping in the charge sheet. In the HFET, the threshold voltage is calculated to have a non-linear dependence on the magnitude of the doping in the charge sheet.

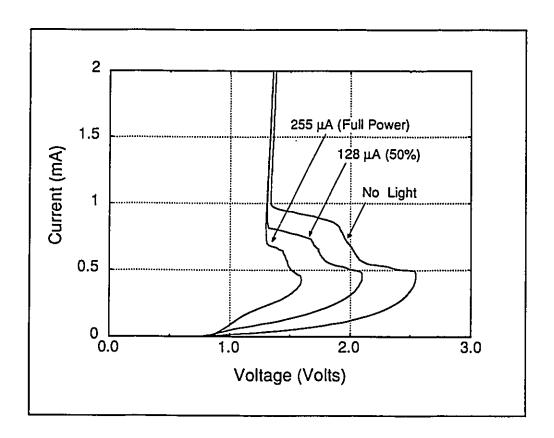

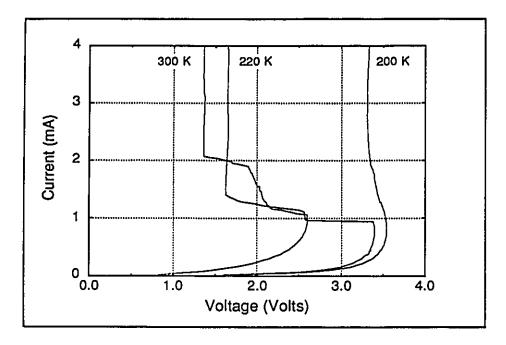

The measured switching voltages and currents compare well with the calculations of the model. Separately, the effects of illumination and temperature on the dc electrical characteristics of the device are investigated. Illumination is seen to reduce the switching voltage and holding current. With decreasing temperature, the switching voltage and holding current are observed to increase. The effects of illumination and temperature are explained as phenomena related to carrier injection (or the lack thereof).

An account of the fabrication of these devices is given in detail. A self-aligned technology for the Si/Si<sub>1-x</sub>Ge<sub>x</sub> -based HFET was developed using the aluminum gate as a mask for reactive ion etching and ion implantation procedures.

Oscillatory electrical behavior of the DOES is examined. Self-induced oscillations are shown to be correlated to the regime of negative differential resistance. The dc current-voltage characteristics of the DOES are demonstrated to be affected by this oscillatory behavior. In addition, an enhancement in the optical emission over a narrow range of drive currents in the DOES is shown to be a result of device oscillations.

Changes in the electrical characteristics of the DOES in response to third terminal current injection are measured for both active layer contact and inversion layer contact. Contact to the inversion layer is shown to be more effective than a third terminal contact to the active layer. These experimental observation are supported by the computer-based model. Concurrent usage of optical and electrical injection to affect the I-V characteristic of the device is demonstrated. Electrical extraction via the third terminal is shown to negate the effect of optical injection.

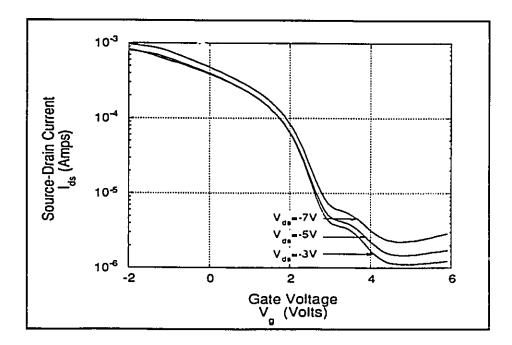

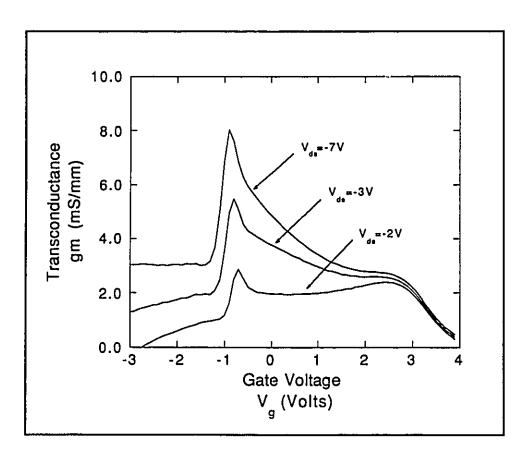

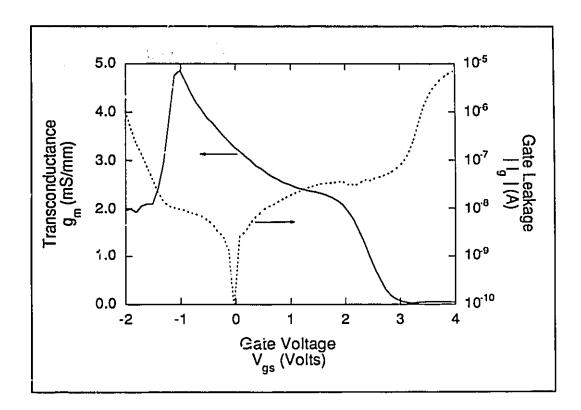

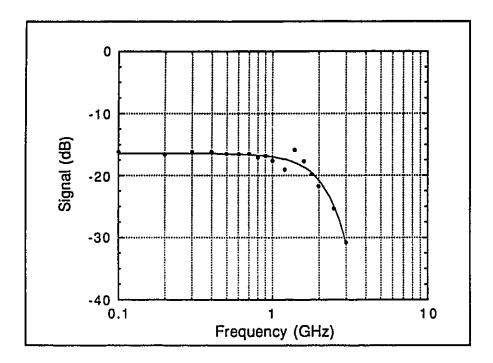

The highest reported transconductance in a Si/SiGe-based metal-semiconductor FET is found in the HFETs reported in this thesis. Peak transconductance of 8mS/mm is measured for a depletion mode device. Subthreshold slope is measured as 720mV/decade and a high frequency 3-dB point for voltage gain is seen to be 1.8GHz.

The suitability of this technology for integration is examined by demonstrating a Reset-Set Flip-Flop which is comprised of two HFETs and a three-terminal DOES. The range of operational voltages for the circuit are shown to be determined primarily by the operational characteristics of the DOES. Gate leakage from the HFET is seen to hinder circuit performance.

# Dedication

125

To Diane, for making it easy.

#### Publications and Presentations

$V_{\mathcal{A}}$

- 1. S.J. Kovacic, J.G. Simmons, J.P. Noël, D.C. Houghton, and S. Kechang, "Si/SiGe Digital Optoelectronic Switch," IEEE Electron Dev. Lett., Vol. 12, p. 439, 1991.

- 2. J.G. Simmons, S.J. Kovacic, K. Song, J.P. Noel, and D.C. Houghton, 1990, "Si/SiGe double heterojunction optoelectronic switch", 37th American Vacuum Society Meeting Proceedings on Si-Based Hetero-Structures, October, 1990, American Vacuum Society.

- 3. S.J. Kovacic, J.G. Simmons, J-P. Noël, D.C. Houghton, M. Buchanan, "Three-Terminal Si/SiGe Digital Opto-Electronic Switch," Electron. Lett., Vol. 28, p. 292, 1992.

- 4. S.J. Kovacic, J.G. Simmons, J.P. Noel, D.C. Houghton, and M. Buchanan, "Three terminal Si/SiGe DOES", Invited Speaker at the Northern Telecom SiGe Mini-Symposium on SiGe Structures, November, 1990, Northern Telecom Electronics Ltd.

- 5. S.J. Kovacic, J.G. Simmons, J.P. Noel, D.C. Houghton, and M. Buchanan, "Three-terminal Si/SiGe DOES", First Graduate Student Conference on Opto-Electronic Materials, Devices, and Systems, June 24-26, McMaster University, Hamilton, Ontario.

- 6. S.J. Kovacic, J.G. Simmons, J.P. Noël, D.C. Houghton, and M. Buchanan, "The inversion-channel Si/SiGe Heterojunction Field Effect Transistor," Electron. Lett., Vol. 28, p. 2234, 1992.

- 7. S.J. Kovacic, J.J. Ojha, J.H. Swoger, J.G. Simmons, J-P. Noël, and D.C. Houghton, "On Transconductance in the p-Channel Si/SiGe Heterojunction Field Effect Transistor," accepted for publication in the Can. J. Phys., Sept., 1992.

- 8. S.J. Kovacic, J.J. Ojha, J.G. Simmons, J-P. Noël, D.C. Houghton, "Gain enhancement in the p-channel Si/SiGe heterojunction field effect transistor," presented at the Sixth Canadian Semiconductor Technology Conference, August, 1992, Ottawa, CANADA.

- 9. S.J. Kovacic, J.G. Simmons, J.J. Ojha, J-P. Noël, and D.C. Houghton, "Modeling and Characteristics of Bistable Optoelectronic Switches and Heterojunction Field Effect Transistors in MBE-Grown SiGe/Si," accepted for publications J. Vac. Sci. Tech., October, 1992.

10. J.G. Simmons, S.J. Kovacic, and J.J. Ojha, "Bistable optoelectronic switches and FETs in MBE SiGe/Si," presented at the Annual Meeting of the American Vacuum Society, November, 1992, Chicago,

e),

- 11. S.J. Kovacic, B.J. Robinson, J.G. Simmons, and D.A. Thompson," InP/InGaAsP Double Heterostructure Opto-Electronic Switch," IEEE Electron. Dev. Lett., Vol. 14, p. 54, 1992.

- 12. S.J. Kovacic, B.J. Robinson, J. Showell, J.J. Ojha, J.G. Simmons, and D.A. Thompson, "An inversion-channel heterostructure for the InP/InGaAsP materials system," presented at the North American Molecular Beam Epitaxy Conference, October, 1992, Ottawa.

- 13. S.J. Kovacic, B.J. Robinson, J.H. Swoger, J.G. Simmons, and D.A. Thompson, "An MBE-Grown InP/InGaAsP Heterostructure for Inversion-Channel Devices," submitted for publication in J. Vac. Sci. Tech., October, 1992.

- 14. S.J. Kovacic, J.J. Ojha, J.G. Simmons, P.E. Jessop, R.S. Mand, and A.J. SpringThorpe, "Optical and Electrical Oscillations in Double Heterojunction Negative Differential Resistance Devices," submitted for publication in IEEE Trans. Electron Dev., October, 1992.

- 15. A. Vetter, S.J. Kovacic, J.G. Simmons, J-P. Noël, and D.C. Houghton, "Demonstration of a Si/SiGe optoelectronic reset-set flip-flop based on an inversion-channel heterostructure," submitted for publication in Solid State Electron., November, 1992.

- 16. S.J. Kovacic, J.G. Simmons, J.-P. Noel, and D.C. Houghton, "Integration of functionalities in the SiGe/Si-based hetero-junction field effect transistor," presented at Annual Meeting of the American Vacuum Society, November, 1992, Chicago.

#### Acknowledgments

Many unselfish individuals have devoted their time and energy to this research. First and foremost, I would like to thank my supervisors - John Simmons, who's competence and experience is rivaled only by his enthusiasm and salesmanship and Paul Jessop, who quietly always gives the most sane advice.

I have worked closely with fellow graduate students Jugnu Ojha and Jim Swoger. Many of our discussions are reflected in this thesis and Jim's labors on modeling are used extensively in Chapter 2.

The excellent technical support of Tony Vetter and Kechang Song is gratefully appreciated. For these fellows 'quitting time' is a moving target.

In Ottawa, at the National Research Council (NRC), J.-P. Noël and Derek Houghton are to be thanked for their expertise in materials growth. I greatly appreciate the painstaking ground work they have done.

Financial support during my time at McMaster has come from the Natural Sciences & Engineering Research Council (NSERC) of Canada and the Ontario Center for Materials Research (OCMR). In addition, the Solid State Opto-electronics Consortium (SSOC) contributed both financial and equipment support during my time at NRC.

# Table of Contents

| CHAPTER      | 1: INTRODUCTION                                      | 1  |

|--------------|------------------------------------------------------|----|

| 1.1          | Technology Directions and System Considerations      | 2  |

| 1.2          | Material Properties of Si/SiGe                       | 6  |

| <b>1.3</b> . | Objectives of the Thesis                             | 10 |

| CHAPTER      | 2: OPERATIONAL THEORY OF THE DOES                    | 11 |

| 2.1          | Current-Voltage Characteristics of the DOES          | 11 |

| 2.2          | The Physical Structure of the Si/SiGe-Based DOES     | 13 |

| 2.3          | Energy Band Diagrams                                 | 16 |

| 2.4          | Charge Equations                                     | 20 |

| 2.5          | Current Equations                                    | 25 |

| 2.6          | Simulations and Predictions                          | 27 |

|              | 2.6.1 Effect of Charge Sheet Doping Density          | 27 |

|              | 2.6.2 Effect of Barrier Layer Doping                 |    |

|              | 2.6.3 Effect of Injection Current                    |    |

| CHAPTER      | 3: OPERATIONAL THEORY OF THE HFET                    | 34 |

| 3.1          | Si/SiGe HFET: An Operational Discussion              | 34 |

| 3.2          | Conduction Equations                                 | 37 |

| 3.3          | Charge in the Conduction Channel                     | 41 |

|              | 3.3.1 Effect of δ-Layer Doping and Dopant Ionization | 41 |

|              | 3.3.2 Effect of Parallel-Path Gate Leakage           | 48 |

|              | 3.3.3 Effect of Gate Leakage on the Active Layer     | 50 |

| CHAPTER | 4:      | HETEROSTRUCTUE           | RE GROWTH &                            |    |

|---------|---------|--------------------------|----------------------------------------|----|

|         |         | DEVICE FABRICA           | ATION                                  | 54 |

| 4.1     | Grount  | and Analysis             |                                        | 55 |

| 7.1     | 4.1.1   | •                        | ;h                                     |    |

|         |         |                          | Micrography of Wafer #951              |    |

|         |         |                          | oscopy of Wafer #951                   |    |

| 4.2     |         |                          |                                        |    |

| 7.2     |         |                          | Cleaning                               |    |

|         | 4.2.2   | _                        | iithography                            |    |

|         |         |                          |                                        |    |

| 4.3     |         |                          |                                        |    |

| 5       |         |                          | sa Etch                                |    |

|         | 4.3.2   | -                        | ling                                   |    |

|         | 4.3.3   | •                        | Lift-off                               |    |

| 4.4     |         |                          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |    |

|         | 4.4.1   |                          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |    |

|         | 4.4.2   | •                        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |    |

|         | 4.4.3   | = * *                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |    |

|         | 4.4.5   | <u> </u>                 | ling                                   |    |

|         | 4.4.6   | =                        |                                        |    |

| CHAPTER | 5:      | TWO-TERMINAL DO          | DES: EXPERIMENTAL                      |    |

|         | •       |                          | SSION                                  | 90 |

| 5.1     | Experi  | nental Procedure         |                                        | 91 |

| 5.2     | -       |                          | eristics                               |    |

|         | 5.2.1   |                          | cs                                     |    |

|         | 5.2.2   | Effect of Illumination   |                                        | 92 |

|         | 5.2.3   | Effect of Temperature    |                                        | 96 |

| 5.3     | Oscilla |                          |                                        |    |

|         | 5.3.1   |                          |                                        |    |

|         | 5.3.2   |                          | Light-Current Characteristics 10       |    |

|         | 5.3.3   | Effect of Parasitic Circ | cuit Elements 10                       | 04 |

| <b>CHAPTER</b> | 6:     | THREE-TERMINAL DOES: EXPERIMENTAL              |     |

|----------------|--------|------------------------------------------------|-----|

|                |        | RESULTS & DISCUSSION                           | 111 |

| 6.1            | Curre  | nt-Voltage Characteristics                     | 112 |

|                | 6.1.1  | Effect of Injection into the Active Layer      | 112 |

|                | 6.1.2  | Effect of Injection into the Inversion-Channel | 114 |

|                | 6.1.3  | Effect of Extraction                           | 116 |

|                | 6.1.4  | Optical and Current Injection                  | 118 |

| 6.2            | Compa  | arison with Simulations                        | 121 |

| CHAPTER        | 7:     | HFET: EXPERIMENTAL RESULTS                     |     |

|                |        | & DISCUSSION                                   | 123 |

| 7.1            | Experi | mental Procedure                               | 123 |

| 7.2            | dc Cur | Tent-Voltage Characteristics                   | 126 |

|                | 7.2.1  | Source-Drain Current-Voltage Characteristics   | 126 |

|                | 7.2.2  | Transconductance Characteristics               | 130 |

|                | 7.2.3  | Effect of Device Size                          | 132 |

| 7.3            | High I | Frequency Characteristics                      | 133 |

| 7.4            | Simul  | ations & Comparisons                           | 135 |

| CHAPTER 8:     |        | DEMONSTRATION OF A Si/SiGe                     |     |

|                |        | OPTOELECTRONIC RS FLIP-FLOP                    | 137 |

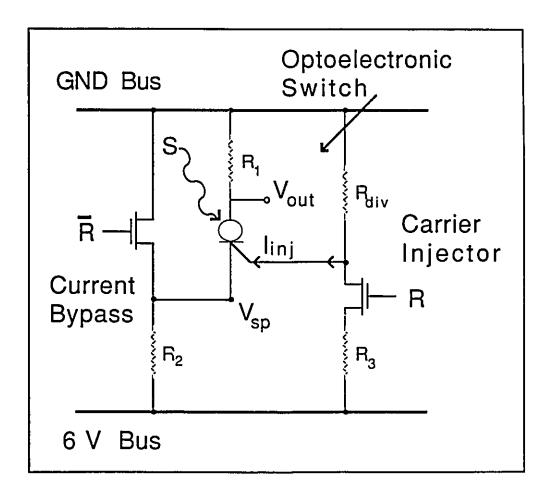

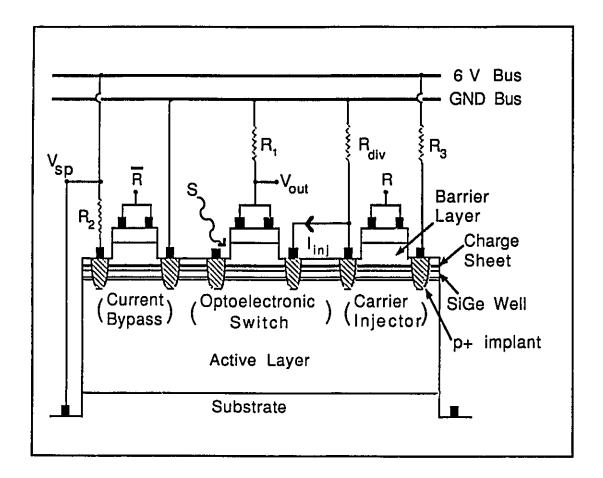

| 8.1            | Circui | t Design and Operation                         | 138 |

|                | 8.1.1  | Optoelectronic Switch Module                   | 140 |

|                | 8.1.2  | Carrier Injector Module                        | 142 |

|                | 8.1.3  | Current Bypass Module                          | 143 |

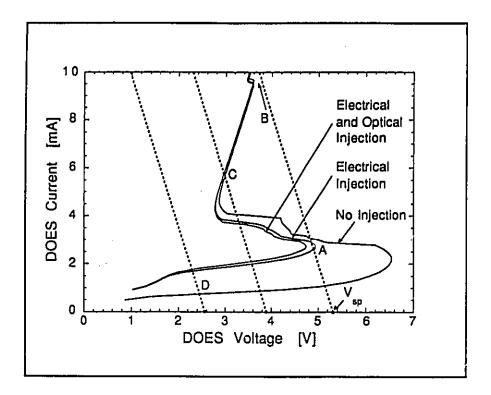

| 8.2            | Result | s and Discussion                               | 144 |

| CHAPTER        | 9:     | CONCLUSIONS                                    | 148 |

| APPENDIX    | A: CURRENT COMPONENTS       | 150 |

|-------------|-----------------------------|-----|

| <b>A.</b> 1 | Barrier Thermionic Currents | 150 |

| A.2         | Recombination Currents      | 151 |

| A.3         | Generation Current          | 152 |

| A.4         | Diffusion Currents          | 153 |

| REFERENC    | 'ES                         | 155 |

1723

# List of Figures

| Figure |                                                                                                                           | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------|------|

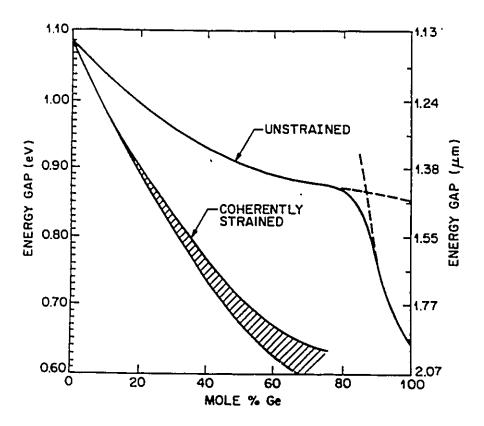

| 1.1    | The lowest energy indirect bandgap of coherently strained Si <sub>1-x</sub> Ge <sub>x</sub> alloys on Si(001) substrates. | 8    |

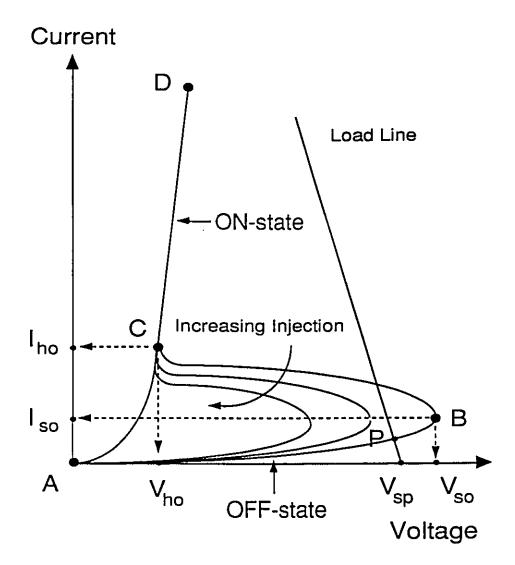

| 2.1    | The hypothetical I-V characteristic of the DOES.                                                                          | 12   |

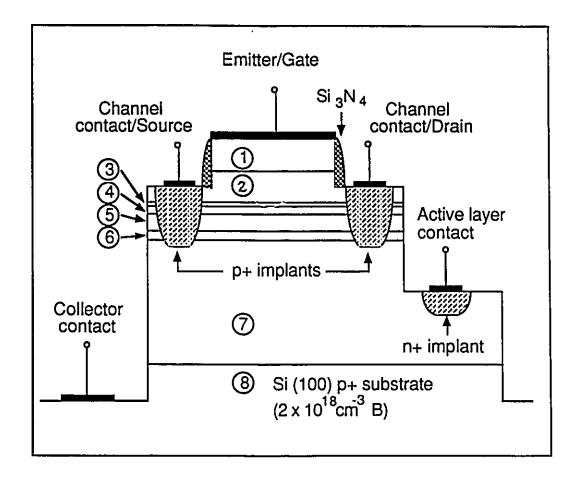

| 2.2    | The target heterostructure used to implement the Si/SiGe DOES.                                                            | 15   |

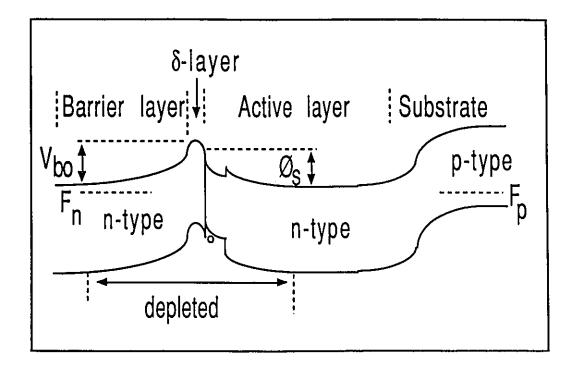

| 2.3    | The schematic energy band diagram of the heterostructure under equilibrium conditions.                                    | 17   |

| 2.4    | The energy band diagram of the heterostructure under forward -bias conditions in the (a) OFF-state and the (b) ON-state.  | 19   |

| 2.5    | The schematic energy band diagram of the heterostructure.                                                                 | 21   |

| 2.6    | A schematic representation of the formation of hole energy levels in the valence band at the n-n heterojunction.          | 24   |

| 2.7    | The calculated $log(J)$ -V characteristics of the DOES with $N_{\mbox{ob}}$ as a parameter.                               | 28   |

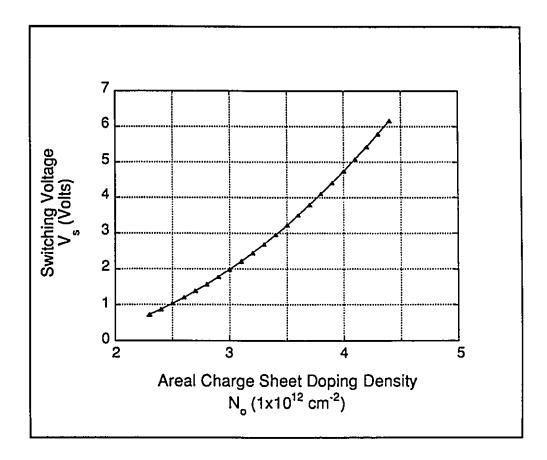

| 2.8    | The calculated switching voltages, $V_{so}$ , as a function of $N_{ob}$ .                                                 | 29   |

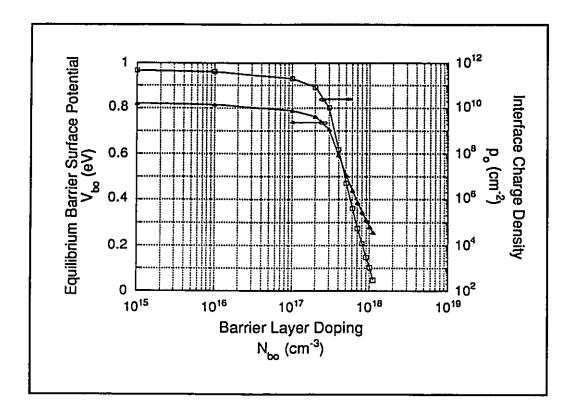

| 2.9    | The calculated dependence of $V_{bo}$ and $p_o$ on $N_{bo}$ .                                                             | 30   |

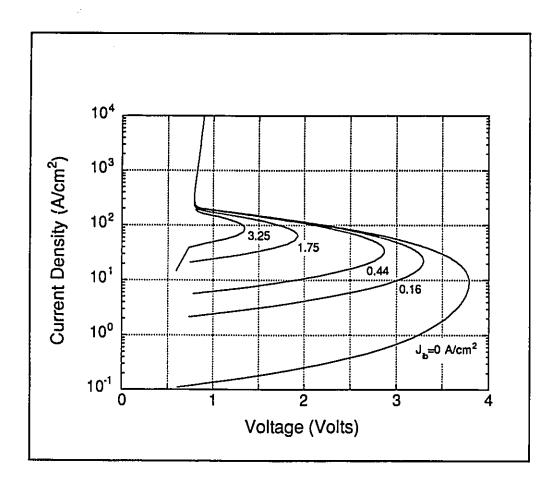

| 2.10   | The calculated log(J)-V characteristic with J <sub>ib</sub> as a parameter.                                               | 32   |

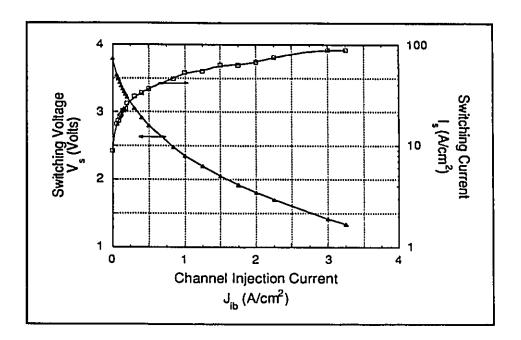

| 2.11   | The calculated dependence of $V_{so}$ and $I_{so}$ as a function of $J_{ib}$ .                                            | 33   |

| 2.12   | The calculated dependence of $V_{\text{S}}$ as a function of $J_{\text{ia}}$ and $J_{\text{ib}}$ .                        | 33   |

| 3.1    | Schematic three-dimensional energy band diagram of the HFET with non-zero source and drain potential.                     | 35   |

| 3.2    | Idealized source-drain current-voltage characteristics for a FET.                                                         | 36   |

| 3.3    | The energy band diagrams of the HFET.                                                                                     | 39   |

| 3.4    | The calculated dependence of V <sub>Th</sub> on N <sub>oh</sub>                                                           | 44   |

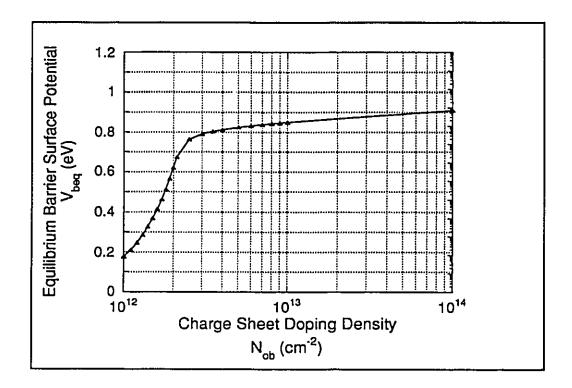

| 3.5   | The calculated dependence of V <sub>bo</sub> versus N <sub>bo</sub> in the HFET                                                  | 45 |

|-------|----------------------------------------------------------------------------------------------------------------------------------|----|

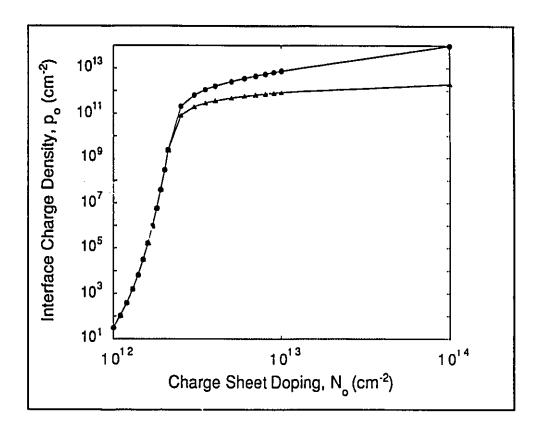

| 3.6   | The calculated dependence of $p_0$ , on $N_{0b}$ with and without consideration to the degree of charge sheet dopant ionization. | 46 |

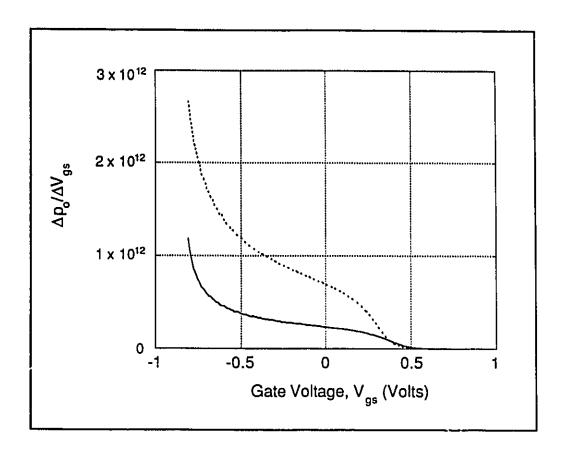

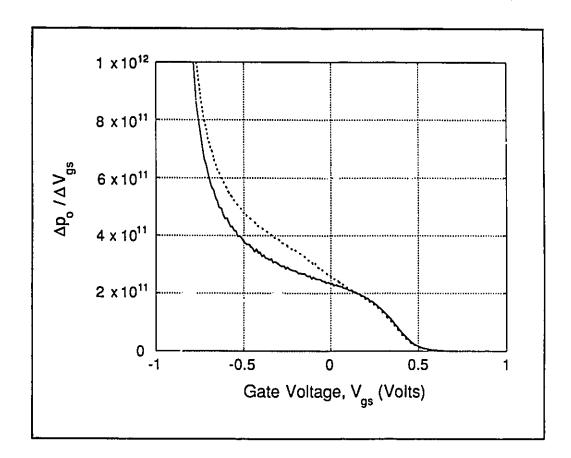

| 3.7   | The calculated dependence of $g_m$ on gate bias with and without consideration to the degree of charge sheet dopant ionization.  | 48 |

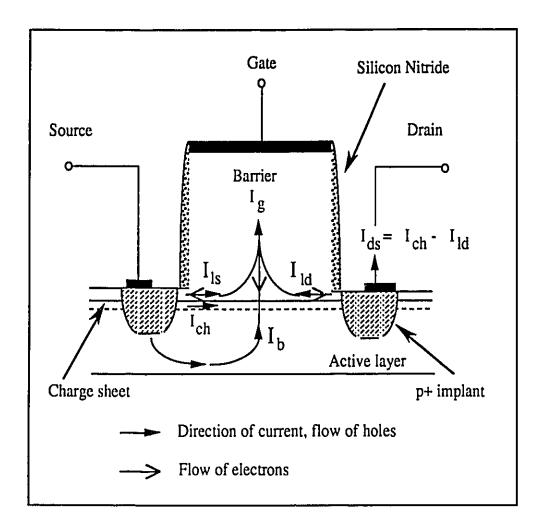

| 3.8   | A cross-sectional view of the HFET with gate leakage pathways.                                                                   | 49 |

| 3.9   | The calculated dependence of $g_m$ on the gate bias with and without consideration to the effect of gate leakage.                | 52 |

| 4.1   | The transmission electron micrograph (TEM) of wafer #951.                                                                        | 57 |

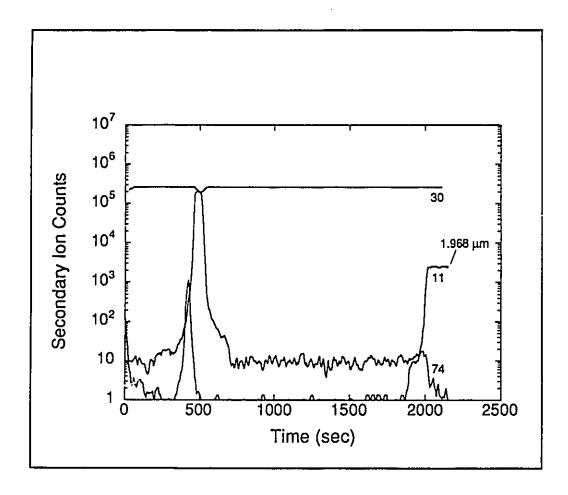

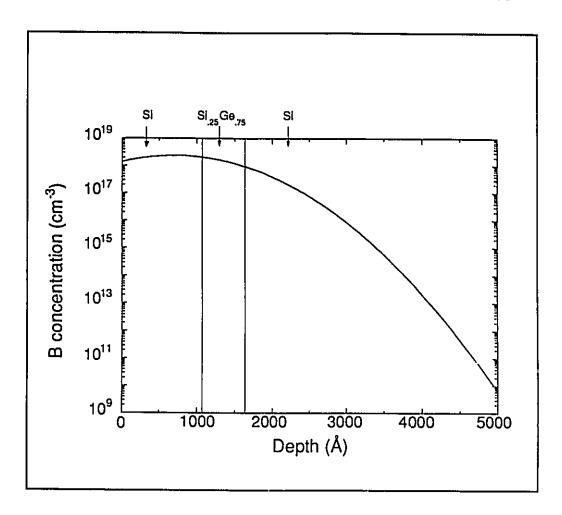

| 4.2   | The Si (30), B (11), and Ge (74) count profile of wafer # 951 obtained by SIMS.                                                  | 59 |

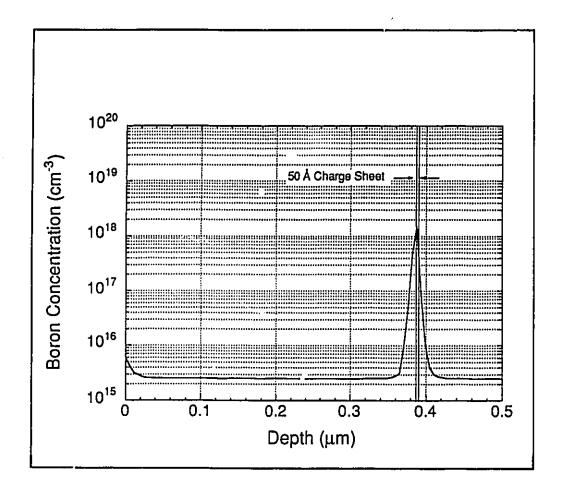

| 4.3   | The calibrated boron concentration from SIMS of wafer # 951.                                                                     | 61 |

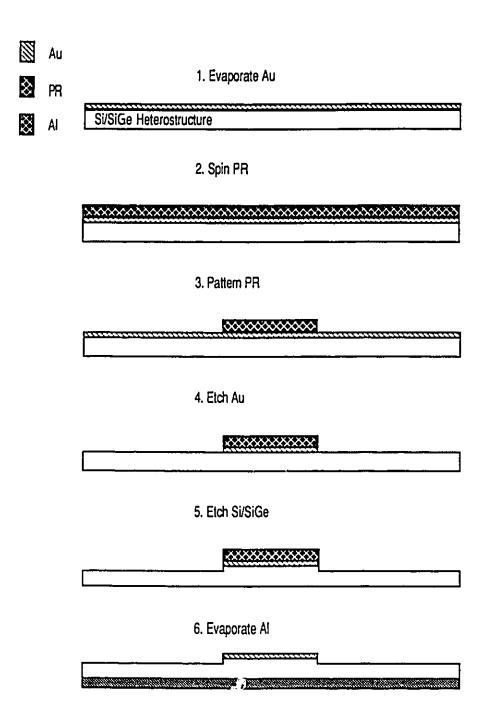

| 4.4   | The fabrication sequence for batch D1.                                                                                           | 63 |

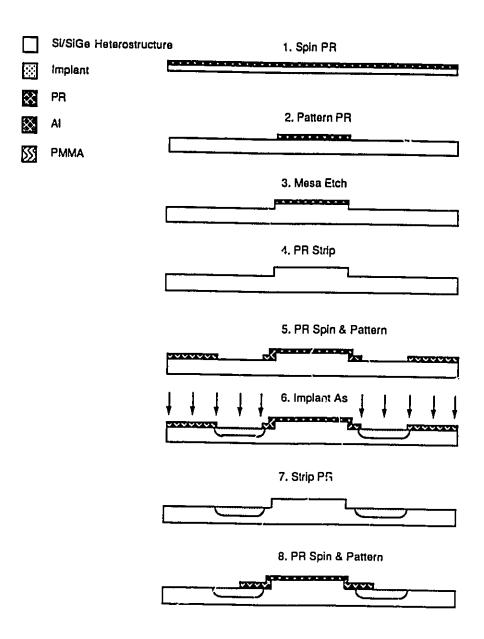

| 4.5   | The fabrication sequence for batch D2 (steps 1-16).                                                                              | 68 |

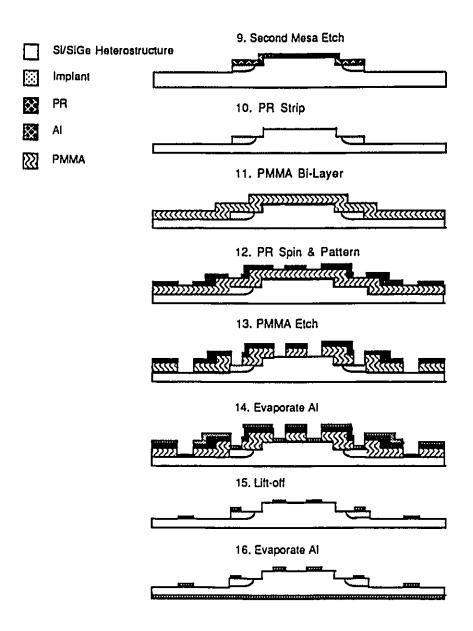

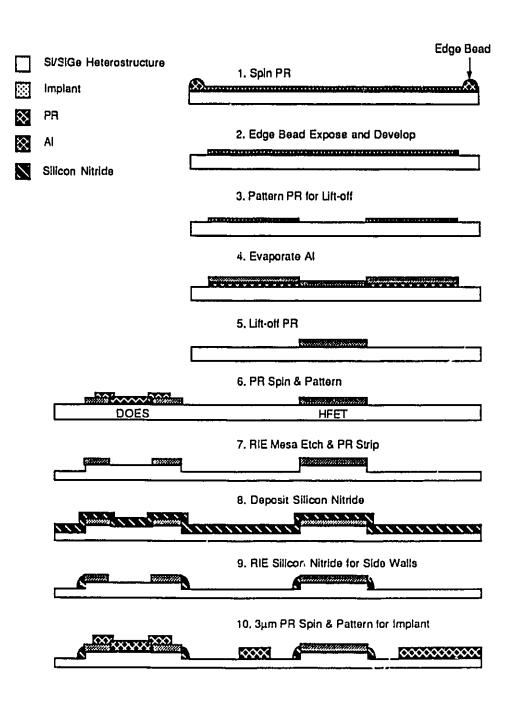

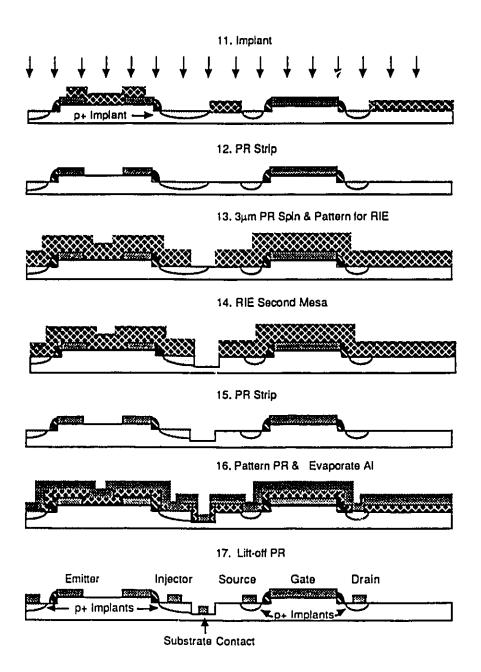

| 4.6   | The fabrication sequence for batch D3 (steps 1-17).                                                                              | 74 |

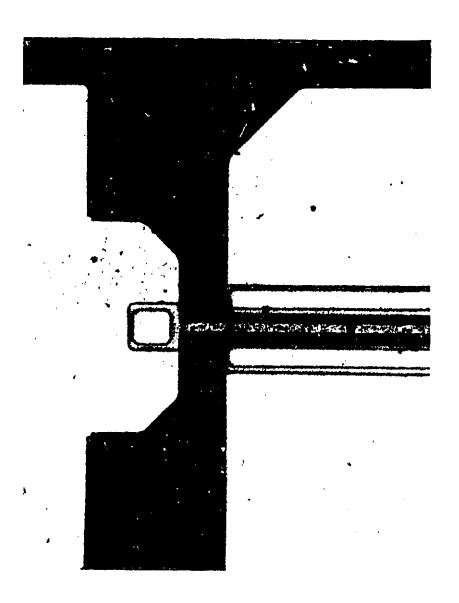

| 4.7   | The optical micrograph of the metallization after RIE.                                                                           | 81 |

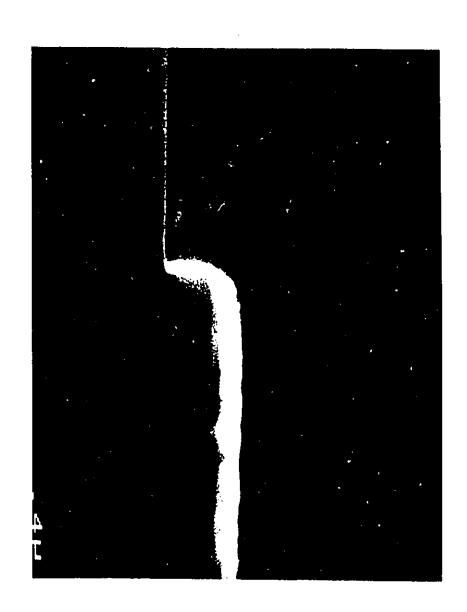

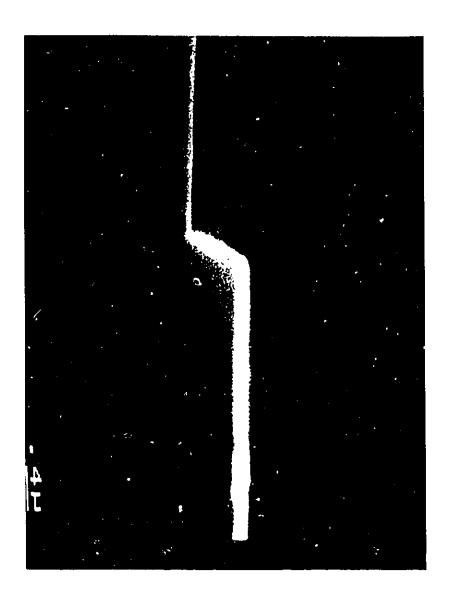

| 4.8:  | The scanning electron micrograph (SEM) of the mesa.                                                                              | 82 |

| 4.9   | The scanning electron micrograph of the mesa with side-walls.                                                                    | 83 |

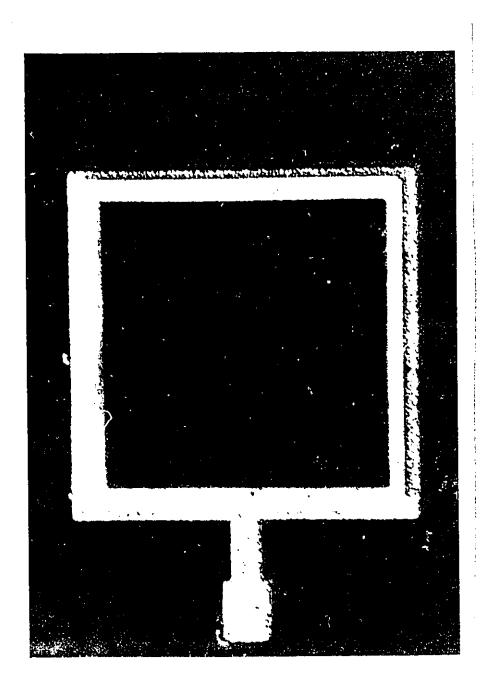

| 4.10: | The optical micrograph of the gate metal for the HFET with source and drain implant area defined with 3µm PR.                    | 84 |

| 4.11  | The calculated implant profile at 20keV and dose 2x10 <sup>13</sup> B /cm <sup>2</sup> .                                         | 86 |

| 4.12  | The optical micrograph of a double-mesa three-terminal DOES.                                                                     | 88 |

| 4.13  | The optical micrograph of a self-align HFET.                                                                                     | 89 |

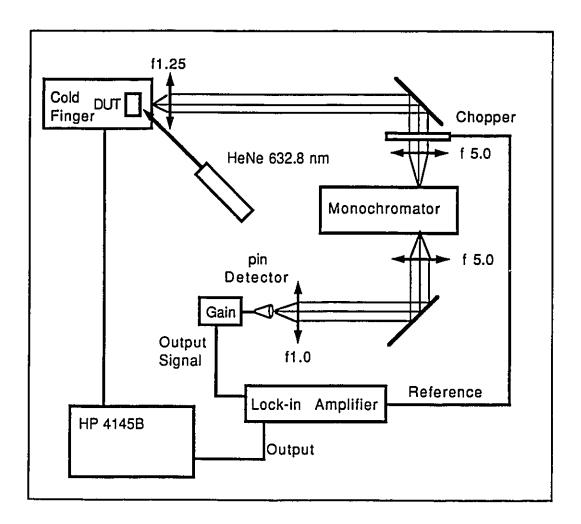

| 5.1   | A schematic representation of the experimental set-up.                                                                           | 93 |

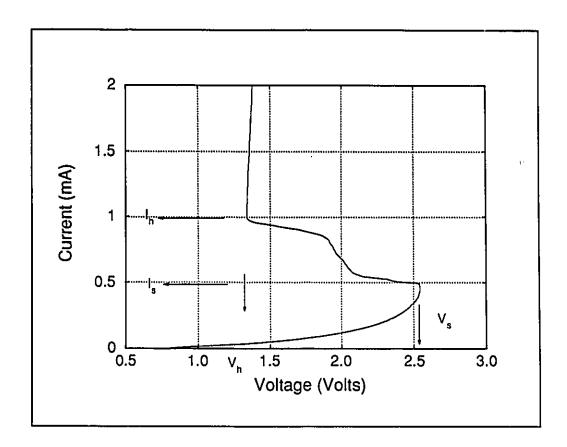

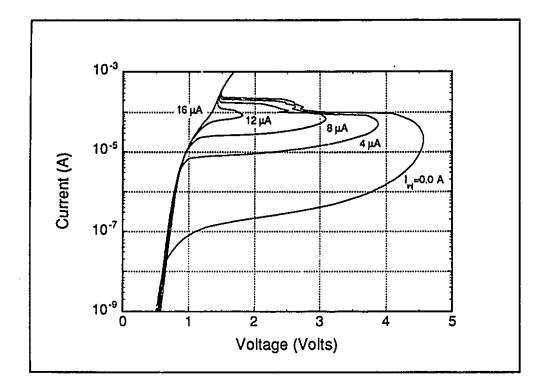

| 5.2   | The dark I-V characteristic of the two-terminal DOES (Batch D1).                                                                 | 94 |

| 5.3   | The I-V characteristics of the two-terminal DOES (Batch D1) with optical input as a parametric variable.                         | 95 |

| 5.4   | The I-V characteristic of the two-terminal DOES (Batch D1) with temperature as a parametric variable.                            | 97 |

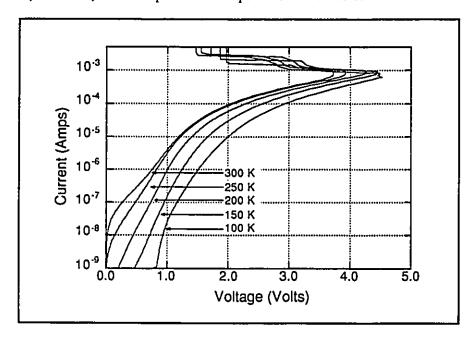

| 5.5  | The log(I)-V characteristic of the two-terminal DOES (Batch D2) with temperature as a parametric variable.                      | 97  |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

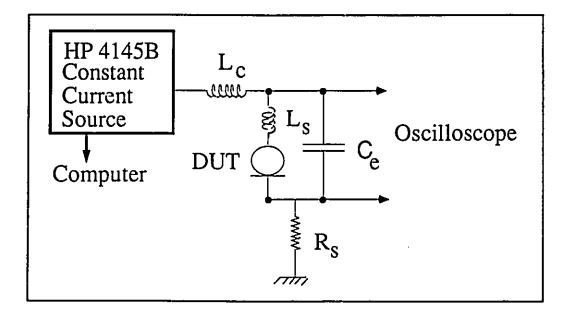

| 5.6  | The lumped circuit used to explain oscillations in the regime of negative differential resistance.                              | 99  |

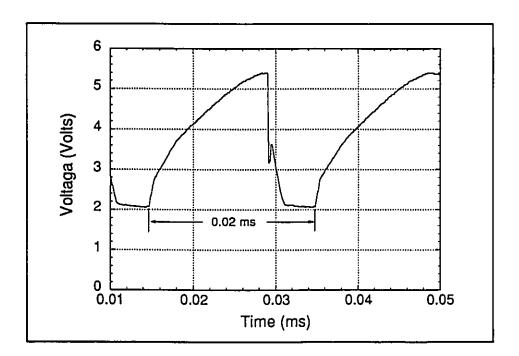

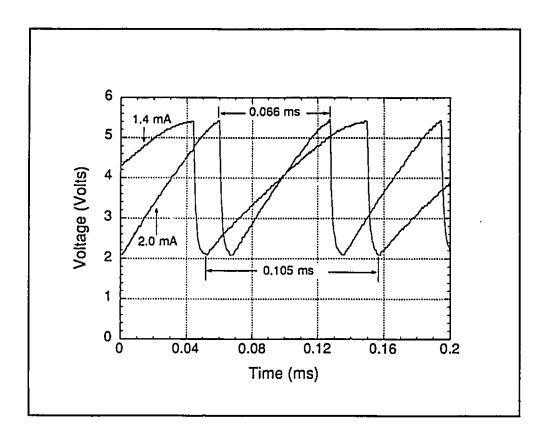

| 5.7  | The oscilloscope trace of the voltage across the DOES (Batch D3) with no external capacitor.                                    | 100 |

| 5.8  | The oscilloscope trace of the voltage across the external capacitor (22nF) placed in parallel with the DOES (Batch D3).         | 101 |

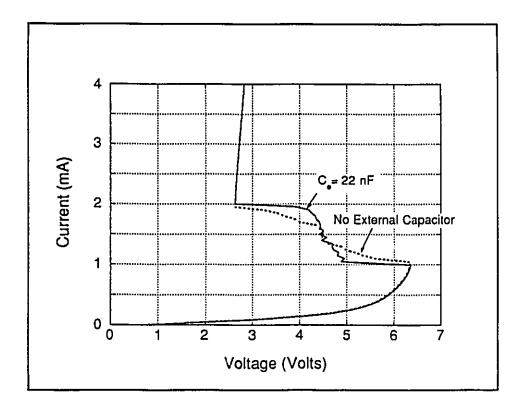

| 5.9  | The I-V characteristic of the DOES with and without a 22nF external capacitor.                                                  | 102 |

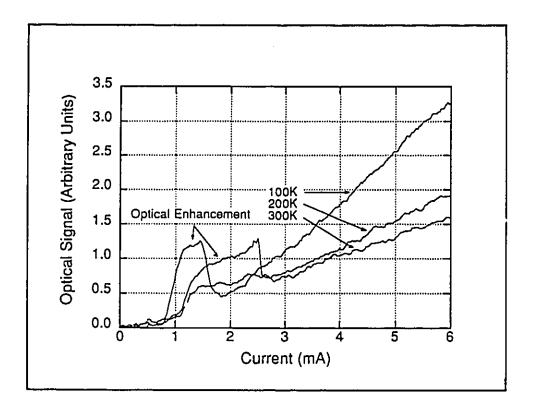

| 5.10 | The L-I characteristic of the two-terminal DOES (Batch D1) with temperature as a parametric variable.                           | 103 |

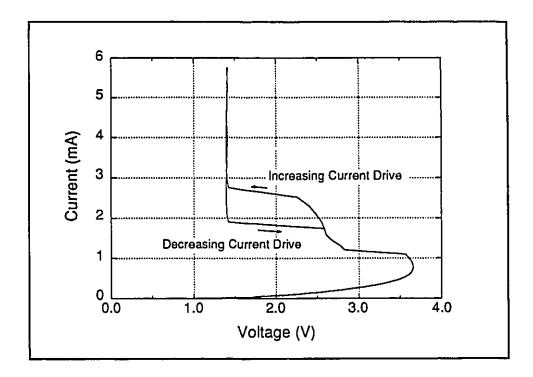

| 5.11 | The I-V characteristic of the DOES with hysteresis.                                                                             | 104 |

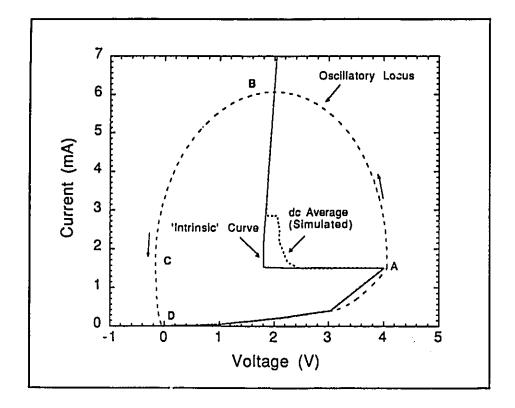

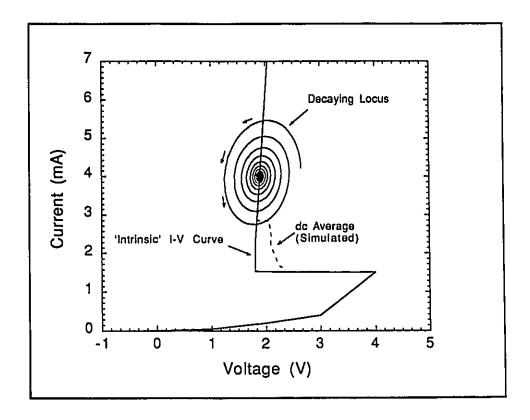

| 5.12 | The calculated average of voltage and current over 10 oscillation cycles simulated in the numerical model with $I_d$ =1.65mA.   | 107 |

| 5.13 | The calculated dc average of voltage and current oscillations simulated in the numerical model with $I_d$ =4.0mA.               | 108 |

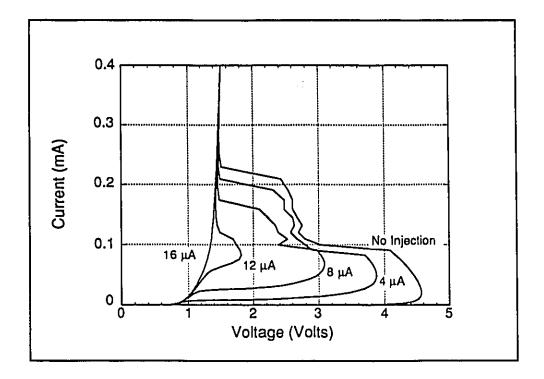

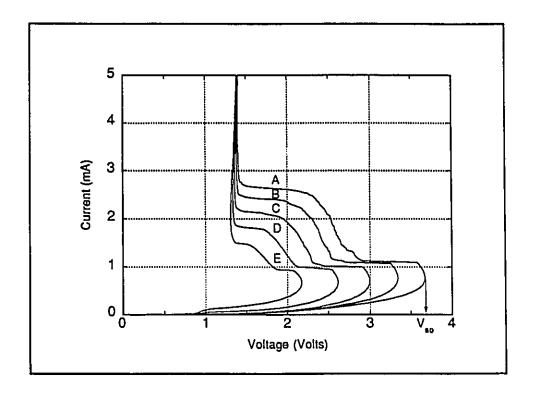

| 6.1  | The I-V characteristic for the three-terminal DOES (batch D2) with contact to the active region.                                | 113 |

| 6.2  | The log(I)-V characteristic for the three-terminal DOES (batch D2) with contact to the active region.                           | 114 |

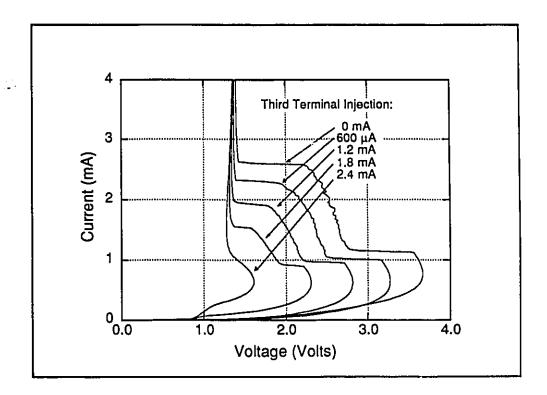

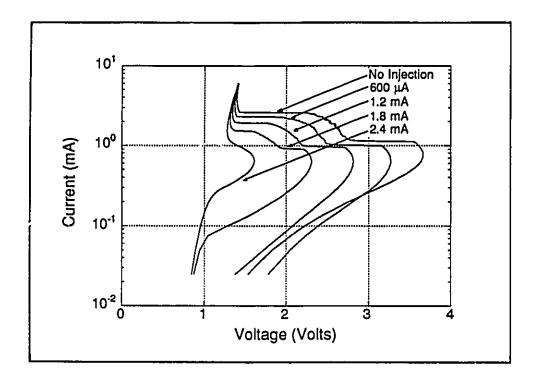

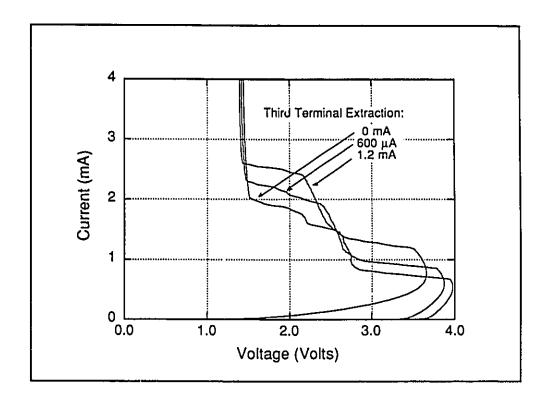

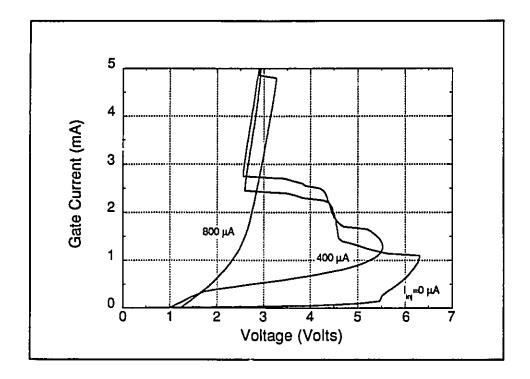

| 6.3  | The I-V characteristics for the three-terminal DOES (batch D3) with the third terminal making contact to the inversion channel. | 115 |

| 6.4  | The log(I)-V characteristics for the three-terminal DOES (batch D3) with contact to the inversion channel.                      | 116 |

| 6.5  | The I-V characteristic for the three-terminal DOES (batch D2) with contact to the active region.                                | 117 |

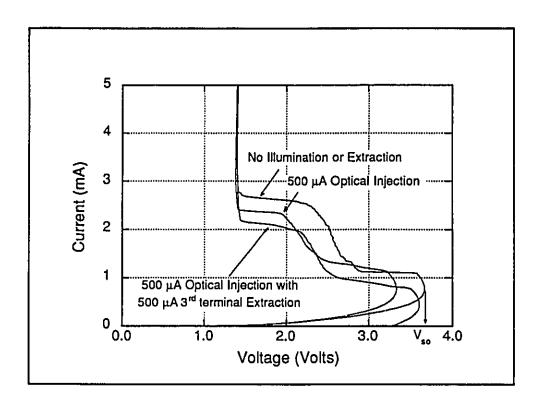

| 6.6  | The I-V characteristic of the three-terminal DOES (batch D2) with concurrent optical injection and electrical injection.        | 119 |

| 6.7  | The I-V characteristic of the three-terminal DOES (batch D2) with concurrent optical injection and electrical extraction.       | 120 |

| 6.8  | Comparing measured and calculated J-V characteristics for DOES (batch D3) with contact to the inversion change!                 | 122 |

| 7.1  | A schematic of the HFET.                                                                                                             | 124 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

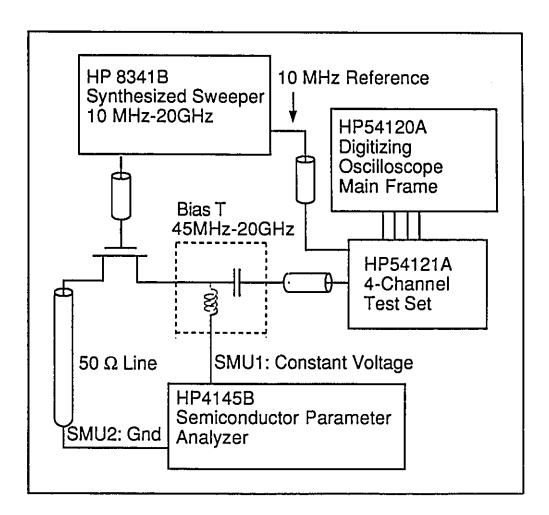

| 7.2  | A schematic of the high frequency experimental set-up.                                                                               | 125 |

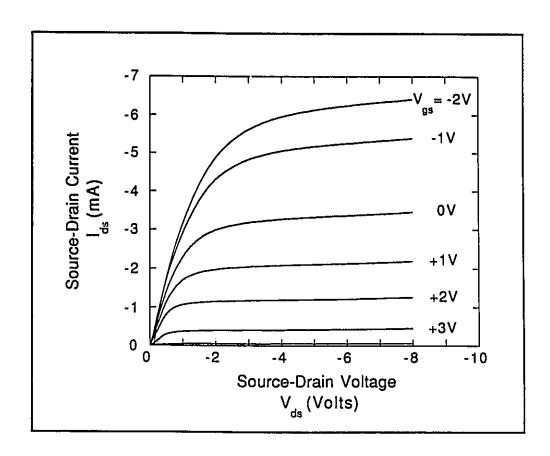

| 7.3  | The source-drain I-V characteristic of the HFET with gate length 1µm and width 150µm.                                                | 127 |

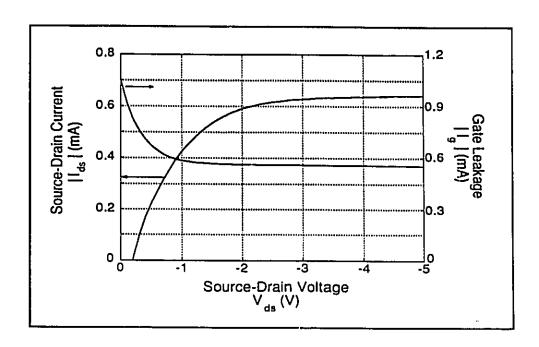

| 7.4  | At $V_{gs}$ =-2V, the dependence of $I_{ds}$ and gate leakage on $V_{ds}$ .                                                          | 129 |

| 7.5  | The subthreshold characteristics of the HFET.                                                                                        | 129 |

| 7.6  | The transconductance characteristic of the HFET with gate length $1\mu m$ and width $150~\mu m$ .                                    | 130 |

| 7.7  | The transconductance characteristic and $I_g$ for a device at $V_{ds}$ =-7V.                                                         | 131 |

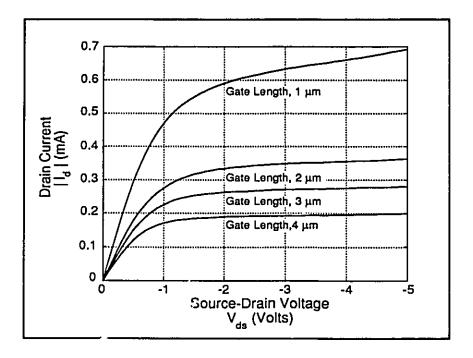

| 7.8  | The I-V characteristic of the HFET with $V_{gs}=1V$ and gate width 100 $\mu$ m. The gate length is used as a parameter.              | 132 |

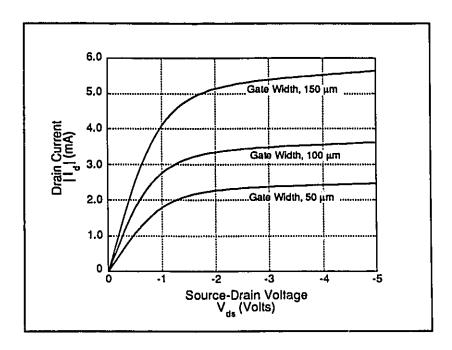

| 7.9  | The I-V characteristic of the HFET with $V_{gs}=1V$ and gate length $2\mu m$ . The gate width is used as a parameter.                | 133 |

| 7.10 | The high frequency response of the HFET.                                                                                             | 134 |

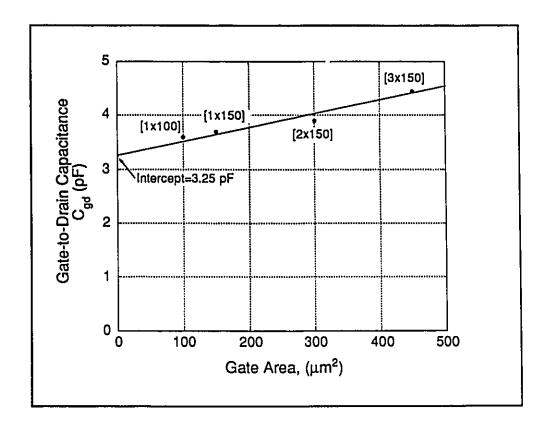

| 7.11 | The dependence of gate-to-drain capacitance of the HFET.                                                                             | 135 |

| 8.1  | The switching I-V characteristic of an HFET configured to operate as a DOES.                                                         | 138 |

| 8.2  | A schematic of the RS flip-flop design.                                                                                              | 139 |

| 8.3  | The RS flip-flop design, showing the integrated heterostructure.                                                                     | 140 |

| 8.4  | The characteristic I-V of the opto-electronic switch module under three conditions.                                                  | 142 |

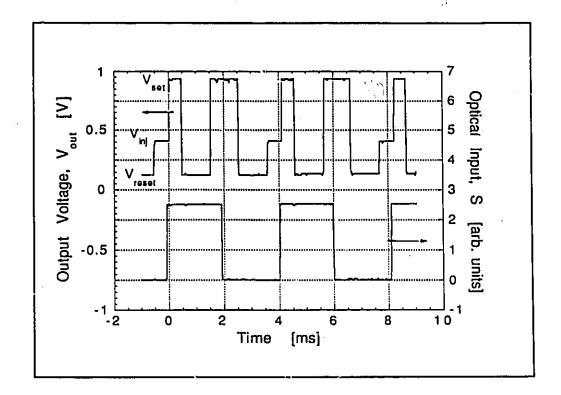

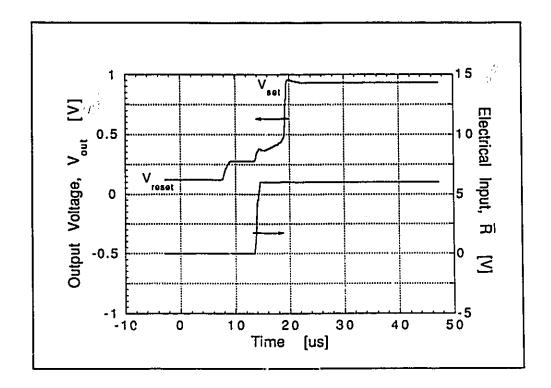

| 8.5  | The oscilloscope trace of Vout in response to the optical input.                                                                     | 145 |

| 8.6  | The oscilloscope trace of the transition from the low to the high state in response to a change in the electrical injection current. | 147 |

# **CHAPTER 1**

Ŋ,

$C_{i}$

## INTRODUCTION

It is arguable that no other technology has had as much of an impact on society as the transistor and related devices. Bardeen and Brattain [1] could hardly have foreseen the uses and abuses of the technology spawned by their device - 'a semiconductor triode'. Within thirty years, we have become a society which is dependent upon telecommunications and information processing to satisfy the most basic human needs. Since the first transistor, technological and conceptual developments in devices and systems have taken place at a frenetic pace. Starting from the bipolar junction transistor (BJT) of 1948, transistors based on the effect of an electric fields such as the metal-oxide-semiconductor field-effect transistor (MOSFET) [2], the insulated gate field-effect transistor (IGFET) [3], the metal-semiconductor field-effect transistor (MESFET) [4], the junction field-effect transistor (JFET) [5], and the semiconductor-insulator-semiconductor field-effect transistor (SISFET) [6] have all been realized.

The introduction of heterostructures in 1962 [7] has extended existing device concepts as in the case of the heterojunction bipolar transistor (HBT) [8] and has invigorated research into entirely new types of transistors such as the resonant-tunneling hot electron transistor (RHET) [9]. In most cases, the impetus for development has been to realize devices that are: i) fast and have high current drive capabilities in order to satisfy capacitive loads; or ii) have very low power consumption requirements while at the same time have very stable and well-defined operating states. The latter requirements arise when the device is used as

a switch rather than as a driving element. The logical state of the switch represents a variable or bit of information. However, a single transistor is not intrinsically a bistable device. Bistability is achieved by combining two transistors. One way to optimize speed and lower power consumption is to make the device smaller. Device processing engineers have made strong efforts in this area. Transistors with gates as narrow as 500 Å have been obtained in which intrinsic device capacitance has been reduces to fF [10]. Materials research is critical for many of the most recent developments in device performance. For example, strained layer growth of semiconductor heterostructures has allowed the incorporation of very high mobility materials [11] which have improved the speed of devices. Also, the use of very thin layers, where doping and composition are well controlled, have manifested quantum size effects within devices Quantum effects, such as those due to carrier confinement, have improved device performance by enhancing carrier transport [12] and have introduced entirely new device phenomenon into the design arena [9].

## 1.1 Technology Directions and System Considerations

For information processing circuits such as memory chips, all of the aforementioned operational attributes are desired. Silicon-based very large scale integration (VLSI) of the MOSFET [13] now dominates information processing circuits. Each MOSFET must be able to drive the capacitive load associated with subsequent devices in the circuit, switch operating states quickly, and use as little power as possible. The capacitive load in VLSI comes not only from the following devices in the circuit, but also from the interconnecting metal wire. In fact, it

is this interconnect capacitance which at present is the dominant capacitive element in VLSI and, therefore, the factor which limits circuit speed [14]. This so-called 'interconnect bottleneck' is unavoidable if electrons are used to transport a signal to the next device. A solution to this bottleneck is to use light to carry information either interchip or intrachip using waveguides or free-space optical links. Optical interconnects offer an number of basic advantages over electrical interconnects [15]:

- They can be more densely placed than electrical wires and can even intersect pathways.

- b) Propagation delays will be at least one-third shorter, with no dependence on number of interconnect branches. This is simply because photons travel approximately three times faster than electrical signal on strip lines. In addition, with metal interconnects, each branch off the interconnect adds capacitive load and increases the propagation delay.

- Electrical transmission lines need to be terminated with a load

which matches the impedance of the interconnect to avoid

reflections which add to the power requirement of the signal.

Using optical interconnects, power requirements are determined

only by the sensitivity of the photodetector and interconnect losses.

These advantages have been recognized by the telecommunications industry as seen by the drive to implement optical-fiber based networks. If light is chosen to carry signals, perhaps some of the electrical-to-optical and optical-to-electrical conversions which are required can be avoided.

Recently, there has been some interest in developing devices and monolithically integrated circuits which are sensitive to an optical signal and re-emit that signal after some signal processing [16, 17]. These opto-electronic integrated circuits (OEICs) can be used as pre- or post-processors of signals and information from Si-based VLSI circuits in a hybrid scheme or, potentially, even replace it. Introducing photons into information processing and storage methodologies has, and will continue to, drive development into entirely new device concepts and functions.

An example of this development is the inversion-channel family of devices, as manifested in the GaAs/AlGaAs alloy system. These include: the double heterojunction opto-electronic switch (DOES) [18]; the heterojunction field-effect transistor (HFET) [19]; the bipolar inversion-channel field-effect transistor (BICFET) [20]; and the two- and three-terminal inversion-channel laser [21, 22]. Some of the opto-electronic and electronic devices introduced above are designed to provide amplification while others are used as switches. Devices that have distinct bistable operating states such as the DOES have also been the subject of investigation. Using this technology, a number of OEIC demonstrations have been reported [23-25], although no performance comparisons to Si-based processors has been made to date.

Devices based on direct bandgap and high mobility materials have been available to system designer for some time but Si-based circuits have continued to be used for mass produced electronic processors. In effect, although state-of-theart discrete Si-based devices do not compare well with those based in III-V alloys, the demands of the system as a whole require the properties of Si. These considerations include cost, reliability, and reproducibility. The exception to this is GaAs-based monolithic microwave integrated circuits [26]. Here, in this purely

electronic application, GaAs-based circuits are desired for their high-frequency capabilities. However, even this niche for GaAs-based circuits is being threatened by the recent introduction of  $Si_{1-x}Ge_x$  alloy heterostructures [27]. A  $Si_{1-x}Ge_x$ -based HBT has already been demonstrated at IBM with  $f_T \approx 75$  GHz [28]. In addition, these  $Si_{1-x}Ge_x$  alloys have also been shown to be luminescent with efficiencies far greater than one would expect for the alloy of two indirect-gap materials [29]. The potential for efficient luminescence and the hetero-offset which accompanies the smaller bandgap  $Si_{1-x}Ge_x$  layer grown on Si may make this materials system a candidate for OEICs. A number of opto-electronic device concepts using the  $Si/Si_{1-x}Ge_x$  have been proposed or realized to date [30-32].

...

In Si-based VLSI of complementary MOS (CMOS) technology, the p-channel transistor is the 'weak' device from a performance perspective. Si-based, p-channel MOSFETs are typically two of three times the size of their n-channel counter-parts [33]. The size difference comes about simply because of lower p-channel mobility and a desire to balance the current from both types of devices. Researchers hope that from improvements in p-channel devices using Si<sub>1-x</sub>Ge<sub>x</sub>-based heterostructures, the greatest gains in VLSI packing density and speed will be realized.

A parallel development has been BICMOS - the incorporation of bipolar transistor (BJT) into CMOS circuits. The goal here is to use the current drive ability of BJTs and the low power consumption and high density of CMOS to yield a faster circuit with minimum power penalty and avoiding a costly reduction in gate length of the MOSFETs. A logical extension of this is to bring together the best attributes of Si<sub>1-x</sub>Ge<sub>x</sub>-based HBTs and CMOS technology. However, much work is still needed in the area of device fabrication in order to realize a Si<sub>1-x</sub>Ge<sub>x</sub>-based VLSI circuit.

#### 1.2 Material Properties of Si/SiGe

Si-based VLSI is a mature technology and has dominated information processing for 30 years with good reason. Silicon has exceptionally good material properties for making circuits. It is an abundant element with little or no volatility or toxicity and a relatively high melting point (1415°C). A high melting point allows a high thermal budget for device fabrication. Silicon readily forms a stable oxide which has excellent dielectric properties and has fair mechanical strength. The SiO<sub>2</sub> is used in VLSI CMOS technology as an diffusion and implant mask and also as a platform for metal interconnects.

As a semiconductor material, silicon is capable of changing resistivity over 10 orders of magnitude by doping with group III or V elements but it's energy bandgap of 1.12eV is indirect which precludes it from being used as a material for optical sources. Germanium (group IV) also has good mechanical properties and an indirect bandgap of 0.66eV.

Compound semiconductor materials such as GaAs, InP, and related quaternaries and ternaries have been predominately used in opto-electronic devices and circuits. This, in spite, of the fact that in these materials, devices are much harder to fabricate than those based on silicon. In addition, devices based on the III-V materials have operational characteristics which are difficult to control. However, the III-V materials, in general, have better intrinsic electron and hole conduction characteristics. Electron mobility (at 300°C) in GaAs (8500cm<sup>2</sup>/V-s) is twice that of Ge (3900cm<sup>2</sup>/V-s) which, in turn, has mobility approximately three times larger than Si (1500cm<sup>2</sup>/V-s) [34]. Thus, discreet device applications which require the highest frequency operation are generally fabricated using the III-V material system [35]. Another advantage of the

compound III-V materials is the ability to grow alloys of the compounds commensurately on the underlying substrate. Thereby, the best properties of each III-V compound and alloy can be used in a device design. A clear example of this is to compare the performance of the homojunction and the double heterojunction laser [36].

This design flexibility is now available with Si- and Ge-based devices. The alignment of Si and Si<sub>1-x</sub>Ge<sub>x</sub> conduction and valence bands is type I if the Si<sub>1-x</sub>Ge<sub>x</sub> layer is grown commensurately on Si(001) substrate. That is, the narrower Si<sub>1-x</sub>Ge<sub>x</sub> energy gap falls within the wider gap of the Si. Thus, a thin strained layer of Si<sub>1-x</sub>Ge<sub>x</sub> between unstrained layers of Si forms an energy well for both holes and electrons. However, the well for electrons is quite shallow compared to that for holes in Si<sub>1-x</sub>Ge<sub>x</sub> layers grown on Si [37]. Commensurate growth of Si<sub>1-x</sub>Ge<sub>x</sub> strained layers on Si(001) results in a biaxial in-plane compression of the Si<sub>1-x</sub>Ge<sub>x</sub> layer and an extension normal to the interface. The effect of the strain on the indirect bandgaps can be estimated using a deformation potential theory [38] and is found to decrease the energy gap of the Si<sub>1-x</sub>Ge<sub>x</sub> (Fig. 1). That decrease is seen predominately in an increase the valence band hetero-offset. For example, for Si<sub>1-x</sub>Ge<sub>x</sub> with Ge fraction 0.25 grown on Si(001),  $\Delta E_v \approx 0.185 \text{eV}$  and  $\Delta E_c \approx 0.02 \text{eV}[37]$ .

A number of devices have been reported in the literature which take advantage of the hetero-offset between Si<sub>1-x</sub>Ge<sub>x</sub> and Si. These include n- and p-channel MODFETs [39,40], PMOS [41], and the p-channel BICFET [42]. From these and other studies [43-46] an enhancement in p- and n-channel mobility in the strained Si<sub>1-x</sub>Ge<sub>x</sub> layers compared to unstrained, bulk material has been both predicted and observed.

Figure 1.1: The lowest energy indirect bandgap of coherently strained  $Si_{1-x}Ge_x$  alloys on Si(001) substrates.

$\bigcirc$

Although, strain in these heterostructures appears to benefit device performance, some less appealing properties and issues must be dealt with. The thickness of the strained  $Si_{1-x}Ge_x$  layers must be restricted to avoid strain relaxation in the form of misfit dislocations. If pervasive throughout a device, these dislocations can act as fast recombination/generation centers [47], increase dark currents in  $Si_{1-x}Ge_x$ -based photo-detectors [48], or simply reduce the strain-induced contribution to bandgap lowering.

Heterostructures incorporating strained Si<sub>1-x</sub>Ge<sub>x</sub> are restricted to layers smaller than the critical thickness (h<sub>c</sub>). Experimentally, the maximum thickness which can be grown on a Si(001) is considerably larger than values predicted by the early theory of strain relief. People and Bean [49] have proposed extensions to this theory [50-53] and have obtained a good fit to the experimental data. Heterostructure designs which require Si<sub>1-x</sub>Ge<sub>x</sub> layers close to h<sub>c</sub> will at the same time place restrictions on device processing. In particular, the amount of heating the wafer experiences (the so-called 'thermal budget') must be kept low in order to keep the Si<sub>1-x</sub>Ge<sub>x</sub> layer in the metastable strained state [54]. This may or may not exclude a Si<sub>1-x</sub>Ge<sub>x</sub>-based heterostructure from the same processing steps used to make MOSFETs. In the formation of a MOSFET, several high temperature (>700°C) processes, including the formation of the gate and field oxide and the annealing of ion implantation damage for the source and drain contacts, are required [55].

The Si<sub>1-x</sub>Ge<sub>x</sub>-based MESFET is easier to fabricate than the MOSFET since no gate oxide deposition or growth is required. Pearsall and Bean [40] were able to restrict processing temperatures to 700° C in the fabrication of p-channel Si<sub>1-x</sub>Ge<sub>x</sub> MODFETs. A BF<sub>2</sub> implant of the source and drain was used. The degree of dopant activation desired and the annealing of crystal damage after an

implant will determine the ultimate processing temperatures required in the fabrication of a Si<sub>1-x</sub>Ge<sub>x</sub> MODFET.

#### 1.3 Objectives of the Thesis

It is the objective of this work to experimentally and theoretically investigate two- and three-terminal DOES devices and the p-channel HFETs based in the  $Si/Si_{1-x}Ge_x$  alloy system. This is the first time the inversion-channel technology has been applied to the  $Si/Si_{1-x}Ge_x$  material system.

Following this introductory chapter, the theory of operation of the DOES and HFET in the Si/Si<sub>1-x</sub>Ge<sub>x</sub> system is presented (Chapters 2 & 3 respectively). The fabrication procedure developed for these devices is presented in Chapter 4. In Chapters 5, 6, and 7 the experimental characteristics of the DOES and HFET, are found and compared to simulations based on the theory. A logic circuit application of these devices and their monolithic integration is demonstrated in Chapter 8. Finally, in Chapter 9, a summary of the major findings and a discussion on future research directions for this work concludes the thesis.

## **CHAPTER 2**

11.12

## OPERATIONAL THEORY OF THE DOES

This chapter reviews the theory of operation of the DOES and relates it to the salient electrical characteristics of the device. Much of the theory behind the Si/SiGe DOES presented here is an extension of the work of Simmons, Taylor, and Swoger [56-58]. Indeed, simulations of both the two- and three-terminal DOES which appear in this chapter use a computer algorithm written by Swoger with alterations applicable to the Si/SiGe-based heterostructure.

## 2.1 Current-Voltage Characteristics of the DOES

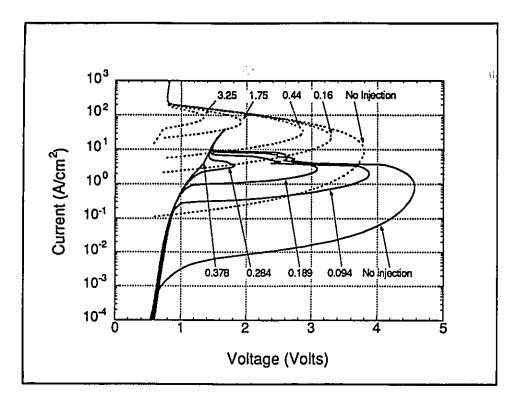

In previous manifestations of the DOES based in the GaAs/AlGaAs material system [18], if current is driven from the emitter to the collector and the voltage required to do this is recorded, then an 'S'-shaped current-voltage characteristic will be observed (Fig. 2.1). This characteristic exhibits electrical bistability; a high-impedance OFF-state and a low-impedance ON-state that are separated by a differential negative resistance region. Without any injection current from the third-terminal, a switching voltage, V<sub>SO</sub>, and its associated current, I<sub>SO</sub>, define the limit of the high-impedance state. The onset of the low-impedance state is characterized by a holding voltage, V<sub>hO</sub>, and an associated current, I<sub>hO</sub>. By injecting carriers via the third terminal, the switching voltage, V<sub>S</sub>, is reduced below V<sub>SO</sub>, I<sub>S</sub> and I<sub>h</sub> move to slightly lower values, and V<sub>h</sub> remains

Figure 2.1: The hypothetical current-voltage (I-V) characteristic of the DOES with increasing third-terminal injection as a parametric variable. The switching voltage,  $V_{so}$ , switching current,  $I_{so}$ , holding voltage,  $V_{ho}$ , and holding current,  $I_{ho}$ , mark the boundaries of the impedance states of the device with no third-terminal injection. From point A to B, the device is in the OFF-state, from point B to C, in the regime of negative differential resistance, and from point C onwards to higher current, the device is in the ON-state.

essentially unchanged. Thus, with  $I_{inj}$  as a parametric variable, a family of I-V curves nesting within the original ( $I_{inj} = 0$ ) I-V characteristic is generated as shown in Fig. 2.1. A simple switching circuit may be constructed using a load resistor in series with the device. For the  $I_{inj}=0$  curve, assume that the operating point is P on the high impedance portion of the device characteristic. Here, essentially all the supply voltage,  $V_{sp}$ , is dropped across the device and only a small current flows in the external circuit. When a third-terminal injection current is applied it is seen that the load line can only intersect the low impedance portion of the new I-V curve. Thus, there is now only  $V_h$  across the device and  $V_{sp}$ - $V_h$  across the resistor, and therefore substantial current is now flowing in the circuit. One would expect that the device can be switched from the ON-state back to the OFF-state by extracting current, which results in quenching the feed-back current flowing in the device.

Ð

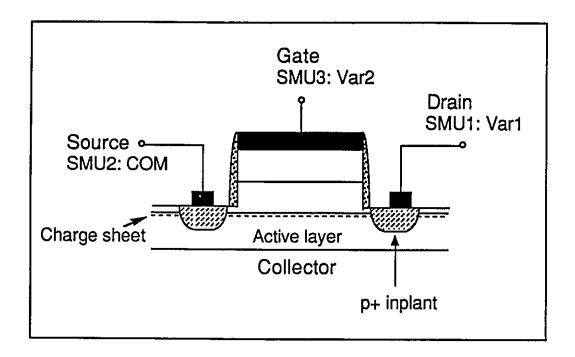

## 2.2 The Physical Structure of the Si/SiGe-Based DOES

The basic physical structure of the DOES comprises, in sequence, a heavily-doped p-type wide-bandgap semiconductor (WBGS), a n-type narrow bandgap active layer, a highly doped p-type charge sheet, and a n-type wide bandgap barrier layer. The first p-type layer is usually the substrate. The heterostructure designed to implement the Si/SiGe DOES and HFET is seen in Fig. 2.2. It must be emphasized that this was the target heterostructure from which the actual grown layer may deviate substantially.

The Si/SiGe DOES heterostructure resembles the npnp structure of the Si-based optical thyristor [59]. However, there are two distinct and critical features of this design. The first is a 50Å thick layer of Si doped p-type at  $5 \times 10^{18}$  cm<sup>-3</sup>

with boron. This layer forms the charge sheet and creates a triangular energy barrier. This charge sheet is depleted of free charge and, as we shall see later, minimizes the problems of charge storage. The magnitude of the doping in the charge sheet has been shown [56] to have a strong effect on the electrical characteristics of a DOES. Astride the charge sheet, are the barrier and active layers. These layers are doped n-type at 2x10<sup>17</sup> As cm<sup>-3</sup> and 1x10<sup>17</sup> As cm<sup>-3</sup> respectively. The barrier layers (sometimes called the emitter) includes a highly doped cap layer to facilitate an ohmic contact.

The second feature is a layer of Si.75Ge.25, with no intentional doping incorporated, placed between the charge sheet and the active layer. This layer is grown lattice matched to the underlying (100) Si active layer and as such is under compressive strain. The Si.75Ge.25 layer forms a valence band hetero-offset at nearly the same point as the charge sheet. It is at this hetero-offset that free holes induced by the charge sheet collect. In actuality, the charge sheet and the Si.75Ge.25 layer are separated by a 50Å thick spacer layer of undoped Si which is required to spatially separate the holes in the inversion layer from the acceptors in the charge sheet and thereby reduce ionized impurity scattering [12].

The entire heterostructure was grown on a Si(100) substrate doped p-type at  $2 \times 10^{18}$  cm<sup>-3</sup> with boron. The substrate was used in this design as a contact and is called the collector.

The magnitude of the valence band discontinuity at the Si-SiGe interface is determined by the Ge content in the alloy. A large offset in the valence band is conducive to hole accumulation at the Si/SiGe interface and enhances the feedback gain in the DOES and reduces gate leakage in the HFET. We shall see that the gain of the hetero-structure has an exponential dependence on the valence-band discontinuity or, equivalently,

Figure 2.2: The layer structure and cross-sectional view of the self-aligned three-terminal DOES/HFET with terminals contacting the inversion charge on both sides of the mesa with a  $p^+$  implant. Another terminal is seen to make contact to the active layer with an  $n^+$  contact. The layer sequence: 1) 100nm of n-type Si (2 x  $10^{18}$  cm<sup>-3</sup> As); 2) 200nm of n-type Si (2 x  $10^{17}$  cm<sup>-3</sup> As); 3) the 5nm charge sheet of p-type Si (5 x  $10^{18}$  cm<sup>-3</sup> B); 4) 20nm of undoped Si; 5) 60nm of undoped Si<sub>.75</sub>Ge<sub>.25</sub>; 6) 20nm of undoped Si; 7) the 1000nm active layer of n-type Si (1 x  $10^{17}$  cm<sup>-3</sup> As); and finally, 8) the substrate.

on the Ge content of the SiGe well. Also, creating or reducing hole accum-ulation at the Si-SiGe interface by third-terminal injection/extraction is the primary method of controlling the switching voltage of the device. In the DOES, the

third-terminal refers to the terminal which makes contact to the charge which is trapped at the hetero-interface or a terminal to the active region. This is illustrated in Fig. 2.2.

The switching voltage can also be controlled by optical injection. Light absorbed in the depletion regions astride the charge sheet will enhances the hole accumulation at the hetero-interface. Electrons and holes created by absorption are spatially separated by the electric field associated with the depletion regions. Holes are swept to the n-n hetero-interface whereas electrons are swept to the neutral part of the barrier and active layers. The operational parameters of the DOES will depend on the incident optical power and the wavelength-dependent absorption depth of the light. This has been reported for DOES manifested in the GaAs/AlGaAs system [18].

## 2.3 Energy Band Diagrams

The energy band diagram for the structure shown in Fig. 2.2 under equilibrium conditions is shown in Fig. 2.3. A principle feature of this diagram is the depleted n-layers on either side of the Si/Si-Ge well, which are induced by the depleted p+delta region. Thus, with the charge sheet acceptors fully occupied by electrons, the sheet assumes a negative polarity and the depleted barrier and active layers assume a positive polarity. It will be shown that the occupancy of the charge sheet acceptors depends on the position of the Fermi level at the n-n heterojunction.

The relatively small thickness of the charge sheet compared with that of the barrier layer allows us to illustrate the sheet as part of the surface layer of the barrier. The junctions formed by the barrier layer, the charge sheet, and the active

layer are collectively called the n-n heterojunction. The junction formed by the wide bandgap active layer and the substrate is called the p-n junction.

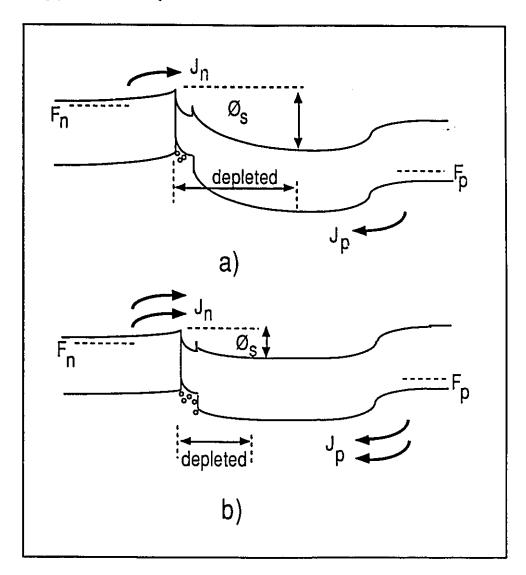

Figure 2.3: The schematic energy band diagram of the heterostructure under equilibrium conditions.  $F_n$  and  $F_p$  are the Fermi levels in the neutral part of the barrier layer and substrate respectively.  $Ø_s$  is the total surface potential in the active layer.

Under forward-bias conditions (emitter is biased negatively with respect to the substrate), the Fermi-level in the emitter is raised and the barrier-sheet junction becomes forward-biased while the sheet-active layer junction becomes reverse-biased. The active-collector junction also becomes forward-biased to some extent. A brief explanation of the I-V characteristics of the device can be made with reference to the energy diagrams in Fig. 2.3 & 2.4. In the OFF-state, Fig. 2.4(a), the n-n heterojunction and the active region-substrate junction are

both slightly forward-biased, but the left side of the active layer is reversed-biased and, as such, its surface potential  $\mathcal{O}_S$  absorbs most of the applied voltage. Electrons flowing over the barrier layer into the active layer also pass over the p-n junction, thereby forward-biasing it. Consequently, this causes the injection of holes into the active region, which then pass through the barrier layer. This process incrementally forward-biases the barrier layer, thus augmenting the flow of electrons through the barrier layer. This positive feed-back action continues with increasing current and voltage until the small-signal gain of the heterojunction and the p-n junction reaches unity. This causes the depletion region and, hence,  $\mathcal{O}_S$  to collapse (Fig. 2.4(b)) with further increase in the current, a process which generates a regime of negative differential resistance (Fig. 2.1). The device exists in this condition until the surface potential reduces to a few millivolts, when the device then enters the low-impedance mode.

It is constructive in this discussion to briefly identify some of the figures of merit for a device such as the DOES. As a switch, one would presumably like to have the two operational states as extreme as possible; the OFF-state having extremely large impedance (high  $V_S$  and low  $I_S$ ); and the ON-state having very low impedance (diode-like). The time to switch between states is also an important figure of merit for the applications envisioned for the DOES. Sensitivity to third-terminal injection and optical injection is a critical aspect of this device. The change in  $V_S$  versus optical intensity or third-terminal injection is perhaps the most simple way to describe the sensitivity.

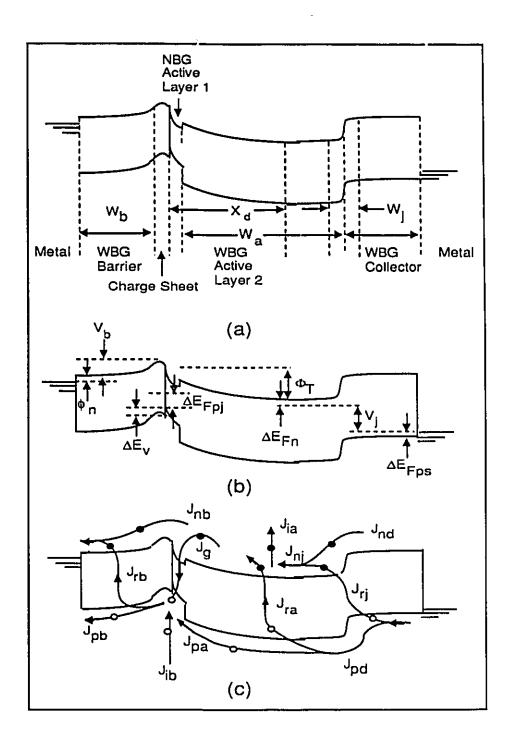

The mathematical discussion to follow will attempt to focus on the aforementioned figures of merit. In Fig. 2.5, the energy band diagram of the Si/SiGe heterostructure described above illustrates the physical parameters, current components, and the various potentials to be referenced in the equations.

A parameter followed by the subscript naught ( $_0$ ) indicates the equilibrium value. For example, the barrier potential at equilibrium is denoted by  $V_{bo}$ , as opposed to simply  $V_b$ , the non-equilibrium value.

Figure 2.4: The schematic energy band diagram of the heterostructure under forward-bias conditions in the (a) OFF-state and in the (b) ON-state.  $J_n$  and  $J_p$  are the electron current over the barrier and the hole current from the substrate respectively.

## 2.4 Charge equations

Charge neutrality in the heterostructure dictates that,

$$Q_0 + Q_b + Q_{Si} + Q_{SiGe} + q p_0 = 0 (2.1)$$

where the Si barrier depletion charge is  $Q_b$ , the charge in the  $p^+$  doped Si charge sheet is  $Q_o$ , the hole charge in the channel is  $qp_o$ , and the charge of the depleted n-type dopants in the Si active region is  $Q_{Si}$  and  $Q_{Si}$  for the SiGe well. All of the above are in units of charge density per unit area.

In practice, in this heterostructure, the SiGe well was not doped to any degree intentionally. Any doping in this well arises from the residual effects within the MBE growth facility and therefore is doped orders of magnitude below the Si active layer.

In equation 2.1, Q<sub>0</sub>, the contribution from the charge sheet, is given by:

$$Q_o = \frac{-q N_o}{1 + \exp\left[\left(E_a + \Delta E_{Fpj} - \Delta E_v\right) / V_t\right]},$$

(2.2)

where  $E_a$  is the activation energy of the acceptors and  $N_0$  is the acceptor areal density of the charge sheet given by the product of the doping in the delta layer multiplied by the thickness. Clearly, from equation 2.2, if  $(\Delta E_{Fpj} - \Delta E_v)$  approaches  $E_a$  then  $Q_0$  will begin to fall. This must be compensated by a decrease in  $Q_b$ ,  $Q_{Si}$ ,  $Q_{SiGe}$ , and  $q_{Po}$ . This will be shown to have severe repercussions vis a vis the operation of the Si/SiGe-based HFET.

Figure 2.5: The schematic energy band diagram of the heterostructure with (a) layers and thickness identified, (b) various potentials shown, and (c) current components labeled.

The depletion approximation is used to determine the depleted charge from the barrier and active layer. For the barrier:

$$Q_{b} = \sqrt{2 q \varepsilon_{b} N_{bo} V_{b}}, \qquad (2.3)$$

where  $V_b$  is the barrier potential, and  $N_b$  is the donor concentration in the barrier. Similarly, in the active region,

$$Q_{SiGe} = qN_{SiGe}W_{SiGe}, \qquad (2.4)$$

$$Q_{Si} = \sqrt{2 q \, \varepsilon_{Si} \, N_{Si} \, \phi_{Si}} , \qquad (2.5)$$

where  $N_{SiGe}$  and  $N_{Si}$  is the doping concentration in the SiGe and Si active region respectively, and  $\phi_{SiGe}$  and  $\phi_{Si}$  are the surface potential of the SiGe and Si depletion regions, respectively.

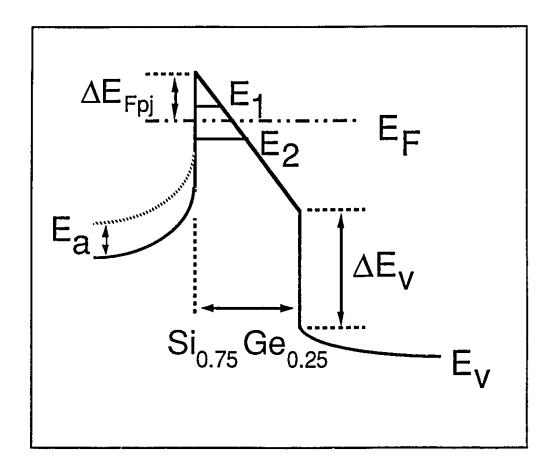

The next step is to solve for  $p_0$  in the channel. Here the analysis is complicated by a number of factors. Firstly, under bias conditions, the SiGe-well is a triangular-like quantum well which contains quantized energy levels. The electric field in the active layers determines the width of the well. In such energy levels, the density of states is altered to become a step-like density where the first energy level lies above the valence band edge [60]. Secondly, the free charge in the channel is dependent upon  $\Delta E_{Fpj}$  in a manner which requires a self-consistent solution. Finally, the conduction channel lies in the strained SiGe well where splitting of the valence bands is predicted [36]. This will almost certainly affect mobility and hole mass in the channel. In the following analysis the effect of strain and interband mixing is neglected.

The channel is approximated by a triangular quantum well, as is commonly done for High Electron Mobility Transistors (HEMTs). Using this model, which is graphically illustrated in Fig. 2.6, the first two energy levels in the well are given [61] by:

$$E_1 = \beta_1 \left[ \frac{\text{qp}_0 + \sqrt{2\text{q} \, \epsilon_{\text{SiGe}} \, \text{N}_{\text{SiGe}} \, \phi_{\text{SiGe}}}}{\epsilon_{\text{SiGe}}} \right]_3^2, \tag{2.6}$$

and

$$E_2 = \left(\frac{7}{3}\right)^{2/3} E_1,$$

(2.7)

where

$$\beta_1 = \left(\frac{h^2}{8 \text{ q mp}}\right)^{\frac{1}{3}} \left(\frac{9}{8}\right)^{\frac{2}{3}}$$

If we can neglect the hole filling of the second energy level then we need only to integrate the density of states multiplied by the Fermi-filling function over  $E_1$  to  $E_2$ ; that is, the Fermi level in the channel always remains above  $E_2$ . Then

$$p_0 = \int_{E_2}^{E_1} g(E) f(E) dE$$

where

$$g(E) = \frac{4\pi q m_p}{h^2}$$

14.

Figure 2.6: A schematic representation of the formation of hole energy levels in the valence band at the n-n heterojunction. Also illustrated is the Fermi-level in the channel,  $E_F$ , and the activation energy,  $E_a$ , of the dopant in the charge sheet.  $\Delta E_{Fpj}$  is the difference between  $E_F$  and the valence band edge,  $E_v$ , at the heterointerface. The quantized energy levels arising due to carrier confinement are labeled  $E_1$  and  $E_2$ .

is the density of states, and

$$f(E) = \frac{1}{1 + \exp\left(\frac{E - \Delta E_{Fpj}}{V_t}\right)}$$

is the Fermi-filling function. The Fermi level position is found by combining the above equations to give:

$$\Delta E_{\text{Fpj}} = -V_{t} \ln \left[ \frac{\exp\left(\frac{-E_{1}}{V_{t}}\right) - \exp\left(\frac{-E_{2}}{V_{t}}\right) e^{A}}{e^{A} - 1} \right]$$

(2.8)

where

$$A = \frac{p_0 h^2}{4 p q m_p V_t}$$

The value of po used here is found by re-arranging eqn. (2.1):

$$p_0 = \frac{Q_0 - Q_b - Q_{SiGe} - Q_{Si}}{q}$$

(2.9)

Swoger [57] has developed a computer-based algorithm which solves equations (2.8) and (2.9) in a self-consistent manner. Thus, in theory, given an arbitrary heterostructure design, the above equations are used to determine  $p_0$  and  $\Delta E_{Fpj}$ .

## 2.5 Current Equations

By examining the current components in Fig. 2.5(c) and assuming steady state conditions, two of continuity relations can be discerned. First, the electron flow over the barrier,  $J_{nb}$ , plus the generation current in the active layer,  $J_g$ , must balance the electron flow into the substrate,  $J_{nd}$ , plus the recombination currents

in the neutral part of the active layer,  $J_{ra}$ , and the recombination current at the p-n junction,  $J_{rj}$ :

$$J_{nb} + J_g = J_{ri} + J_{nd} + J_{ra}$$

(2.10)

A summation of currents at the hetero-interface indicates that, hole flow into the barrier,  $J_{pb}$ , plus the rate at which holes recombine in barrier,  $J_{rb}$ , must balance holes which flow to the hetero-interface from the active layer,  $J_{pa}$ , plus the generation current in the active layer,  $J_g$ , plus any hole injection via the third terminal,  $J_{ib}$ :

$$J_{pb} + J_{rb} = J_{pa} + J_g + J_{ib}. (2.11)$$

Analytical expressions for the various current components can be found in appendix A. These expressions differ somewhat from the expressions used by Swoger [56] in that the SiGe-well requires segmentation of the active region.

The total applied bias voltage, V, between the emitter and collector can be found by summing the various potentials in Fig. 2.5(b):

$$V = V_j + \phi_T - \phi_{T_0} + V_{b_0} - V_b, \qquad (2.12)$$

where

$$\phi_{T_0} = \phi_{SiGc_0} + \phi_{Si_0} + \Delta E_c$$

$$\phi_T = \phi_{SiGc} + \phi_{Si} + \Delta E_c$$

#### 2.6 Simulations and Predictions

Given equations 2.1 to 2.12, it is possible to predict the salient operating characteristics of both the two- and three-terminal DOES. For example, the areal charge sheet doping density can be varied to investigate the effect on switching voltage. These simulations will be compared to the experimental data in later chapters of this thesis. Other parameters of interest are the injected current both at the barrier, J<sub>ib</sub>, and into the active layer, J<sub>ia</sub>. In both cases, injecting current will allow the DOES to satisfy the criterion for switch back at a lower voltage. It is possible to determine the sensitivity of the DOES to third-terminal injection. However, such a determination, obtained using a computer-based model, can be inaccurate when the physical design and fabrication process of the device has not been considered. Rather than attempt absolute measures, it is more realistic and, perhaps, more informative to compare device sensitivity to electrical injection into the inversion layer and into the active layer.

#### 2.6.1 Effect of Charge Sheet Doping Density

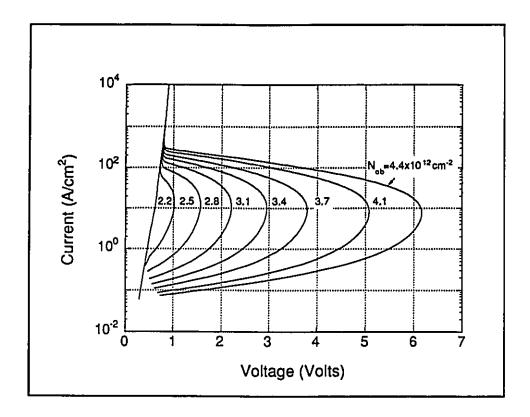

Figure 2.7 illustrates the calculated logarithmic of current density versus voltage (log(J)-V) characteristics of the DOES with structure identical to that of Fig. 2.2 with the exception that the charge sheet doping density, N<sub>0</sub>, is used as a parameter. Varying the charge sheet doping density (either by varying the width of the charge sheet or by varying the doping density itself) was calculated to have the greatest effect on the operational characteristics of the DOES.

With increasing charge sheet doping density, the I-V characteristic is seen to change from a 'diode'-like curve at  $N_0=2.2\times10^{12}$  cm<sup>-2</sup> to a 'S'-like curve at  $N_0=4.4\times10^{12}$  cm<sup>-2</sup> with switching voltage,  $V_{so}\approx6.2V$ .

Figure 2.7: The calculated logarithm of current density versus applied voltage (log(J)-V) characteristics of the Si/SiGe-based DOES with charge sheet doping density,  $N_{ob}$ , as a parameter.

Also, the current before switching decreases markedly with higher doping in the sheet whereas the holding current is seen to increase.

Figures 2.8 represents a compilation of switching voltages with varying N<sub>0</sub> for set doping in the barrier and active layers. A family of curves can be generated if the doping in the barrier or active layers is varied. It was also found in these simulations that the switching current is relatively insensitive to N<sub>0</sub>. This implies that the criterion of switch back in the DOES - unity gain in the feedback loop, is primarily determined by the current and not by the voltage. In retrospect, this is a fairly obvious point exemplified the fact that the DOES is a current drive

device. For a device of dimension 50µm x 50µm square, we can predict that the switching current is should be approximately 0.25mA.

Figure 2.8: Predicted switching voltages,  $V_{SO}$ , as a function of areal charge sheet doping density,  $N_{Ob}$ .

## 2.6.2 Effect of Barrier Layer Doping

The doping on either side of the charge sheet is also important in determining the I-V characteristics of the DOES. Figure 2.9 plots the equilibrium barrier surface potential,  $V_{bo}$ , versus the magnitude of the doping in the barrier layer,  $N_{bo}$ .

Figure 2.9: The calculated equilibrium barrier surface potential,  $V_{bo}$  (open squares), and the interface charge density,  $p_0$  (dark triangles), versus the doping density in the barrier layer,  $N_{bo}$ .

With increasing  $N_{bo}$ ,  $V_{bo}$  is initially insensitive from  $N_{bo}$ =1x10<sup>15</sup> cm<sup>-3</sup> to 1x10<sup>17</sup> cm<sup>-3</sup>. However, over the range of  $N_{bo}$  from 1x10<sup>17</sup> cm<sup>-3</sup> to 1x10<sup>18</sup> cm<sup>-3</sup>,  $V_{bo}$  falls quickly. The barrier surface potential measures the height of the triangular barrier for electron flow into the active region. Large  $V_{bo}$  values impedes electron flow into the active layer and necessitates high switching voltages.

Also plotted in Fig. 2.9 along with  $V_{bo}$  is the equilibrium interface charge density,  $p_0$ , which mirrors the dependence of  $V_{bo}$  but changes values over nine orders of magnitude.

Figures 2.7-2.9 show graphically how sensitive the I-V characteristics and the parameters of energy band diagram are to the design of the heterostructure. Implicitly, this allows a device designer freedom to optimize a heterostructure for particular operational characteristics and, in general, manipulate the design parameter space. However, this sensitivity also necessitates very rigid control over growth and doping.

#### 2.6.3 Effect of Injection Current

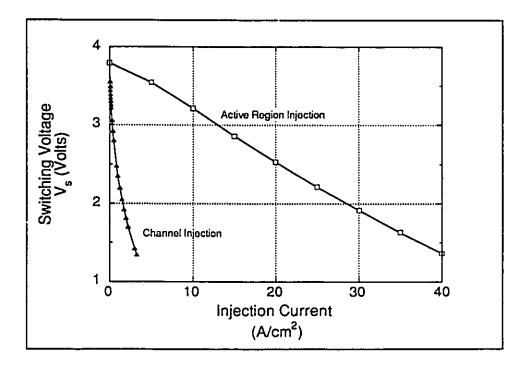

The calculated effect of  $J_{ib}$  is illustrated in Fig. 2.10. The simulated I-V characteristics of the DOES with structure identical to that of Fig. 2.2 (except  $N_{ob}$ =3.7x10<sup>12</sup> cm<sup>-2</sup>) shows that with increasing  $J_{ib}$  the curves partially nest toward lower  $V_s$  and higher  $I_s$ . Also, the current before switching is seen to increase as the energy barrier to electron flow is progressively reduced by the hole accumulation at the n-n heterojunction.

A summary of this effect is seen in Fig. 2.11 where  $V_S$  and  $I_S$  are plotted against  $J_{ib}$ . This summary will prove useful in Chapter 6 to compare experimental results obtained with the three-terminal DOES. With increasing  $J_{ib}$  a monotonic reduction of  $V_S$  is observed. When extended to high channel injection values  $V_S$  is calculated to saturate at the holding voltage of the device. The switching current also increases with increasing  $J_{ib}$ .

In Fig. 2.12, the switching voltage versus injection current is plotted for third-terminal injection directly into the inversion layer,  $J_{ib}$ , and into the active layer,  $J_{ia}$ . Injection into the inversion layer is seen to lower device switching voltage more effectively than into the active layer. This is explained by examining the path that current injected into the active layer is required to take in order

Figure 2.10: The calculated logarithmic of current density versus voltage (log(J)-V) characteristic with current injected at the n-n heterojunction, J<sub>ib</sub>, as a parameter.

to effect the inversion channel hole population (Fig. 2.5(c)). Electrons injected in the active layer are first required to diffuse across the p-n junction formed by the active layer and the substrate. This, in turn, causes hole injection from the substrate into the active layer. Only a fraction of these will add to the hole population at the hetero-interface and thereby affect the barrier voltage.

Figure 2.11: Calculated switching voltages and currents as a function of current injected directly into the channel via the third-terminal.

Figure 2.12: The predicted switching voltages as a function of current injected into the active layer and directly into the inversion channel.

| 1 | Q | 539 |  |

|---|---|-----|--|

|   |   |     |  |

|   | • |     |  |

|   |   |     |  |

|   |   |     |  |

|   | ; |     |  |

|   |   |     |  |

|   |   |     |  |

|   |   |     |  |

|   |   |     |  |

|   |   |     |  |

|   |   |     |  |

|   |   |     |  |

|   |   |     |  |

# **CHAPTER 3**

## OPERATIONAL THEORY OF THE HFET

This chapter reviews the theory of operation of the HFET and relates that theory to the salient electrical characteristics of the device. The DOES and the HFET are distinct devices but much of the theory of the DOES concerning the inversion charge will be reiterated for the HFET.

## 3.1 Si/SiGe HFET: An Operational Discussion

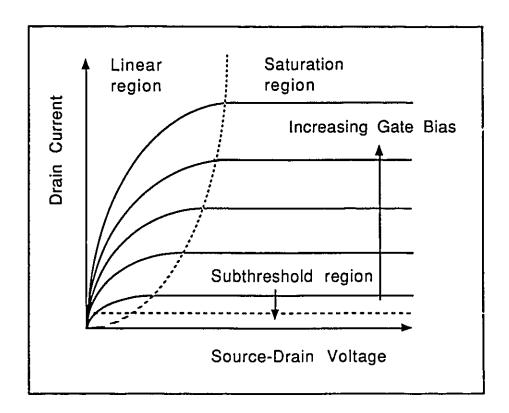

In the preceding section, it was stated that within the strained SiGe-well at the n-n hetero-interface, an accumulation of holes is found to be sensitive to the bias on the emitter terminal. The basis of the SiGe HFET is to use this hole accumulation as a conductive channel between source and drain contacts. To visualize this, a three-dimensional energy band diagram is required (Fig. 3.1).

In the SiGe HFET, all voltage biases are referenced with respect to the source terminal which is at ground potential. The gate of the SiGe-HFET serves much the same purpose as the gate of a MOSFET. That is, to modulate the channel charge by changing the width of the depletion regions, and thereby affect the source to drain conduction properties. An idealized family of FET current-voltage (I-V) characteristics are seen in Fig. 3.2 where gate bias is used as a parametric variable. In Fig. 3.2, three regions of operation can be identified; i) the linear region where current increases monotonically with increasing source-

drain bias, ii) the saturation region where the output impedance approaches infinite values, and iii) the subthreshold region where regardless of source-drain bias very little current is extracted. However, because the Si/SiGe DOES heterostructure is inherently bipolar and capable of

0

Figure 3.1: Schematic three-dimensional energy band diagram of the HFET with non-zero source and drain potential.

feedback, the dependence of the hole accumulation on the gate bias requires a more complex treatment than the MOSFET. In the ideal theory of the MOSFET,

1

the oxide forms a perfect insulator and gate leakage is not considered. This treatment is given by Lebby [62] and is qualitatively described in this section. In the HFET, gate leakage is a consequence of forward-biasing the n-n heterojunction and can have dramatic effect on the channel properties. In the discussion to follow, the idealized theory of HFET operation is first presented along with some of the important figures of merit for this class of device. Following this, issues related to gate leakage and feedback are examined.

÷

Figure 3.2: Idealized source-drain current-voltage characteristics for a FET with gate bias as a parametric variable. The dashed line delineates between the various region of operation.

#### 3.2 Conduction Equations

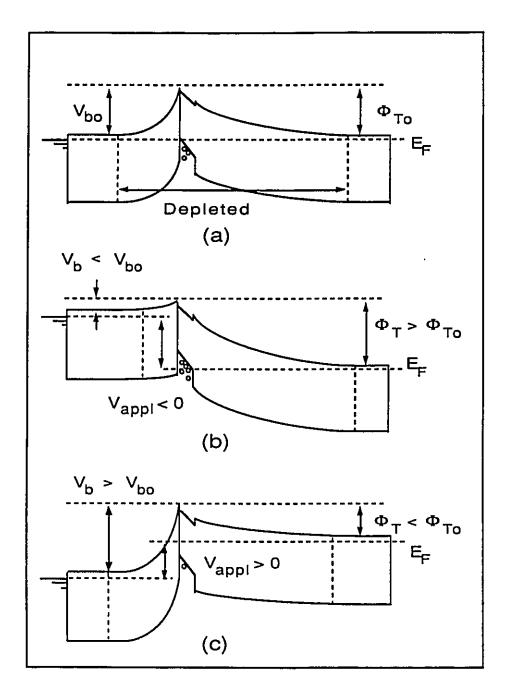

Assuming that the barrier layer acts as a perfect insulator allows an analysis of the HFET which much resembles the description of a MOSFET. However, even with such a simplification, the channel charge requires a self-consistent analysis. In the HFET, the hole density in the channel increases when the gate to charge sheet diode is forward-biased. Biasing the gate negatively with respect to the source ( $V_{gs}$ <0) causes a reduction of the barrier layer depletion region which from the charge neutrality requirements (eqn. 2.1), causes an increase in the hole population in the channel.

15

Assuming no gate leakage, the diode formed by the active region and the charge sheet becomes reverse-biased in response to a negative  $V_{gs}$  and the depletion layer in the active region expands. Hypothetically, this reduces the over-all increase in the hole population since some of the decrease in the barrier layer charge goes to increase the active layer charge. Conversely, a positive  $V_{gs}$  reduces the hole population in the channel since the barrier depletion region expands in response to the reverse-bias. Graphically, these bias conditions are illustrated in Fig. 3.3(a,b,c). When the Fermi level at the drain is raised with respect to the source (negative  $V_{ds}$ ) the hole population along the channel will gradually decrease. At the drain end of the conduction channel the gate to drain potential is  $V_{gs}$ - $V_{ds}$ .

The current-voltage characteristics of the HFET can be described using a gradual channel approximation outlined by Shur [63]. Briefly, the current from source to drain at any position x along the channel can be shown to be

$$I_{ds} = q\mu_p p_0(x) \frac{dV_c(x)}{dx} W, \qquad (3.1)$$

where;

$$V_c(0) = 0 \& V_c(L) = V_{ds}$$

where  $\mu_p$  is the low-field hole mobility in the channel,  $p_0(x)$  is the position dependent hole density in the channel, W is the gate width of the HFET, and  $dV_c(x)/dx$  is the electric field at position x. Equation 3.1 is only valid for those  $V_{ds}$  values at which an inverted hole population still exists (ie.  $p_0(L) \ge 0$ ). In eqn. 3.1,  $I_{ds}$  would seem to change along the length of the channel as  $dV_c(x)/dx$  increases from source to drain. In actuality,  $p_0(x)$  decreases at a rate which balances the increasing electric field term to yield a constant  $I_{ds}$  value across the channel. However, as  $V_{ds}$  is progressively increased,  $I_{ds}$  will increase accordingly. When an inverted hole population no longer exists for a particular  $V_{ds}$ , then the channel is described as 'pinched-off'. For  $V_{ds}$  values beyond those where the channel is pinched-off, no increase in  $I_{ds}$  is expected on the first order. The channel current is said to be saturated at  $I_{dsat}$  and the output impedance of the device is infinitely large. In practice, other factors such as channel length modulation, velocity saturation, and avalanche breakdown near the drain will combine to yield the non-ideal non-saturating current-voltage characteristics [63].

An important figure of merit in the HFET is transconductance,  $g_{\rm m}$ , given by:

$$g_{m} = \frac{\partial I_{ds}}{\partial V_{gs}} \Big|_{constant V_{ds}}$$

(3.2)

Figure 3.3: The energy band diagram of the HFET (at  $V_{ds}=0V$ ) (a) under equilibrium conditions, (b) with a negative potential on the gate with respect to the source (forward-bias), and (c) with a positive potential on the gate (reverse-bias).

Using eqn. 3.1, g<sub>m</sub> is given by:

$$g_{\rm m} = \mu_{\rm p}(\frac{W}{L})c_{\rm i} V_{\rm dsat} \tag{3.3}$$

where  $c_i$  is the capacitance per unit area of the gate electrode. Using long channel devices where channel width, W, and the length, L, are approximately equal, the device transconductance and saturation voltage,  $V_{dsat}$ , may be used to calculate channel mobility. Alternatively, the differential drain conductance,  $g_{ds}$ , is given by

$$g_{ds} = \frac{dI_{ds}}{dV_{ds}} \Big|_{V_{gs}} = \mu_p \left( \underline{W} \right) c_i \left( V_G - V_{Th} \right)$$

(3.4)

for

$$V_{G}-V_{Th} < V_{dsat}$$

Using eqn. 3.4 and measuring the slope of the linear region of the FET I-V characteristic for a specific  $V_{gs}$ , the channel mobility can also be calculated. However, this calculation also requires knowledge of the threshold voltage,  $V_{Th}$ , and the capacitance per unit area of gate.