# UNIFIED DC/SMALL-SIGNAL/LARGE-SIGNAL MICROWAVE DEVICE MODELING AND CIRCUIT OPTIMIZATION

$\mathbf{B}\mathbf{y}$

SHEN YE, B.S. (Eng.), M.Eng. (Shanghai University of Technology)

A Thesis

Submitted to the School of Graduate Studies

in Partial Fulfilment of the Requirements

for the Degree

Doctor of Philosophy

McMaster University

© Copyright by Shen Ye, June 1991

UNIFIED DC/SMALL-SIGNAL/LARGE-SIGNAL MICROWAVE DEVICE MODELING AND CIRCUIT OPTIMIZATION

DOCTOR OF PHILOSOPHY (1991)

McMASTER UNIVERSITY

(Electrical and Computer Engineering)

Hamilton, Ontario

TITLE:

Unified DC/Small-Signal/Large-Signal Microwave Device

Modeling and Circuit Optimization

AUTHOR:

Shen Ye

B.S. (Eng.), M.Eng.

(Shanghai University of Technology)

SUPERVISOR:

J.W. Bandler

Professor, Department of Electrical and Computer Engineering

B.Sc. (Eng.), Ph.D., D.Sc. (Eng.) (University of London)

D.I.C. (Imperial College)

P.Eng. (Province of Ontario)

C.Eng. F.I.E.E. (United Kingdom)

Fellow, I.E.E.E.

Fellow, Royal Society of Canada

NUMBER OF PAGES: xv, 184

# Abstract

This thesis presents an in-depth investigation of microwave FET device modeling and unified DC, small-signal and large-signal computer-aided design of microwave circuits.

Advances in microwave FET device modeling are reviewed. The physical, analytical and nonlinear empirical models and their relationship are discussed.

A new integrated DC and small-signal FET model parameter extraction approach is presented which simultaneously fits the FET model responses to the DC and small-signal measurements. Detailed formulas are derived to explore the relationship between the nonlinear DC equivalent circuit and the small-signal equivalent circuit linearized at given bias points.

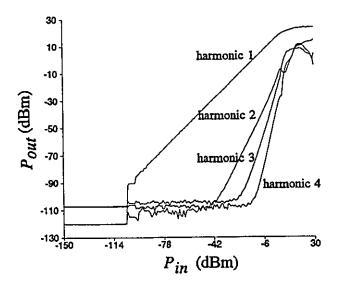

A large-signal FET model parameter extraction approach is introduced. The power spectrum responses of the model are calculated employing the newly exploited harmonic balance (HB) technique for efficient nonlinear frequency-domain circuit simulation. State-of-the-art optimization tools are used to fit model responses to corresponding measurements. Special considerations are given to weighting factor assignment which takes into account the wide spread magnitude of the error functions in the optimization.

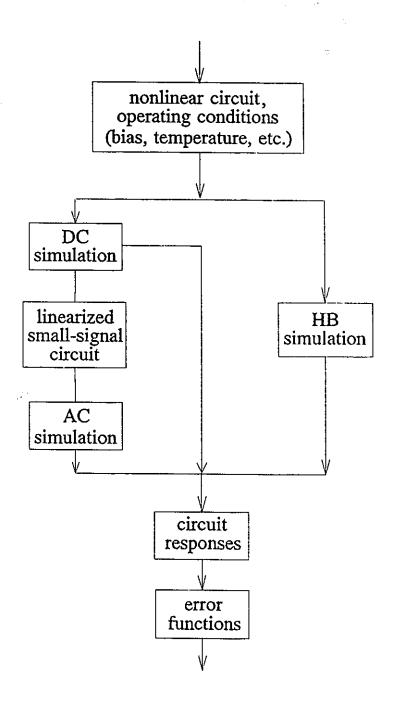

The HB technique for nonlinear frequency domain simulation of microwave circuits is discussed. The formulations of the HB equation, its Jacobian matrix and the related discrete Fourier transformation are described. A new approach for constructing the multiport matrix especially suitable for HB based circuit optimization is presented.

The theoretical background of the unified DC, small-signal and large-signal circuit simulation is investigated. Derivations of the inherent consistency between DC/small-signal simulation and general nonlinear HB simulation are presented. A novel circuit design concept is introduced which explores the seamless integration of DC/small-signal and large-signal circuit design with multi-dimensional specifications. Examples of simultaneous DC/small-signal/large-signal FET model parameter extraction and a small-signal broad-band amplifier design are given to demonstrate the concept.

# Acknowledgements

The author wishes to express his sincere appreciation to Dr. J.W. Bandler for his encouragement, expert guidance and supervision throughout the course of this work. He also thanks Dr. S.H. Chisholm and Prof. J. Siddall, members of his Supervisory Committee, for their continuing interest.

The author appreciates the opportunity given to him by Dr. Bandler to be involved in industrially relevant projects developed by Optimization Systems Associates Inc., Ontario. Specifically, the author has benefitted from the participation of the development of the RoMPE TM and HarPE TM microwave CAD systems. Certain FET measurement data was kindly made available by Raytheon Company, Lexington, MA and Texas Instruments Inc., Dallas, TX.

It is the author's pleasure to acknowledge inspiring discussions with Dr. R.M. Biernacki, Dr. Q.J. Zhang, Dr. S.H. Chen, J. Song and Q. Cai of the Simulation Optimization Systems Research Laboratory (SOSRL). Valuable suggestions by Dr. Q.J. Zhang and Dr. S.H. Chen have helped the author to develop, improve and test new ideas.

The technical assistance of G. Simpson of SOSRL in managing computer resources is acknowledged.

The financial assistance provided in part by the Natural Sciences and Engineering Research Council of Canada through Grants OGP0007239, STR0040923 and EQP0043573,

the Department of Electrical and Computer Engineering through a Teaching Assistantship and Scholarship, and the Ministry of Colleges and Universities through an Ontario Graduate Scholarship is gratefully acknowledged.

# Contents

| A  | BST] | RACT                                           | iii  |  |  |  |  |

|----|------|------------------------------------------------|------|--|--|--|--|

| A  | CKN  | OWLEDGEMENTS                                   | v    |  |  |  |  |

| LJ | ST ( | OF FIGURES                                     | хi   |  |  |  |  |

| LI | ST ( | OF TABLES                                      | xv   |  |  |  |  |

| 1  | INI  | TRODUCTION                                     | 1    |  |  |  |  |

| 2  | RE   | VIEW OF FET DEVICE MODELING                    | 7    |  |  |  |  |

|    | 2.1  | Introduction                                   | . 7  |  |  |  |  |

|    | 2.2  | Physical MESFET Device Modeling                | . 8  |  |  |  |  |

|    |      | 2.2.1 2-Dimensional Numerical Model            | . 8  |  |  |  |  |

|    |      | 2.2.2 2-Dimensional Quasi-Static Model         | . 11 |  |  |  |  |

|    | 2.3  | Nonlinear Empirical FET Model                  | . 12 |  |  |  |  |

|    | 2.4  | Analytical Model                               | . 18 |  |  |  |  |

|    | 2.5  | Relationship between Different Models          | . 20 |  |  |  |  |

|    | 2.6  | Concluding Remarks                             | . 22 |  |  |  |  |

| 3  | INT  | TEGRATED FET MODEL PARAMETER EXTRACTION        | 23   |  |  |  |  |

|    | 3.1  | Introduction                                   | . 23 |  |  |  |  |

|    | 3.2  | Feasibility of Integrated Parameter Extraction | . 25 |  |  |  |  |

|    |      | 3.2.1 The Identifiability of Model Parameters  | . 25 |  |  |  |  |

|    |      | 3.2.2 A Simple RC Circuit Example              | . 20 |  |  |  |  |

|    | 3.3  |                                                |      |  |  |  |  |

|    |      | 3.3.1 Classification of Model Parameters       |      |  |  |  |  |

|    |      | 3.3.2 A Practical FET Device Example           | . 31 |  |  |  |  |

|    | 3.4  | Multi-bias DC and AC Modeling Optimization     |      |  |  |  |  |

|   | 3.5= | Cradient Computation                                                   |  |  |  |  |  |  |

|---|------|------------------------------------------------------------------------|--|--|--|--|--|--|

|   |      | 3.5.1 Gradient for DC Response                                         |  |  |  |  |  |  |

|   |      | 3.5.2 Gradient for AC Responses                                        |  |  |  |  |  |  |

|   | 3.6  | Program Structure for Integrated Parameter Extraction                  |  |  |  |  |  |  |

|   | 3.7  | Examples                                                               |  |  |  |  |  |  |

|   |      | 3.7.1 Case 1 — Materka and Kacprzak Model                              |  |  |  |  |  |  |

|   |      | 3.7.2 Case 2 — Curtice Model                                           |  |  |  |  |  |  |

|   |      | 3.7.3 Selection of Starting Point for Optimization                     |  |  |  |  |  |  |

|   | 3.8  | Concluding Remarks                                                     |  |  |  |  |  |  |

| 4 | UT   | ILIZING THE HARMONIC BALANCE TECHNIQUE                                 |  |  |  |  |  |  |

|   | 4.1  | Introduction                                                           |  |  |  |  |  |  |

|   | 4.2  | Nonlinear Circuit Simulation Using the HB Method 5                     |  |  |  |  |  |  |

|   | 4.3  | Discrete Fourier Transformation for HB Simulation 6                    |  |  |  |  |  |  |

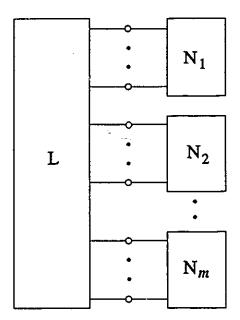

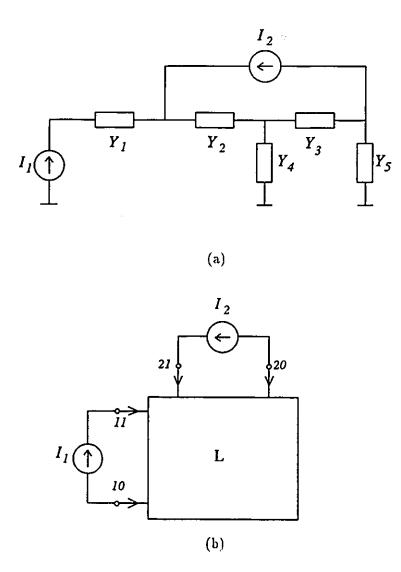

|   | 4.4  | An Efficient Multiport Matrix Construction Approach 6                  |  |  |  |  |  |  |

|   |      | 4.4.1 Multiport Matrix                                                 |  |  |  |  |  |  |

|   |      | 4.4.2 An Example                                                       |  |  |  |  |  |  |

|   |      | 4.4.3 Discussion                                                       |  |  |  |  |  |  |

|   | 4.5  | Concluding Remarks                                                     |  |  |  |  |  |  |

| 5 | LA   | RGE-SIGNAL FET MODEL PARAMETER EXTRACTION 78                           |  |  |  |  |  |  |

|   | 5.1  | Introduction                                                           |  |  |  |  |  |  |

|   | 5.2  | Large-Signal Measurements                                              |  |  |  |  |  |  |

|   | 5.3  | Optimization for Large-Signal Parameter Extraction                     |  |  |  |  |  |  |

|   | 5.4  | Nonlinear Circuit Simulation and Gradient Calculation                  |  |  |  |  |  |  |

|   |      | 5.4.1 Nonlinear Circuit Simulation Using the HB Method                 |  |  |  |  |  |  |

|   |      | 5.4.2 Gradient Calculation by Nonlinear Adjoint Sensitivity Analysis 8 |  |  |  |  |  |  |

|   | 5.5  | Weight Assignment Procedure                                            |  |  |  |  |  |  |

|   | 5.6  | Program Structure for Large-Signal Parameter Extraction                |  |  |  |  |  |  |

|   | 5.7  | Numerical Examples                                                     |  |  |  |  |  |  |

|   |      | 5.7.1 Case 1 — Test of Robustness, Reliability and Efficiency 8        |  |  |  |  |  |  |

|   |      | 5.7.2 Case 2 — Fitting to the Curtice Model                            |  |  |  |  |  |  |

|   |      | 5.7.3 Case 3 — Processing Measurement Data from Texas Instruments 9    |  |  |  |  |  |  |

|   | 5.8  | Concluding Remarks                                                     |  |  |  |  |  |  |

| 6 | UN   | IFIED CIRCUIT SIMULATION AND DESIGN 10                                 |  |  |  |  |  |  |

|   | 6.1  | Introduction                                                           |  |  |  |  |  |  |

|                  | 6.2               | 2 Unified Circuit Simulation |                                                                 |      |  |

|------------------|-------------------|------------------------------|-----------------------------------------------------------------|------|--|

|                  |                   |                              | Harmonic Balance Simulation Under Small-Signal Conditions       | 104  |  |

|                  |                   | 6.2.2                        | Jacobian Matrix For HB Simulation Under Small-Signal Conditions | 104  |  |

|                  |                   | 0.2.2                        | (HBSS)                                                          | 107  |  |

|                  |                   | 6.2.3                        | Consistency of DC/Small-Signal/Large-Signal Analysis            | 109  |  |

|                  |                   | 6.2.4                        | Numerical Verification                                          | 110  |  |

|                  |                   | 6.2.5                        | Remark                                                          |      |  |

|                  | 6.3               |                              | d Circuit Design                                                | 113  |  |

|                  | 6.4               |                              | - · · · · · · · · · · · · · · · · · · ·                         | 113  |  |

|                  | 6.5               |                              | ple 1 — FET Model Parameter Extraction                          | 116  |  |

|                  |                   |                              | ple 2 — Small-Signal Amplifier Design                           | 125  |  |

|                  | 6.6               | Concli                       | ading Remarks                                                   | .131 |  |

| 7                | CO                | NCLU                         | SIONS                                                           | 133  |  |

| A                | CIR               | CUIT                         | AND DATA FILES                                                  | 139  |  |

|                  | A.1               | Circui                       | t and Data Files for Examples in Chapter 3                      | 139  |  |

|                  |                   |                              | Case 1                                                          | 139  |  |

|                  |                   |                              | Case 1 — Extended with Simulated Data                           | 142  |  |

|                  |                   |                              | Case 2°                                                         | 147  |  |

|                  | A.2               |                              | t and Data Files for Examples in Chapter 5                      | 150  |  |

|                  |                   |                              | Case 3                                                          | 150  |  |

|                  | A.3               |                              | t and Data Files for Examples in Chapter 6                      | 155  |  |

|                  |                   | A.3.1                        | Circuit File for the Example in Section 6.2.4                   | 155  |  |

|                  |                   | A.3.2                        | Example 1                                                       | 155  |  |

|                  |                   | A.3.3                        | Example 2                                                       |      |  |

|                  |                   | - 21010                      | 2.000.00.00.00.00.00.00.00.00.00.00.00.0                        | 100  |  |

| В                | RE                | LATIO                        | NSHIP BETWEEN $I_{B0}$ AND $V_{BC}$ IN THE MATERKA              |      |  |

|                  | MO                | DEL                          |                                                                 | 167  |  |

|                  |                   |                              |                                                                 |      |  |

| C                |                   |                              | EAR CHARGE EXPRESSIONS FOR THE MATERKA                          |      |  |

|                  | MO                | DEL                          |                                                                 | 169  |  |

| D                | PO                | WER :                        | SPECTRUM EXPRESSION FOR $ S_{21} $                              | 173  |  |

| BIBLIOGRAPHY 175 |                   |                              |                                                                 | 175  |  |

| A                | AUTHOR INDEX 181  |                              |                                                                 |      |  |

| SI               | SUBJECT INDEX 183 |                              |                                                                 |      |  |

| - '              |                   | - <b></b>                    |                                                                 |      |  |

# List of Figures

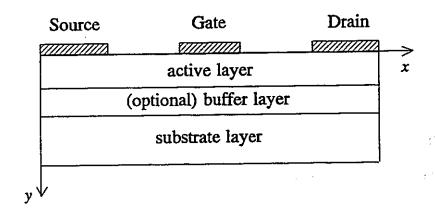

| 2.1          | A Schematic diagram of a MESFET device                                        | 8  |

|--------------|-------------------------------------------------------------------------------|----|

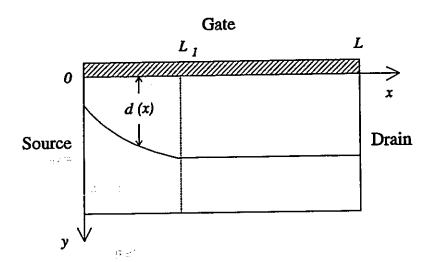

| 2.2          | Active region of a MESFET                                                     | 12 |

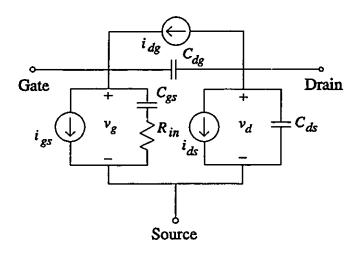

| 2.3          | A basic nonlinear intrinsic FET model                                         | 14 |

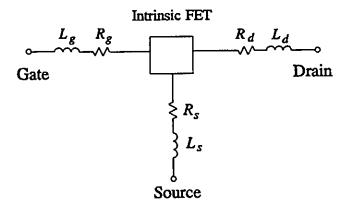

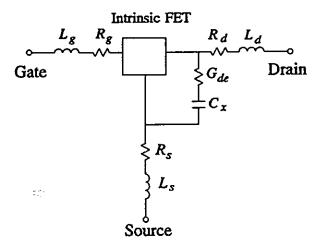

| 2.4          | Basic extrinsic part of a FET model                                           | 14 |

| 2.5          | High frequency compensation branch $(G_{de}, C_x)$ for the FET model          | 16 |

| 2.6          | FET equivalent circuit at zero drain-to-source bias voltage                   | 17 |

| 2.7          | Active region of a MESFET for the analytical model                            | 18 |

| 2.8          | Schematic MESFET diagram for the Ladbrooke model                              | 20 |

| 2.9          | Relationship between different FET device models                              | 21 |

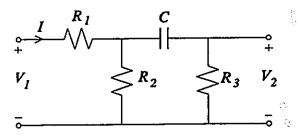

| 3.1          | Simple RC linear circuit example                                              | 26 |

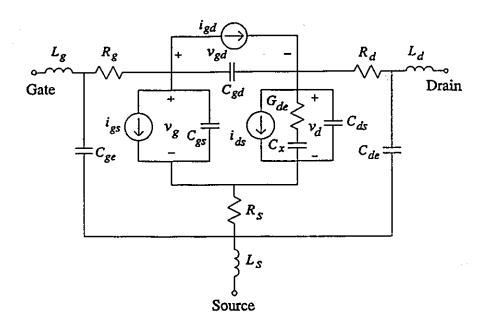

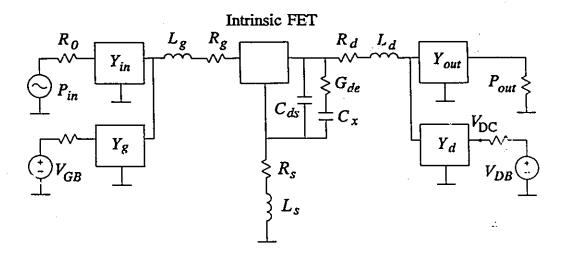

| 3.2          | A nonlinear FET device equivalent circuit model                               | 28 |

| 3.3          | The Materka and Kacprzak nonlinear FET model                                  | 32 |

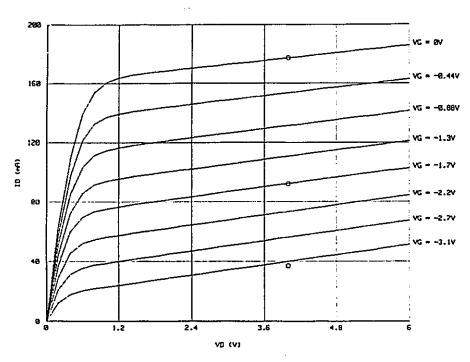

| 3.4          | DC I-V curve fit for Case 1                                                   | 44 |

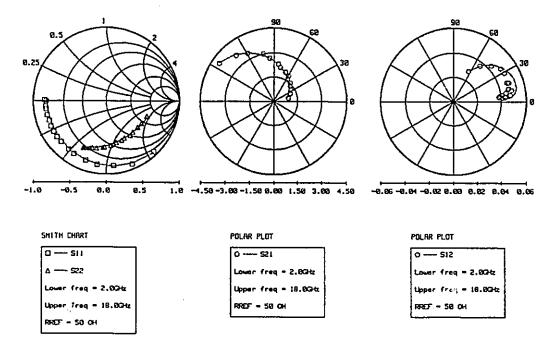

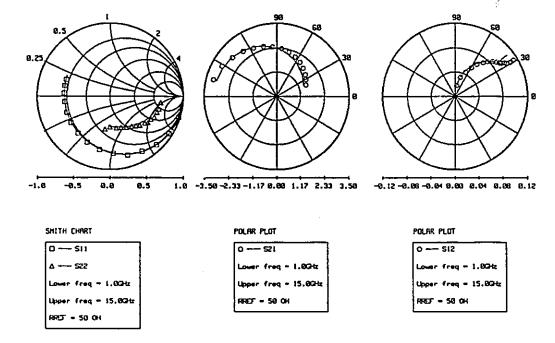

| 3.5          | S parameter fit for Case 1 at bias $V_{GB}=0.0$ and $V_{DB}=4$ V              | 44 |

| 3.6          | S parameter fit for Case 1 at bias $V_{GB}=-1.74$ and $V_{DB}=4$ V            | 45 |

| 3.7          | S parameter fit for Case 1 at bias $V_{GB}=-3.10$ and $V_{DB}=4$ V            | 45 |

| 3.8          | The Curtice and Ettenberg nonlinear FET model                                 | 48 |

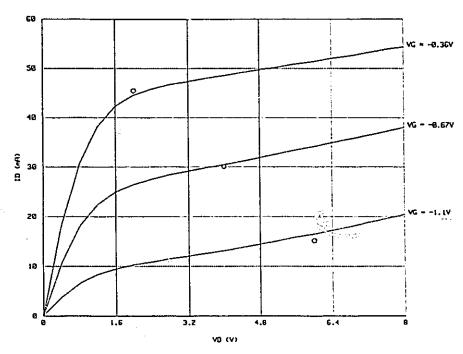

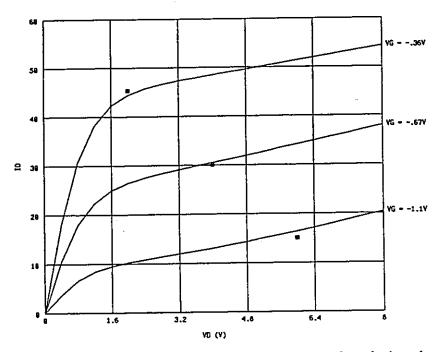

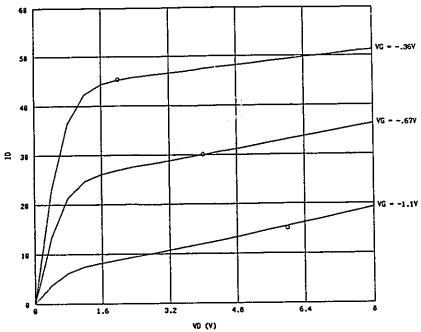

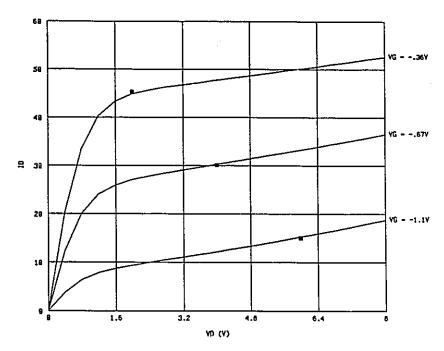

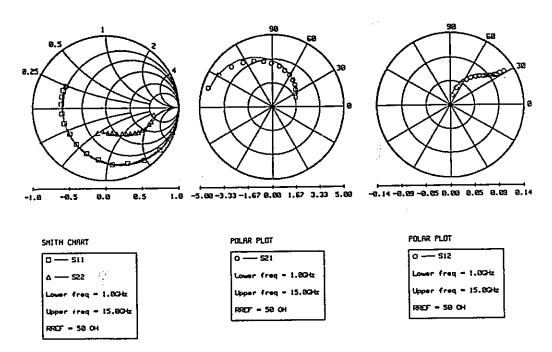

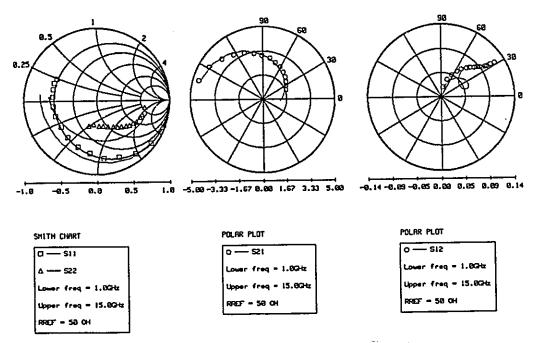

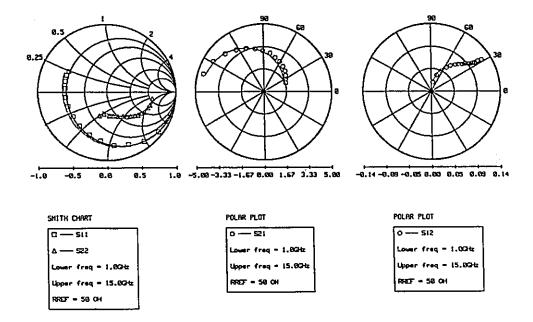

| 3.9          | DC $I-V$ curve at the solution of Case 2                                      | 51 |

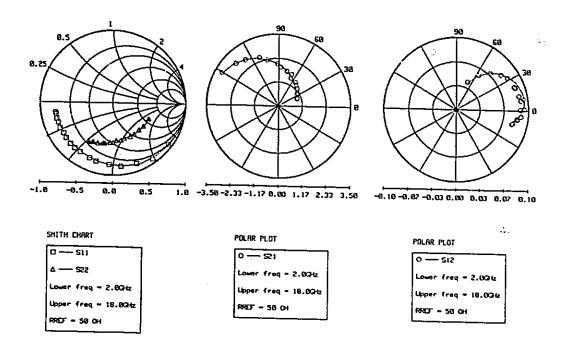

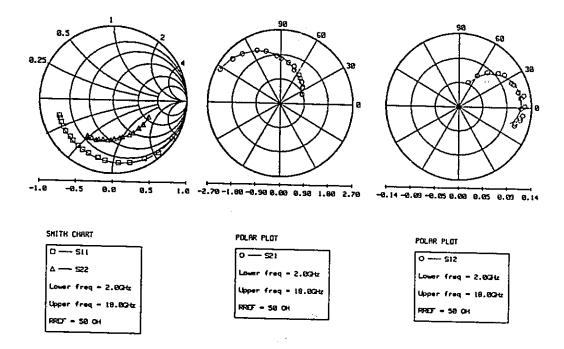

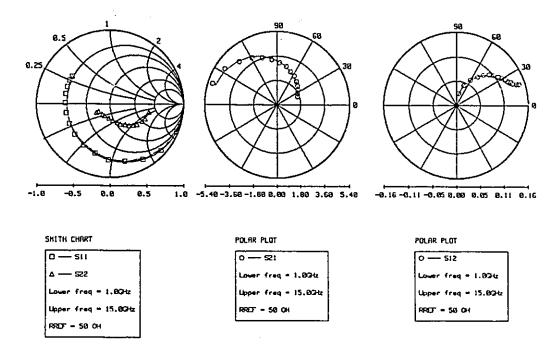

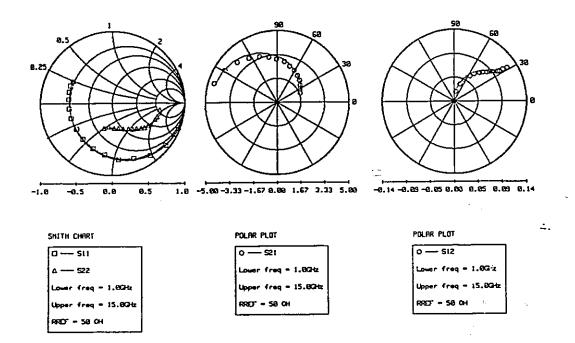

| 3.10         | S parameter fit for Case 2 at bias $V_{GB}=-0.361$ and $V_{DB}=2$ V           | 51 |

| <b>3.</b> 11 | S parameter fit for Case 2 at bias $V_{GB} = -0.667$ and $V_{DB} = 4$ V       | 52 |

| 3.12         | $S$ parameter fit for Case 2 at bias $V_{GB}=-1.062$ and $V_{DB}=6\mathrm{V}$ | 52 |

| 4.1          | Diagram for illustrating the HB simulation technique                          | 58 |

| 4.2          | Circuit example for illustrating the multiport matrix construction approach   | 70 |

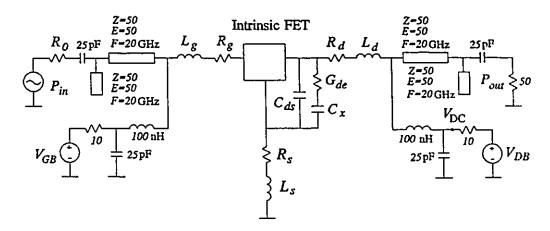

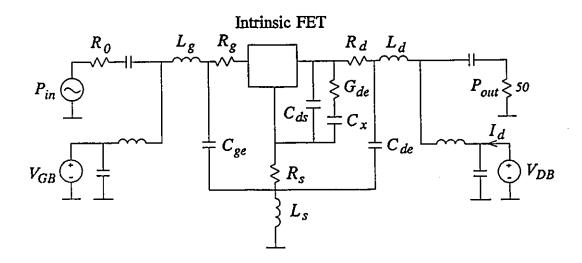

| 5.1          | Circuit setup for large-signal multiharmonic FET measurement                  | 77 |

| 5.2          | Block diagram for illustrating circuit simulation using the HB method         | 80 |

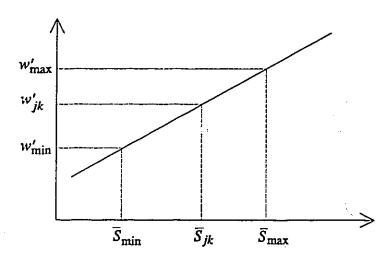

| 5.3          | Linear mapping for balanced weight assignment                                 | 86 |

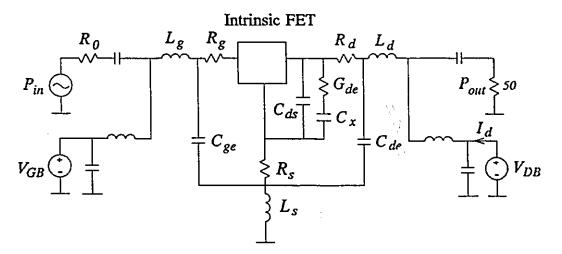

| 5.4  | Modeling circuit diagram for Case 1 and Case 2                                    |

|------|-----------------------------------------------------------------------------------|

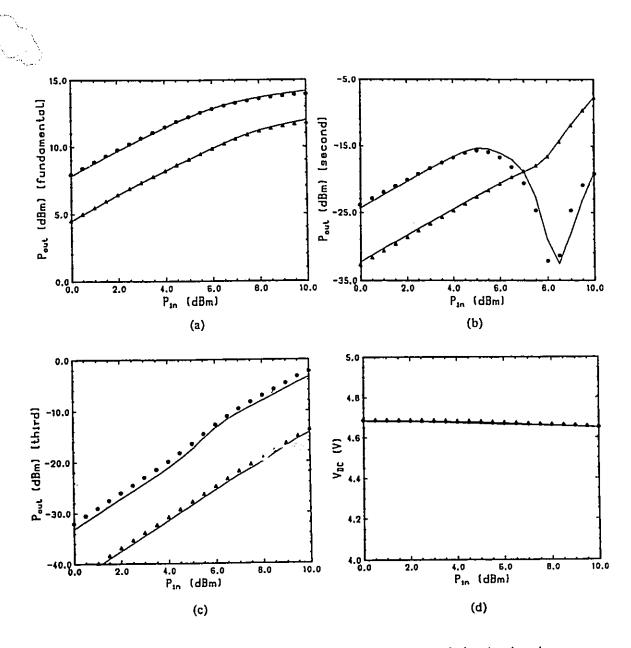

| 5.5  | Agreement between the model responses and the simulated measurements in           |

|      | Case 2                                                                            |

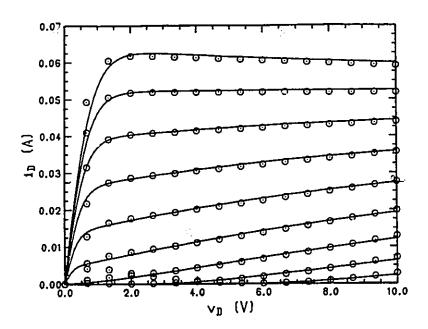

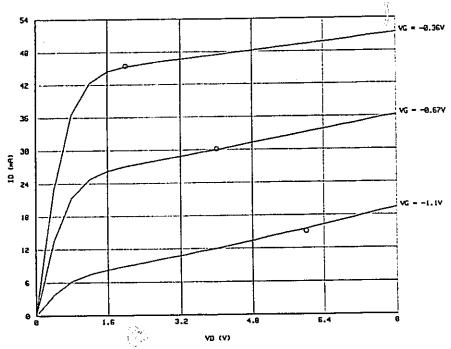

| 5.6  | DC I-V curve fit for Case 2                                                       |

| 5.7  | Modeling circuit diagram for Case 3 98                                            |

| 5.8  | Agreement between the Curtice model responses and the measurements for            |

|      | Case 3 at bias point $V_{GB}=-0.373 \text{V}$ and $V_{DB}=2 \text{V}$             |

| 5.9  | Agreement between the Curtice model responses and the measurements for            |

|      | Case 3 at bias point $V_{GB}=-0.673 	ext{V}$ and $V_{DB}=4 	ext{V}$               |

| 5.10 | DC characteristics of the Curtice model after optimization                        |

| 6.1  | Single FET circuit with the Curtice nonlinear intrinsic FET model 111             |

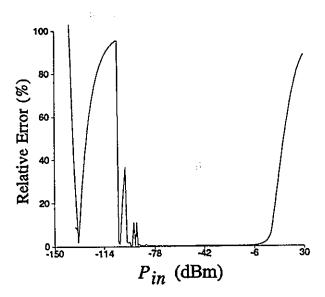

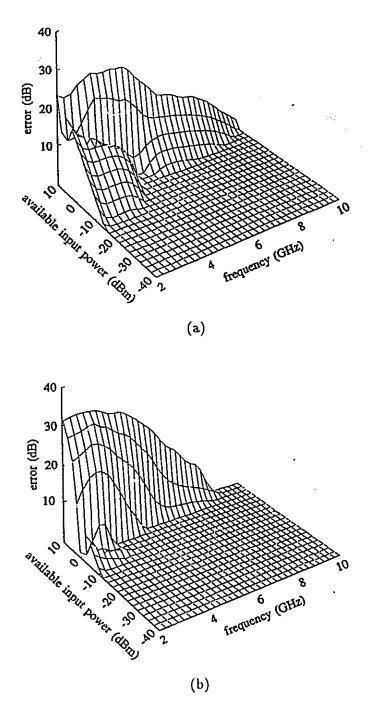

| 6.2  | Relative error between the matched transducer power gain calculated by HB         |

|      | and $ S_{21} $ by small-signal analysis with respect to different available input |

|      | power levels                                                                      |

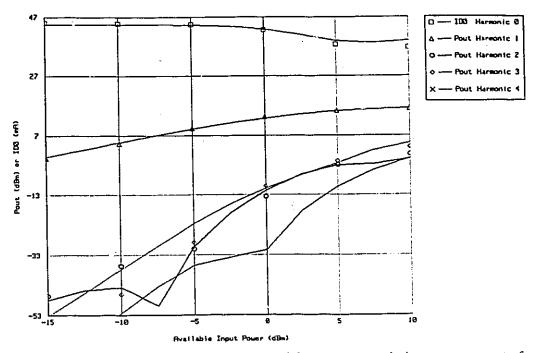

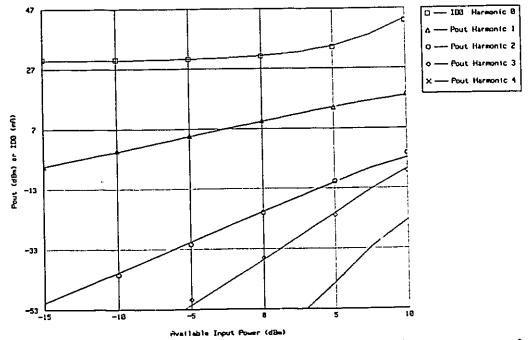

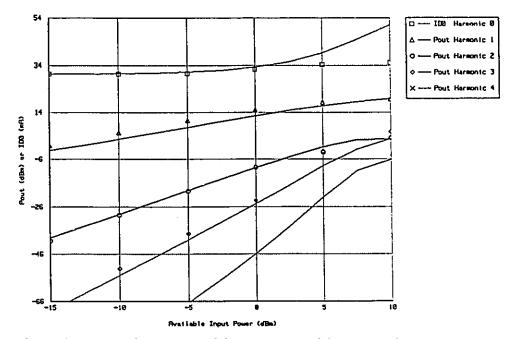

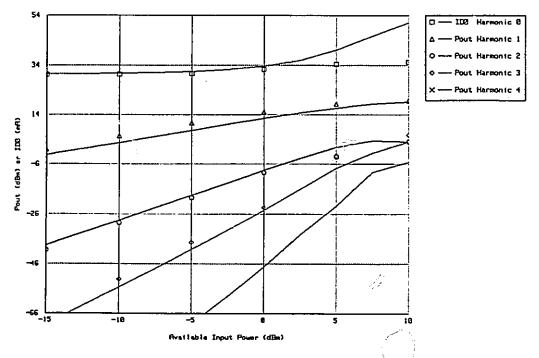

| 6.3  | Spectrum response of the single FET circuit                                       |

| 6.4  | Block diagram for illustrating the unified circuit design                         |

| 6.5  | DC agreement between model and measurements at the solution obtained              |

|      | from DC/small-signal measurement fitting                                          |

| 6.6  | DC agreement between model and measurements at the solution obtained              |

|      | from large-signal measurement fitting                                             |

| 6.7  | DC agreement between model and measurements at the solution obtained              |

|      | from simultaneous DC/small-signal and large-signal fitting                        |

| 6.8  | Agreement between model responses and measured $S$ parameters where the           |

|      | model is obtained from DC and small-signal measurement fitting 125                |

| 6.9  | Agreement between model responses and measured $S$ parameters where the           |

|      | model is obtained from large-signal measurement fitting                           |

| 6.10 | Agreement between model responses and measured $S$ parameters where the           |

|      | model is obtained from simultaneous DC, small- and large-signal measure-          |

|      | ment fitting                                                                      |

| 6.11 | Agreement between model responses and large-signal measurements where             |

|      | the model is extracted from large-signal measurement fitting                      |

| 6.12 | Agreement between model responses and large-signal measurements where             |

|      | the model is extracted from simultaneous DC, small-signal and large-signal        |

|      | measurement fitting                                                               |

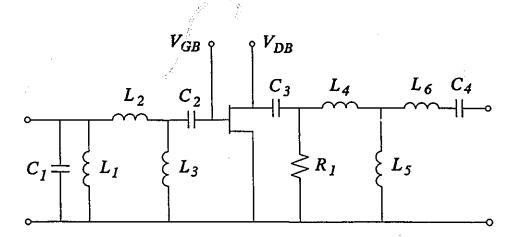

| 6 13 | 4-8GHz small-signal broadband amplifier                                           |

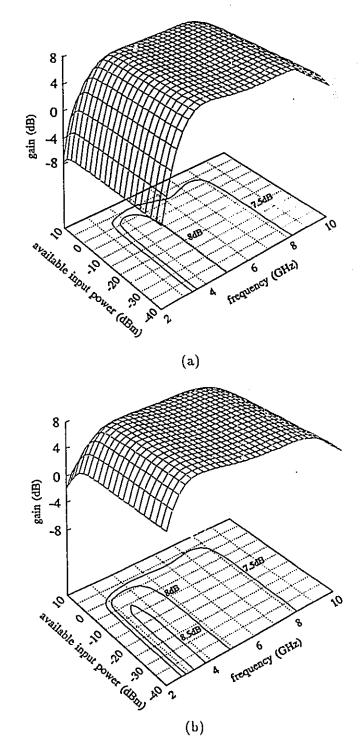

| 6.14 Comparison of the gain response surfaces obtained by small-signal design an |                                                                             |  |  |  |  |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                                                                                  | simultaneous small- and large-signal design                                 |  |  |  |  |

| 6.15                                                                             | Comparison of the error surfaces obtained by small-signal design and simul- |  |  |  |  |

|                                                                                  | taneous small- and large-signal design                                      |  |  |  |  |

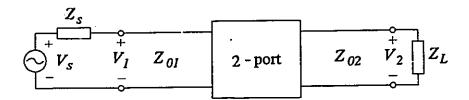

| D.1                                                                              | A general two-port circuit                                                  |  |  |  |  |

i,

# List of Tables

Š,

| 3.1 | Definitions of the model parameters                                  | 30  |

|-----|----------------------------------------------------------------------|-----|

| 3.2 | Parameter classifications for the Materka and Kacprzak FET model     | 34  |

| 3.3 | Measurement data set for Case 1                                      | 42  |

| 3.4 | Parameter values of the FET model for Case 1                         | 43  |

| 3.5 | Extra DC measurement data for Case 1                                 | 47  |

| 3.6 | Parameter values for Case 2                                          | 50  |

| 4.1 | Notation and definition for the HB equation                          | 57  |

| 5.1 | Parameter values of the intrinsic FET model for Case 1               | 90  |

| 5.2 | Match errors between the measurements and model responses for Case 1 | 92  |

| 5.3 | Parameters of the Curtice model used for Case 2                      | 94  |

| 5.4 | Bias-input-frequency combinations for Case 2                         | 95  |

| 5.5 | Bias-input-frequency combinations for Case 3                         | 99  |

| 5.6 | Parameter values of the Curtice model for Case 3                     | 100 |

| 6.1 | Measurement sets used for parameter extraction in Example 1          | 118 |

| 6.2 | Solutions of the parameter extraction in Example 1                   | 119 |

| 6.3 | FET model parameter values for Example 2                             | 126 |

| 6.4 | Solutions of the small-signal amplifier design in Example 2          | 128 |

|   |   | 3 |    |  |

|---|---|---|----|--|

|   |   |   | ·  |  |

|   | • |   |    |  |

|   |   |   |    |  |

| ÷ |   |   | e. |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

|   |   |   |    |  |

## Chapter 1

# INTRODUCTION

Computer-aided design (CAD) of circuit systems in electrical engineering has been growing ever since its introduction in the late 1960's (Temes and Calahan 1967 [67]). Today, circuit CAD systems are applied in areas such as analog, digital, and microwave circuit design. They cover circuits ranging from simple and linear to sophisticated large-scale nonlinear systems.

In microwave engineering, commercial CAD software programs have been developed. Some of them are widely used by the microwave society, for example, the linear microwave circuit CAD systems *Touchstone* by EEsof Inc., [71] and *SuperCompact* by Compact Software Inc., [65]. Today, some of the programs offer the user a design environment to allow the user to enter an actual circuit schematic, i.e., geometrically enter a circuit element-by-element. The program can schematically capture the user input, convert it to a circuit file form, analyze the circuit, and produce the final layout for manufacturing. Such comprehensive software has substantially increased the quality and productivity of circuit designs.

Though the comprehensiveness of those CAD tools has been improved significantly compared with early CAD systems, the essential requirement of a good CAD system remains and will remain the same: accurate device models, efficient circuit simulation, and based upon these, powerful circuit optimization.

The field effect transistor (FET) device is one of the fundamental active elements used in microwave circuits. Analysis and modeling of the FET device has been of continuing research interest since it was introduced by Shockley in 1952 [59]. Theoretical studies of the device physics have been carried out by device engineers. With physical modeling, the behaviour of the FET device can be thoroughly analyzed. The physical model plays an important role in understanding the device mechanism. By using the geometrical, material and process parameters, the device characteristics can be predicted before the device is manufactured. The critical drawback of such physical models, however, is the computational intensity required in numerically solving field related problems. The analytical model, on the other hand, relates the device physical parameters to equivalent circuit elements. It is relatively simple and easy to implement. However, its application is largely limited by the conditions under which the model is derived by simplification.

The empirical model, namely, the FET equivalent circuit model, has been extensively used in circuit design area. Its simplicity and flexibility makes it more efficient in circuit simulation than the physical model. There are different levels of equivalent circuits suitable for different kinds of applications. Compared with physical or analytical models, the equivalent circuit model is usually determined after the device has been manufactured, since the parameters of the model are identified with the aid of device measurements.

The main interest in the equivalent circuit model is in the circuit structure, the circuit element characterization, and the way of determining the parameters of the model elements. Several nonlinear bias-dependent FET device models have been proposed, for example, the Materka and Kacprzak model [48]. In order to identify the model parameters for a particular device, it is customary to determine some parameters using DC measurements and others using AC (RF) small-signal measurements. Such a separate determination procedure may not yield a reliable model, because a parameter determined solely from DC measurements may not be suitable for microwave simulation, and the information contained

in AC measurements is not fully utilized.

For a circuit containing nonlinear elements, the small-signal response may be simulated using small-signal equivalent circuit models for those nonlinear elements, and the nonlinear time-domain response using nonlinear equivalent circuit models. Recently, a highly efficient frequency domain simulation technique, the harmonic balance (HB) technique, has been exploited, and implemented into some commercial software products, for example, Libra from EEsof Inc., [45] and Microwave Harmonica from Compact Software Inc., [49]. However, most of them are not coupled between small-signal simulation and large-signal simulation, which imposes restrictions on possible comprehensive design of a circuit containing nonlinear devices.

This thesis addresses itself to the topics of nonlinear empirical FET device modeling and unified DC, small-signal and large-signal circuit simulation and optimization. Emphasis will be given to nonlinear FET model parameter extraction.

In Chapter 2, we review the progress of the FET device modeling and model parameter extraction. Various approaches are reviewed, including physical, analytical and empirical device modeling. In physical device modeling, the 2-dimensional and quasi-static models are examined. General descriptions of analytical modeling and nonlinear empirical device modeling are provided. Comparisons are made between those different models, and their relationships are described.

Chapter 3 describes an approach of nonlinear FET model parameter extraction. Compared with the conventional approaches in the literature, this approach utilizes the functional relationship between DC and small-signal equivalent circuits of the FET model, and extracts the model parameters by simultaneously matching the model responses to the DC and multi-frequency small-signal measurements at many bias points. The uniqueness and reliability of the model are improved. Popular nonlinear FET equivalent circuit models with practical industrial measurement data are used to demonstrate the feasibility of the

approach.

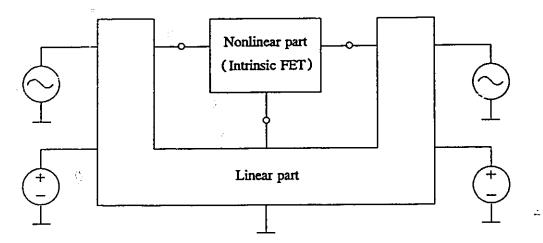

To facilitate the nonlinear large-signal simulation, we discuss the HB technique in Chapter 4. The concept of HB simulation is illustrated. The formulation and the Jacobian matrix of the HB equation are provided, together with the discrete Fourier transformation which dynamically relates the nonlinear elements simulated in the time domain and the linear part of the circuit simulated in the frequency domain. Also, a new approach for constructing the linear multiport matrix is presented in Chapter 4. The approach is simple and efficient, and can be incorporated in the HB simulation to improve 'ne performance when the HB simulation is integrated in a circuit optimization environment.

A large-signal FET model parameter extraction technique is shown in Chapter 5, where the parameters are determined under real (large-signal) working conditions. The application of the powerful nonlinear adjoint-based optimization, which employs the HB method as the nonlinear circuit simulation technique, is described. The approach simultaneously processes multi-bias, multi-power input, multi-fundamental-frequency excitations, and multiharmonic measurements to uniquely reveal the parameters of the FET model.

A new design strategy for microwave circuit design is presented in Chapter 6. The analytical relationship between DC/small-signal and frequency domain large-signal analyzes is derived. A consistent device model is used for both small-signal and large-signal circuit simulation and design. Unified circuit optimization can be performed with respect to multi-dimensional specifications, such as bias, frequency, input power, temperature, etc. In one example the nonlinear FET model parameters are extracted by simultaneously matching DC, small-signal and large-signal measurements. In the other example a small-signal broadband amplifier is designed with its upper-end of the dynamic range expanded.

The thesis is concluded in Chapter 7 with some suggestions for future research and development.

The author contributed substantially to the following original developments presented in the thesis:

Ţ.

13

- Integrated nonlinear FET equivalent circuit model parameter extraction by simultaneously matching model responses to the DC and small-signal measurements, where the DC and small-signal equivalent circuits are functionally related.

- 2. Nonlinear large-signal FET equivalent circuit model parameter extraction using a IIB based optimization technique.

- 3. An efficient approach to establish a linear circuit matrix for IIB simulation.

- 4. Theoretical derivation of the consistency of DC/small-signal analysis and the frequency-domain nonlinear large-signal HB analysis.

- 5. Presentation of unified DC/small-signal/large-signal circuit design strategy.

- 6. Applications of unified circuit design for FET model parameter extraction and small-signal amplifier design.

$\partial$

## Chapter 2

# REVIEW OF FET DEVICE MODELING

#### 2.1 INTRODUCTION

For circuit simulation, it is necessary to understand the behaviour of the devices used in the circuit. Device modeling, consequently, is of fundamental importance to circuit designs. The philosophy of device modeling is to establish a model such that it can produce the same output as the actual device would in a working environment.

<

Consider the nonlinear active MESFET device. A schematic description of the MESFET device is given in Figure 2.1. The device has wide applications in microwave engineering, such as amplifiers, mixers, etc. Various MESFET modeling approaches have been seen in the literature. A brief survey by Estreich (1987) [33] gives a schematic description of MESFET device modeling progress for monolithic microwave integrated circuits (MMICs).

Following the pioneering work done by Shockley (1952) [59], important developments in MESFET modeling may be divided into physical modeling, which simulates the actual device from the internal physical mechanism, empirical modeling, which simulates the actual device by approximating the external behaviours, and analytical modeling, which may be considered as one between physical modeling and empirical modeling. We review briefly these different modeling approaches in the following sections.

Figure 2.1: A schematic diagram of a MESFET device.

## 2.2 PHYSICAL MESFET DEVICE MODELING

The physical modeling approach may further be separated into 2-dimensional numerical and 2-dimensional quasi-static modeling approaches.

#### 2.2.1 2-Dimensional Numerical Model

Consider the schematic MESFET diagram shown in Figure 2.1. By applying Poisson's equation and Boltzmann's transport equation, Reiser (1973) [57] presented a 2-D numerical model which simulates the MESFET device by using its geometrical and material parameters. There are two basic partial differential equations governing the behaviour of the device: the Poisson equation

$$\nabla^2 \psi = -\frac{q}{\epsilon_0 \epsilon_r} (N - n) \tag{2.1}$$

and the current continuity equation

$$\nabla \cdot \boldsymbol{J}_n = q \frac{\partial n}{\partial t} \tag{2.2}$$

where  $\psi$  is the electric potential,  $\epsilon_0$  is the permittivity of free space,  $\epsilon_r$  is the relative permittivity of the material, q is the electron charge, N represents the doping density (or

doping profile), n is the electron density distribution. These two equations are defined for the device active, buffer and substrate regions.

The conducting current density can be expressed as

$$\boldsymbol{J}_n = q(n\mu\boldsymbol{E} + D\boldsymbol{\nabla}n) \tag{2.3}$$

where the electric field E is derived from

$$E = -\nabla \psi \tag{2.4}$$

and  $\mu$  and D are electron mobility and diffusion coefficient, respectively. The doping density N is a function of geometric position. The electric potential  $\psi$  and the electron density distribution n are both functions of geometrical position and time.

The boundary conditions related to the Poisson and current continuity equations are taken such that (1) the electric potential and the electron density distribution at the drain, gate and source contacts are constant, (2) there is no current flowing through the boundary between the surrounding space and the material excluding the contacts, in other words, the gradient parts of either electric potential or electron density distribution perpendicular to the surface, except for the drain, gate and source contacts, are zero.

Finite difference or finite element techniques can be applied to numerically solve those two basic equations in time steps. The time domain solutions of the electric field E and electron density n can be used to compute the time domain drain and gate currents using (2.3)

$$J_t = J_n + \epsilon_0 \epsilon_r \frac{\partial E}{\partial t} \tag{2.5}$$

where  $J_t$  stands for total current density, from which the time domain response of the device can be obtained.

The DC characteristic of the device can be obtained if the time-domain simulation reaches steady state. Using a step-response calculation together with Fourier transformation

.....

[43], we can derive frequency domain small-signal Y parameters of the device at a given bias point from the time domain simulation, i.e., a small-signal equivalent circuit for the device can be determined and used for circuit simulation [57].

This 2-D numerical model provides detailed insight into device operation. It can theoretically be used for circuit simulation purposes. In practice, however, the most serious disadvantage which limits the application of this model has been the intensive computation time required for the time domain simulation. Also in Reiser's 2-D model, the velocity overshoot phenomenon which exists in the short-gate length FET was not considered.

Curtice et al. (1981) [25] and Snowden et al. (1987) [63] proposed a temperature model and a energy model, respectively, to incorporate the velocity overshoot phenomenon. Besides the electric potential and electron density distribution being considered as variables in the simulation, the electron temperature distribution is also included as a variable and iteratively solved together with the other two variables, i.e.,  $\psi$  and n. The accuracy of the model is therefore improved, though at cost of even higher computational intensity.

On the other hand, an approach to approximate the effect of velocity overshoot was proposed by Thornber (1982) [68], Kizilyalli and Artaki (1989) [39]. The principle is based on the observation that velocity overshoot occurs at an area where the electric field has a large gradient with respect to the longitudinal direction. Hence a modification term proportional to the magnitude of the gradient of the electric field is introduced to approximate the effect of velocity overshoot, i.e.,

$$J_n = q \left( n\mu E + D\nabla n + n\mu L(E) \frac{\partial E}{\partial x} x^0 \right)$$

(2.6)

where L(E) is a length coefficient used to add the velocity overshoot effect to the current density  $J_n$ , x is the longitudinal coordinate parallel to the gate surface,  $x_0$  is the unit vector in the x direction, and E is the Euclidian norm of E. Compared with the temperature or energy model, this approximation approach is simple and easy to implement. However, more

studies in this area are required, especially in the determination of the length coefficient L(E).

#### 2.2.2 2-Dimensional Quasi-Static Model

In order to take advantage of the 2-D numerical model while making it computationally feasible, a simplified 2-D model has been proposed by Khatibzadeh and Trew (1988) [38]. The so-called Trew model starts from the basic Poisson equation (2.1) and the current continuity equation (2.2). Instead of solving the electric potential  $\psi(x,y)$  and the electron density distribution n(x,y) directly, a functional form for n(x,y) is assumed a priori. Therefore,  $\psi$  can be solved analytically.

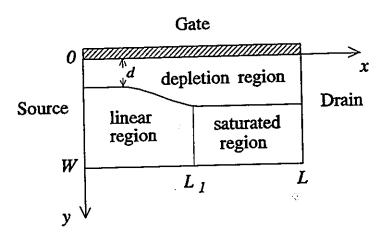

Consider the active region of a MESFET used in the Trew model, as shown in Figure 2.2. The electron density distribution n(x, y) is assumed

$$n(x,y) = [1 + \gamma(x - L_1)] T(d(x), y) N(y)$$

(2.7)

where  $\gamma$  is a model parameter, T(d(x), y) is a transition function and N(y) is the doping density which is assumed to be a function of y. The transition function T(d(x), y) is defined as

$$T(d(x), y) = 1 - \frac{1}{1 + \exp\left[\frac{y - d(x)}{\lambda}\right]}$$

(2.8)

where d(x) is the effective depletion-layer depth and  $\lambda$  is a model parameter describing the width of the transition region.

Similar to the 2-D numerical model, this model accepts arbitrary doping density N, and the drain and source currents can be calculated for given gate and drain biases. Since the electric potential  $\psi$  can be solved analytically due to the assumed electron density distribution n(x,y), there is no numerical method involved in solving the partial differential equations. Thus, this model is much more efficient than the true 2-D numerical model.

<u>.</u> .

Figure 2.2: Active region of a MESFET.

Because of its relative efficiency and the ability to simulate the device from basic geometrical and material parameters, the model has been used in circuit designs, for example by Bandler et al. (1990) [20].

Due to the fact that the electron density distribution n is a function of time t as well as space x and y, an accurate time domain response can not be obtained theoretically. Thus, we term it a 2-D quasi-static model. On the other hand, the computation time required to simulate this model is still very long compared with the empirical model to be discussed in the next section.

### 2.3 NONLINEAR EMPIRICAL FET MODEL

The nonlinear empirical FET model, first proposed by Willing et al. (1978) [72], is a model which approximates the electrical behaviour of the FET device by an empirical equivalent circuit. The formation of the equivalent circuit is consistent with the physical structure and working mechanism of the FET, for instance, the circuit correspondence described by Pucel et al. [54].

Several different nonlinear empirical FET models have been proposed since Willing's

work. For instance, the Tajima model (1981) [66], the Materka model (1985) [48], the Curtice model (1985) [27] and the Statz model (1987) [64]. A basic nonlinear intrinsic FET model can be shown as in Figure 2.3, where  $C_{gs}$ ,  $C_{dg}$ ,  $C_{ds}$  and  $R_{in}$  can all be bias dependent as well as three nonlinear current sources  $i_{gs}$ ,  $i_{dg}$ , and  $i_{ds}$ . Besides the slight differences in the circuit structure, the major differences between these models are in the expressions used to characterize the nonlinear circuit elements, most noticeably, the nonlinear current source  $i_{ds}$ . As an example,  $i_{ds}$  from the Curtice model reads

$$i_{ds} = (A_0 + A_1 v_1 + A_2 v_1^2 + A_3 v_1^3) \tanh(\gamma v_d)$$

$$v_1 = v_a (t - \tau) (1 + \beta (V_{DS0} - v_d))$$

where  $A_0$ ,  $A_1$ ,  $A_2$ ,  $A_3$ ,  $\beta$ ,  $\gamma$ ,  $\tau$  and  $V_{DS0}$  are model parameters, and  $i_{ds}$  from the Statz model is

$$i_{ds} = \frac{\beta(v_g - V_T)^2}{1 + b(v_g - V_T)} \left\{ 1 - \left(1 - \frac{\alpha v_d}{3}\right)^3 \right\} (1 + \lambda v_d),$$

$$for \quad 0 < v_d < \frac{3}{\alpha}$$

$$i_{ds} = \frac{\beta(v_g - V_T)^2}{1 + b(v_g - V_T)} (1 + \lambda v_d),$$

$$for \quad v_d \ge \frac{3}{\alpha}$$

where  $\beta$ ,  $V_T$ , b,  $\alpha$  and  $\lambda$  are model parameters.

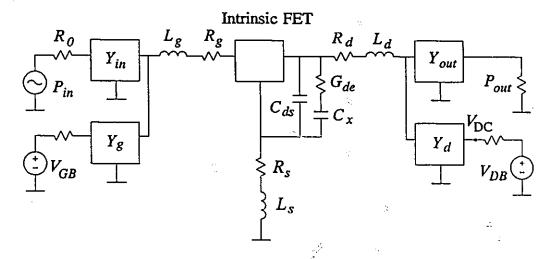

Extrinsic elements of a FET model may include the bond pad effect, the contact effect, the packaging effect, etc., for example,  $R_g$ ,  $R_d$ ,  $R_s$ ,  $L_g$ ,  $L_d$  and  $L_s$  shown in Figure 2.4. These elements are usually considered as bias-independent, i.e., linear elements.

The determination of the parameters of a nonlinear FET model has been discussed in the literature. The principle is to match the model responses as close to the device responses as possible, where the device responses are normally from actual device measurements, though simulation results from physical models may also be taken as simulated measurements.

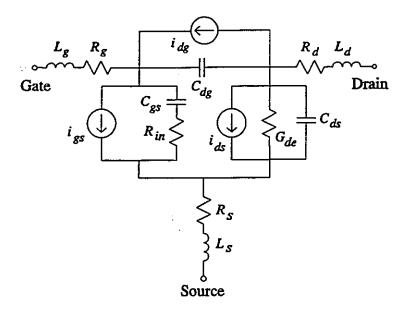

Figure 2.3: A basic nonlinear intrinsic FET model.

Figure 2.4: Basic extrinsic part of a FET model.

The measurements used for nonlinear FET model parameter extraction have been seen, in the literature, in the form of DC, small-signal S parameter, and large-signal load-pull measurements. Because of the indeterminacy of the parameters, different measurements are utilized for determining different sets of the total parameters of the model. Examples are listed as follows.

#### A. Utilizing DC Measurements

Fukui (1979) [34] developed a technique to extract  $R_g$ ,  $R_d$  and  $R_s$  using DC measurements. The technique first determines the gate barrier built-in voltage by gate forward bias DC measurement. Then from the linear part of the DC I-V characteristics,  $R_d + R_s$  can be obtained, as illustrated in Figure 5 of [34]. By measuring the forward gate current in three different ground connections, i.e., source and drain combined, source only and drain only, with applied voltages greater than the gate barrier built-in voltage, three resistance values can be obtained, including  $R_g + R_d$  and  $R_g + R_s$ . Thus,  $R_g$ ,  $R_d$  and  $R_s$  can be obtained.

The full range of DC I-V characteristics is commonly used for determining the parameters of  $i_{ds}$ , for example, by Curtice (1988) [28]. It has been noticed that the output conductance of a GaAs FET behaves quite differently between low and high frequency conditions. On the one hand, a series RC branch was suggested between the intrinsic drain and source to compensate the frequency dependency of the output conductance, as shown in Figure 2.5, by Camacho-Penalosa and Aitchison (1985) [23]. On the other hand, a special DC measurement technique operating at relatively high frequency was proposed, e.g., by Smith  $et\ al.\ (1986)\ [60]$  and Paggi  $et\ al.\ (1988)\ [51]$ , to obtain more accurate DC I-V curves for high frequency purposes.

#### B. Utilizing Small-Signal Measurements

Figure 2.5: High frequency compensation branch  $(G_{de}, C_x)$  for the FET model.

Using small-signal measurements, Willing et al. (1978) [72] first treated the model as a linear small-signal model, and determined the small-signal parameters at various bias conditions. Then polynomial expressions were used to approximate the nonlinear elements of the model, and the coefficients of the polynomials were identified by matching individual polynomials to their corresponding extracted parameter curves.

To improve the identifiability of the model parameters, Curtice et al. (1984) [26] divided the small-signal S parameter measurements into cold and hot circumstances. Cold FET S parameter measurements correspond to zero drain-to-source bias conditions. The equivalent circuit is simplified to a two-port containing no active elements as shown in Figure 2.6.  $L_g$ ,  $L_d$ ,  $L_s$  and  $C_{ds}$  can be determined. Hot FET S parameter measurements are the normal S parameter measurements and are used for extracting parameters of the other capacitive elements.

#### C. Utilizing Large-Signal Load-Pull Measurements

Recently, Epstein et al. (1988) [32] proposed an approach to use large-signal loadpull measurements for FET model parameter extraction. Besides using the Fukui technique, DC I-V curve fitting, cold and hot S parameter measurements to extract model parameters

Figure 2.6: FET equivalent circuit at zero drain-to-source bias voltage.

separately, the final stage is to modify the parameters of  $i_{ds}$ ,  $C_{gs}$ ,  $C_{dg}$ ,  $C_{ds}$  and  $G_{dc}$  by fitting the model power responses to the device load-pull power measurements. Harmonic balance simulation is used.

Summing up, unlike the physical model the parameters of the empirical model elements are determined sequentially in such a way that the model response is as close to the actual device response as possible. Because of this, the empirical model may accurately reproduce the device responses under different bias conditions, provided that the model is appropriate for the device to be modeled. Compared with the 2-D and 2-D quasi-static models, the empirical model is particularly suitable for circuit simulation. It is the kind of model which has been implemented in major commercial software programs, for example, the Curtice model in Libra [45] and Microwave Harmonica [49]. Another apparent advantage of the empirical model is that the model may well be suitable to different kinds of FETs, due to the empirical modeling principle.

For the empirical model, however, it is difficult to relate the model parameters to the device geometrical and material parameters. One empirical model may not be suitable

Figure 2.7: Active region of a MESFET for the analytical model.

for one particular device, since the empirical expression pattern may not be able to fit that particular device response pattern. On the other hand, the uniqueness of the model parameters may be improved by sequential parameter extractions, but the accuracy of the model may be hindered because of lack of freedom in fitting individual measurements.

## 2.4 ANALYTICAL MODEL

The analytical model can be considered as a model between the 2-D numerical model and the empirical model. It starts from the device physics point of view, using device physical parameters. Approximations are taken to reduce the complexity of the problem, so that analytical expressions for the equivalent circuit elements are derived. Different from the empirical model, the element expressions here use device geometrical and material parameters.

A perspective description of the analytical model was given by Pucel et al. (1975) [54]. Consider the intrinsic FET shown in Figure 2.7. The device is divided into a depletion region and a conducting channel, where uniform doping profile N is assumed for both regions.

In the depletion region, the electron density distribution n=0, and the electric field is assumed to be transversal only, i.e.,  $E_y\gg E_x$  and therefore  $E_x$  is neglected in the depletion region. The conducting channel is divided into a linear region and saturated region according to the value of the longitudinal electric field  $E_x$ .  $E_y=0$  is assumed in the linear region, and constant electron density is assumed in the whole channel.

With those simplifications the channel current can be analytically derived [54]. Other elements in the equivalent circuit model are derived accordingly.

One of the basic phenomena, the velocity saturation phenomenon which was not considered by Shockley [59], was included in the model by Pucel et al. [54]. The calculation of the drain current, small-signal equivalent circuit parameters such as the gain  $g_m$  and the gate-to-source capacitance  $C_{gs}$  can be performed by closed form analytic formulas. However, there is a condition upon which the simplifications are based, i.e., the gate length L should be much larger than the channel thickness W.

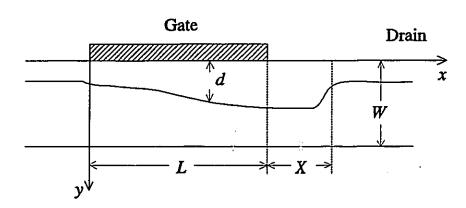

Ladbrooke (1989) [42] developed an analytical model by including the short gate effect existing in submicron MESFETs which have become more popular. The active region of the device is extended by X in the Ladbrooke model, as illustrated in Figure 2.8. An approximate formula was given which relates the length X with device bias voltages as well as physical parameters. Other effects, such as the transversal field in the conducting channel and velocity overshoot, were also considered.

The advantages of the analytical model are its relative simplicity, and closed form analytical expressions which relate the model geometrical and material parameters to the equivalent circuit parameters. Circuit design using device geometrical and material parameters is possible. However, the simplifications required for the analytical model, for example, the assumptions for the doping density and the electron density distribution, limit the simulation accuracy and, therefore, the applications of the model.

Figure 2.8: Schematic MESFET diagram for the Ladbrooke model.

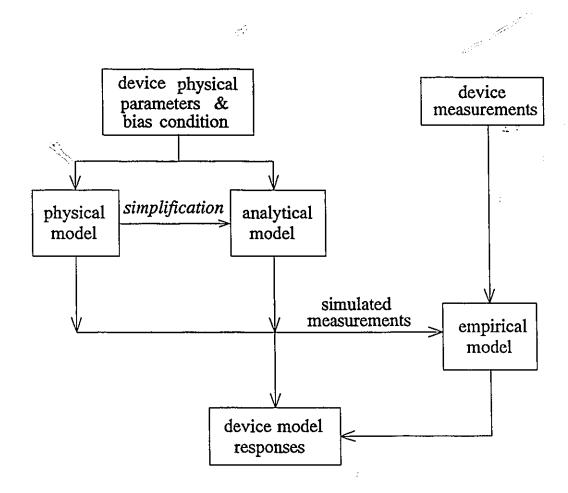

#### 2.5 RELATIONSHIP BETWEEN DIFFERENT MODELS

Examining the different FET models discussed in the previous sections, we may summarize their relationship in Figure 2.9. It can be seen from Figure 2.9 that the 2-D numerical, 2-D quasi-static and analytical models are directly related to the original device. They simulate the device using geometrical and material parameters. The empirical model, on the other hand, relates to the device via device measurements. The model is undefined without certain device response data which is normally from actual device measurements. In terms of circuit simulation, the empirical model is of superior efficiency over other models.

It is natural and has been seen in the literature to connect the empirical model to the physical parameters, i.e., to use the simulation results from the physical models as measurements, and determine the empirical model parameters from those simulated measurements, for example, the works by Reiser (1973) [57], by Ghione et al. (1989) [35], and by Pantoja et al. (1989) [52]. Since the simulated measurements can be obtained off-line, circuit designs can, therefore, be carried out at the physical device level. The feasibility of such an approach, however, depends upon the simulation time of the physical model if optimization at the device level is involved.

Ç

Figure 2.9: Relationship between different FET device models.

Ç

There is still another FET modeling approach, the Monte Carlo particle model, for example [50], which simulates the device down to a microscopic level, suitable for studying the device physics. We will not discuss the Monte Carlo model, for it is out of the scope of this thesis.

#### 2.6 CONCLUDING REMARKS

In this chapter, we briefly reviewed microwave MESFET device modeling. Several modeling approaches were described, namely, physical, analytical and empirical modeling, and the relationships between them were illustrated.

It can be seen that the nonlinear empirical model, though indirectly related to the device geometrical and material parameters, is of superior efficiency in circuit simulation programs. When we apply the simulation results obtained from other physical models as simulated measurements to determine its parameters, the empirical model can effectively be used to predict the designed circuit behaviour without actual device measurements.

A principal interest of nonlinear empirical FET modeling is how to efficiently and reliably identify the parameters when the measurements are given. This is a principal theme in the following chapters. We will discuss nonlinear empirical FET model parameter extraction approaches and related circuit simulation techniques, since parameter extraction is one of the key aspects of applying the empirical model in microwave engineering.

Because of the characteristics of empirical modeling, we will not discriminate between devices in the following chapters.

15

### Chapter 3

....

# INTEGRATED FET MODEL PARAMETER EXTRACTION

1.

#### 3.1 INTRODUCTION

In Chapter 2, we reviewed several FET modeling approaches. We showed that the empirical model, due to its equivalent circuit format, is consistent with normal circuit simulation techniques, and therefore, is particularly efficient from the computational point of view. In circuit design involving optimization, the circuit needs to be repeatedly simulated, making the empirical model fundamentally important. In this chapter we develop a technique of extracting nonlinear empirical FET model parameters from DC and small-signal measurements.

Conventionally, the parameters are extracted by minimizing the difference between the model responses and the measurements. As discussed in Chapter 2, in order to alleviate indeterminacy as well as for simplicity, techniques have been implemented (e.g., Curtice and Ettenberg [27], Kondoh [40], Materka and Kacprzak [48]) which separate the DC, low-frequency, and high-frequency measurements and divide the model parameters into corresponding subsets. This defines a set of subproblems to be solved sequentially. Such a sequentially decoupled solution, however, may not be reliable: a parameter determined solely from DC measurements may not be suitable for the purpose of microwave simulation,

and the information contained in AC measurements is not fully utilized.

Bandler, Chen and Daijavad (1986) [5] proposed a multicircuit algorithm which can improve the uniqueness of the solution by simultaneously processing multiple sets of S-parameter measurements made under different bias conditions. However, the authors assumed for computational purposes that the model elements were either completely bias-independent or arbitrarily bias-dependent.

The approach presented in this chapter by Bandler, Chen, Ye and Zhang (1988) [10] not only attempts to match DC and AC measurements simultaneously, but also employs the DC characteristics of the device as constraints on the bias-dependent parameters. This enables us to use more efficiently the information contained in both DC and non-zero frequency measurements and reduce the degrees of freedom by imposing constraints on bias-dependent parameters, thus improving the identifiability and reliability of the parameters extracted.

In the following sections, we first demonstrate the feasibility and usefulness of integrating DC and AC modeling in one optimization problem. A simple RC circuit is used to illustrate the integrated modeling concept. The FET model parameter extraction optimization problem with both DC and AC responses is then formulated. Depending upon different situations, both  $\ell_1$  and  $\ell_2$  optimization techniques can be used for parameter extraction. The sensitivity calculation of the model responses employing adjoint analysis is described in detail, which significantly improves accuracy and efficiency compared with the conventional perturbation approach. Numerical examples are given to demonstrate the modeling approach.

# 3.2 FEASIBILITY OF INTEGRATED PARAMETER EXTRACTION

#### 3.2.1 The Identifiability of Model Parameters

To illustrate identifiability of the model parameters, we utilize the concept of analog circuit fault diagnosis [4,5]. Consider a system with a complex-valued vector of responses

$$h(\phi) = [h_1(\phi) \cdots h_m(\phi)]^T$$

where  $\phi = [\phi_1 \cdots \phi_n]^T$  is the parameter to be identified from the response  $h(\phi)$ , and we assume  $m \geq n$ .

It is shown by Bandler and Salama in [4] that, if

$$abla h^T(\phi) \left[

abla h^T(\phi)

ight]^T$$

is of full rank, the parameter  $\phi$  is locally identifiable, where  $\nabla$  is the partial derivative operator  $\partial/\partial\phi$ . In other words, if

$$\operatorname{Rank}\left(\nabla h^{T}(\phi)\left[\nabla h^{T}(\phi)\right]^{T}\right) = n \tag{3.1}$$

$\phi$  has unique local solution(s) when solved from the following nonlinear equations

$$f_j - h_j(\phi) = 0, \quad j = 1, \ldots, m$$

where  $f_j$  is the measured value of response  $h_j(\phi)$ .

It is not difficult to see that the measure of identifiability of  $\phi$  in (3.1) is equivalent to testing the rank of the  $m \times n$  Jacobian matrix

$$J = \left[\nabla h^T(\phi)\right]^T. \tag{3.2}$$

If the rank of matrix J is less than n, then  $\phi$  will not be uniquely identifiable from h. Equation (3.1) also shows that by simultaneously processing DC and AC responses, we may

Figure 3.1: Simple RC linear circuit example.

increase the identifiability of  $\phi$ , because the dimension m of  $h(\phi)$  is increased compared with separately processing DC and AC responses.

#### 3.2.2 A Simple RC Circuit Example

As an example to illustrate that combining DC and AC modeling is both feasible and useful for parameter extraction, let us examine the simple linear RC circuit shown in Figure 3.1. The unknown parameters are  $\phi = [R_1 \ R_2 \ C]^T$ .  $R_3$  is assumed to be a known resistor. We also assume the responses to be the DC current I, under the DC excitation  $V_1 = V_{DC}$ , as

$$I = \frac{V_{\rm DC}}{R_1 + R_2} \tag{3.3}$$

and the AC (complex) voltage  $V_2$ , under the AC excitation  $V_1 = V_{AC}$ , as

$$V_2 = \frac{V_{AC}R_2R_3sC}{sC(R_1R_2 + R_1R_3 + R_2R_3) + R_1 + R_2}$$

(3.4)

where s denotes the complex frequency variable. We discuss whether we can identify  $\phi$  by utilizing DC and/or AC measurements.

#### 1) DC Response Only

The corresponding Jacobian matrix of the DC response (3.3) is

$$J_{DC} = \begin{bmatrix} -V_{DC}/(R_1 + R_2)^2 & -V_{DC}/(R_1 + R_2)^2 & 0 \end{bmatrix}.$$

(3.5)

It is clear that rank  $J_{DC} = 1$ . Therefore  $R_1$  and  $R_2$  are not identifiable from the DC response I. This result is also straightforward intuitively.

#### 2) AC Response Only

J.

The corresponding Jacobian matrix of the AC response (3.4) can be derived as

$$J_{AC} = \begin{bmatrix} -D[s_1C(R_2 + R_3) + 1] & D[R_1(s_1CR_3 + 1)/R_2] & D[(R_1 + R_2)/C] \\ \vdots & \vdots & \vdots \\ -D[s_mC(R_2 + R_3) + 1] & D[R_1(s_mCR_3 + 1)/R_2] & D[(R_1 + R_2)/C] \end{bmatrix}$$

(3.6)

where  $s_i$ ,  $i = 1, \dots, m$ , indicate different frequencies, and

$$D = \frac{V_{AC}R_2R_3sC}{[sC(R_1R_2 + R_1R_3 + R_2R_3) + R_1 + R_2]^2}.$$

Denoting the three columns of  $J_{AC}$  by  $J_1$ ,  $J_2$ , and  $J_3$ , we can obtain

$$\frac{(R_2 + R_3)}{R_1} J_2 + \frac{R_3}{R_2} J_1 - \frac{C}{(R_1 + R_2)} J_3 = 0$$

(3.7)

which means that the rank of  $J_{AC}$  is less than 3, no matter how many frequency points are used. Hence we cannot uniquely determine  $\phi$  from the response  $V_2$ .

#### 3) Combined DC and AC Responses

When we consider both DC and AC responses simultaneously then, combining (3.5) and (3.6), the Jacobian matrix becomes

$$J = \begin{bmatrix} -V_{DC}/(R_1 + R_2)^2 & -V_{DC}/(R_1 + R_2)^2 & 0 \\ -D[s_1C(R_2 + R_3) + 1] & D[R_1(s_1CR_3 + 1)/R_2] & D[(R_1 + R_2)/C] \\ \vdots & \vdots & \vdots \\ -D[s_mC(R_2 + R_3) + 1] & D[R_1(s_mCR_3 + 1)/R_2] & D[(R_1 + R_2)/C] \end{bmatrix}$$

which is of full rank for  $m \geq 2$ . This indicates that  $\phi$  is identifiable from the response

$$h(\phi) = [I(\phi) \quad V_2(\phi, s_1) \quad \cdots \quad V_2(\phi, s_m)]^T.$$

Figure 3.2: A typical nonlinear FET device equivalent circuit model.

#### 3.3 NONLINEAR FET EQUIVALENT CIRCUIT MODEL

A typical nonlinear FET equivalent circuit model may be as shown in Figure 3.2 [70], which is composed of linear and nonlinear elements.  $i_{gs}$ ,  $i_{ds}$  and  $i_{dg}$  are voltage-controlled nonlinear current sources,  $C_{gs}$ ,  $C_{ds}$  and  $C_{dg}$  are nonlinear capacitances,  $R_{in}$  is a nonlinear resistance,  $R_g$ ,  $R_d$ ,  $R_s$  and  $G_{de}$  are linear resistances,  $L_g$ ,  $L_d$  and  $L_s$  are linear inductors. There are various differences between various nonlinear models proposed in the literature. For example,  $C_{ds}$  may be considered as a linear element in some nonlinear models.

The linear and nonlinear elements in a nonlinear FET equivalent circuit are basically derived from the device physical structure. The part of the equivalent circuit which corresponds to the intrinsic part of the device is usually considered nonlinear, and the part which corresponds to the extrinsic part of the device linear. The parameters characterizing the elements of the circuit model are of principal interest, i.e., the goal of FET model parameter extraction.

We will present an approach to directly extract parameters of a nonlinear circuit

model from large-signal measurements in Chapter 5. In this chapter, we focus on an approach to extract those model parameters from simultaneous matching of DC and small-signal measurements. In such a situation, special consideration needs to be taken in the circuit simulation and optimization.

#### 3.3.1 Classification of Model Parameters

In the case of DC and small-signal analysis, the model elements can be individually classified as bias-independent, unconstrained bias-dependent, or constrained biasdependent, due to the nature of DC and small-signal simulations.

We can further separate the elements that appear in both DC and AC (small-signal) models from those appearing only in the AC model. For example, the gate resistance  $R_g$  in a FET equivalent circuit model appears in both DC and AC small-signal models, while the gate-to-source capacitance  $C_{gs}$  only appears in the AC small-signal model. Therefore, we define six subsets of model elements, denoted by  $x_a$ ,  $x_b$ ,  $x_c$ ,  $x_d$ ,  $x_c$  and  $x_f$ , respectively, where  $x_a$  and  $x_b$  are bias-independent,  $x_c$  and  $x_d$  are unconstrained bias-dependent, and  $x_c$  and  $x_f$  are constrained bias-dependent.  $x_a$  and  $x_c$  appear in both the DC and AC models, whereas  $x_b$  and  $x_d$  affect only the AC small-signal equivalent circuit.

We use a superscript k to indicate a different bias point and the corresponding device model. Then,  $\boldsymbol{x}_c^k$ ,  $\boldsymbol{x}_d^k$ ,  $\boldsymbol{x}_c^k$  and  $\boldsymbol{x}_f^k$  belong only to the model under the kth bias, whereas  $\boldsymbol{x}_a$  and  $\boldsymbol{x}_b$  remain unchanged for different bias points.  $\boldsymbol{x}_c^k$  and  $\boldsymbol{x}_d^k$  are linear elements under the kth bias and have no effect at any other bias conditions.

We express the functional dependency of  $x_c$  and  $x_f$  on the bias condition by  $x_c^k = x_c(\alpha, V^k)$  and  $x_f^k = x_f(\alpha, \beta, V^k)$ , where  $\alpha$  and  $\beta$  are the coefficients of the constraints, and  $V^k = V(x_a, x_c^k, \alpha)$  denotes the DC state variables (such as the voltages and currents) at the kth bias point. The coefficient  $\alpha$  affects the DC equivalent circuit but  $\beta$  does not.

Table 3.1 summarizes the foregoing definitions. Note that this kind of classification

Table 3.1:

DEFINITIONS OF THE MODEL PARAMETERS

| Category:                       | Notation                | Brief definition                                    |  |

|---------------------------------|-------------------------|-----------------------------------------------------|--|

| bias-independent                | $x_a$                   | affects DC and AC circuits                          |  |

|                                 | $oldsymbol{x}_b$        | affects AC circuit                                  |  |

| unconstrained<br>bias-dependent | $x_c^k$                 | affects DC and AC circuits a the kth bias condition |  |

| J.                              | $oldsymbol{x}_d^k$      | affects AC circuit at the kth bias condition        |  |

| constrained                     | $x_e(lpha,V^k)$         | $\alpha$ affects DC and AC circuits                 |  |

| bias-dependent                  | $x_f(\alpha,\beta,V^k)$ | $oldsymbol{eta}$ affects AC circuit only            |  |

$V^k = V(x_a, x_c^k, \alpha)$  denotes the DC state variables (such as the voltages and currents) under the kth bias condition.

is suitable for DC and small-signal simulations.

. \

This categorization stems from the consideration of the physical device and a feasible model. It is clear that we need  $x_a$  and  $x_b$  to represent the elements which do not vary or vary only slightly with the bias conditions, such as the package capacitance and lead inductance of a FET. We need  $x_c^k$  and  $x_d^k$  to represent those bias-dependent elements whose functional bias dependency expressions may not be known or available; on the other hand  $x_c^k$  and  $x_d^k$  may be used to test or investigate the functional bias-dependent properties of the model elements.

Introducing  $x_c(\alpha, V^k)$  and  $x_f(\alpha, \beta, V^k)$  allows us to describe other bias-dependent elements whose bias-dependent properties can be expressed by functions or, as we refer to them, constraints. Such constraints may be derived from physical characteristics of the

device. They may be introduced empirically to simulate the pattern of the DC characteristic curves. They may also include mathematical expressions, such as polynomials. These constraints reduce the degrees of freedom in modeling, since the parameters of the elements  $x_e$  and  $x_f$ , namely  $\alpha$  and  $\beta$ , are bias-independent.

In practical parameter extraction, some of the parameters may be available via direct measurement, for example, the method by Fukui [34]. In the general case, we use  $\phi$  to denote the variables to be determined from parameter extraction. It is obvious that

$$\phi \in \{x_a, x_b, x_c, x_d, \alpha, \beta\}.$$

For one particular bias point and for one particular response, only some of the variables in  $\phi$  are active while the rest have no effect on the response. For example, if  $x_{cj}^k \in \phi$ ,  $x_{cj}^k$  has no effect on responses at bias-points other than those at the kth bias point.

#### 3.3.2 A Practical FET Device Example

as

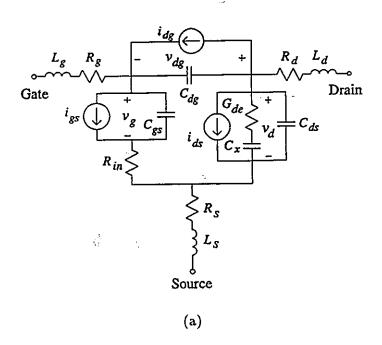

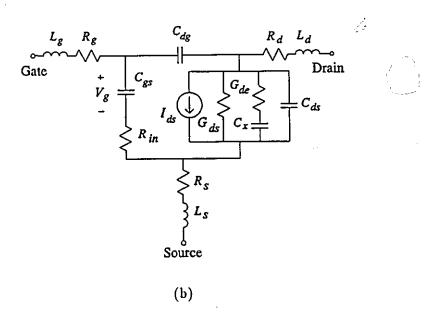

To illustrate the definitions presented in Section 3.3.1, we consider a typical non-linear FET model of the type proposed by Materka and Kacprzak [48] which was later modified and included in *Microwave Harmonica* [49]. Here we do not include packaging effects into the model, but their consideration can be similarly taken into account. The model and its corresponding small-signal equivalent circuit are shown in Figure 3.3 (a) and (b), respectively.

In the Materka and Kacprzak model [49], the intrinsic nonlinear elements are defined

$$i_{ds} = F[v_g(t-\tau), v_d(t)] \left(1 + S_S \frac{v_d}{I_{DSS}}\right)$$

$$F(v_g, v_d) = I_{DSS} \left(1 - \frac{v_g}{V_{P0} + \gamma v_d}\right)^{(E+K_E v_g)} \tanh\left(\frac{S_1 v_d}{I_{DSS}(1 - K_G v_g)}\right)$$

$$i_{gs} = I_{G0}[\exp(\alpha_G v_g) - 1]$$

**÷**.

Figure 3.3: (a) The Materka and Kacprzak nonlinear FET model and (b) the corresponding small-signal equivalent circuit.

$$i_{dg} = I_{B0} \exp[\alpha_B(v_{dg} - V_{BC})]$$

$$\begin{cases} R_{in} = R_{10}(1 - K_R v_g) \\ R_{in} = 0 \end{cases} \text{ if } K_R v_g \ge 1$$

$$\begin{cases} C_{gs} = C_{10}(1 - K_1 v_g)^{-1/2} + C_{1S} \\ C_{gs} = C_{10}\sqrt{5} + C_{1S} & \text{if } K_1 v_g \ge 0.8 \end{cases}$$

and

$$\begin{cases} C_{dg} = C_{F0} (1 + K_F v_{dg})^{-1/2} \\ C_{dg} = C_{F0} \sqrt{5} & \text{if } -K_F v_{dg} \ge 0.8 \end{cases}$$

There are two other bias-dependent elements which appear in the corresponding small-signal equivalent circuit, namely  $I_{ds}$  and  $G_{ds}$ , as illustrated in Figure 3.3 (b)

$$I_{ds} = g_m V_g e^{-j\omega\tau}$$

$$G_{ds} = \frac{\partial i_{ds}}{\partial v_d}\Big|_{v_g = V_{g0} \text{ and } v_d = V_{d0}}$$

where

$$g_m = \left. \frac{\partial i_{ds}}{\partial v_g} \right|_{v_g = V_{g0} \text{ and } v_d = V_{d0}}$$

and  $V_{g0}$  and  $V_{d0}$  are the DC solutions of  $v_g$  and  $v_d$ , respectively, at a bias point.

The linear extrinsic elements are taken as  $R_g$ ,  $R_d$ ,  $R_s$ ,  $G_{dc}$ ,  $L_g$ ,  $L_d$ ,  $L_s$ ,  $C_{ds}$  and  $C_x$ .

The corresponding parameters from the elements in the equivalent circuit read  $I_{DSS}$ ,  $V_{P0}$ ,  $\gamma$ , E,  $K_E$ ,  $S_1$ ,  $K_G$ ,  $\tau$ ,  $S_S$ ,  $I_{G0}$ ,  $\alpha_G$ ,  $I_{B0}$ ,  $\alpha_B$ ,  $V_{BC}$ ,  $R_{10}$ ,  $K_R$ ,  $C_{10}$ ,  $K_1$ ,  $C_{1S}$ ,  $C_{F0}$  and  $K_F$  from nonlinear elements, and  $R_g$ ,  $R_d$ ,  $R_s$ ,  $G_{de}$ ,  $L_g$ ,  $L_d$ ,  $L_s$ ,  $C_{ds}$  and  $C_x$  from linear elements.

Table 3.2 gives a clear classification for all the elements and their corresponding parameters of the Materka and Kacprzak model.

$\sim$

<u>:</u>.

Table 3.2:

PARAMETER CLASSIFICATIONS FOR THE MATERKA AND KACPRZAK FET MODEL

| Category                        | Subset           | Element                                                              | Parameters                                                                                                                                           |

|---------------------------------|------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| bias-<br>independent            | $x_a$            | $R_g \ R_d \ R_s$                                                    | $R_g \ R_d \ R_s$                                                                                                                                    |

|                                 | $x_b$            | $egin{array}{l} L_g \ L_d \ L_s \ C_{ds} \ C_x \ G_{de} \end{array}$ | $egin{array}{c} L_g \ L_d \ L_s \ C_{ds} \ C_x \ G_{de} \end{array}$                                                                                 |

| unconstrained<br>bias-dependent | $oldsymbol{x}_c$ |                                                                      |                                                                                                                                                      |

|                                 |                  | $I_{B0}, lpha_B, V_{BC}$                                             |                                                                                                                                                      |

|                                 | $x_f$            | $C_{dg}$                                                             | $C_{10}, K_1, C_{1S}$<br>$C_{F0}, K_F$<br>$I_{DSS}, V_{P0}, \gamma, E, K_E, S_1, K_G, \tau, S_S$<br>$I_{DSS}, V_{P0}, \gamma, E, K_E, S_1, K_G, S_S$ |

<sup>(1)</sup> The DC state variables are the DC nodal voltages.

<sup>(2)</sup>  $\alpha = [I_{DSS} \ V_{P0} \ \gamma \ E \ K_E \ S_1 \ K_G \ S_S \ I_{G0} \ \alpha_G \ I_{B0} \ \alpha_B \ V_{BC} \ R_{10} \ K_R]^T$ .

<sup>(3)</sup>  $\beta = [\tau \ C_{10} \ K_1 \ C_{1S} \ C_{F0} \ K_F]^T$ .

<sup>(4)</sup> There are no entries in  $x_c$  and  $x_d$ , though we might consider  $R_{in}$  as  $x_c$ , and  $C_{dg}$  and  $C_{ds}$  as  $x_d$ .

## 3.4 MULTI-BIAS DC AND AC MODELING OPTIMIZATION

Assume that the DC and AC measurements are  $S_{\text{DC}}^k$  and  $S_{\text{AC}}^k(\omega_n)$ , respectively, where  $\omega_n$ ,  $n=1,2,\ldots,N$ , is a set of frequency points. Correspondingly, we assume  $F_{\text{DC}}^k(\phi)$  and  $F_{\text{AC}}^k(\phi,\omega_n)$  as the DC and AC model responses, respectively. Notice, as we discussed in the previous section, that a variable from an unconstrained bias-dependent element affects model responses only at the particular bias point where the element is defined.

The error functions corresponding to the DC model responses can be expressed as

$$e_{\text{DC}j}^{k}(\phi) = w_{\text{DC}j}^{k} \left[ F_{\text{DC}j}^{k}(\phi) - S_{\text{DC}j}^{k} \right],$$

(3.8)

$j = 1, 2, \dots, M_{\text{DC}}^{k}; \ k \in K_{\text{DC}}$

where  $w_{DC_j}^k$  is the weighting factor,  $M_{DC}^k$  is the number of DC measurements taken at the kth bias point, and  $K_{DC}$  is the set of bias points at which DC measurements are taken. The error functions corresponding to the AC model responses can be expressed as

$$e_{ACj}^{k}(\phi,\omega_n) = w_{ACj}^{k} \left[ F_{ACj}^{k}(\phi,\omega_n) - S_{ACj}^{k}(\omega_n) \right],$$

$$j = 1, 2, \dots, M_{AC}^{k}; \quad n = 1, 2, \dots, N; \quad k \in K_{AC}$$

$$(3.9)$$

where  $w_{ACj}^k$  is the weighting factor,  $M_{AC}^k$  is the number of AC measurements taken at the kth bias point, and  $K_{AC}$  is the set of bias points at which AC measurements are taken.

If we use K to indicate the set of all bias points, then

$$K = K_{DC} \cup K_{AC} = \{1, 2, \dots, K_{bias}\}.$$

(3.10)

Usually  $M_{DC}$  could be the same for different  $k, k \in K_{DC}$ , such as the number of DC current responses at different bias conditions. Similarly  $M_{AC}^k$  could be the same for different k,  $k \in K_{AC}$ , such as the number of S parameter responses.

The integrated DC and small-signal parameter extraction optimization can be formulated as

$$\min_{\phi} \left( \sum_{k \in K_{DC}} \sum_{j=1}^{M_{DC}^{k}} \left| e_{DCj}^{k}(\phi) \right|^{p} + \sum_{k \in K_{AC}} \sum_{j=1}^{M_{AC}^{k}} \sum_{n=1}^{N} \left| e_{ACj}^{k}(\phi, \omega_{n}) \right|^{p} \right)$$

(3.11)

where the optimization variable is  $\phi$ , and p=1 or 2 corresponds to  $\ell_1$  or  $\ell_2$  optimization, respectively. The selection of  $\ell_1$  or  $\ell_2$  optimization depends on different application situations.