# PERFORMANCE OPTIMIZATION OF HIERARCHICAL MEMORY SYSTEMS

#### by

NAGI NASSIEF MEKHIEL, M.A.Sc.

#### A Thesis

Submitted to the School of Graduate Studies in Partial Fulfillment of the Requirements

for the Degree

Doctor of Philosophy

McMaster University

(c) Copyright by Nagi Nassief Mekhiel, September 1995

# PERFORMANCE OPTIMIZATION OF HIERARCHICAL MEMORY SYSTEMS

# DOCTOR OF PHILOSOPHY (1995) McMASTER UNIVERSITY

(Electrical and Computer Engineering) Hamilton, Ontario

TITLE:

Performance Optimization of Hierarchical

Memory Systems

**AUTHOR:**

Nagi Nassief Mekhiel

SUPERVISOR:

Dr. Daniel McCrackin, Department of

Electrical and Computer Engineering

NUMBER OF PAGES: xviii,153

#### ABSTRACT

The gap between processor speeds and memory speeds is increasing. The performance of supercomputers and the scalability of multiprocessor systems is very dependent on the memory system speed.

A cache system helps to narrow the processor/memory speed gap, but cannot completely decouple the processor from slow memory.

The optimization of main memory performance and the use of a deep multilevel cache hierarchy are proposed here to bridge the processor/memory latency gap.

A novel design that combines optimized bank interleaving with several main memory (DRAM) timing modes to increase memory performance is presented. Four different protocols based on this design are proposed and investigated.

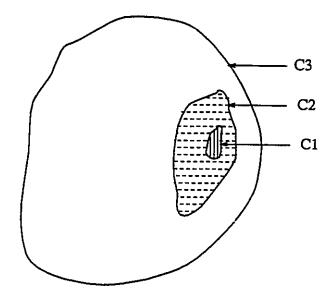

Enforcing the inclusion property for multi-level caches is proposed. A new design that uses three level caches is preserred and three different models are given.

A design flow graph that makes the design of a multi-level memory system simpler and more flexible is introduced. Selected traces that match real workloads running on a wide range of computers are used to calculate realistic overall system performance.

## ACKNOWLEDGMENTS

I would like to thank my supervisor, Dr. Daniel McCrackin, who has helped to make this work possible. I appreciate his encouragement, candid advice, ideas, and outstanding guidance.

I also like to thank my committee members, Dr. David Capson and Dr. Skip Poehlman for their support and help.

I would like to thank Dr. S. Boctor, the chairman of the Electrical Engineering at Ryerson, for his continuous encouragement and support. I also thank professor Ken Clowes at Ryerson for his help.

I would like to thank my beloved wife Hala and my children Caroline and Christopher for their patience and support.

Finally, I would like to dedicate this thesis to my late father who had wished me to get the Ph.D.

# Contents

| 1 | Intr | ntroduction                                     |  |       |  |     | 1  |

|---|------|-------------------------------------------------|--|-------|--|-----|----|

|   | 1.1  | 1 Introduction                                  |  |       |  |     | 1  |

|   | 1.2  | 2 Hierarchical Memory Architecture              |  |       |  |     | 3  |

|   | 1.3  | 3 The Novelty of this research                  |  | <br>• |  |     | 4  |

|   | 1.4  | 4 The Scope of this Work                        |  | <br>• |  |     | 5  |

|   | 1.5  | 5 Related Work                                  |  |       |  |     | 6  |

|   | 1.6  | 6 Trends in Memory Design                       |  |       |  |     | 8  |

| 2 | The  | he Choice of Traces for Simulation              |  |       |  |     | 9  |

|   | 2.1  | 1 Introduction                                  |  |       |  |     | 9  |

|   | 2.2  | 2 The Traces                                    |  |       |  |     | 11 |

|   |      | 2.2.1 The SPEC benchmarks                       |  |       |  |     | 11 |

|   |      | 2.2.2 The ATUM traces                           |  |       |  | •   | 12 |

|   |      | 2.2.3 Hennessy and Patterson Benchmark traces . |  |       |  | • , | 13 |

|   | 2.3 | Trace  | Qualification                                                    | 14 |

|---|-----|--------|------------------------------------------------------------------|----|

|   |     | 2.3.1  | Introduction                                                     | 14 |

|   |     | 2.3.2  | The Method                                                       | 15 |

|   | 2.4 | The S  | Selected Traces                                                  | 16 |

|   |     | 2.4.1  | Selecting traces based on miss rates with different cache sizes. | 16 |

|   |     | 2.4.2  | Selecting traces based on miss rates with different cache block  |    |

|   |     |        | sizes                                                            | 16 |

|   |     | 2.4.3  | Selecting traces based on miss rates with different cache set    |    |

|   |     |        | associativity                                                    | 19 |

|   |     | 2.4.4  | List of the selected traces                                      | 19 |

|   | 2.5 | Sumn   | nary                                                             | 20 |

| 3 | Opt | imizin | g Main Memory Performance                                        | 21 |

|   | 3.1 | Introd | duction                                                          | 21 |

|   | 3.2 | DRAN   | M Interleaving with different bank mapping                       | 24 |

|   |     | 3.2.1  | Introduction                                                     | 24 |

|   |     | 3.2.2  | Low order Address Interleaving                                   | 25 |

|   |     | 3.2.3  | High order Address Interleaving                                  | 25 |

|   |     | 3.2.4  | Variable Address Interleaving                                    | 25 |

|   | 3.3 | Improv | ving Main Memory Performance by using different Access modes     | 26 |

|   |     | 3.3.1  | Random access mode                                               | 29 |

|     | 3.3.2  | Fast page access mode                                        | 29 |

|-----|--------|--------------------------------------------------------------|----|

|     | 3.3.3  | Precharge access mode                                        | 30 |

| 3.4 | Four 1 | New Protocols for DRAM interleaving                          | 31 |

|     | 3.4.1  | Introduction                                                 | 31 |

|     | 3.4.2  | Notation: Design flow graphs                                 | 31 |

|     | 3.4.3  | The precharge protocol                                       | 32 |

|     | 3.4.4  | The fast page protocol                                       | 32 |

|     | 3.4.5  | The fast page protocol with limited number of active banks   | 35 |

|     | 3.4.6  | The fast page precharge protocol                             | 35 |

| 3.5 | The S  | ystem Architecture                                           | 38 |

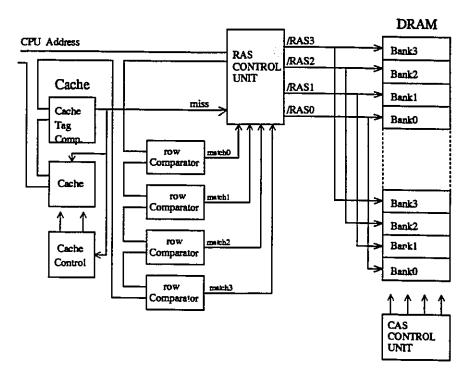

|     | 3.5.1  | The RAS control unit                                         | 39 |

|     | 3.5.2  | The row address comparator                                   | 39 |

|     | 3.5.3  | The CAS control unit                                         | 40 |

| 3.6 | Simul  | ation Model                                                  | 40 |

| 3.7 | The re | esults of Main memory using the four New Protocols           | 41 |

|     | 3.7.1  | Varying the bank select position                             | 42 |

|     | 3.7.2  | Varying the DRAM size                                        | 43 |

|     | 3.7.3  | Low Order Address Interleaving versus number of banks        | 46 |

|     | 3.7.4  | Performance of High Order Address Interleaving versus number |    |

|     |        | of banks                                                     | 48 |

|   |     | 3.7.5    | Page interleaving versus number of banks                | 49 |

|---|-----|----------|---------------------------------------------------------|----|

|   | 3.8 | Summ     | nary                                                    | 50 |

| 4 | Sin | gle Lev  | vel Cache Basics and Design                             | 52 |

|   | 4.1 | Reviev   | w of Cache Design Basics                                | 52 |

|   |     | 4.1.1    | Introduction                                            | 52 |

|   |     | 4.1.2    | Cache Terminology and Organization                      | 53 |

|   |     | 4.1.3    | Cache Parameters and Miss rate                          | 57 |

|   |     | 4.1.4    | Write Strategies                                        | 59 |

|   |     | 4.1.5    | Policies on a Write Miss                                | 62 |

| • | 4.2 | Single   | Level Cache Design                                      | 63 |

|   |     | 4.2.1    | Results and limitations of the WT-NWA and WB-NWA models | 63 |

|   |     | 4.2.2    | summary                                                 | 69 |

| 5 | Opt | timizing | g Multi-level Cache Performance                         | 70 |

|   | 5.1 | Introdu  | action                                                  | 70 |

|   | 5.2 | Multi-l  | Level Cache Design Goals                                | 71 |

|   | 5.3 | Enforci  | ing the Inclusion Property                              | 72 |

|   | 5.4 | Evalua   | ting the Cost of Inclusion                              | 73 |

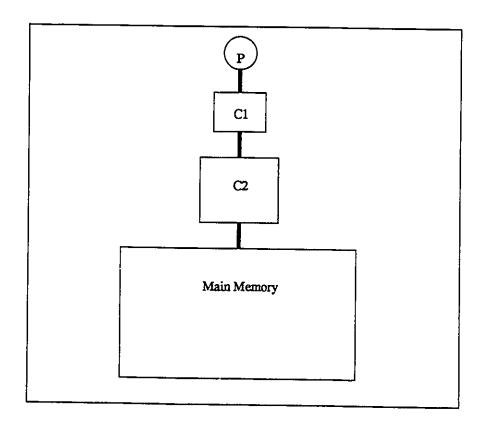

|   | 5.5 | Two Le   | evel Cache Design and Organization Using Inclusion      | 74 |

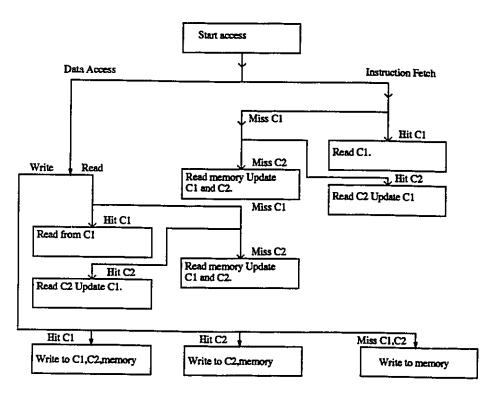

|   |     | 5.5.1    | The write-through/write-through (WTWT) model            | 76 |

|     | 5.5.2               | The write-through/write-back (WTWB) model                         | 76   |

|-----|---------------------|-------------------------------------------------------------------|------|

|     | 5.5.3               | The write-back/write-through (WBWT) model                         | 76   |

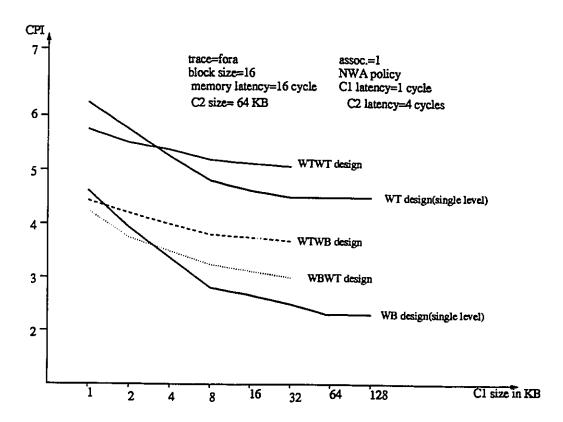

|     | 5.5.4               | Results of the two level cache models                             | 79   |

|     | 5.5.5               | The effect of first level cache size                              | 80   |

|     | 5.5.6               | The effect of second level cache size                             | 84   |

|     | 5.5.7               | The effect of second level cache latency                          | 84   |

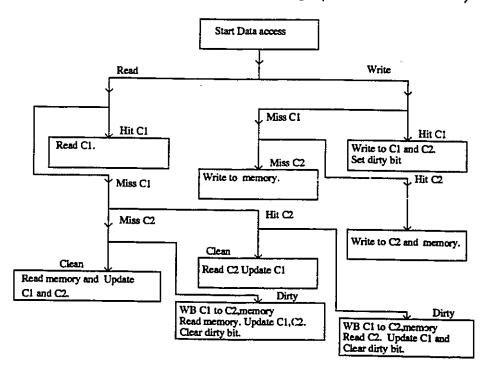

| 5.6 | Three               | Level Cache                                                       | 87   |

|     | 5.6.1               | The write-through/write-through "WTTT" mode                       | l 87 |

|     | 5.6.2               | The write-through/write-back "WTTB" model                         | 88   |

|     | 5.6.3               | The write-back/write-through/write-through "WBTT" model           | 88   |

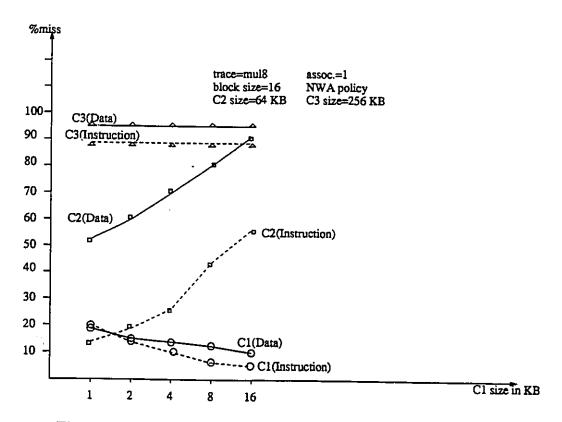

|     | 5.6.4               | Results for three level cache systems                             | 92   |

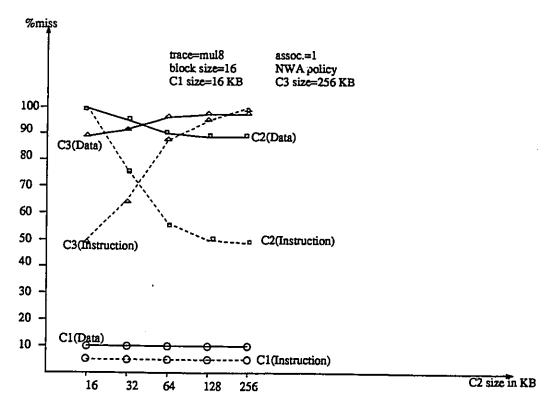

|     | 5.6.5               | The effect of first level cache size on miss rate of each cache . | 92   |

|     | 5.6.6               | The effect of second level cache size on miss rate of each cache  | 93   |

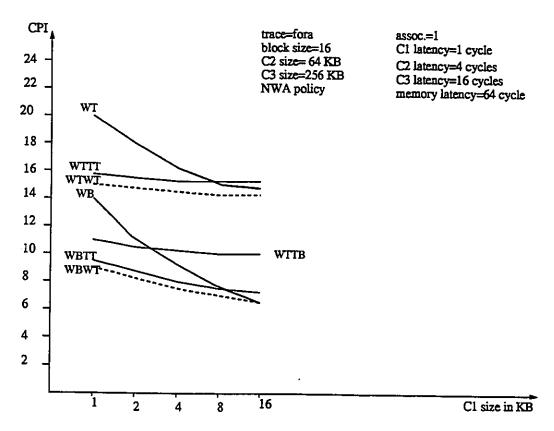

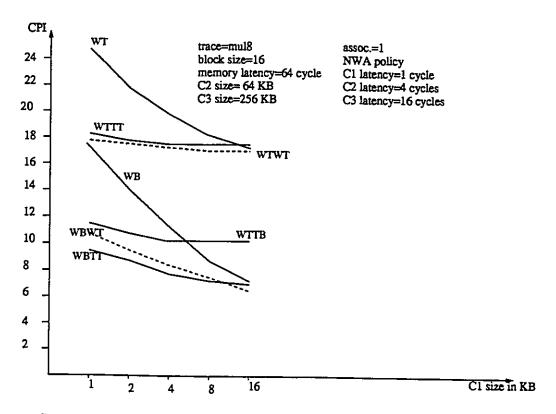

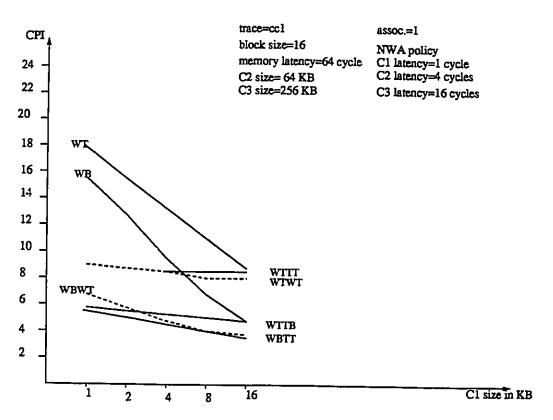

|     | 5.6.7               | The effect of first level cache size on performance               | 96   |

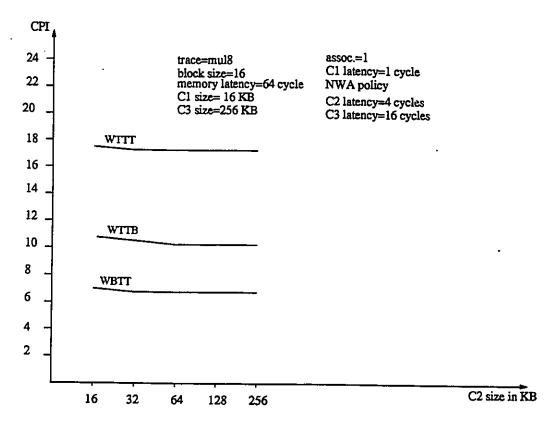

|     | 5.6.8               | The effect of second level cache size on performance              | 100  |

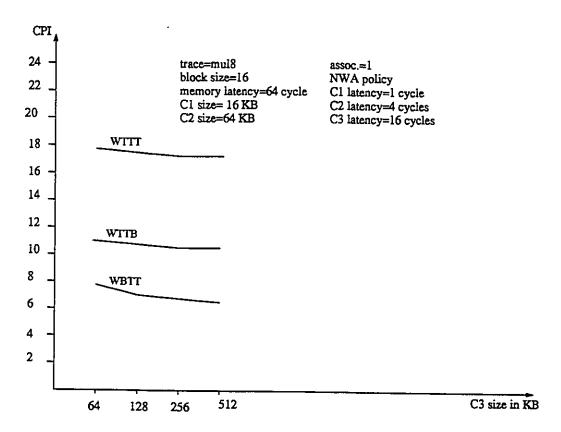

|     | 5.6.9               | The effect of third level cache size on performance               | 100  |

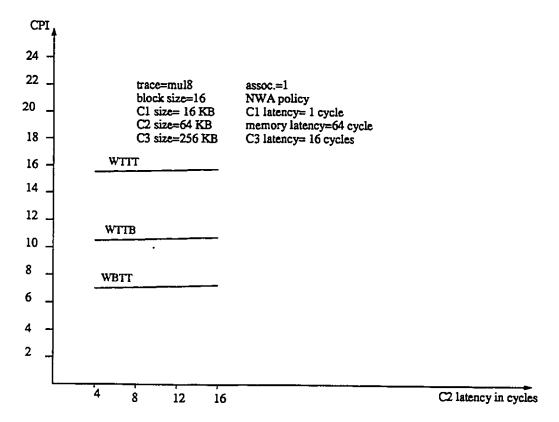

|     | 5.6.10              | The effect of second level cache latency on performance           | 103  |

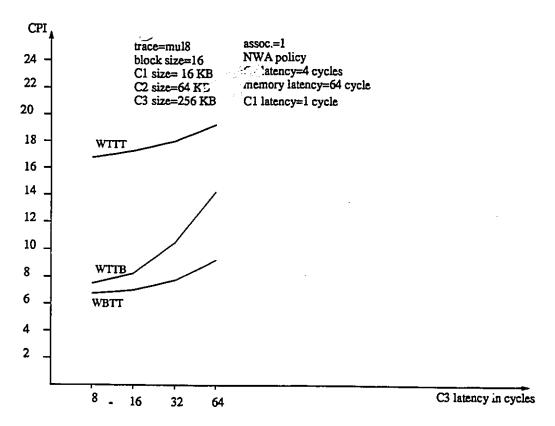

|     | 5.6.11              | The effect of third level cache latency on performance            | 105  |

| 5.7 | Summ                | ary                                                               | 107  |

| Opt | imizin <sub>é</sub> | g Overall Memory Performance                                      | 108  |

|     |                     |                                                                   |      |

1.

| 6.1 | Introd  | luction                                                        | 108 |

|-----|---------|----------------------------------------------------------------|-----|

| 6.2 | The C   | Complete Memory System Architecture                            | 109 |

| 6.3 | Optin   | nizing the Performance of the Complete Memory System (with a   |     |

|     | Single  | Cache Level)                                                   | 111 |

|     | 6.3.1   | Introduction                                                   | 111 |

| ÷   | 6.3.2   | The results of the complete memory system (with single level   |     |

|     |         | cache)                                                         | 111 |

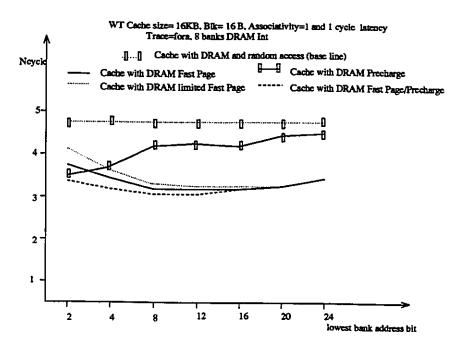

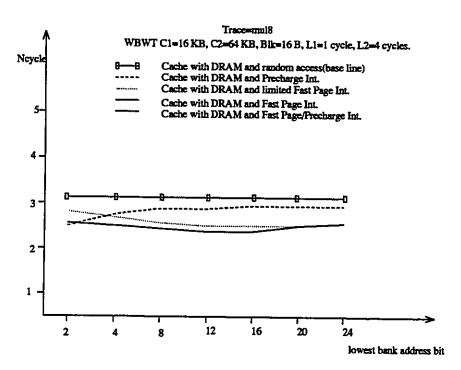

|     | 6.3.3   | The effect of variable address interleaving on the performance |     |

|     |         | of a complete memory system (with single level cache)          | 112 |

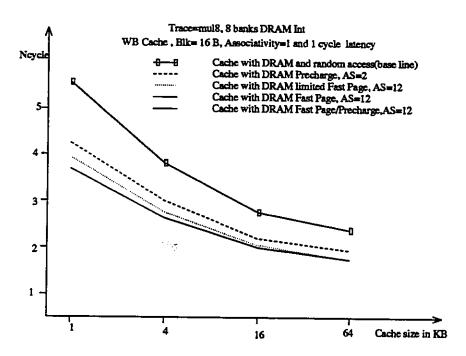

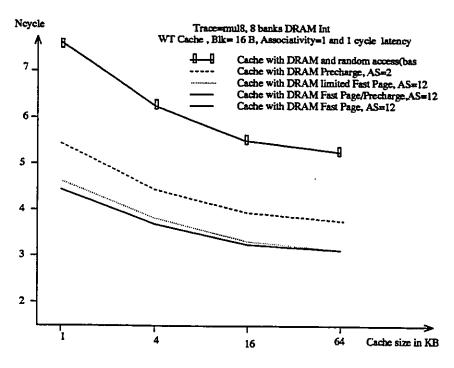

|     | 6.3.4   | The effect of cache size on the performance of a complete mem- |     |

|     |         | ory system (with single level cache)                           | 114 |

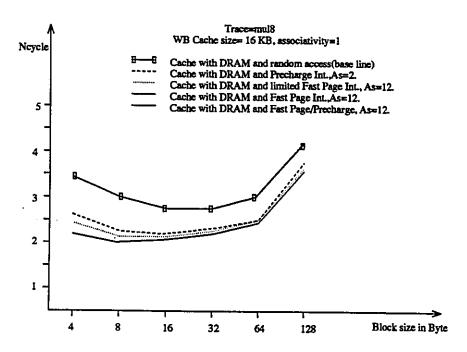

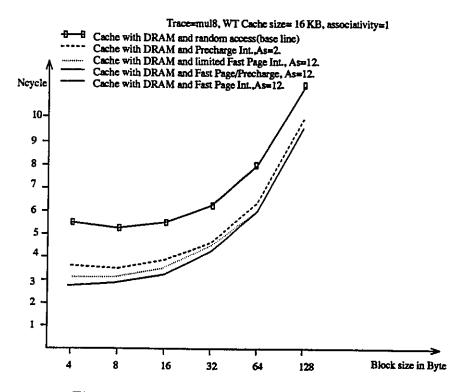

|     | 6.3.5   | The effect of block size on the performance of a complete mem- |     |

|     |         | ory system (with single level cache)                           | 117 |

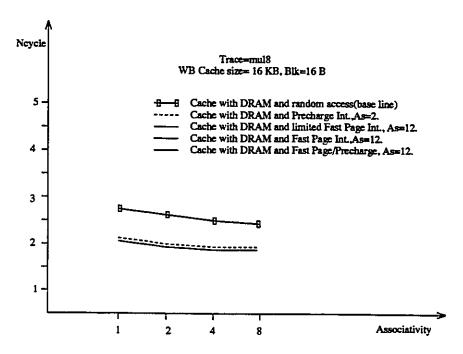

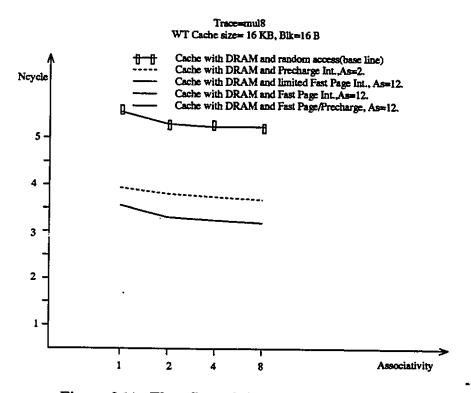

|     | 6.3.6   | The effect of associativity on the performance of a complete   |     |

|     |         | memory system (with single level cache)                        | 120 |

| 6.4 | Optim   | izing the Performance of a Complete Memory System (with        |     |

|     | multi-l | evel cache)                                                    | 122 |

|     | 6.4.1   | Introduction                                                   | 122 |

|     | 6.4.2   | Performance of a complete memory system with two level cache   | 199 |

|   |     | 6.4.3 Variable address interleaving and the performance of a complete | •            |

|---|-----|-----------------------------------------------------------------------|--------------|

|   |     | memory system (with two level cache)                                  | 123          |

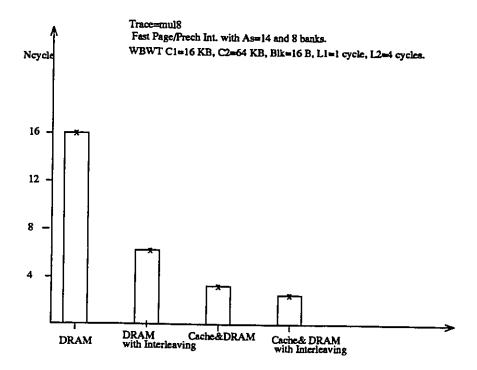

|   | 6.5 | The Effect of Using Different Memory Designs on Overall System Per-   |              |

|   |     | formance                                                              | 126          |

|   | 6.6 | Summary                                                               | 128          |

| 7 | Sun | mary and Conclusions                                                  | .29          |

|   | 7.1 | Summary                                                               | 129          |

|   | 7.2 | Conclusions                                                           | L34          |

|   | 7.3 | Recommendations For Further Work                                      | L <b>3</b> 5 |

|   | Арр | endix A: Simulator Program                                            | .36          |

|   | RE  | ERENCES 1                                                             | 50           |

# List of Figures

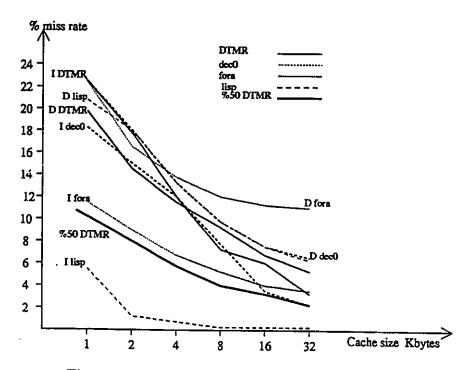

| 2.1  | Miss ratios versus cache size for dec0, fora and lisp traces  | 1' |

|------|---------------------------------------------------------------|----|

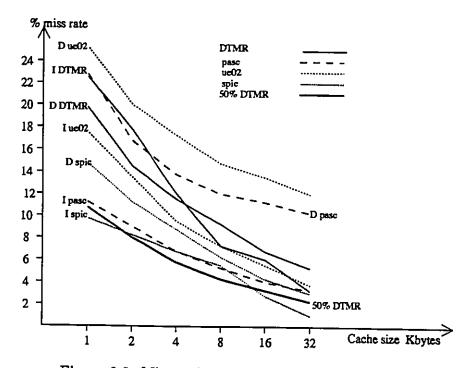

| 2.2  | Miss ratios versus cache size for pasc, ue02 and spice traces | 1  |

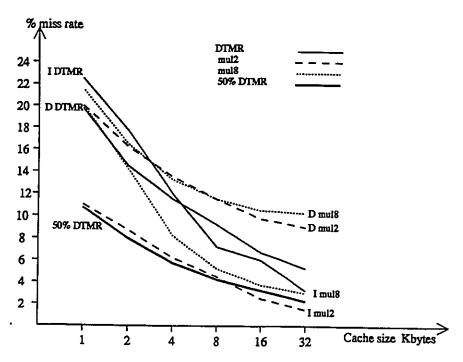

| 2.3  | Miss ratios versus cache size for mul2 and mul8 traces        | 18 |

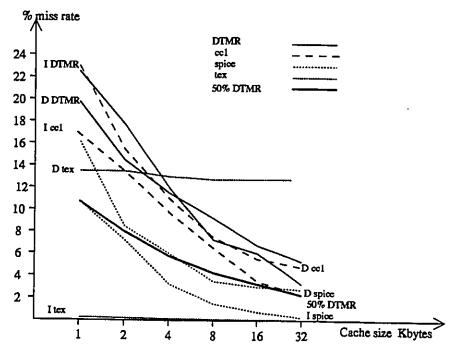

| 2.4  | Miss ratios versus cache size for ccl, spice and tex traces   | 18 |

| 3.1  | Variable Address Interleaving                                 | 27 |

| 3.2  | Row and Column address in Variable Address Interleaving       | 28 |

| 3.3  | Random Access mode                                            | 29 |

| 3.4  | Fast Page Access mode                                         | 30 |

| 3.5  | Precharge Access mode                                         | 30 |

| 3.6  | Precharge Protocol                                            | 33 |

| 3.7  | Fast Page Protocol                                            | 34 |

| 3.8  | Limited Fast Page Protocol                                    | 36 |

| 3.9  | Fast Page precharge Protocol                                  | 37 |

| 3.10 | Memory System Architecture                                    | 38 |

| 3.11 | The Simulation Model                                                        | 41 |

|------|-----------------------------------------------------------------------------|----|

| 3.12 | Variable address interleaving for dec0 trace (4M DRAM)                      | 43 |

| 3.13 | Variable address interleaving for cc1 trace (4M DRAM)                       | 44 |

| 3.14 | Variable address interleaving for fora trace (4M DRAM)                      | 44 |

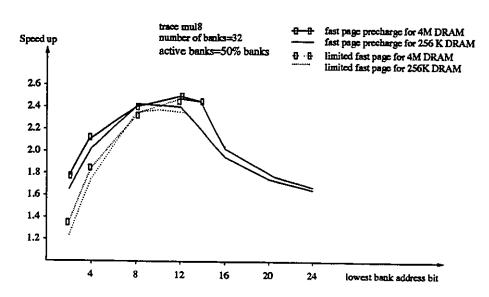

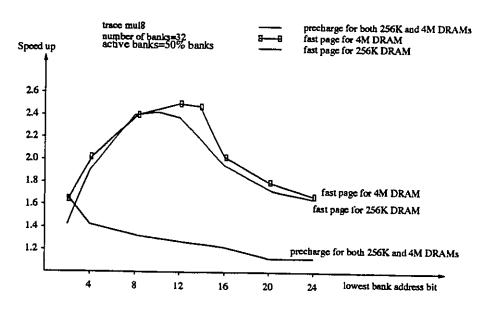

| 3.15 | Variable address interleaving for mul8 trace (4M DRAM)                      | 45 |

| 3.16 | Speed up changes versus variable interleaving for 4M DRAM with dif-         |    |

|      | ferent traces                                                               | 45 |

| 3.17 | Variable address interleaving for limited fast page and fast page precharge |    |

|      | (256K and 4M DRAMs)                                                         | 47 |

| 3.18 | Variable address interleaving for precharge and fast page (256K and         |    |

|      | 4M DRAMs)                                                                   | 47 |

| 3.19 | Low order address interleaving                                              | 49 |

| 3.20 | High order address interleaving                                             | 50 |

| 3.21 | Page interleaving                                                           | 51 |

| 4.1  | Cache organization                                                          | 56 |

| 4.2  | Cache size and associativity versus miss rate                               | 58 |

| 4.3  | Cache block size versus miss rate                                           | 60 |

| 4.4  | Cache block size versus average access time                                 | 61 |

| 4.5  | Write Through Cache with NWA                                                | 63 |

| 4.6  | Write Back Cache with NWA                                                   | 64 |

| 4.7          | Cache size                                                         | 66 |

|--------------|--------------------------------------------------------------------|----|

| 4.8          | Cache block size                                                   | 67 |

| 4.9          | Cache associativity                                                | 68 |

| 5.1          | Multi-Level Cache with Inclusion Property                          | 73 |

| 5.2          | Two level cache architecture                                       | 75 |

| 5.3          | WTWT Design                                                        | 77 |

| 5.4          | WTWB Design (Data Access Section)                                  | 78 |

| 5.5          | WBWT Design (Data Access Section)                                  | 78 |

| 5.6          | CPI versus first level cache size for fora trace                   | 81 |

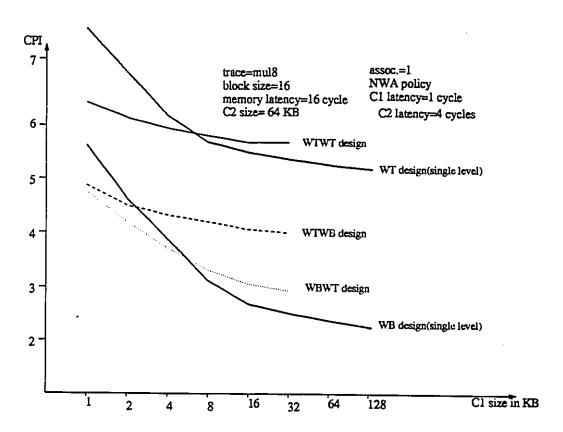

| 5.7          | CPI versus first level cache size for mul8 trace                   | 82 |

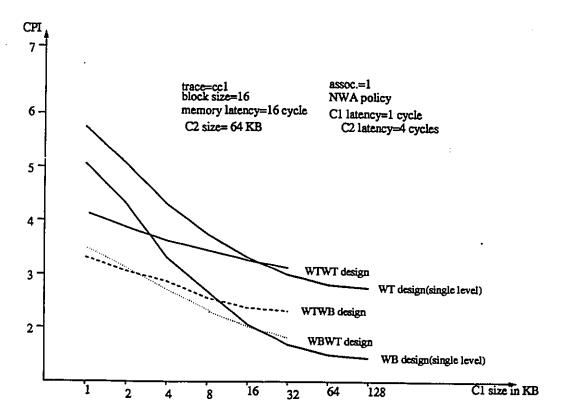

| 5.8          | CPI versus first level cache size for cc1 trace                    | 83 |

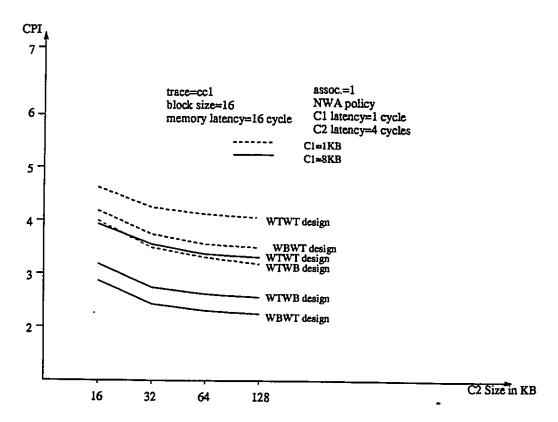

| 5.9          | CPI versus second level cache size                                 | 85 |

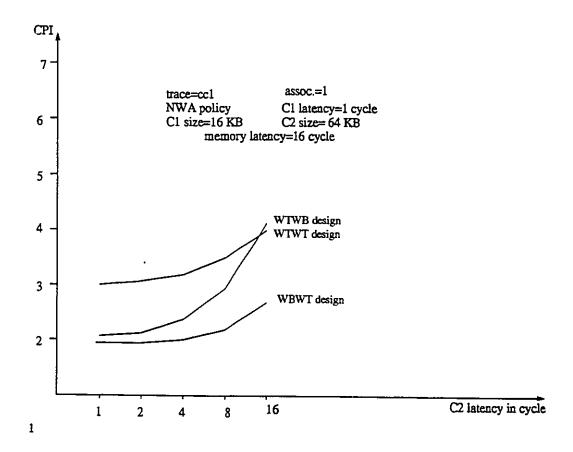

| 5.10         | CPI versus second level cache latency                              | 86 |

| <b>5.</b> 11 | WTTT Design                                                        | 89 |

| 5.12         | WTTB Design (Data Section)                                         | 90 |

| 5.13         | WBTT Design (Data Section)                                         | 91 |

| 5.14         | The effect of first level cache size on miss rate of each cache    | 94 |

| 5.15         | The effect of second level cache size on miss rate of each cache   | 95 |

| 5.16         | The effect of first level cache size on performance for fora trace | 97 |

| 5.17         | The effect of first level cache size on performance for mul8 trace | 02 |

| 5.18         | The effect of first level cache size on performance for cc1 trace | 99  |

|--------------|-------------------------------------------------------------------|-----|

| 5.19         | The effect of second level cache size on performance              | 10  |

| 5.20         | The effect of third level cache size on performance               | 102 |

| <b>5.2</b> 1 | The effect of second level cache latency on performance           | 104 |

| 5.22         | The effect of third level cache latency on performance            | 106 |

| 6.1          | The System Architecture                                           | 110 |

| 6.2          | Variable address interleaving for WB and DRAM using mul8 trace .  | 114 |

| 6.3          | Variable address interleaving for WB and DRAM using fora trace    | 115 |

| 6.4          | Variable address interleaving for WT and DRAM using mul8 trace    | 115 |

| 6.5          | Variable address interleaving for WT and DRAM using fora trace    | 116 |

| 6.6          | The effect of the WB cache size on performance                    | 117 |

| 6.7          | The effect of the WT cache size on performance                    | 118 |

| 6.8          | The effect of the WB cache block size on performance              | 119 |

| 6.9          | The effect of the WT cache block size on performance              | 119 |

| 6.10         | The effect of the WB cache associativity on performance           | 120 |

| 6.11         | The effect of the WT cache associativity on performance           | 121 |

| 6.12         | The WBWT Variable Address Interleaving for mul8 trace             | 125 |

| 6.13         | The WBWT Variable Address Interleaving for fora trace             | 125 |

| 6.14         | The effect of different memory designs on performance             | 127 |

# List of Tables

| 2.1 | ATUM traces for uniprogramming and multiprogramming | 13 |

|-----|-----------------------------------------------------|----|

| 2.2 | Benchmarks traces                                   | 14 |

#### LIST OF SYMBOLS

ATUM Address Traces Using Microcode

CAS Column Address Strobe signal

CPI Clock Per Instruction

CS Chip Select signal

CPU Central Processing Unit

DEC Digital Equipment Corporation

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

DTMR Design Target Miss Ratios

MHz Mega Hertz

MRU Most Recently Used

NWA No Write Allocate

RAS Row Address Strobe signal

RISC Reduced Instruction Set Computer

SRAM Static Random Access Memory

TAA column Address Access Time

T<sub>CP</sub> CAS Precharge Time

$T_{RCD}$  RAS to CAS Delay

TCAC Column Access Time from CAS

TRP RAS Precharge Time

W Word size in bytes

WA Write Allocate

WB Write Back

WBTT Write Back write Through write Through

WBWT Write Back Write Through

WE Write Enable signal

WT Write Through

WTTB Write Through write Through write Back

WTTT Write Through write Through write Through

WTWB Write Through Write Back

WTWT Write Through Write Through

# Chapter 1

# Introduction

#### 1.1 Introduction

It is very important for supercomputer designers to make memory systems fast, as the performance of a computer is greatly influenced by its memory speed, further more, multiprocessor systems the scalability of the system depends on the design of the memory.

The introduction of many new fast processors every year makes the design of a memory system that enables full processor speed more challenging. Furthermore, programs have generally grown in their memory requirements by 1.5 to 2 address bits per year, and the typical main memory needed for any computer normally doubles every three years [13].

An ideal memory system should have the same speed as the processor and have the same size as the processor address space. Building fast memory systems could be done using fast Static Random Access Memory (SRAM), but this is only suitable for small memory systems because of the high cost and low density of SRAM chips. For larger memory systems, the system needs extensive address decoding and data buffering which slow the speed of the memory system.

Fortunately there is a solution to the speed/size conflict of the memory system. This solution comes from the principle of locality. All programs favor small parts of their address space at any instant of time. Programs possess two types of locality: Temporal locality (if an item is referenced now, it is more likely to be referenced again soon) and Spatial locality (the neighbor of a currently referenced item is likely to be referenced soon) [19].

Small parts of the program are used frequently. If they are stored in a fast small memory that could be built with SRAM, the overall system speed will not suffer from having the rest of the program stored in a larger, slower memory. This partitioning of the program into small fast memory and slow larger memory is the principle behind hierarchical memory architecture.

In this thesis we examine optimization of hierarchical memory systems. This Chapter gives an overview of the hierarchical memory architecture, presents the scope of this work, and examines related work and trends in memory design.

## 1.2 Hierarchical Memory Architecture

A hierarchical memory system is built with multiple levels of memory.

A memory hierarchy generally consists of the following:-

The Cache: The cache is the closest memory level to the processor and is also the

fastest and the smallest. Cache operation is based on the program's temporal

and spatial locality. Memory references that are made close together in time or

space to recent references can be retrieved from a fast cache.

The hit rate is defined as the ratio of references found in the cache to the total references requested [19]. It is important to maximize the cache hit rate.

Usually the latency (or access time) of the first cache level matches the speed of the processor.

- The Main Memory: The main memory is the second level in the memory hierarchy. It affects the processor performance in that its latency determines the cost of the cache misses. Thus the latency of the main memory is an important parameter affecting the performance of the computer memory system.

- The Virtual Memory: It is generally considered impractical to build a memory system that includes all the address space of a 32 or 64 bit processor. Virtual memory divides the existing physical memory into some form of pages, and lets the operating system transfer data between a secondary store (usually imple-

mented using magnetic disk) and main memory whenever it is needed. In effect, the main memory acts as a cache for the much larger disk store.

In this thesis we concentrate on the upper memory levels including the cache and main memory; virtual memory is largely a software subject and beyond the scope of this study.

## 1.3 The Novelty of this research

We introduce a design flow graph that is used to visually illustrate the design of each memory system. It shows the decisions taken by the system in each operation. This is a new notational tool that helps in making complicated systems simpler to follow and gives us more flexibility to consider different design options. Recently a similar method has been used to illustrate the algorithm of a system [4].

The traces that we use for simulations are tested and qualified against the results of real workloads running on wide range of computers. Traces affect the result of simulation and can cause them to vary by up to 300% [44]. Furthermore the performance of our design is measured in number of clock cycles per instruction, which gives more realistic results than other studies using miss rates to evaluate the performance of systems.

We present four novel interleaving protocols for the main memory design.

The protocols combine multi-bank interleaving with DRAM access modes. An optimal bank mapping for each protocol is found by varying the bank mapping (a new method). Conventional main memory designs use either interleaving or special DRAM access modes to increase system performance, not both. Conventional multi-bank interleaving uses simple low-order (fixed) bank mapping that does not give the system optimal performance.

We use multi-level cache design to increase the cache performance and enforce the inclusion property for simpler multiprocessor cache coherency protocols. Our multi-level cache design is kept simple by limiting the number of write back caches to a single level. A novel three level cache design is introduced and analyzed. Other recent multi-level cache designs use only up to two levels.

In this research, the performance of the overall memory system is optimized which is a fundamentally different approach from other research work that has optimized one level of the memory hierarchy at a time.

#### 1.4 The Scope of this Work

In Chapter 2 we examine different traces for simulation and qualify them against results on a wide class of workloads running on a wide range of computers and workstations.

Chapter 3 presents a new optimized main memory design that uses multiple

bank interleaving and several main memory (DRAM) timing modes.

In Chapter 4 we give a review of cache design basics and single level cache design. Chapter 5 discusses the design of a multi-level cache system and evaluates the performance of both a two level cache and a new three level cache design.

Chapter 6 deals with the performance optimization of the complete memory system using the optimized main memory design of Chapter 3 and the single and multi-level cache designs of Chapter 4 and Chapter 5.

Chapter 7 presents conclusions and gives recommendations for future work.

#### 1.5 Related Work

Previous research work on dealing with memory latency has relied largely on the use of a cache system. There have been numerous articles about cache design. All studies show that as cache size or block size or associativity increase, the rate of performance increase shows diminishing returns [3], [45] and [19].

Newer cache designs tend to use two levels of cache, but as the second level cache size is increased, performance comes to be dominated by the smaller first level cache and increasing the second level cache size yields little additional improvement [31] and [43].

With the current trend of processor speed increasing much more quickly than main memory speed, and with little performance improvement gained from new

#### CHAPTER 1. INTRODUCTION

research, we could very well find future processors running at more clock cycles per instruction than present day machines [8].

In this study we use a multi-level cache design with the inclusion property (blocks in higher cache levels are included in lower cache levels) to optimize cache performance. This improves the first level cache miss rate. Enforcing the inclusion property between different cache levels makes the cache coherence protocols for multiprocessor systems simpler [7] and [19].

In this thesis we focus on obtaining optimal system performance by reducing the processor dependency on the main memory. The goal is to close the processor/memory speed gap.

Our study considers performance optimization at all memory hierarchy levels. We also attack one much-neglected level: the performance of the DRAM main memory itself.

The optimization techniques used in this investigation are applied across the whole memory system because optimizing the performance of a single memory level does not guarantee optimal system performance.

In all of our designs, we use a design flow graph technique which is a new and useful method for obtaining and estimating the interactions between each memory level and different program operations. This method gives a simple view of the entire memory system. It also allows the caching algorithm to be specified and the cache

performance to be estimated at the same time.

# 1.6 Trends in Memory Design

Most current research in memory design concentrates on providing methods to improve cache performance. Some recent research uses multi-level, prefetch, victim caches and code restructuring methods to improve cache performance.

It seems fair to say that the intensity of the research in memory system design is growing as the speed gap between processors and memory increases.

Research in cache design will only find use if it produces a significant performance improvement. Our focus for the rest of this thesis is thus upon system performance rather than on simply minimizing the miss rate of the cache system.

The industry focuses in producing faster main memory using new architectures like the cached DRAM and multi-bank DRAM. We share the same opinion with industry and believe that this emphasis on main memory design and memory integration should continue.

# Chapter 2

# The Choice of Traces for

# Simulation

## 2.1 Introduction

The computer systems of today are more complex and rapidly changing than those of even a few years ago. The need for tools and techniques to help in understanding the behavior of these systems is growing. One of the most important techniques is modelling.

There are two main types of computer system modelling. The first is analytical modelling which is inexpensive and fast but may involve simplifications that can make the results unreliable. The second method is to simulate the system by using a

program which behaves like the system. If properly done, a simulation gives accurate results, and the system parameters can be easily varied to test different designs.

A simulator needs an input which represents an actual workload. The output of a simulated system depends greatly on the input and a realistic workload should be given to drive the simulator [1][23].

In trace-driven simulation, traces of real program addresses are used as an input to the memory system simulator. Traces are sequences of addresses that the program accesses during its execution. Trace driven simulation is the most popular and reliable method for evaluating the performance of a memory system.

As the results of the simulation depend on the input traces, the selection of the input traces is very important. Input traces should represent real workloads running on real computers. In this Chapter, we discuss the different types of traces that exist and select suitable traces by comparing the results of different traces on our simulator to typical levels of performance for a wide class of workloads and computers from the study done by A.J. Smith in [44].

In Section 2, we explain the characteristics of the available traces. Section 3 discusses a trace qualification method. In Section 4, we apply the trace qualification method to test and select traces.

#### 2.2 The Traces

#### 2.2.1 The SPEC benchmarks

The System Performance Evaluation Cooperative (SPEC) benchmark suite is a set of programs and data designed to provide realistic system performance results [16]. The metric of performance on each program is the ratio of program run time on the target system to the run time of the same program on a DEC VAX 11/780. The geometric mean of the set ratios gives the SPEC figure of merit which is most commonly quoted in advertisements, although all figures for all programs are really needed for a complete picture.

Interestingly, it has been reported that the SPEC benchmarks results are sensitive to cache size and generally yield miss rates lower than they should be [44]. In particular, the integer SPEC benchmarks put very little stress on the memory system.

The SPEC benchmarks have become so popular that computer designers are tuning their design to optimize SPEC benchmark performance regardless of the results of their applications [16].

A study by M.D. Hill [16] concludes that SPEC benchmarks are lacking a significant operating system component, which affects the results of cache simulations in two ways: miss ratios are very low, and the performance of the operating system

functions are not tested.

For our study the traces that we use should put greater stress on the memory system and give more realistic miss ratios.

#### 2.2.2 The ATUM traces

Address Traces Using Microcode (ATUM) is one of the most realistic sets of traces [1]. Traces of all addresses (including system addresses) that the processor visits are recorded and stored using the microcode of the machine. The ATUM traces include both the addresses and information about the type of each reference (read, write or instruction fetch).

The ATUM traces have the following advantages with respect to other traces like those from the SPEC benchmarks:

- ATUM traces include operating system code.

- No omission of multitasking; the traces are real traces from a live machine.

- No granularity distortion or implementation distortion.

The only problem the ATUM traces have are that they do not include input/output activities and they have limited trace length.

In conclusion, the ATUM traces provide realistic address traces that include operating system and multitasking effects and are more suitable for memory sim-

ulations than the SPEC traces. We use the ATUM traces available from Stanford University to drive our simulations [18]. The following is the list of available ATUM traces from Stanford University for workloads running on VAXes. We use uniprogram-

| Trace name | Total Refs | Inst.   | Data    |

|------------|------------|---------|---------|

| dec0       | 361,982    | 183,023 | 178,959 |

| fora       | 65,291     | 40,527  | 24,764  |

| lisp       | 291,390    | 169,786 | 121,604 |

| pasc       | 422,090    | 193,025 | 229,065 |

| ue02       | 357,810    | 199,973 | 157,837 |

| spice      | 446,701    | 223,706 | 222,995 |

| mul2       | 372,104    | 208,434 | 163,670 |

| mul8       | 429,432    | 199,455 | 229,977 |

Table 2.1: ATUM traces for uniprogramming and multiprogramming

ming (processes are executed in serial fashion) and multiprogramming (processes are executed in a time-multiplexed fashion) ATUM traces.

### 2.2.3 Hennessy and Patterson Benchmark traces

We also used the traces that are available from the text book "Computer Architecture: A Quantitative Approach" by J. Hennessy and D.A. Patterson. The benchmarks traces for spice, ccl and Tex are longer than the other traces and are obtained from Stanford University [18]. The traces are of 1,000,000 references long and are Dineroformatted [23] and [16]. The greater length makes them arguably good candidates for memory system testing.

| Trace name | Total Refs. | Inst.   | Data    |

|------------|-------------|---------|---------|

| spice'     | 1000,0001   | 782,764 | 217,237 |

| ccl        | 1000,002    | 757,341 | 242,661 |

| Tex        | 832,477     | 597,309 | 235,168 |

Table 2.2: Benchmarks traces

The following is the list of the obtained benchmarks and some of their characteristics:

### 2.3 Trace Qualification

#### 2.3.1 Introduction

The characteristics of the used traces affect the results of the simulated model. We want to select traces that represent normal workload conditions.

Smith in [44] studied the effect of workloads on cache miss rates and defined DTMR (Design Target Miss Ratios) for normal loading.

In this section, we will introduce our trace qualification method that uses the values of Smith's DTMR to set a cut off point for the miss rates produced by the tested traces.

#### 2.3.2 The Method

DTMRs are typical levels of cache performance for a wide range of computers [44]. They represent realistic miss ratios on cache systems in typical workstations running realistic workloads. Smith [44] has used hardware monitors, personal experience and trace driven simulation to obtain these miss ratios. The DTMRs for different cache sizes, set associativity and block sizes are presented in [22] and [24].

The miss ratios of trace driven simulations are often optimistic and we need to test our memory system under realistic conditions. DTMRs will be used as guidelines to qualify the traces used in our simulations.

As a lower limit on acceptable miss rates, 50% of the DTMR for the instruction and data caches is chosen. Thus the selected traces must give miss ratios higher than 50% of the DTMR to be used in our memory system simulation. This is reasonable considering the results of instruction and data caches miss ratios may vary widely. For example, the DTMR is 3 times larger than the SPEC miss ratios for instruction caches as measured by [16]. Note that we have set no upper bound for miss ratios on selected traces. This encourages the selection of traces with higher miss ratios which test the memory system under realistic, non-optimal conditions.

Next we will compare cache miss ratios using the different traces with the DTMRs for the same cache parameters, and will select the traces that satisfy the above criterion.

## 2.4 The Selected Traces

# 2.4.1 Selecting traces based on miss rates with different cache sizes

This trace evaluating simulation is done assuming a block size of 16 Bytes and a set associativity of two using the ATUM uniprogramming and multiprogramming traces and the Hennessy and Patterson benchmark traces.

The miss ratios for different cache sizes are compared with the DTMR expected values and traces giving miss rates of more than 50% DTMR are selected.

The results for this simulation are shown in figure 2.1 to 2.4.

Lisp, Spice, mul2 and Tex fail the 50% DTMR test.

# 2.4.2 Selecting traces based on miss rates with different cache block sizes

Simulation is now done assuming a cache size of 32 Kbytcs and a set associativity of two for the ATUM traces. The miss ratios for different cache block sizes is compared with the DTMR expected values and traces giving miss rates of less than 50% DTMR are rejected.

Results show that fora, dec0, ue02, mul8 and cc1 still qualify.

Figure 2.1: Miss ratios versus cache size for dec0, fora and lisp traces

Figure 2.2: Miss ratios versus cache size for pasc, ue02 and spice traces

Figure 2.3: Miss ratios versus cache size for mul2 and mul8 traces

Figure 2.4: Miss ratios versus cache size for cc1, spice and tex traces

# 2.4.3 Selecting traces based on miss rates with different cache set associativity

Simulation is now done assuming a cache size of 32 Kbytes and a block size of 16 Bytes for the ATUM traces. The miss ratios for different cache set associativity is compared with the DTMR expected values and traces giving miss rates of less than 50% DTMR are rejected.

Results show that fora, dec0, ue02, mul8 and cc1 still qualify.

#### 2.4.4 List of the selected traces

The following are the selected traces which we will use in our simulation in this work.

- Uniprogramming ATUM traces are:

- fora- 65,291 total number of references, 40,527 instructions and 24,764 data

references.

- dec0- 361,982 total number of references, 183,023 instructions and 178,959

data references.

- ue02- 357,810 total number of references, 199,973 instructions and 157,837

data references.

- multiprogramming ATUM traces are:

- mul8- 429,432 total number of references, 199,455 instructions and 229,977 data references.

- Hennessy and Patterson Benchmarks are:

- cc1- 1000,002 total number of references, 757,341 instructions and 242,661

data references.

All the above selected traces give similar or worse results than DTMR expected values for different cache parameters for both instruction and data caches.

#### 2.5 Summary

We compare the performance of a cache model using the ATUM and Hennessy and Patterson Benchmarks traces, available from Stanford University, to the results of the DTMR [44] (using same cache parameters) and selected the traces that give similar or higher miss rates. We chose 50% of the DTMR as a lower limit for the miss rates of selected traces for any chosen cache parameters.

The traces are qualified against the DTMR for different cache sizes, block sizes and set associativity. The traces dec0, fora, Mul8 and cc1 will be used in this work as they represent uniprogramming, multiprogramming and the Hennessy and Patterson benchmarks, and also pass our DTMR test.

### Chapter 3

## Optimizing Main Memory

### Performance

#### 3.1 Introduction

The main memory is typically the second level in the memory hierarchy. The main memory supplies caches, vector units and I/O units with required data. The main memory is generally the most important level in the hierarchy, from the point of view that it is the largest level whose speed is at all comparable to that of the CPU (within 2 orders of magnitude). Even the fastest disk devices are incredibly slow in comparison to the CPU (> 5 orders of magnitude slower).

The main memory is usually built using DRAM (Dynamic Random Access

Memory) which has large capacity and low cost. From an economic point of view it is almost necessary to use DRAM chips in building a typical multiple-mega byte main memory.

It is well known that the need for using larger memory is growing rapidly because of larger software applications, leading to a continuing growth of processor address space. The DRAM industry has partly kept up with this need with DRAM capacity growing by a factor of 4 every 3 years [13].

The only problem with the DRAM is speed. The DRAM is organized as an array of capacitive memory cells, and does not match the speed of the logic circuits that are used in building SRAMs. Also, to reduce the cost of DRAM chips, the pin count is reduced by using a multiplexed address for the columns and rows of the array. The chip has to latch the first half of the address then latch the second half, making access slower.

Thus DRAM speeds are not keeping pace with increasing CPU speeds. There is no main memory available that can allow the newer processors (like the DEC Alpha [47]) to run at full speed.

The processor/main memory speed gap could be narrowed by using a cache.

Any cache system has cache misses, in which the processor has to retrieve the data

from the main memory at slower speed. Even for the best cache design, cache misses

still exist and the performance of the system is limited by the speed of DRAM accesses.

This is a classic application of Amdahl's law [19].

The attention that is being given to improving the main memory speed is very little compared to that given to cache design. Improving the main memory performance is essential for the best overall system performance, and can have a dramatic effect, as we will demonstrate.

The following are the known conventional methods used in improving main memory performance:

Wider memory- In wider word fetch, multiple words of data can be accessed simultaneously, reducing the cache line fill latency.

The performance increase obtained by using a wider memory organization is limited by the cache line size, the memory access time and the delay of the multiplexer used between the cache and the processor.

Interleaving- Interleaved memory uses several memory banks that are arranged so that they can be accessed in a parallel or an overlapped fashion [19], [38] and [28]. The processor can send addresses to multiple banks so that data can be retrieved in parallel.

In this research we consider the interleaved memory organization, since it has many advantages over the wider memory organization and can be easily expanded.

We will first look at how addresses are mapped into different banks and

introduce variable address interleaving, a novel interleaving method. In Section 3, we review DRAM access modes like fast page/static column and the precharge mode. A novel method that combines both bank interleaving and these different DRAM access modes will be discussed. We then present four new memory protocols based on the use of the different address modes and bank interleaving. The rest of the Chapter focuses on evaluating the performance of the main memory using the four proposed protocols as a function of the bank mapping, DRAM size and the number of used banks. The characteristics and features of each protocol are examined using the traces of Chapter 2.

# 3.2 DRAM Interleaving with different bank mapping

#### 3.2.1 Introduction

Memory interleaving is often used in high performance computers like the Cray vector processors [11].

The mapping of addresses to memory banks can affect the performance of the memory system. Consecutive accesses should be to different banks to achieve optimal performance (maximum bandwidth utilization) in simple word interleaving. If one bank has two successive requests, the second request must wait for the first one to complete and the system must generate a wait state [28].

The following are two conventional bank mapping methods:

#### 3.2.2 Low order Address Interleaving

In low order address interleaving, the low order address lines are used to select the different banks. Accesses to consecutive addresses will go to different banks. This is the same as the word interleaving. If the number of banks =  $N_b$ , then  $log_2N_b$  of the lower address lines are used to select one of the banks.

#### 3.2.3 High order Address Interleaving

In high order address interleaving, the high order address lines are used to select the different banks. Each bank contains consecutive memory locations of total memory size divided by the total number of banks.

We now introduce a novel bank mapping method:

#### 3.2.4 Variable Address Interleaving

The performance of the interleaved memory system depends on the bank mapping.

Low order address interleaving has an advantage for only consecutive accesses. A smart memory design should optimize the performance of both consecutive and non-consecutive accesses.

In this research, we introduce variable address interleaving in which the location of address bits for bank selection is made variable to cover all the memory address space. Variable address interleaving allows us to optimize the performance of the interleaved memory over all the address space.

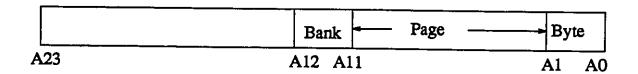

Figure 3.1 shows the variable address interleaving and the mapping of each memory address in different banks. In this example four banks are used and bank select is set at A12-A11. Each bank consists of multiple pages each of which has 0.5K words of consecutive memory locations.

Figure 3.2 shows the correct row address and column address for variable address interleaving assuming that the number of banks equals four. The bank select address takes any value from A3A2 to A23A22. For each location the row address (r) and column address (c) is shown as a function of the overall address space.

# 3.3 Improving Main Memory Performance by using different Access modes

There are three common DRAM access methods: random, fast page and RAS precharge.

There are several timing parameters of interest, notably:

- t<sub>RP</sub> the RAS "row address strobe" precharge time.

- $v_{RCD}$  the RAS to CAS "column address strobe" delay.

Address space and bank select bits.

Mapping of memory locations in different banks.

Figure 3.1: Variable Address Interleaving

|                 | memory address                                                                  |

|-----------------|---------------------------------------------------------------------------------|

| mapping address | A23 A21 A19 A17 A15 A13 A11 A9 A7 A5 A3 A22 A20 A18 A16 A14 A12 A10 A8 A6 A4 A2 |

| A3 A2           | r r r r r r r r c c c c c c c c b b                                             |

| A5 A4           | r r r r r r r r r c c c c c c d b b c c                                         |

| A7 A6           |                                                                                 |

| A9 A8           |                                                                                 |

| A11 A10         | L L L L L L L L C d p p c c c c c c c                                           |

| A13 A12         | rrrrrrrbbccccccc                                                                |

| A15 A14         | L L L L L L L P P L L C C C C C C C C                                           |

| A17 A16         | L L L L L P P L L L C C C C C C C C C                                           |

| A19 A18         | rrr p p L rrrrcccccccc                                                          |

| A21A20          | r l b b r r r r r r r c c c c c c c c c                                         |

| A23 A22         | p p L L L L L L L L L C C C C C C C C C                                         |

Figure 3.2: Row and Column address in Variable Address Interleaving

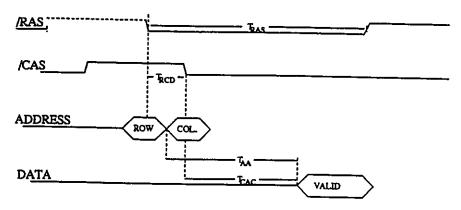

Figure 3.3: Random Access mode

- t<sub>CP</sub> the CAS precharge time.

- $t_{AA}$  the access time from column address.

- $t_{CAC}$  the access time from CAS.

The different access modes are:

#### 3.3.1 Random access mode

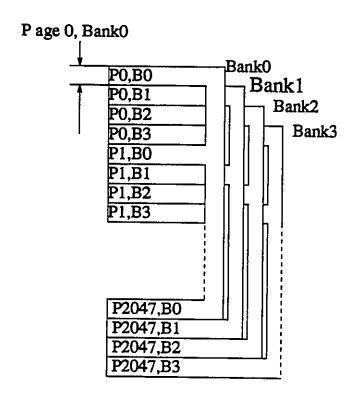

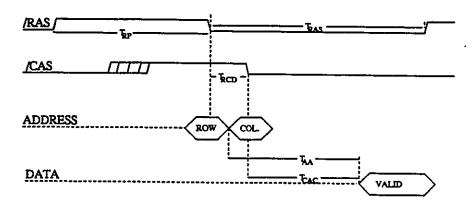

Figure 3.3 shows the random access mode timing. All of the timing requirements  $(t_{RP}, t_{RCD}, t_{CP}, t_{AA} \text{ and } t_{CAC})$  must be satisfied for this access mode. [15].

#### 3.3.2 Fast page access mode

Figure 3.4 shows the fast page mode access timing. In this mode, the bank RAS is kept active low to latch the previous row address and if the arriving access has the

Figure 3.4: Fast Page Access mode

Figure 3.5: Precharge Access mode

same row address then there is no need to re-latch the row; the system need only latch the column address. Thus only  $t_{AA}$  and  $t_{CAC}$  constrain the access time [15]..

#### 3.3.3 Precharge access mode

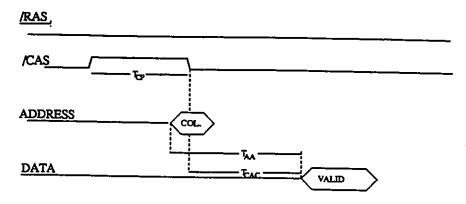

Figure 3.5 shows the precharge access mode. In this mode the RAS of the accessed bank is fully precharged and ready to latch the row address of the coming access. The row address must be latched via RAS, satisfying  $t_{RCD}$ , then the column address must be latched, satisfying  $t_{AA}$  and  $t_{CAC}$  [15].

#### 3.4 Four New Protocols for DRAM interleaving

#### 3.4.1 Introduction

In bank interleaving, successive accesses could be overlapped in time. While one bank is finishing the access, the other bank could start a new access.

Combining the different access modes and bank interleaving gives the memory system the advantages of having fast access modes and overlapping of the accesses.

Combinations of both techniques produce new and interesting memory systems. We present four different designs, as described by the following protocols:-

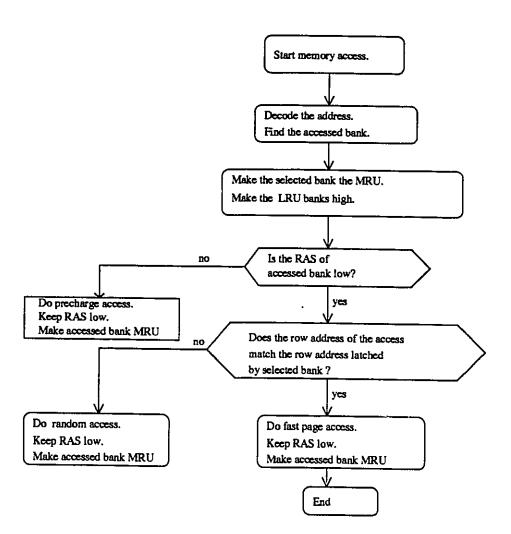

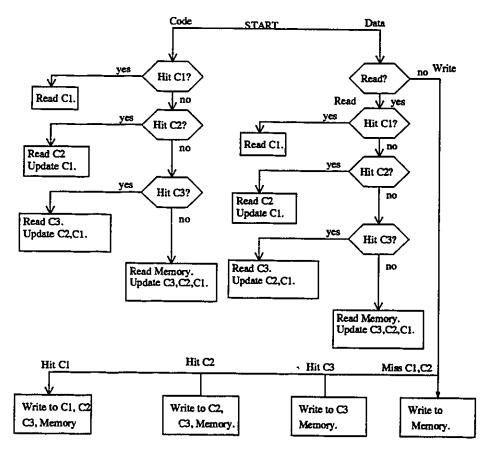

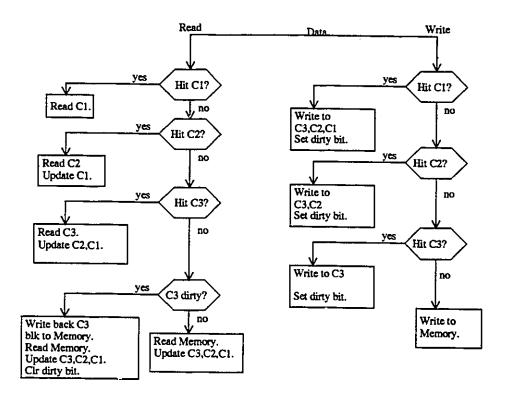

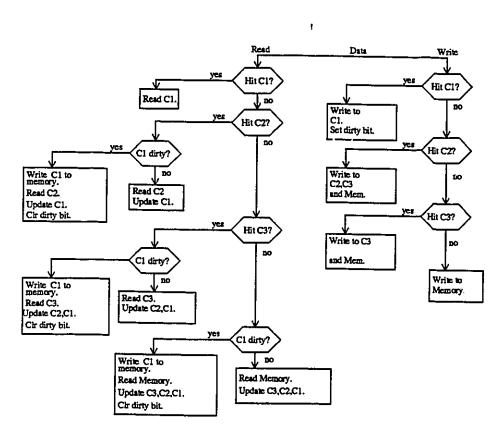

#### 3.4.2 Notation: Design flow graphs

We introduce a design flow graph to visually illustrate the design of each memory system. It shows all decisions taken by the system in each operation. Each node of the graph corresponds to a decision element (like encountering a bank miss or a bank hit).

By assigning probabilities to each arc of the graph and assigning a cost to each operation, a simple and accurate analytical model of the system can be obtained as shown in our publication [33].

This is a new, powerful tool that that helps in making complicated systems simpler to follow. It also gives us more flexibility to consider different design options.

We will use this graph to illustrate the design of each memory system. Interestingly, recently a similar method has been used to illustrate the algorithm of a system [4].

The design flow graph is used to define the DRAM systems described in the following sections:

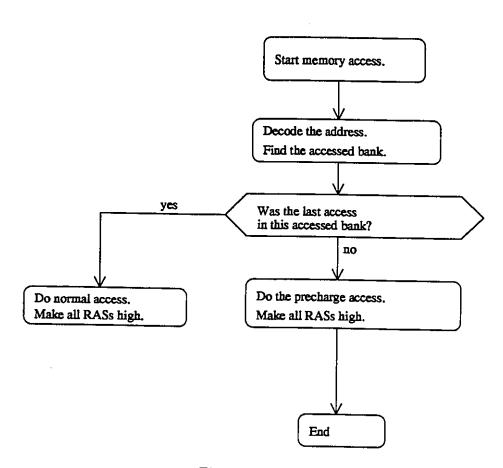

#### 3.4.3 The precharge protocol

Figure 3.6 shows the flow chart of the conventional precharge protocol. In this protocol the RAS signals of different banks are kept precharged high while an access to another bank is taking place. If the next access is to one of the precharged banks, the system will do the precharge access sequence described above. If the next access is to the same bank, the system has to perform the random access sequence.

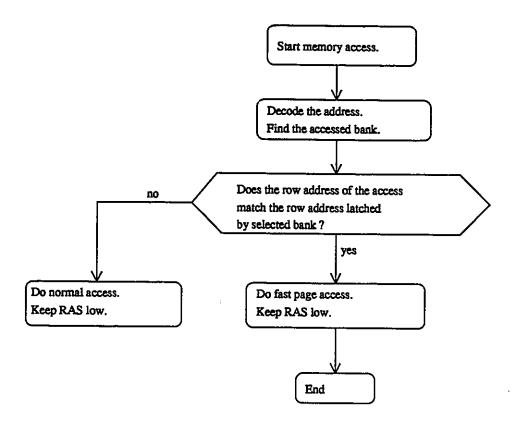

#### 3.4.4 The fast page protocol

In this conventional protocol the system uses a comparator and latch for each bank.

This requires a large and impractical amount of hardware for systems with large numbers of banks.

Figure 3.7 shows the flow chart of the fast page protocol. In this protocol, the RAS signals of all banks are kept active low, latching different row addresses. When an access occurs, the RAS control unit selects the accessed bank, and if the RAS of the selected bank is latching a row address that is the same as the row address of

Figure 3.6: Precharge Protocol

ý.

#### Fast page protocol

Figure 3.7: Fast Page Protocol

the access, the system performs a fast page mode access. If the selected bank has a row address that is different from the row address of the incoming access, the system performs a random mode access. The bank will then use RAS to hold the new row address.

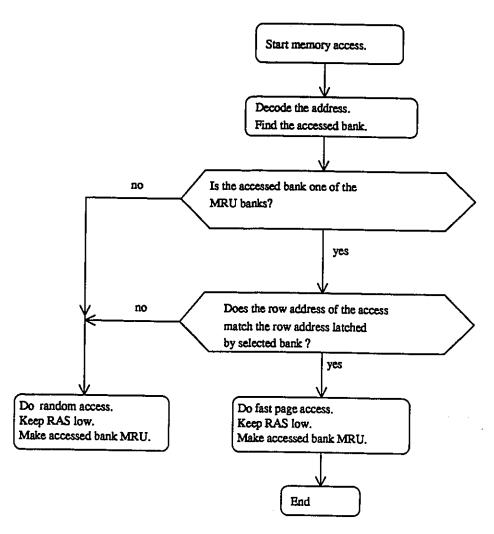

# 3.4.5 The fast page protocol with limited number of active banks

Figure 3.8 shows the flow chart of our novel limited fast page protocol. Some fraction of the the most recently used (MRU) RAS signals is kept active low (50%, in this case), to reduce the number of row comparators and row latches. An access to MRU bank that has same row address is a fast page access, while an access to a MRU bank with different row address is a random access and an access to a LRU (least recently used) bank is always a random access.

#### 3.4.6 The fast page precharge protocol

Figure 3.9 shows the flow chart of our novel fast page precharge protocol. In this protocol, 50% (the MRU) of the RAS signals are kept active like the limited fast page protocol and the other 50% of the RAS signals are kept precharged. This protocol uses half the comparators and latches of the fast page protocol. However, new accesses to a LRU bank take only precharge access time, an access to a MRU bank that has the same row address takes a fast page access time, and an access to a MRU bank with a different row address takes a random access time.

It is thus possible for this protocol to have greater performance than both the limited fast page and the fast page protocols, as not all bank misses result in random (long) accesses.

Figure 3.8: Limited Fast Page Protocol

Figure 3.9: Fast Page precharge Protocol

Figure 3.10: Memory System Architecture

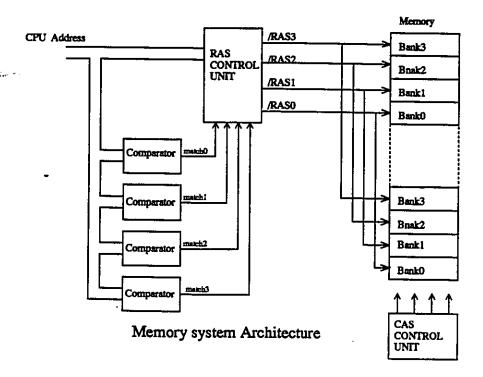

#### 3.5 The System Architecture

The system that we now simulate consists of a main memory using multiple bank interleaving. Figure 3.10 shows an example of a system that uses 4 banks. The system consists of the memory (divided into 4 separate banks,) the RAS control unit that generates the 4 RAS lines for the different banks, four row address comparator units and a CAS control unit.

#### 3.5.1 The RAS control unit

The RAS control unit is used to decode the address bits and map addresses into the banks of the memory. We assume that this unit supports the above three different access modes. For normal accesses, the unit allows the RAS to precharge and to go active low to latch the new row address. For precharge accesses, the unit allows the RAS to stay high while the system is using other banks so that the precharge time is satisfied. The RAS unit tracks the value of each RAS so that it can decide to do a precharge access if it finds that the accessed RAS is precharged.

For the fast page mode the RAS is kept active low, latching the last row address in the DRAM. The unit examines the value of the 4 match signals, coming from the comparator units, to do the fast page access.

#### 3.5.2 The row address comparator

The row address comparator is used to detect if an access has the same row as the one that is being latched in a specific memory bank. The comparator has a latch that keeps the last row address that the memory bank uses. For each access, the incoming row address is compared with the latched one and the comparator signals a match if they are equal.

#### 3.5.3 The CAS control unit

The CAS control unit generates the required CAS for the memory. It allows for CAS precharge and the other CAS timing requirements based on the type of access being performed.

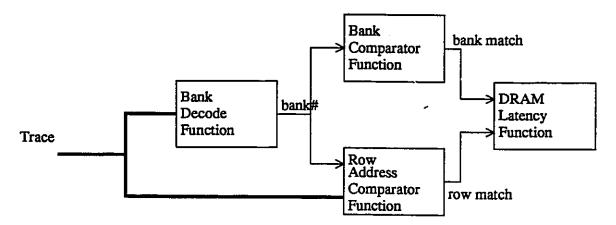

#### 3.6 Simulation Model

Figure 3.11 shows the block diagram of the simulation model.

The simulator reads the trace input file to find the current address. The bank decode function gives the current bank number from the address. The address comparators compare the latched row number of the accessed bank with the current access row number and signal a match if they are the same.

The bank comparators distinguish between a RAS precharge or random access by examining the accessed bank's RAS value. If the RAS line is still active, then the row comparators determine if the current access is on the same page (fast page access) or not (random access).

Figure 3.11: The Simulation Model

# 3.7 The results of Main memory using the four New Protocols

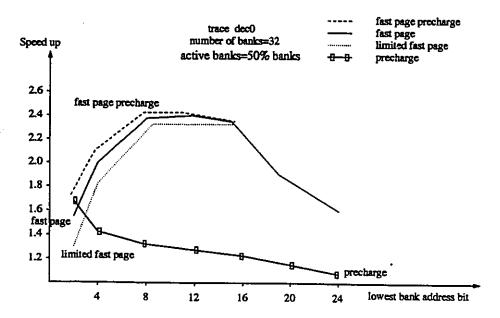

The following traces were used to simulate the DRAM performance: dec0, the cc1 benchmark, for a and mul8. The processor is assumed to run at 100 MHz; this makes the clock cycle time equal to 10 ns.

The DRAM chips are chosen to be 4 M bits with 80 ns access times and support fast page mode access [15]. The total time for a random access to the DRAM is 155 ns. We assume that this takes a total of 16 cycles for random access considering that the cycle is 10 ns [15]. For fast page mode, the access takes 6 cycles and for the precharge access it takes 9 cycles according to the DRAM access timing. We use N banks with variable bank select address and variable DRAM size.

Performance improvement is measured by dividing the time taken when the

system uses the random access mode by the time when the system uses the protocols under test.

#### 3.7.1 Varying the bank select position

3

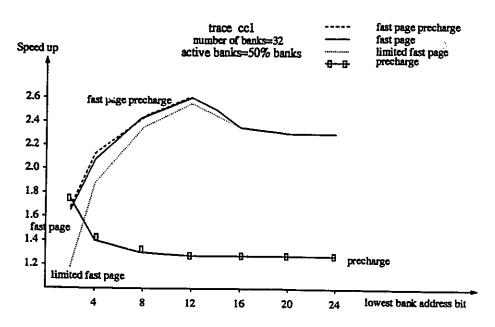

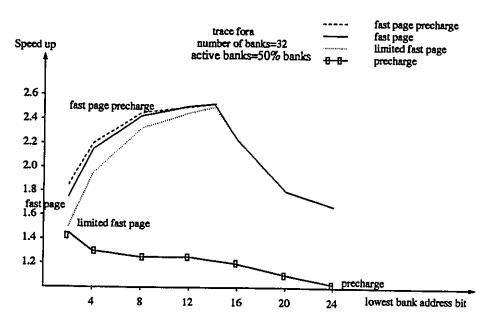

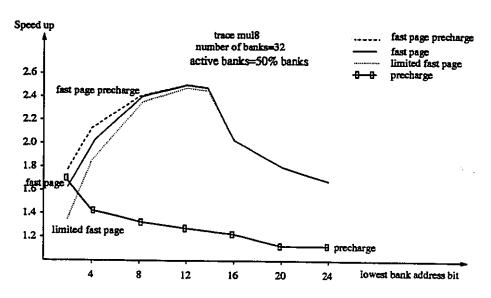

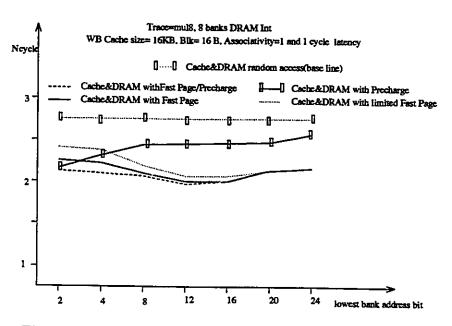

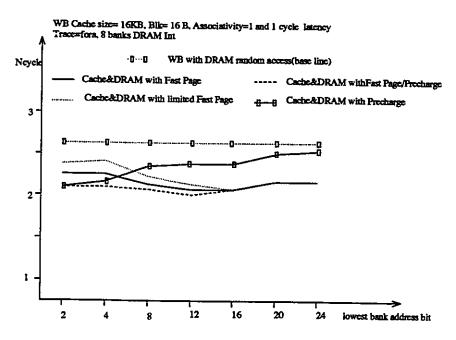

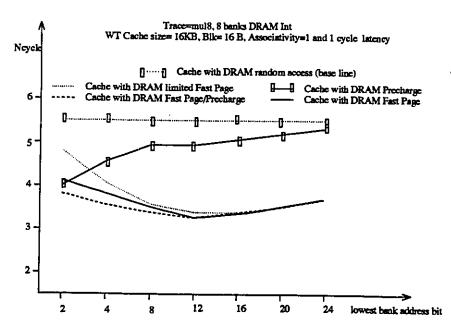

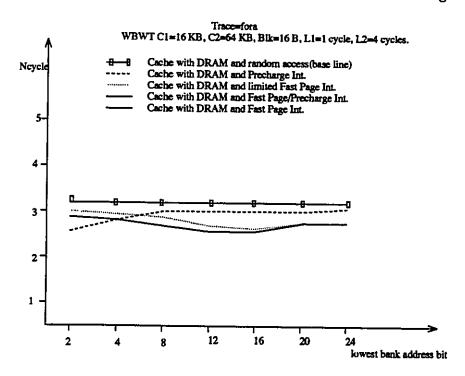

The location of address bits for bank select are varied to cover all the memory address space. Figures 3.12, 3.13, 3.14 and 3.15 show the performance speed up of each protocol versus the bank select address bits for the dec0, cc1, for and uml8 traces.

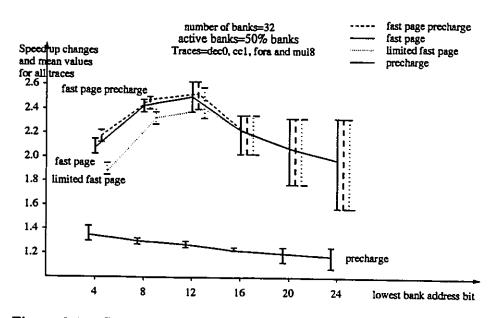

Figure 3.16 shows the range of changes in speed up due to the different traces versus the bank mapping address.

From the results, we find the following:

- The performance of all protocols vary considerably from varying the address interleaving (up to 260%).

- The precharge protocol performs badly with high address interleaving and gives its best performance when the banks are interleaved around a word size.

- The fast page, fast page precharge and limited fast page protocols give the best performance when the banks are mapped at A12 (page interleaving). This is a 2 K word bank size, and exactly the size of a page for the 4 M DRAM.

- The new fast page precharge gives the best performance of all protocols. This is particularly interesting as it actually requires less hardware than the fast page

Figure 3.12: Variable address interleaving for dec0 trace (4M DRAM) protocol.

• the results are insensitive to workload variations.

#### 3.7.2 Varying the DRAM size

The results for the rest of this Chapter are done using all the above traces. We choose only to display the results of one trace (mul8 trace) as the results are insensitive to workload variations (at the point of optimal performance), and this reduces the number of figures considerably.

The performance speed up from the new protocols also depends on the size of the DRAM chip. Figures 3.17 and 3.18 show the speed up for a low density DRAM

Figure 3.13: Variable address interleaving for cc1 trace (4M DRAM)

Figure 3.14: Variable address interleaving for fora trace (4M DRAM)

Figure 3.15: Variable address interleaving for mul8 trace (4M DRAM)

Figure 3.16: Speed up changes versus variable interleaving for 4M DRAM with different traces

that has a size of 256 K bit and the speed up of the 4M DRAM for the different protocols. From the figures, we conclude the following:-

- The performance of the precharge protocol does not depend on DRAM size.

- The optimum performance for the three other protocols occurs around A8, which is the size of a page for the 256 K bit DRAM.

- The performance of fast page, limited fast page and fast page precharge protocols is smaller than that of 4M DRAM, which indicates that larger DRAM size is an advantage when using those schemes (larger DRAM size means larger number of columns in one row and has an effect similar to using larger cache sizes).

- Future DRAM chips, with large sizes, should gain from using the four protocols and page interleaving.

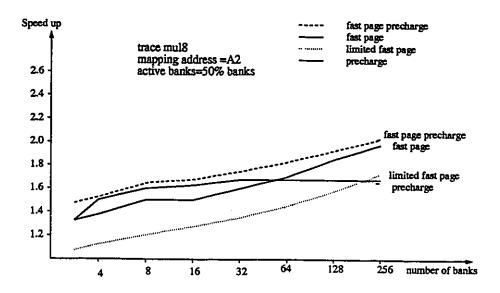

# 3.7.3 Low Order Address Interleaving versus number of banks

Figure 3.19 shows the performance speed up of each protocol versus the number of banks for the low order address interleaving for the 4 M DRAM.

From the results, we find the following:

Figure 3.17: Variable address interleaving for limited fast page and fast page precharge (256K and 4M DRAMs)

Figure 3.18: Variable address interleaving for precharge and fast page (256K and 4M DRAMs)

- the precharge protocol gives a very reasonable performance for a small number of banks. Increasing the number of banks for the precharge protocol helps the performance up to 8 banks and any more increase in number of banks does not produce an increase in performance.

- The fast page precharge gives the best performance of all protocols. The performance of the fast page precharge protocol increases with the increase in number of banks.

- The fast page protocol gives good performance with a very large number of banks.

- The limited fast page protocol gives only moderate performance and needs a large number of banks.

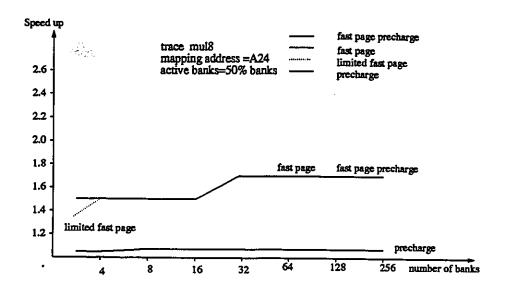

# 3.7.4 Performance of High Order Address Interleaving versus number of banks

Figure 3.20 shows the performance speed up of each protocol versus the number of banks for the high order address interleaving for the 4 M DRAM.

From the results, we find the following:

• The performance of fast page, fast page precharge and limited fast page are the same for bank numbers larger than 4.

Figure 3.19: Low order address interleaving

The precharge protocol gives the worst performance because the large bank size (most programs run in a single bank) forces most accesses to use the random access mode.

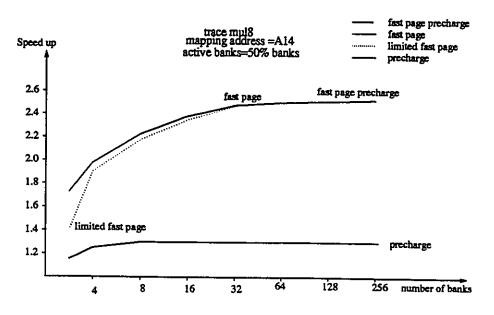

#### 3.7.5 Page interleaving versus number of banks

Figures 3.21 shows the performance speed up of each protocol versus the number of banks for the page interleaving for the 4 M DRAM. The page interleaving is when banks are interleaved around a page size; in this example, it is address A12.

From the results, we find the following:

- The precharge protocol gives the lowest performance.

- For large number of banks, the fast page, the fast page precharge and the limited

Figure 3.20: High order address interleaving

fast page protocols give similar performance.

- Increasing the number of banks improves performance. The increase in bank number gives diminishing returns if the number of banks is larger than 16.

- For a small number of banks, the fast page precharge and the fast page protocols give the best performance.

#### 3.8 Summary

In this Chapter we have investigated the effect of multi-bank DRAM interleaving with different access modes on the performance of main memory system. We present four interleaving protocols based on the use of the different DRAM access modes.

Figure 3.21: Page interleaving

The effect of bank mapping on system performance using the four protocols is studied. It is found that for interleaving based on the fast page access mode, best system performance occurs when banks are interleaved around a DRAM page size. With the RAS precharge access mode, best performance occurs when banks are interleaved around one word size.

A new fast page precharge protocol is introduced that offers the best performance with less banks, fewer row comparators and is suitable for future larger size DRAMs.

The performance of the fast page precharge is better than the performance of the fast page protocol but it uses less hardware (row comparators and latches).

### Chapter 4

### Single Level Cache Basics and

### Design

### 4.1 Review of Cache Design Basics

#### 4.1.1 Introduction

It is generally impossible to find fast enough main memory to match the speed of newer processors. One way of dealing with this speed gap is to add wait states to each processor memory access to match the DRAM speed. This would represent a significant reduction in system performance.

The better solution to this processor/main memory speed mismatch is to use a cache system. Cache memory uses a small, fast SRAM to provide the processor

with no wait state accesses. Information from the main memory (DRAM) is placed into the fast cache (SRAM) system and can be retrieved with no delay if it is needed again.

Cache operation is based on the concept of program locality. Programs tend to reference memory locations that are close to recently accessed locations (spatial locality), and tend to reference items that have been recently referenced (temporal locality).

In this Chapter, we review basic cache design and review the effect of cache parameters on system performance. In Section 2, we define cache terminology and discuss cache organization. Section 3 discusses the effect of cache parameters on miss rate. In Section 4, we review the different write strategies, present two designs (write through and write back), and examine the performance of each.

#### 4.1.2 Cache Terminology and Organization

#### Terminology

The following are the definitions of the most commonly used cache terms:

• Cache tag (directory): A memory device that is used to keep the addresses of memory locations that exist in the cache.

- Cache hit/miss: The cache has a comparator that compares the tag addresses

to the CPU addresses and gives a cache hit if a match occurs. If there is no

match the comparator signals a cache miss.

- Hit rate: The number of cache hits compared to the total number of memory references made by the CPU.

- Blocks: The amount of data loaded from the main memory and stored in cache

in a given access. Block size is always a multiple of the processor word size. For

each block in cache, the tag keeps the base address for data in the block.

- Valid bit: For each block in the cache, the tag uses an extra bit to indicate

whether or not the block has valid data (i.e., data in cache is the same as in

main memory).

- Associativity: If a given block can be stored in only one place in the cache, the

cache is known as direct mapped (associativity=1).

If a block can be stored in any place in the cache, the cache is known as fully associative.

If a block can be placed in a restricted set of places in the cache, the cache is known as set associative.

#### Cache Organization

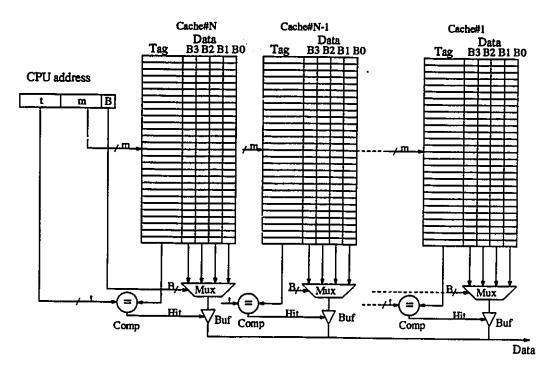

Figure 4.1 shows the organization of a N way set associative cache. The cache system consists of the following parts:

- Cache memory: This example uses N cache memories. The total size of each cache memory=  $2^m$  blocks (m points to the accessed block in the cache).

- Cache Blocks: The number of words in each block= 2<sup>B</sup> words (B points to the selected word in each block).

- Tag memory: The size of the tag memory=  $2^m \times t$  bits (t is used to determine if the CPU access exists in the cache).

- N sets: The N way set associativity is implemented by duplicating the cache memory and tag memory N times.

- multiplexers: each multiplexer is used to select one word from the selected cache block.

Note that for simplicity we have omitted the following:

- Byte accesses.

- Other ways of mapping the address to cache lines (hash, hash-rehash, and skewed).

Figure 4.1: Cache organization

#### 4.1.3 Cache Parameters and Miss rate

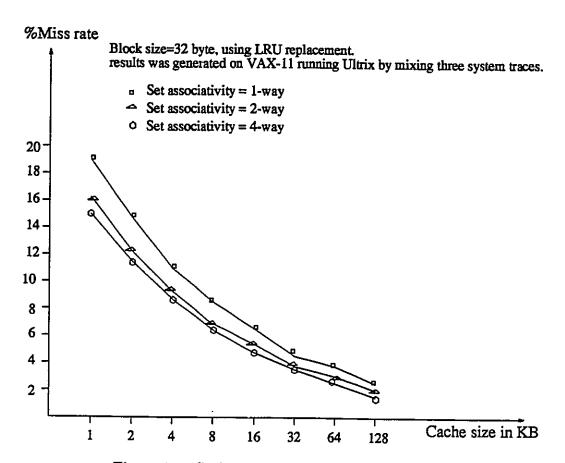

It is useful to briefly review the effect of cache design parameters on single-level cache miss rates. Since this is a set of well-known phenomenon, we will use the data from Hennessy and Patterson's book "Computer Architecture: A Quantitative Approach" page 421-424 [19]. The results are for a trace that has a total length of over a million addresses that was generated on a VAX-11 running Ultrix.

## The effect of cache size and cache associativity on miss rate

Figure 4.2 shows the effect of cache size on miss rate of a cache system with variable set associativity (according to [19]). The results show the following:

- Increasing the cache size, improves the cache hit rate.

- Increasing the cache associativity improves the cache hit rate.

- Increasing cache size influences miss rate much more than increasing cache associativity.

- The improvement in hit rate shows diminishing returns with larger cache sizes or larger cache associativity.

Figure 4.2: Cache size and associativity versus miss rate

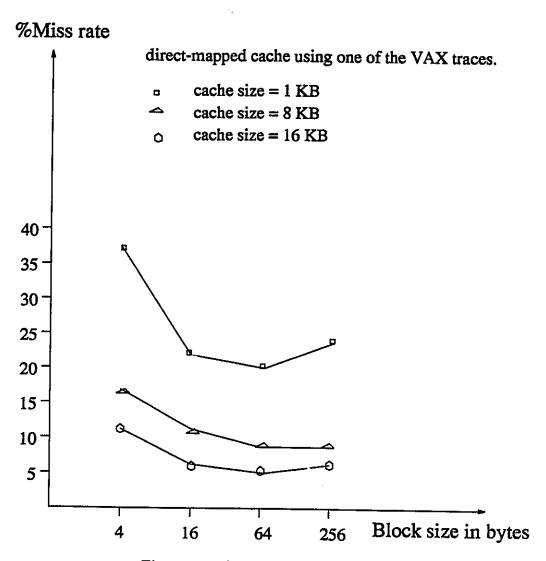

#### The effect of cache block size on miss rate

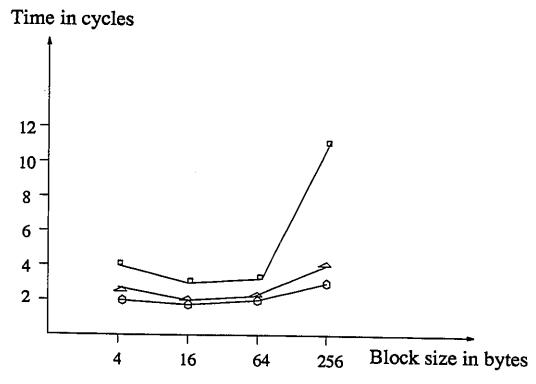

Figure 4.3 shows the effect of cache block size on cache miss rate [19]. Figure 4.4 shows the value of the average access time versus cache block size [19].

The results show the following:

- Larger block sizes generally reduce miss rate.

- The optimal miss rate for 1 KB, 8KB and 16 KB cache sizes occurs at a block size of 64 bytes.

- The optimal average access time for these cache sizes occurs at a block size of 16 bytes.

- The difference between the block size values for optimal miss rate and optimal

average access time indicates that the miss rate should not be used to evaluate

the cache performance, since average access time is a better predictor of system

performance.

### 4.1.4 Write Strategies

In any cache design, read operations are handled in the same way. On a read hit, the processor gets the data directly from the cache. On a read miss, the cache system gets the data from memory and updates the cache. It is the write strategy that distinguishes many cache designs.

Figure 4.3: Cache block size versus miss rate

direct-mapped cache using one of the VAX traces. memory latency = 8 cycles. transfer costs 1 cycle per 4 bytes

- cache size = 1 KB

- cache size = 8 KB

- o cache size = 16 KB

Figure 4.4: Cache block size versus average access time

#### Policies for Writing to the Cache

There are two different ways for handling write operations in a cache system :

- Write Through (WT): data written by the processor is always written to the main memory and cache at the same time.

- Write Back (WB): the data written by the CPU is stored in the cache and a

bit (the dirty bit) in the cache tag is set to indicate that the cache has data

that is different from the main memory contents. The write back of this block

to memory is deferred as long as possible.

## 4.1.5 Policies on a Write Miss

There are two policies on a write miss:

- Write allocate (WA): The cache is updated with the new data on a cache write miss.

- No write allocate (NWA): The data is written only to the main memory on a

cache write miss.

Figure 4.5: Write Through Cache with NWA

## 4.2 Single Level Cache Design

In the following, we present two models of a single level cache design based on using these different write strategies. The first model, WT-NWA, uses write through with the NWA policy. The second model, WB-NWA, uses write back with the NWA policy.

We use the flow graph method that was introduced in Chapter 3 to present the two models. The flow graph explains the design method, and defines precisely what happens in each operation (read, write, hit and miss) and also gives an overview of the whole system.

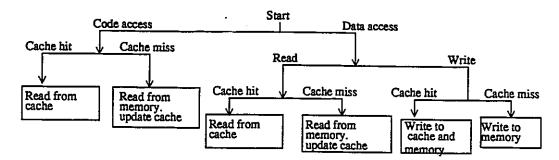

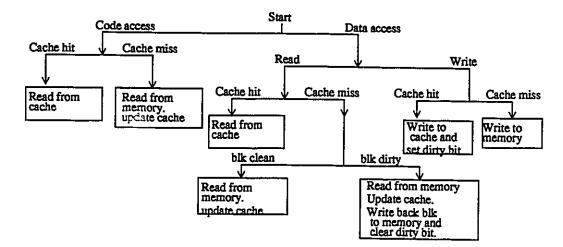

Figure 4.5 and figure 4.6 show the flow graphs of our WT and WB models.

## 4.2.1 Results and limitations of the WT-NWA and WB-NWA models

In this study we assume the following:

Figure 4.6: Write Back Cache with NWA

- The processor has separate data and instruction buses and uses separate instruction and data caches.

- The cache latency is 1 cycle.

- The main memory latency is 16 cycles.

- The cache uses no write allocate and implements the LRU replacement policy.

- The effect of the block size is to add 1 cycle per extra word size. The word size is 4 Bytes and the bus is 1 word wide.

- The CPU is a 1- clock-per-instruction Harvard type architecture.

The performance of the system is measured in the number of cycles per instruction (CPI), which is a more accurate representation of system performance than cache miss rate.

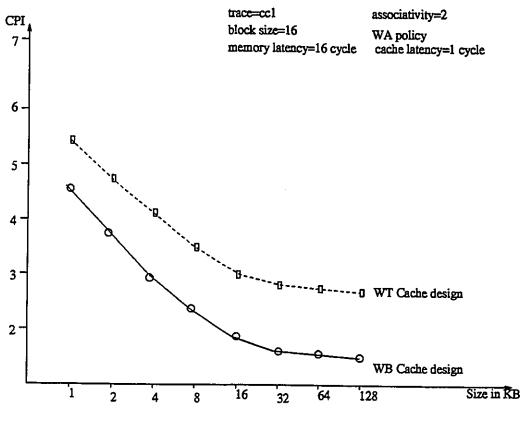

The following are the results of our WT-NWA and WB-NWA models using simulation with the cc1 benchmark trace (defined in Chapter 2).

#### • The effect of cache size:

Figures 4.7 shows the performance of the WT-NWA and the WB-NWA cache designs versus the cache size in KBytes.

The WB-NWA cache design gives better performance than the WT-NWA design. This is a natural consequences of the cost of writes to a slow memory and the high frequency of write operations in the workload. The increase in cache size improves the performance up to a size of 16 KB, then the rate of performance improvement diminishes.

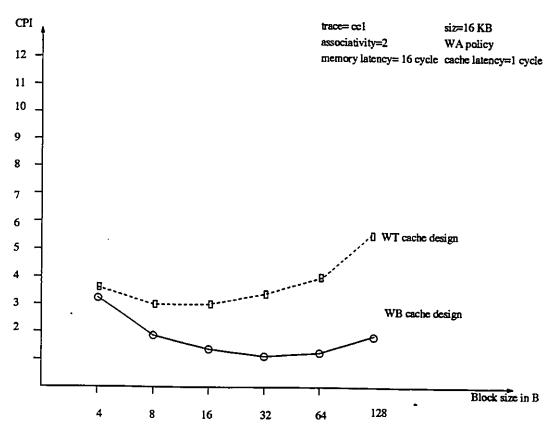

#### The effect of cache block size:

Figures 4.8 shows the performance of the WT and the WB cache designs versus the cache block size in Bytes.

Optimal WT-NWA and WB-NWA performance occurs with block size in the range of 16- 32 Bytes.

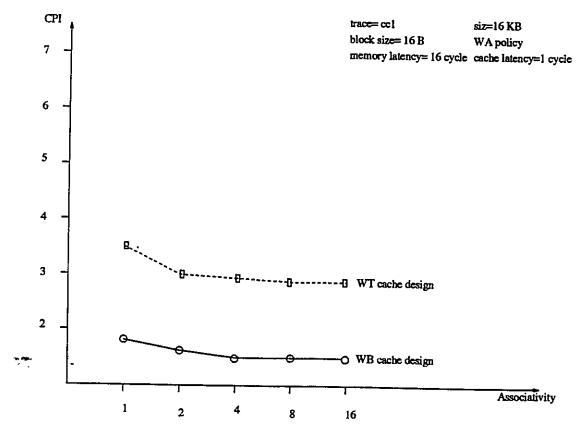

#### • The effect of cache set associativity: