INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand comer and continuing from left to

right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

UMI

800-521-0600

# DESIGN, FABRICATION AND CHARACTERIZATION OF N-CHANNEL InGaAsP-InP BASED INVERSION CHANNEL TECHNOLOGY DEVICES (ICT) FOR OPTOELECTRONIC INTEGRATED CIRCUITS (OEIC):

Double Heterojunction Optoelectronic Switches (DOES),

Heterojunction Field-Effect Transistors (HFET),

Bipolar Inversion Channel Field-Effect Transistors (BICFET) and

Bipolar Inversion Channel Phototransistors (BICPT).

By

EUGENE TAN, B.Eng., M.Eng.

A Thesis

Submitted to the School of Graduate Studies

in Partial Fulfillment of the Requirements for the Degree

Doctor of Philosophy

McMaster University Hamilton, Ontario, Canada

© Copyright by Eugene Tan, 1998

# InGaAsP-InP BASED INVERSION CHANNEL TECHNOLOGY **DEVICES FOR OEIC**

DOCTOR OF PHILOSOPHY (1998) (Engineering Physics)

McMASTER UNIVERSITY Hamilton, Ontario

Canada

TITLE: Design, Fabrication and Characterization of n-Channel

InGaAsP-InP Based Inversion Channel Technology

Devices (ICT) for Optoelectronic Integrated Circuits (OEIC): Double Heterojunction Optoelectronic Switches (DOES), Heterojunction Field-Effect Transistors (HFET), Bipolar Inversion Channel Field-Effect Transistors (BICFET) and Bipolar Inversion Channel Phototransistors (BICPT).

AUTHOR: Eugene Tan, B.Eng., M.Eng. (McMaster University)

SUPERVISORS: Dr. J.G. Simmons and Dr. D.A. Thompson

NO. OF PAGES: xxii, 220

### **ABSTRACT**

This thesis demonstrates inversion channel technology (ICT) as a viable technique for realizing InGaAsP-InP based monolithic optoelectronic integrated circuits (OEIC). Inversion channel technology utilizes a common substrate and a common fabrication sequence to monolithically integrate electrical, optical and optoelectronic devices, therefore, requiring compatibility in both the device structure and fabrication sequence. This technology is demonstrated by designing, fabricating and characterizing four types of ICT devices, the DOES, HFET, BICFET and BICPT, on a common structure with a common fabrication sequence. These devices were selected because they are complementary in function and provide the circuit designer all the basic elements for building monolithic OEICs: optical emitter, optoelectronic switches, bipolar and unipolar transistors, and photodetectors.

Device models for InGaAsP-InP based DOES, HFET, BICFET and BICPT are developed and used to design the four device structures used in this work. These models identify the effect of device structure on the performance of the devices. The device models are also used to predict the input, output and transfer characteristics of each type of device. This provides an understanding of device physics and operation, and a basis for comparison with experimental results.

A common fabrication sequence and fabrication recipes for self-aligned n-channel InGaAsP-InP based DOES, HFET, BICFET and BICPT is designed, developed and demonstrated. This includes the photomask set for self-

aligned ICT devices, SiO<sub>2</sub> masking for self-aligned contact formation, SiO<sub>2</sub> sidewall passivation of mesas for ion-implantation, high accuracy RIE etching with a an in-situ QMS, implant activation for n- and p-implants in InGaAsP-InP, and metallization over tall vertical mesa structures.

The operation of the DOES, HFET, BICFET and BICPT is demonstrated experimentally. Complete sets of electrical, optical and optoelectronic measurements of the input, output and transfer characteristics of each type of device is performed. These characteristics are compared with the theoretical predictions made by the models to validate the operation of each type of device.

This work demonstrates ICT as a technology for realizing OEICs in the InGaAsP-InP material system, and presents the technology required to design, fabricate and characterize these integrated devices.

### **ACKNOWLEDGMENTS**

"If I have seen farther it is by standing on the shoulders of giants.."

—Sir Isaac Newton

I wish to thank my supervisors John Simmons and Dave Thompson for their guidance, encouragement, and technical support. Thanks to the Institute for Microstructural Sciences at the National Research Council of Canada, Bell Northern Research, the Natural Sciences and Engineering Research Council, the Ontario Centre for Materials Research, the Ontario Graduate Scholarship Program, the Centre for Electrophotonic Materials and Devices, McMaster University, and the Department of Engineering Physics for providing me with technical and financial support.

Many thanks to my coworkers who unselfishly shared their time, knowledge and equipment, and to my friends who have been a tremendous source of knowledge, encouragement and support:

Jim Swoger, Jugnu Ojha, Steve Kovacic, Heidi Pinkney, Greg Letal, Gary Dyck, Bruce Takasaki, Marcel Boudreau, Jeff Brown, Rob Bierman, Jon Showell, Mike Clarke, John Hazell, Doug Bruce, Kechang Song, Doris Stevanovich, Mike Davies, Phil Chow-Chong, Margaret Buchanan, Case Blaauw, Nobert Peutz, Doug Melville, Boris Elenkrig, Elaine Moore, Ann Greene, Fran Allen, Bobbie Kartonchik, Paul Jessop, Andreas Decken and Bob Hamade.

Sincere thanks to my wife Susan, my parents and sister (Phil, Grace and Lianne Tan), and my in-laws (the Clugstons) for their love, encouragement and support.

### **TABLE OF CONTENTS**

| ABSTRACT                                                 | iii |

|----------------------------------------------------------|-----|

| ACKNOWLEDGMENTS                                          | v   |

| TABLE OF CONTENTS                                        | /ii |

| LIST OF FIGURESx                                         | iii |

| LIST OF TABLES                                           | cxi |

| CHAPTER 1                                                |     |

| INTRODUCTION                                             | 1   |

| 1.1 Technological Trends and Driving Forces              | 1   |

| 1.2 Telecommunication Systems                            |     |

| 1.3 Optical Communication Systems                        |     |

| 1.4 Monolithic Optoelectronic Integrated Circuits (OEIC) |     |

| 1.5 OEIC Technology                                      |     |

| 1.6 Inversion Channel Technology for OEIC's              |     |

| 1.7 Motivation and Scope                                 | 10  |

| References                                               |     |

| CHAPTER 2                                                |     |

| DESCRIPTION AND THEORY OF THE DOES                       | 19  |

| 2.1 Device Structure                                     | 20  |

| 2.2 Device Model                                         |     |

| 2.2.1 Internal Potentials and Voltages                   | 21  |

| 2.2.2 Charge Conservation and Fixed Charge Components    |     |

| Charge Conservation                                      |     |

| Depletion Layer Charges                                  |     |

| Charge Sheet Layer Charge                                |     |

| Inversion Channel Charge                                 |     |

| 2.2.3 Current Continuity and Current Density               |    |

|------------------------------------------------------------|----|

| Components2                                                | 28 |

| Current Continuity 2                                       | 28 |

| Diffusion Currents2                                        | 29 |

| Thermionic Currents3                                       | 31 |

| Net-Thermal Recombination Currents 3                       | 32 |

| Optically Generated Currents3                              | 34 |

| Terminal Currents                                          | 35 |

| 2.2.4 Optical Emission                                     | 36 |

| 2.2.5 Solution to DOES Device Equations                    | 37 |

| 2.3 Device Operation                                       | 37 |

| 2.3.1 The a-c, e-i and a-i Junctions of the DOES           |    |

| 2.3.2 J-V Characteristics                                  |    |

| OFF State                                                  |    |

| NDR State                                                  | 46 |

| ON State                                                   | 46 |

| 2.3.3 Two-Terminal L-J Characteristics                     | 47 |

| 2.3.4 Effect of Inversion-Channel Current                  |    |

| 2.3.5 Effect of Active-Layer Current                       | 49 |

| 2.3.6 Efficiency of the Inversion-Channel and Active-Layer |    |

| Current                                                    | 53 |

| 2.3.7 Effect of Optical Injection                          | 53 |

| 2.4 Device Structure Design                                | 57 |

| References                                                 | 60 |

|                                                            |    |

| CHAPTER 3                                                  |    |

| DESCRIPTION AND THEORY OF THE HFET                         | 61 |

| 3.1 Device Structure                                       | 62 |

| 3.2 Biasing and Operation                                  | 63 |

| 3.3 Charge Conservation and Fixed Charge Components        | 63 |

| 3.4 Charge States                                          | 66 |

| Threshold Voltage                                          |    |

| 3.5 Current-Voltage Characteristic                         |    |

| Linear Region                                              |    |

| Saturation Region                                          |    |

| 3.6 Transconductance                                       |    |

| References                                                      | <i>7</i> 5 |

|-----------------------------------------------------------------|------------|

| CHAPTER 4                                                       |            |

| DESCRIPTION AND THEORY OF THE BICFET AND BICPT                  | 77         |

| 4.1 Device Structure                                            |            |

| 4.2 Biasing and Operation                                       | 80         |

| 4.3 Device Model                                                | 81         |

| 4.3.1 Internal Potentials and Voltages                          | 81         |

| 4.3.2 Charge Conservation and Fixed Charge Components.          | 85         |

| 4.3.3 Current Continuity and Current Density  Components        | 85         |

| 4.3.4 Solution to Device Equations                              |            |

| 4.4 BICFET Output Current-Voltage Characteristic                |            |

| OFF State                                                       |            |

| LINEAR State                                                    |            |

| SATURATION State                                                |            |

| 4.5 BICFET/BICPT Output Resistance                              |            |

| 4.6 BICFET Current Gain Characteristic                          |            |

| 4.7 BICPT Output Current-Voltage Characteristic                 | 94         |

| References                                                      |            |

|                                                                 |            |

| CHAPTER 5                                                       |            |

| FABRICATION OF 4-TERMINAL N-CHANNEL InGaAsP-InP BASED           |            |

| ICT DEVICES                                                     | 99         |

| 5.1 Device Structure                                            | 100        |

| 5.2 Fabrication Sequence                                        | 106        |

| 5.3 Photolithographic Mask Set                                  | 115        |

| 5.4 Cleaving and Cleaning of Substrates                         |            |

| 5.5 Patterning of CVD-SiO <sub>2</sub>                          | 121        |

| 5.6 Photoresist Mask for Ion-Implantation                       | 123        |

| 5.7 Patterning for Metal Lift-Off and Lift-Off                  | 124        |

| 5.8 Self-aligned SiO <sub>2</sub> and Sidewall Passivation Mask | 126        |

| 5.9 RIE with QMS                                                | 130        |

| 5.9.1 Etching Parameters                                        | 132        |

| 5.9.2 In-Situ Analysis With QMS                                 |            |

| 5.9.3 Chamber Cleaning                                          |            |

| 5.10 n- and p-Type Ion Implantation                                               | 140 |

|-----------------------------------------------------------------------------------|-----|

| 5.11 Implant Activation by RTA                                                    |     |

| 5.11.1 Annealing Results                                                          |     |

| 5.12 Contact Metallization                                                        |     |

| 5.12.1 Backside Metal                                                             | 149 |

| 5.12.2 Topside Metal with Tilt Stage                                              | 150 |

| 5.12.3 Contact Anneal Conditions                                                  |     |

| References                                                                        | 155 |

| CHAPTER 6                                                                         |     |

| EXPERIMENTAL CHARACTERIZATION OF THE DOES                                         | 159 |

| 6.1 Experimental Apparatus and Biasing                                            | 159 |

| 6.2 Two-Terminal Device Operation                                                 | 163 |

| 6.2.1 DC I-V Characteristics                                                      | 163 |

| 6.2.1 Time-Dependent I-V Characteristics                                          | 167 |

| 6.3 Effect of Structural Parameters and Size                                      | 169 |

| 6.4 Four-terminal Device Operation                                                | 173 |

| 6.4.1 Effect of Inversion Channel Current                                         |     |

| 6.4.2 Effect of Active Layer Current                                              | 176 |

| 6.4.3 Summary of Current Injection                                                |     |

| 6.5 Optical Characteristics                                                       |     |

| 6.5.1 L-I Characteristics                                                         |     |

| 6.5.2 Effect of Optical Injection                                                 |     |

| CHAPTER 7                                                                         |     |

| EXPERIMENTAL CHARACTERIZATION OF THE HFET                                         | 187 |

| 7.1 Experimental Apparatus and Biasing                                            | 187 |

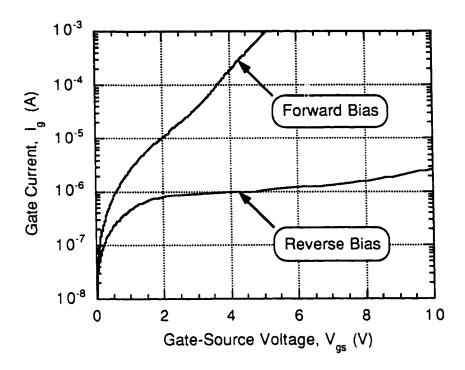

| 7.2 Input Characteristics                                                         | 188 |

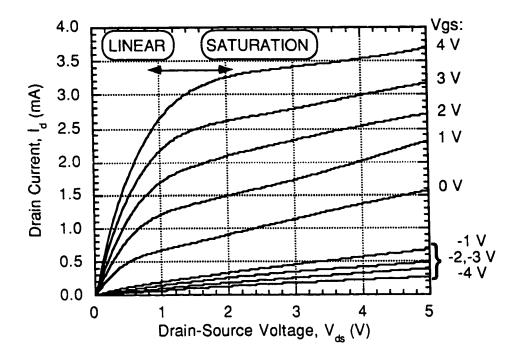

| 7.3 Output Characteristics                                                        | 189 |

| 7.3.1 Drain Current Characteristics (I <sub>d</sub> -V <sub>ds</sub> )            | 189 |

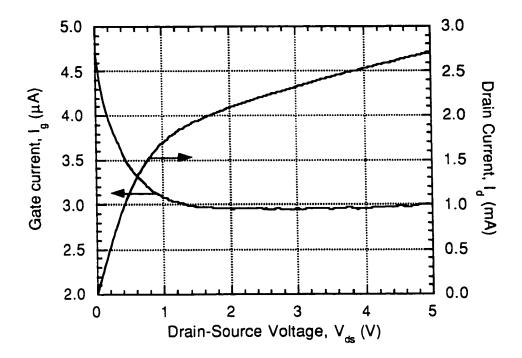

| 7.3.2 Gate Current Characteristics (Ig-Vds)                                       |     |

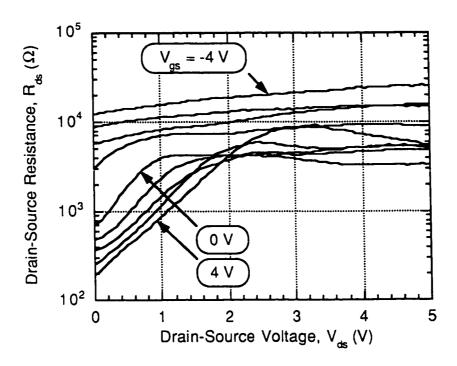

| 7.3.3 Drain-Source Resistance Characteristics (R <sub>ds</sub> -V <sub>ds</sub> ) | 193 |

| 7.4 Transfer Characteristics                                                      | 193 |

| 7.4.1 Drain Current Characteristics (I <sub>d</sub> -V <sub>gs</sub> )            |     |

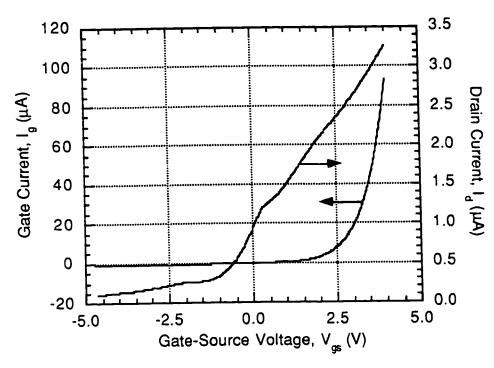

| 7.4.2 Gate Current Characteristics (Ig-Vgs)                                       | 195 |

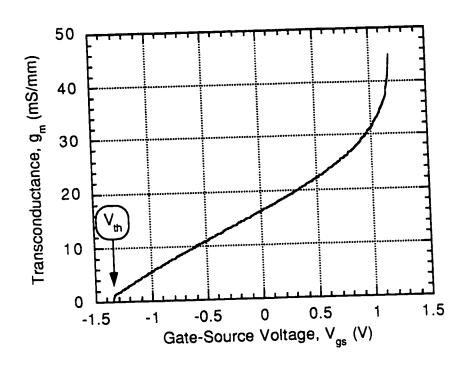

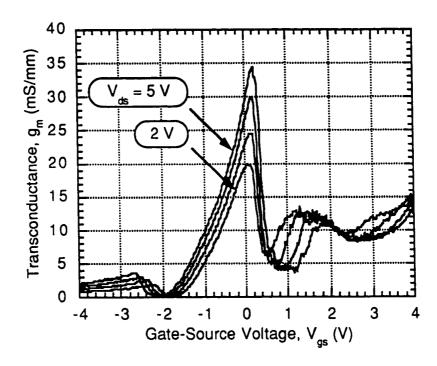

| 7.4.3 Transconductance Characteristics (g <sub>m</sub> -V <sub>gs</sub> )         | 197 |

|     | 7.5 Effect of Structural Parameters           | 197 |

|-----|-----------------------------------------------|-----|

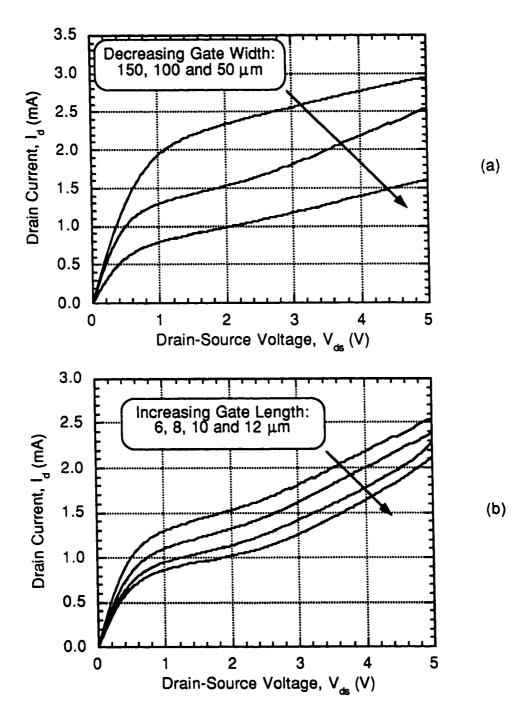

|     | 7.6 Effect of Size                            | 200 |

|     | References                                    | 203 |

| CH. | APTER 8                                       |     |

| EXP | PERIMENTAL CHARACTERIZATION OF THE BICFET AND |     |

| BIC | PT                                            | 205 |

|     | 8.1 BICFET                                    | 206 |

|     | 8.2 BICPT                                     | 212 |

| CH  | APTER 9                                       |     |

| CO  | NCLUSIONS                                     | 217 |

### LIST OF FIGURES

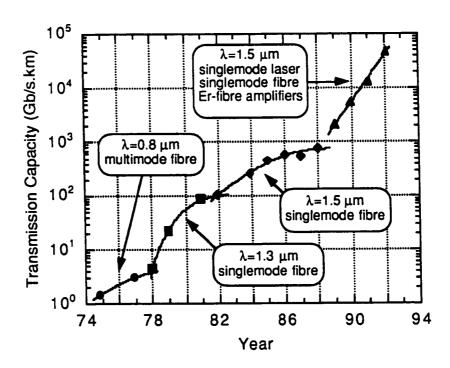

| Figure 1.1:  | Progress of optical transmission system capacity [3] 5                                                                                                                                                                                    |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

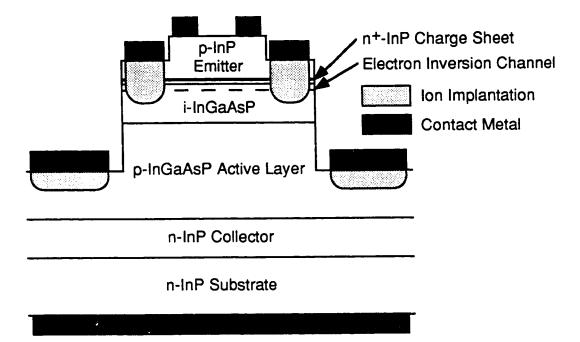

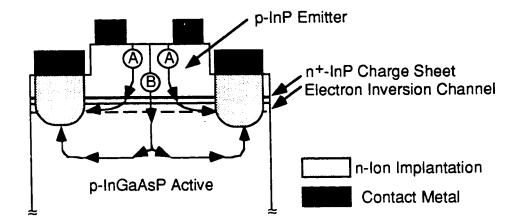

| Ü            | Schematic cross-section of a 4-terminal n-channel InGaAsP-InP double heterostructure optoelectronic switch (DOES).                                                                                                                        |

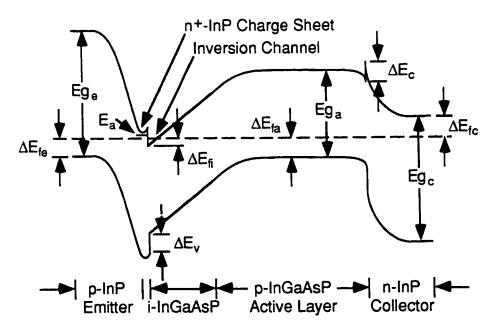

| Figure 2.2:  | Equilibrium energy-band representation of the n-channel InGaAsP-InP DOES including the energy levels and energy gaps (see Figs. 2.3 and 2.5 also)                                                                                         |

| Figure 2.3:  | OFF-state energy band representation of the DOES device including the internal potentials, junction voltages and depletion layer thicknesses (see Figs. 2.2 and 2.5 also)                                                                 |

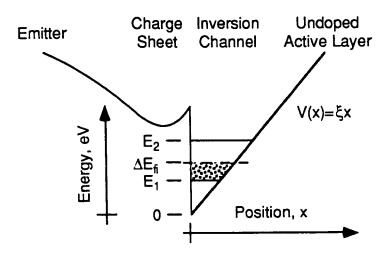

| Figure 2.4:  | Magnified view of the triangular potential well formed at the p-p heterointerface of the DOES. The triangular potential approximation is applied to yield analytical solutions for the first and second energy levels ( $E_1$ and $E_2$ ) |

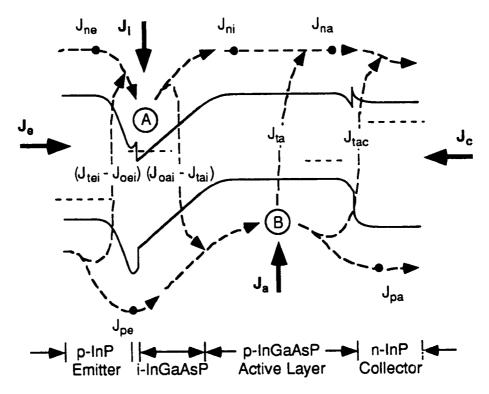

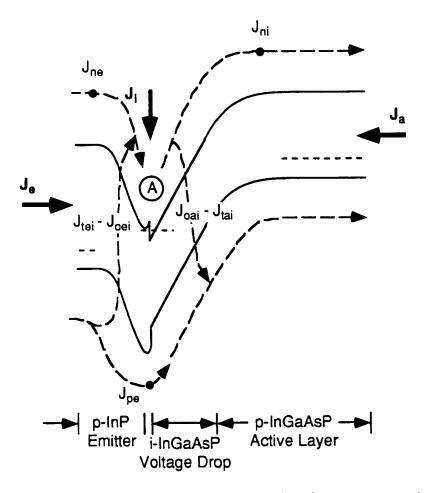

| Figure 2.5:  | ON-state energy band representation of the DOES identifying the internal current density components, terminal current density components and direction of current flow (see Figs. 2.2 and 2.3 also)                                       |

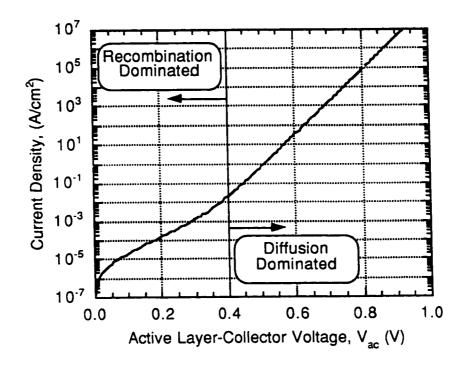

| Figure 2.6:  | Current density-voltage (J-V) characteristics of the active layer-collector (a-c) junction of the DOES                                                                                                                                    |

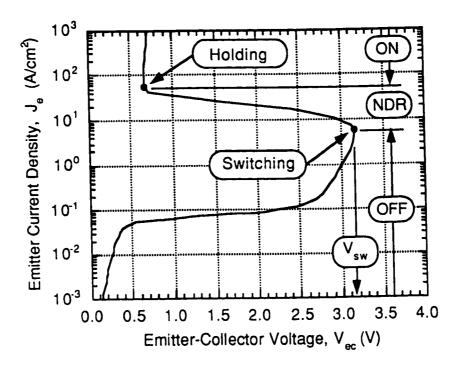

| Figure 2.7:  | Dark, two-terminal J-V characteristic of the DOES 41                                                                                                                                                                                      |

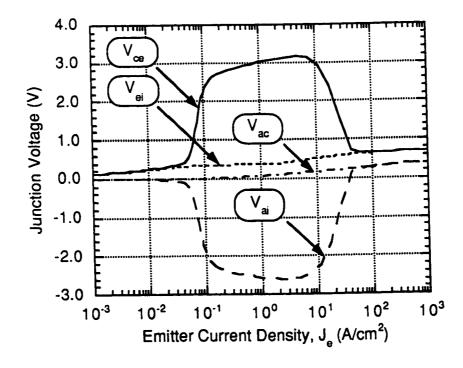

| Figure 2.8:  | Voltage across the e-i, a-i and a-c junctions as a function of emitter current density                                                                                                                                                    |

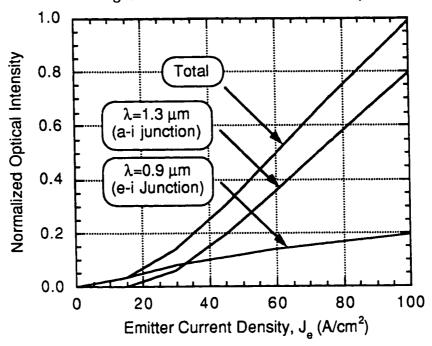

| Figure 2.9:  | Light-current density (L-J) characteristic of the DOES 48                                                                                                                                                                                 |

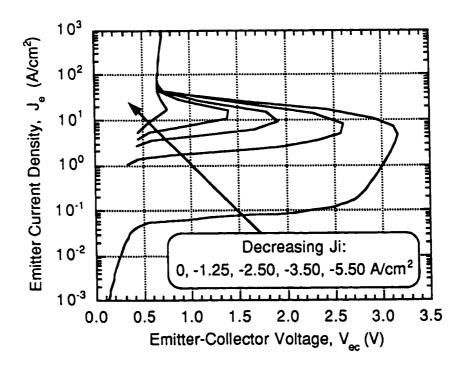

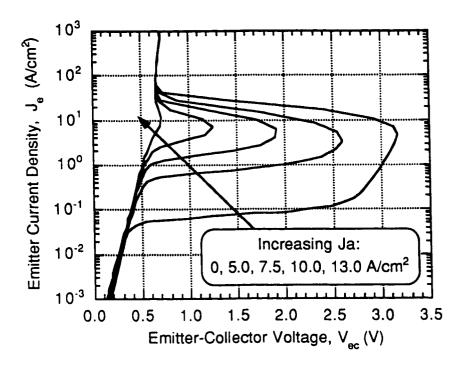

| Figure 2.10: | J-V characteristic of the DOES with inversion-channel current density ( $J_i$ ) as the parametric variable                                                                                                                                |

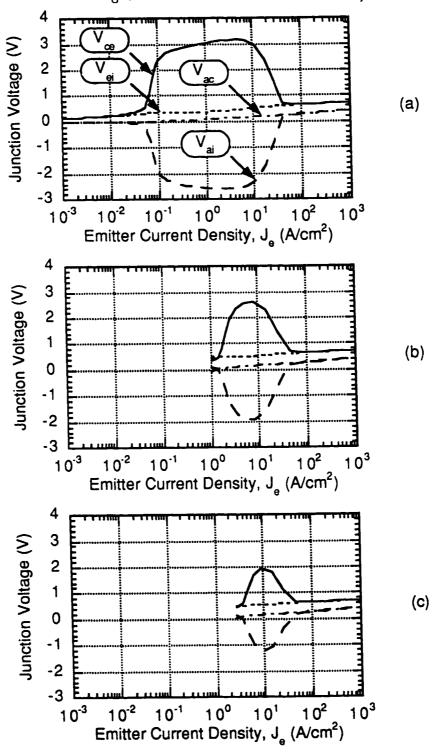

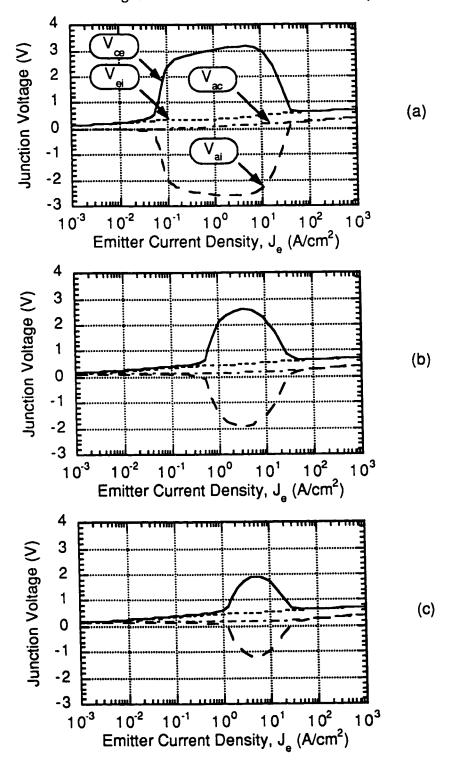

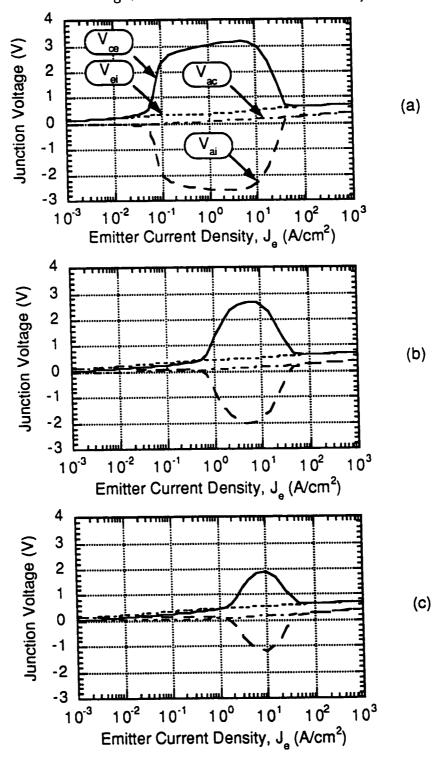

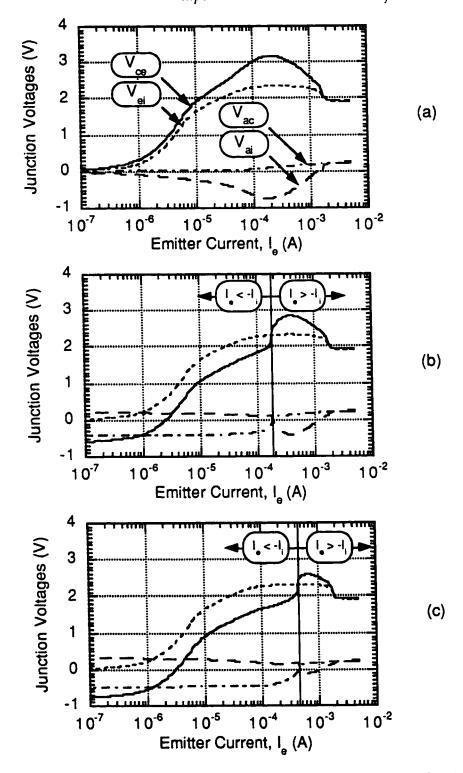

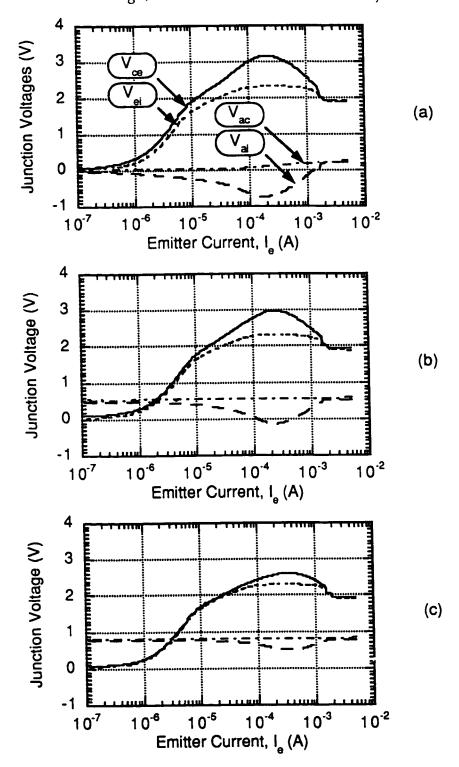

| Figure 2.11: | Voltage across the e-i, a-i and a-c junctions as a function of emitter current density with inversion-channel current density $J_i = a$ 0, b) -1.25 and c) -2.5 A/cm <sup>2</sup>     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.12: | J-V characteristic of the DOES with active-layer current density ( $J_a$ ) as the parametric variable                                                                                 |

| Figure 2.13: | Voltage across the e-i, a-i and a-c junctions as a function of emitter current density with active-layer current density $J_a = a) 0$ , b) 5.0 and c) 7.5 A/cm <sup>2</sup>           |

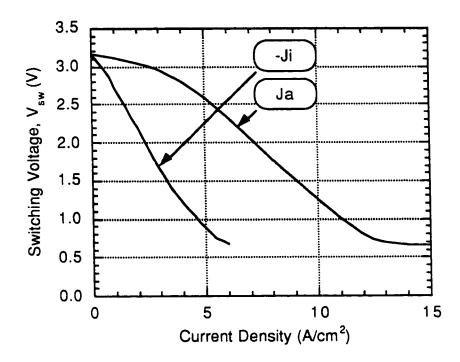

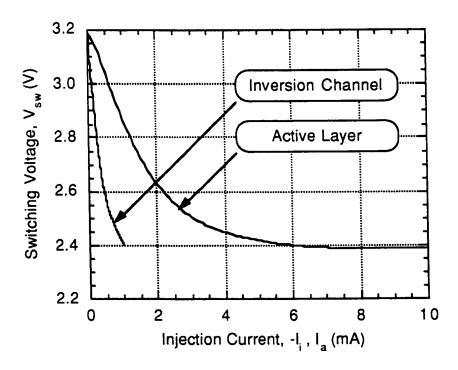

| Figure 2.14: | Switching voltage of the DOES as a function of the inversion-channel current density $(J_i)$ and active-layer current density $(J_a)$                                                 |

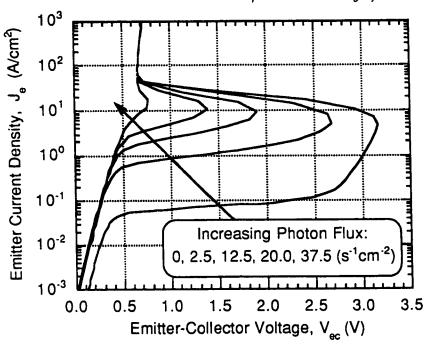

| Figure 2.15: | J-V characteristic of the DOES with incident photon flux as the parametric variable                                                                                                   |

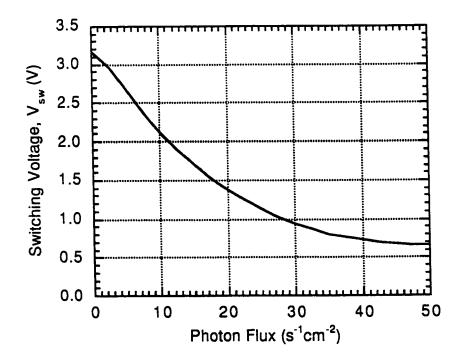

| Figure 2.16: | Switching voltage of the DOES as a function of the incident photon flux                                                                                                               |

| Figure 2.17: | Voltage across the e-i, a-i and a-c junctions as a function of emitter current density with incident optical flux $\Phi = a$ ) 0, b) 2.5 and c) 12.5 s <sup>-1</sup> cm <sup>-2</sup> |

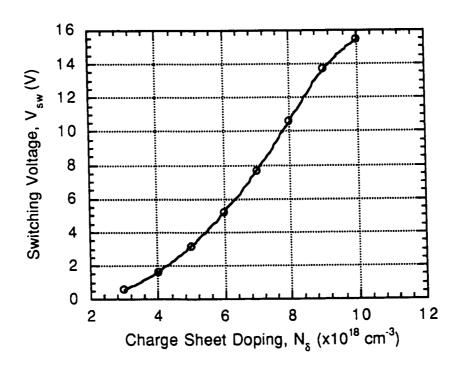

| Figure 2.18: | Switching voltage of the DOES as a function of the charge sheet doping ( $N_\delta$ )                                                                                                 |

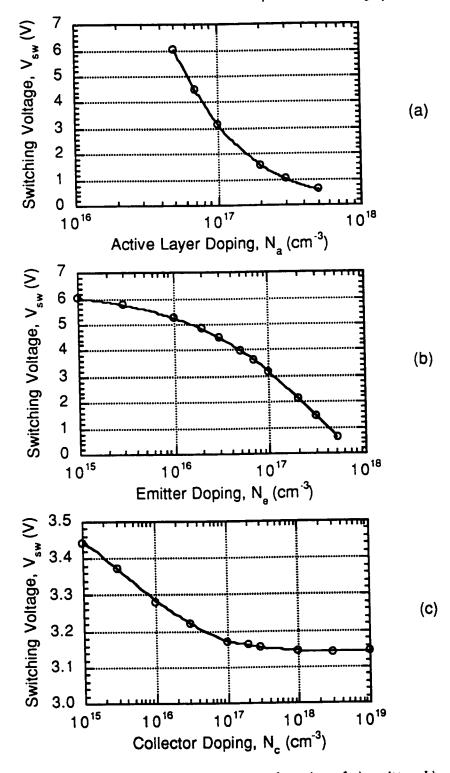

| Figure 2.19: | Switching voltage of the DOES as a function of a) emitter, b) active layer and c) collector layer doping                                                                              |

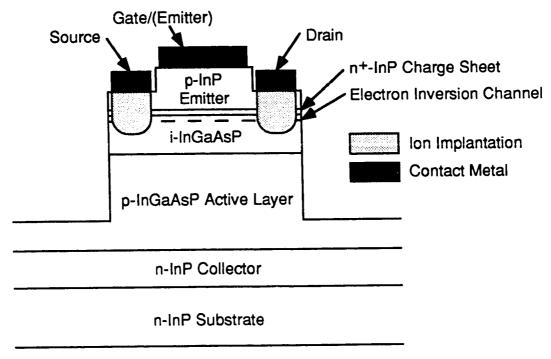

| Figure 3.1:  | Schematic cross-sectional view of the n-channel InGaAsP-InP heterojunction field-effect transistor (HFET)                                                                             |

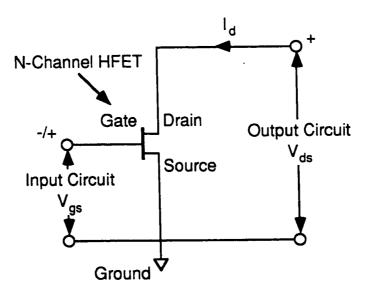

| Figure 3.2:  | Typical biasing scheme for an n-channel HFET in the common-source circuit configuration                                                                                               |

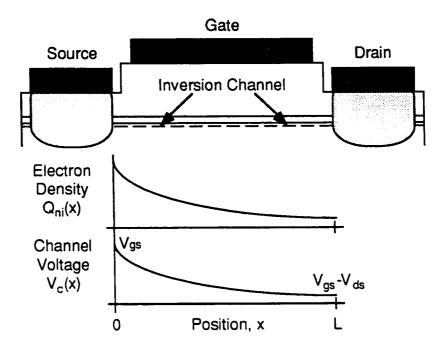

| Figure 3.3:  | Magnified cross-sectional view of the HFET illustrating the variation of the electron density $(Q_{ni})$ and channel voltage $(V_c)$ with position $(x)$                              |

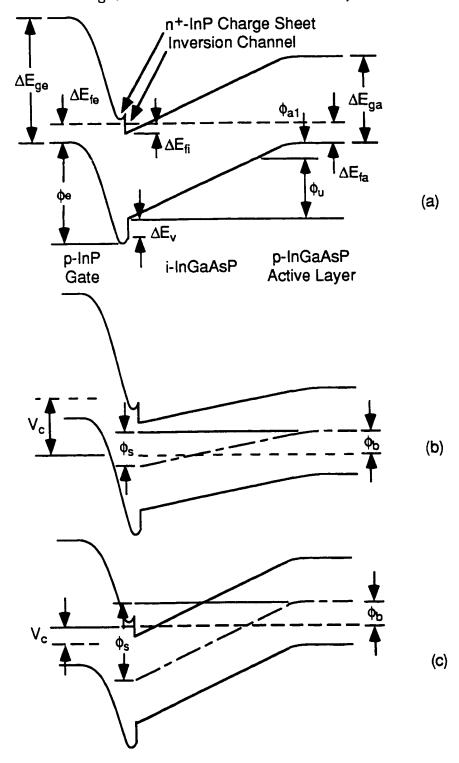

| Figure 3.4:  | Energy band representation of the n-channel HFET under a) Equilibrium, b) Depletion and c) Strong Inversion                                                                           |

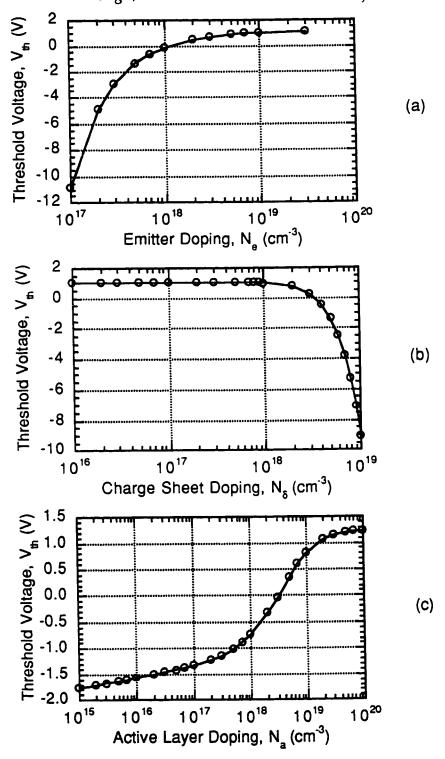

|              | Threshold voltage of the HFET as a function of the a) emitter, b) charge sheet and c) active layer doping                                                                                             | 70   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

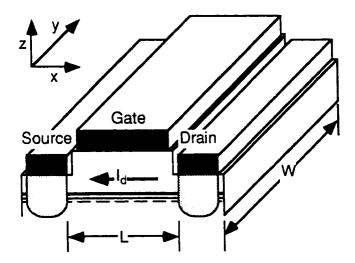

| Figure 3.6:  | Three-dimensional view of the n-channel HFET                                                                                                                                                          | 72   |

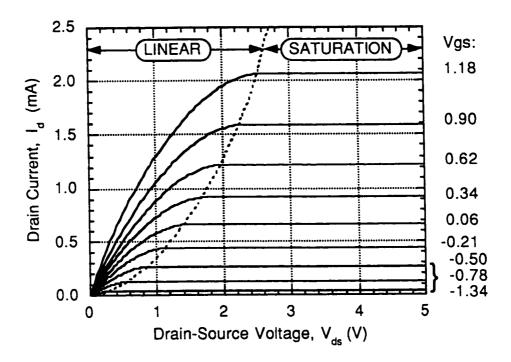

| Figure 3.7:  | I <sub>d</sub> -V <sub>ds</sub> characteristic of the HFET                                                                                                                                            | 74   |

| Figure 3.8:  | Transconductance characteristic of the HFET                                                                                                                                                           | 75   |

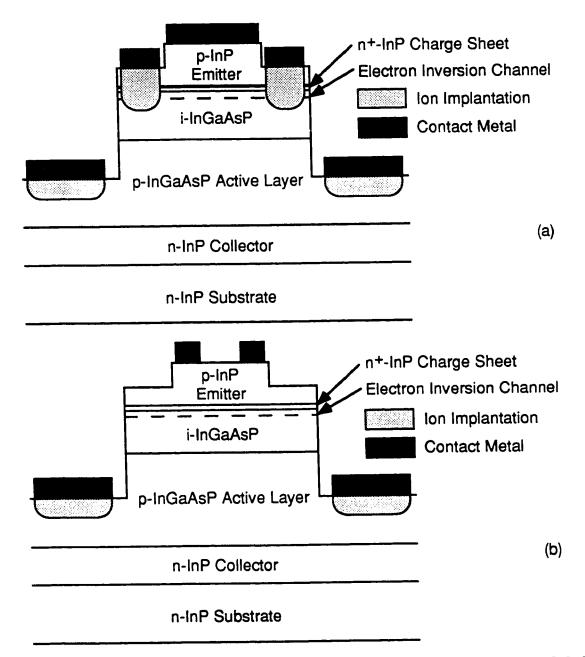

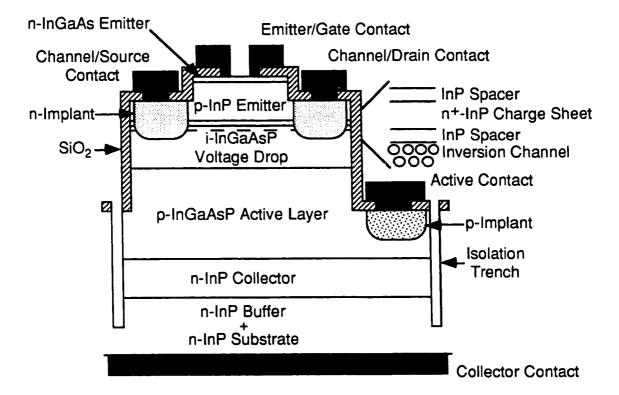

|              | Schematic cross-sectional view of the n-channel InGaAsP-InP based a) bipolar inversion channel field effect transistor (BICFET) and b) bipolar inversion channel phototransistor (BICPT)              | 79   |

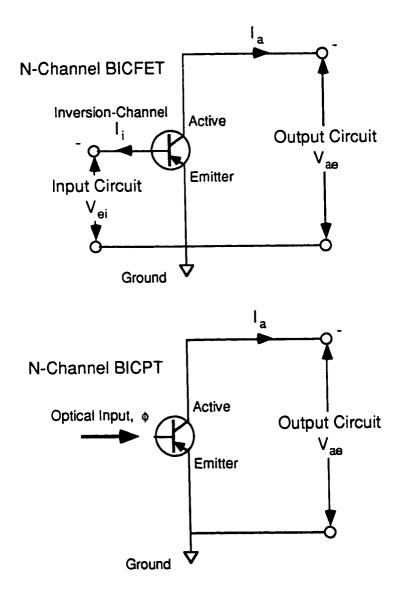

| J            | Typical biasing scheme for the n-channel a) BICFET and b) BICPT connected in the common-emitter circuit configuration.                                                                                | 82   |

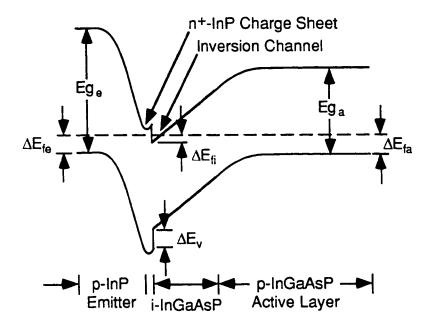

| Figure 4.3:  | Equilibrium energy band representation of the n-channel InGaAsP-InP BICFET/BICPT showing the energy levels and energy gaps (see Figs. 4.4 and 4.5 also).                                              | 83   |

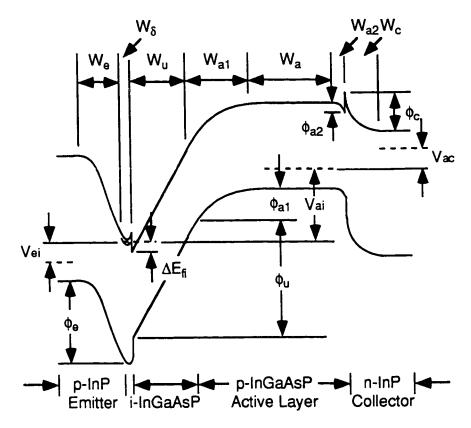

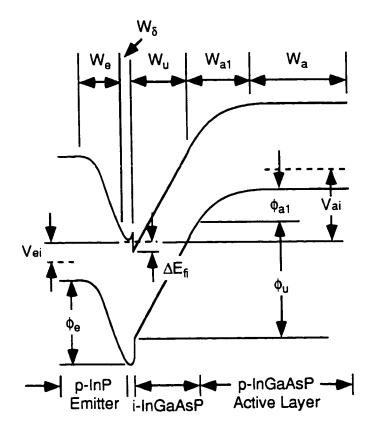

| Figure 4.4:  | SATURATION-state energy band representation of the BICFET/BICPT showing the internal potentials, junction voltages and depletion layer thicknesses (see Figs. 4.3 and 4.5 also)                       | 84   |

| Figure 4.5:  | SATURATION-state energy band representation of the BICFET/BICPT showing the internal current components, terminal currents and direction of current flows (see Figs. 4.3 and 4.4 also).               | 87   |

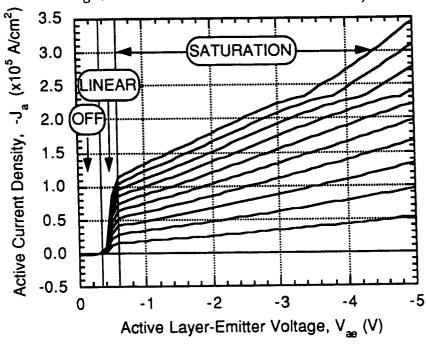

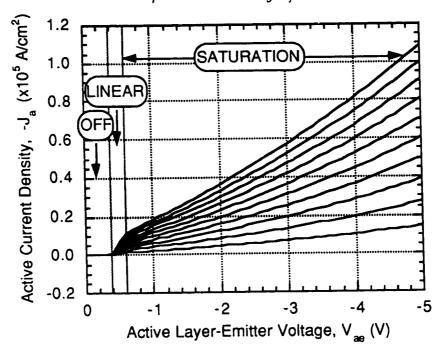

| Figure 4.6:  | Common-emitter output characteristic $(J_a-V_{ae})$ of the BICFET with $J_i$ as the parametric variable $(J_i=0 \text{ to } -1000 \text{ A/cm}^2 \text{ in } -100 \text{ A/cm}^2 \text{ increments})$ | 90   |

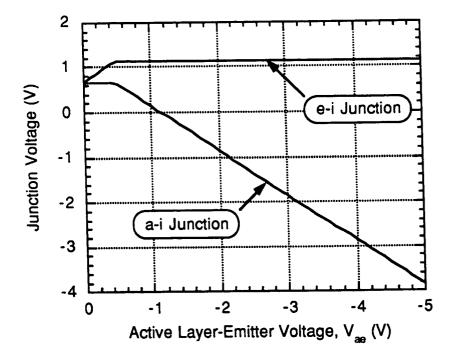

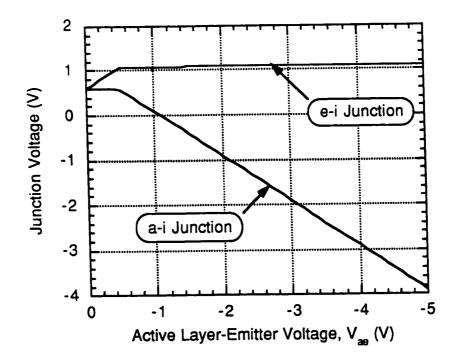

| Figure 4.7:  | $V_{ei}$ and $V_{ai}$ as a function of $V_{ae}$ for $J_i = -500$ A/cm <sup>2</sup>                                                                                                                    | 90   |

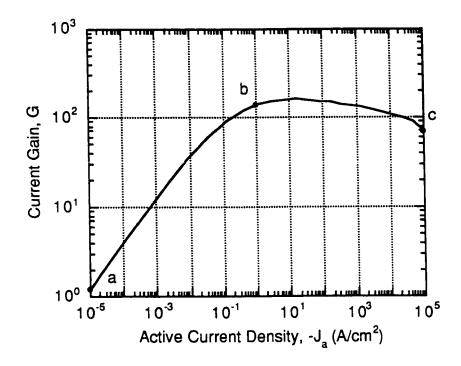

| Figure 4.8:  | Current gain characteristics of the BICFET                                                                                                                                                            | 94   |

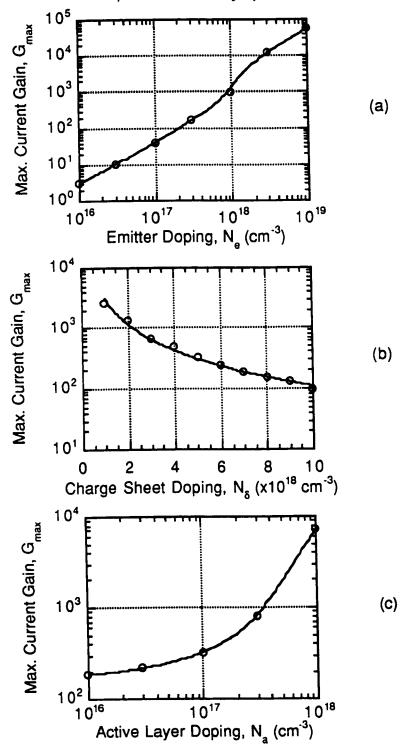

| Figure 4.9:  | Maximum current gain of the BICFET as a function of the a) emitter, b) charge sheet and c) active layer doping                                                                                        | . 95 |

| Figure 4.10: | $J_a$ - $V_{ae}$ characteristic of the BICPT with $\Phi$ as the parametric variable ( $\Phi = 0$ to $1000$ cm <sup>-2</sup> in $100$ cm <sup>-2</sup> increments)                                     | . 97 |

| Figure 4.11: | $V_{ei}$ and $V_{ai}$ as a function of $V_{ae}$ for $\Phi = 100$ cm <sup>-2</sup>                                                                        | . 97 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 5.1:  | Schematic cross-sectional view of a 4-terminal n-channel InGaAsP-InP based inversion channel technology (ICT) device                                     | .101 |

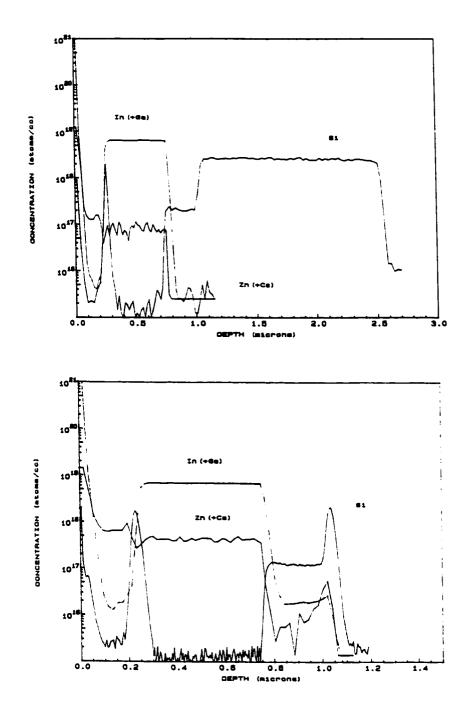

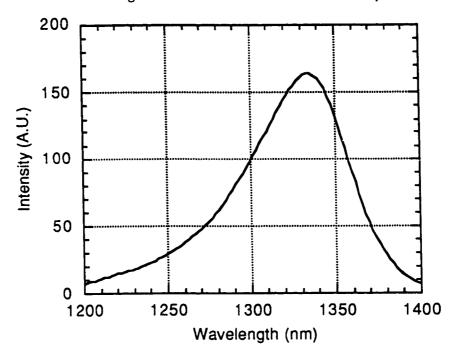

| Figure 5.2:  | Secondary ion mass spectroscopy (SIMS) depth profile of structures a) S1601 and b) S1602                                                                 | .102 |

| Figure 5.2:  | SIMS depth profiles of structures c) S1603 and d) S1604                                                                                                  | 103  |

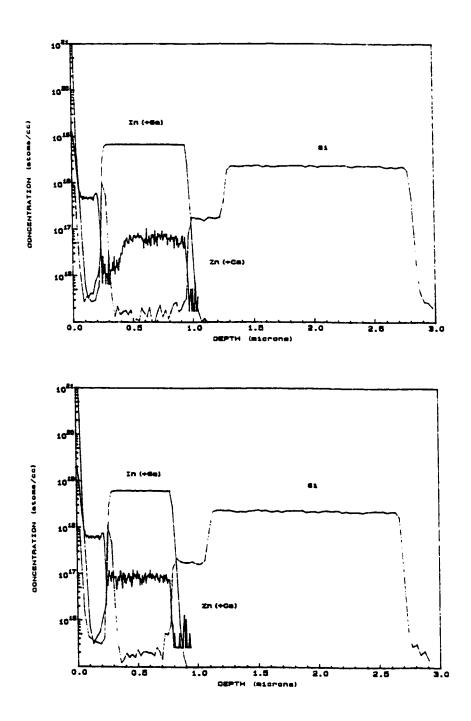

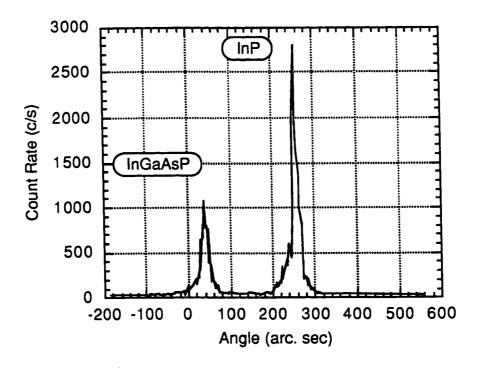

| Figure 5.3:  | Photoluminescence spectra of the InGaAsP ( $\lambda$ = 1.3 $\mu$ m) active layer of structure S1603                                                      | 104  |

| Figure 5.4:  | Double crystal x-ray diffraction spectra of structure S1603                                                                                              | 104  |

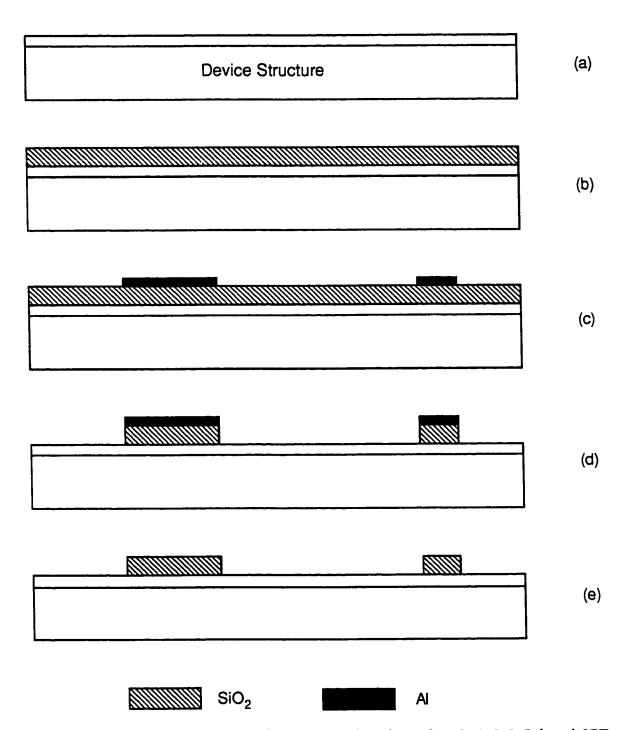

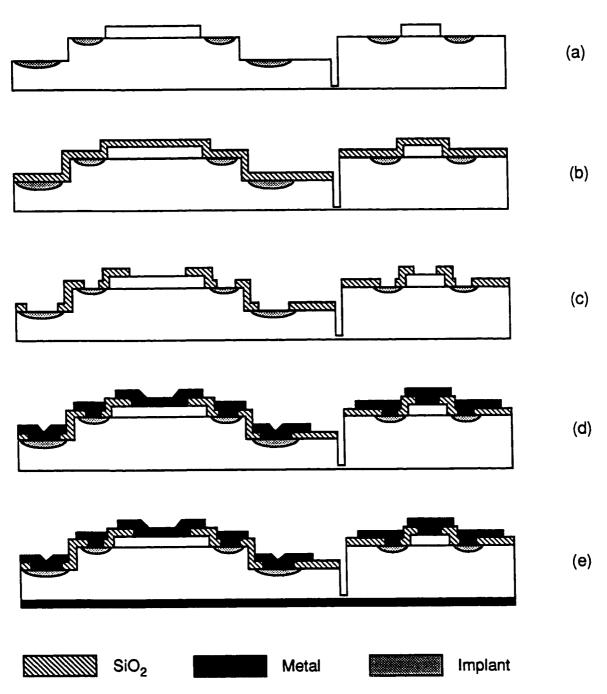

| Figure 5.5:  | Fabrication sequence for 4-terminal n-channel InGaAsP-InP based ICT devices. Mask levels: (c) MES1                                                       | 108  |

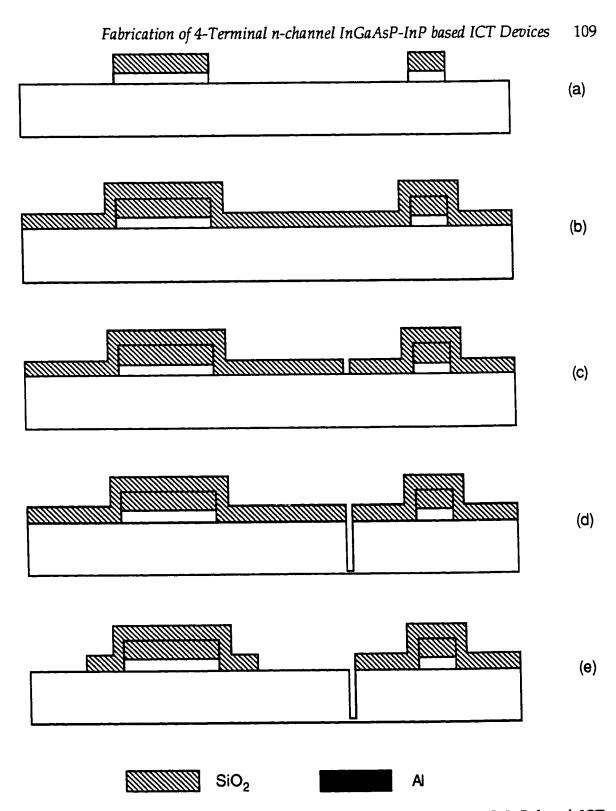

| Figure 5.6:  | Fabrication sequence for 4-terminal n-channel InGaAsP-InP based ICT devices. Mask levels: (c) ISO, (e) MES2                                              | 109  |

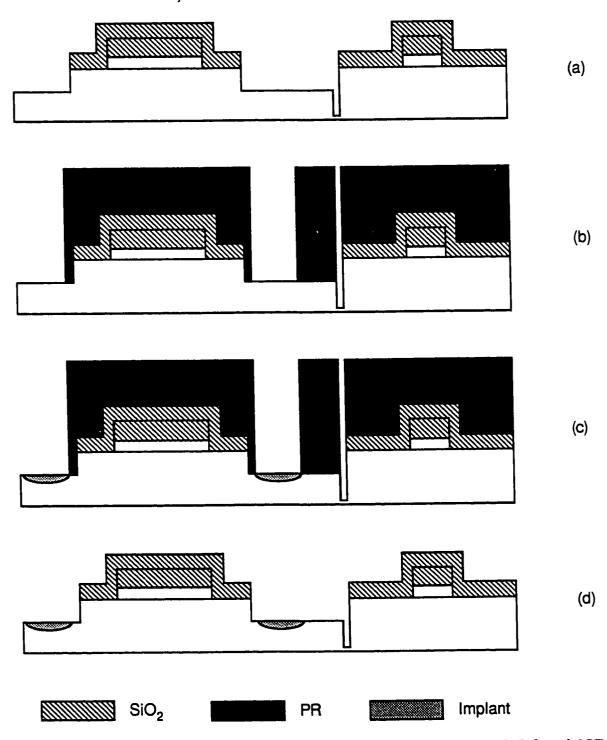

| Figure 5.7:  | Fabrication sequence for 4-terminal n-channel InGaAsP-InP based ICT devices. Mask levels: (b) IIM3                                                       | 111  |

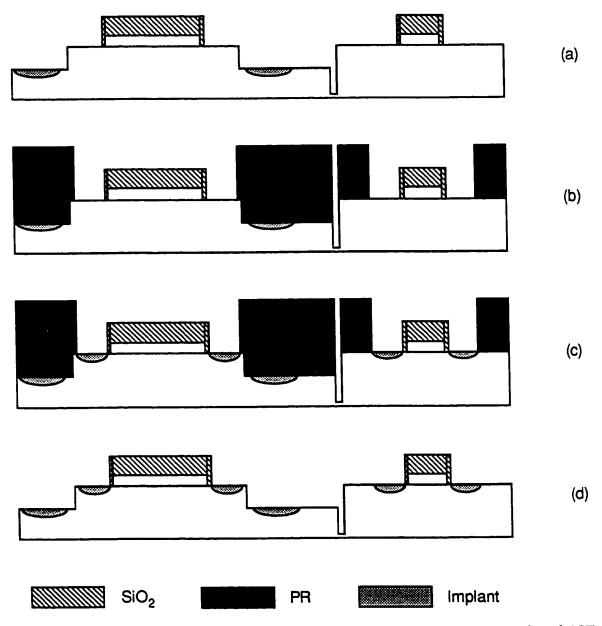

| Figure 5.8:  | Fabrication sequence for 4-terminal n-channel InGaAsP-InP based ICT devices. Mask levels: (b) IIM1                                                       | 112  |

| Figure 5.9:  | Fabrication sequence for 4-terminal ICT devices. Mask levels: (c) VIA, (d) MET1, MET2 and MET3                                                           | 114  |

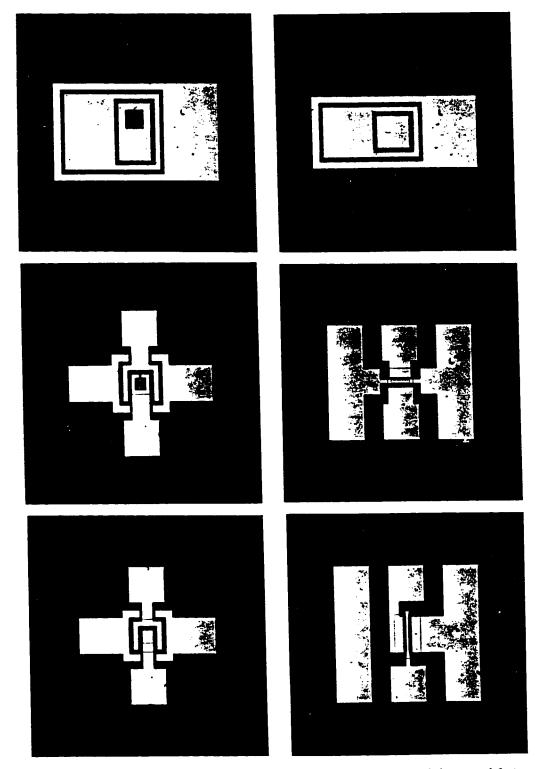

| Figure 5.10: | Photographs showing the top views of the 6 styles of devices fabricated                                                                                  | 116  |

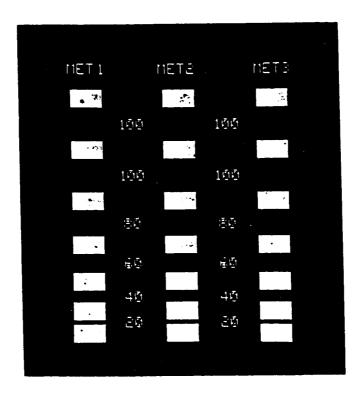

| Figure 5.11: | Photographs of transmission line measurement (TLM) structures fabricated on each wafer for evaluating contact resistance between metal and semiconductor | 117  |

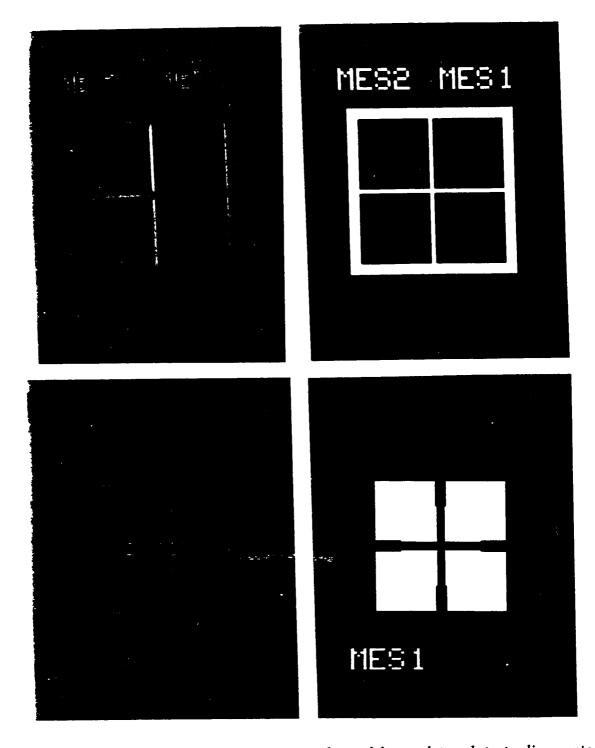

| Figure 5.12: | Photographs of the alignment marks used for mask to substrate alignments. a) and b) show cross pattern, c) and d) show Maltese cross pattern.            | 118  |

| Figure 5.13  | : Photographs of resolution targets included on each mask level to evaluate quality of photolithography                                                  | 120  |

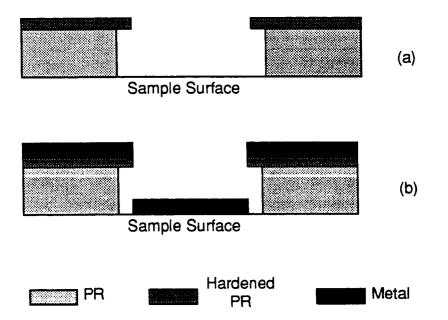

| Figure 5.14: | Schematic representation of a) the undercut photoresist profile and b) metal coverage for the metal lift-off process1                                                                                                                             | 26   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

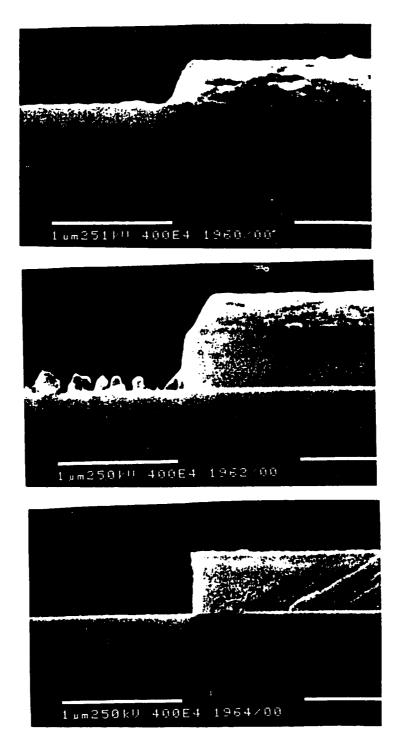

| Figure 5.15: | Scanning electron microscope (SEM) photographs showing intermediate steps in the formation of the self-aligned $SiO_2$ mask a) Al patterns on $SiO_2$ /Substrate b) $CF_4$ reactive ion etch of $SiO_2$ and c) self-aligned $SiO_2$ on substrate. | 28   |

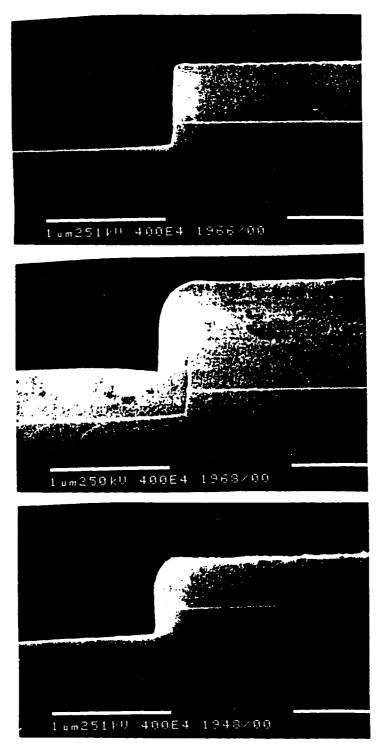

| Figure 5.16: | SEM photographs showing intermediate steps in the formation of $SiO_2$ sidewall passivation a) Mesa 1 with selfaligned $SiO_2$ mask, b) CVD Deposition of $SiO_2$ over structure and c) $CF_4$ reactive ion etch back of $SiO_2$                  | 131  |

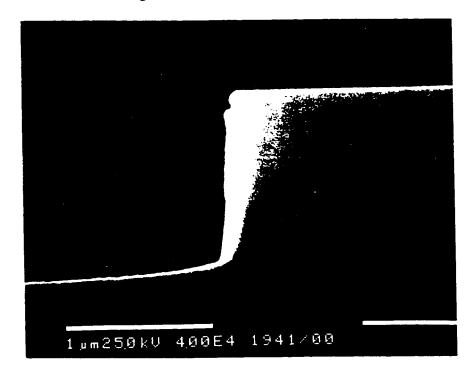

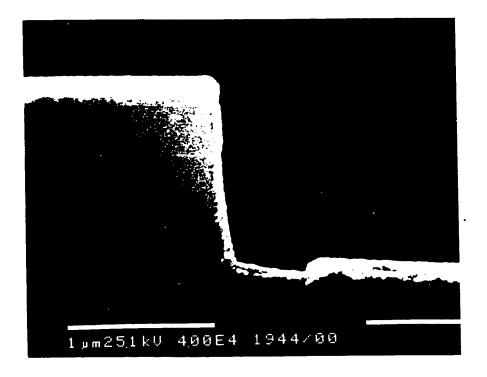

| Figure 5.17: | SEM photograph illustrating the cross-sectional view of a 1 $\mu$ m mesa etched with an CH <sub>4</sub> /H <sub>2</sub> /Ar based plasma                                                                                                          | 134  |

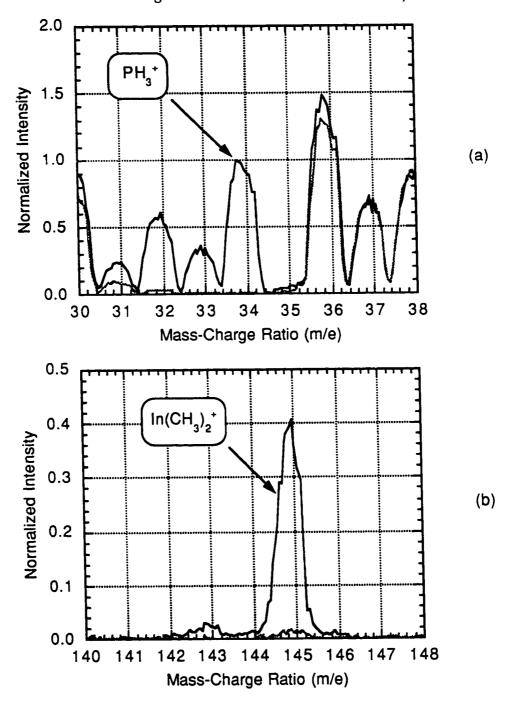

| Figure 5.18: | Mass/charge profiles of InP etched in a CH <sub>4</sub> /H <sub>2</sub> /Ar based plasma. (Light trace shows the background profile)                                                                                                              | 136  |

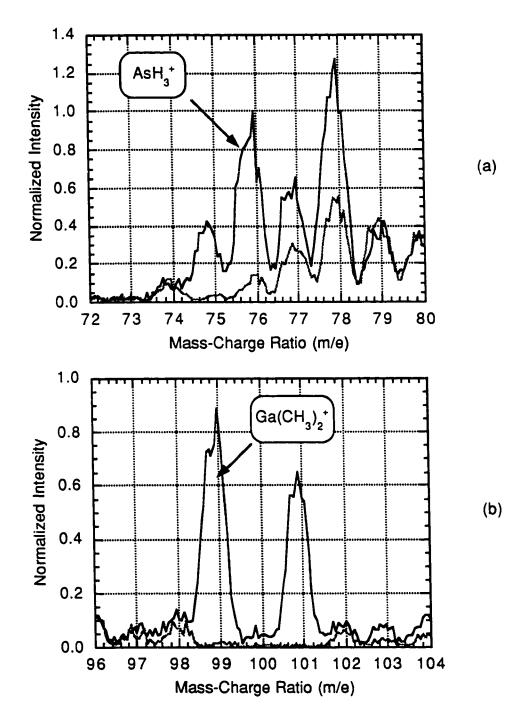

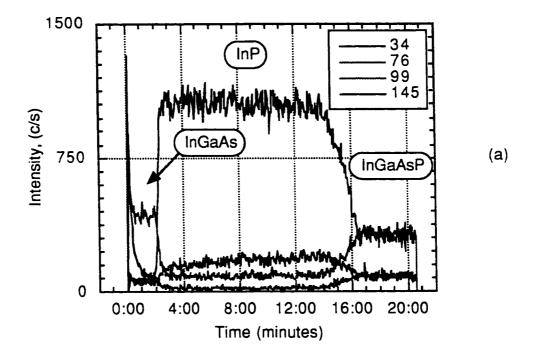

| Figure 5.19: | Mass/charge profiles of GaAs etched in a CH <sub>4</sub> /H <sub>2</sub> /Ar based plasma. (Light trace shows the background profile)                                                                                                             | 137  |

| Figure 5.20: | Time dependent tracking of the volatile species ( $m/e=34$ , 76, 99 and 145) in the plasma during the RIE of S1603                                                                                                                                | 139  |

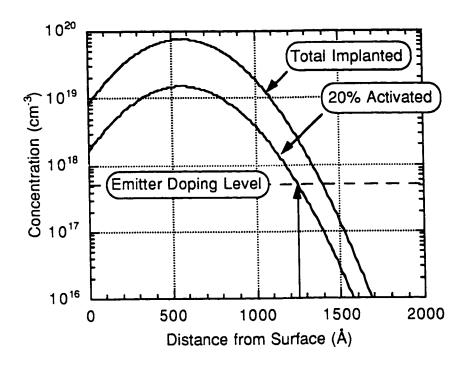

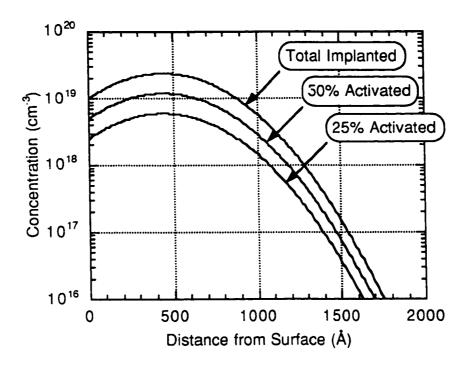

| Figure 5.21: | Calculated dopant distribution for 5x10 <sup>14</sup> cm <sup>-2</sup> Se implanted into InP at 120 keV.                                                                                                                                          | 142  |

| Figure 5.22: | Calculated dopant distribution for 2x10 <sup>14</sup> cm <sup>-2</sup> Mg implanted into InP at 30 keV                                                                                                                                            | .143 |

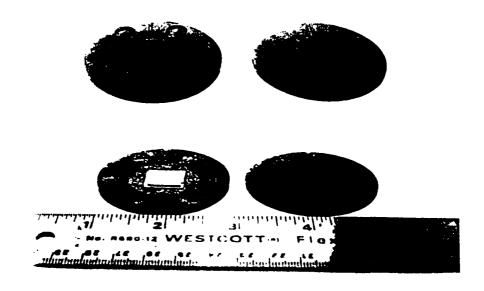

| Figure 5.23: | Photograph showing the graphite boat used for annealing.  a) empty, b) with sample and crushed InP and c) in annealing chamber.                                                                                                                   | .145 |

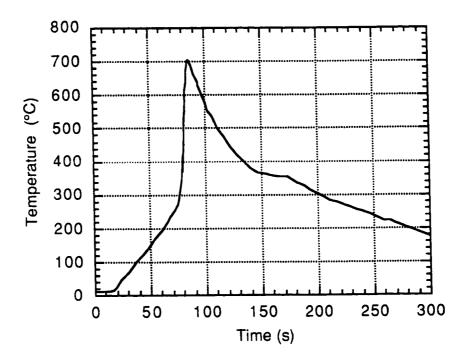

| Figure 5.24: | Annealing temperature profile used for ion implant activation. The annealing was performed in a rapid thermal annealer (RTA)                                                                                                                      | .147 |

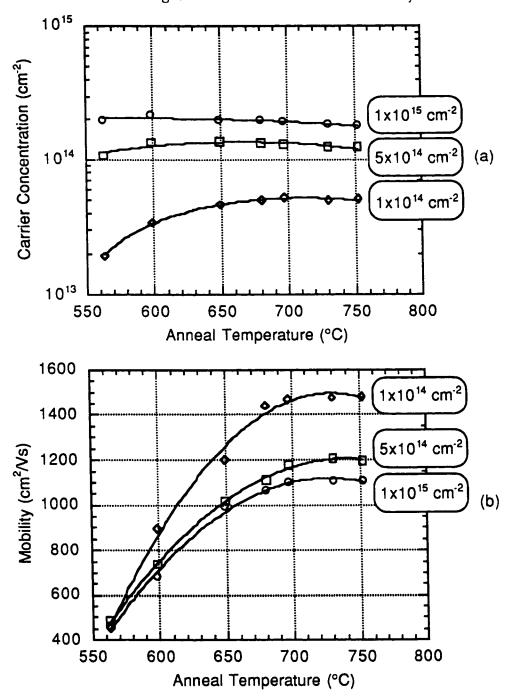

| Figure 5.25  | : a) Carrier concentration and b) mobility as a function of annealing temperature for Se implanted SI:InP. Samples were subjected to 1 second anneal                                                                                              | 148  |

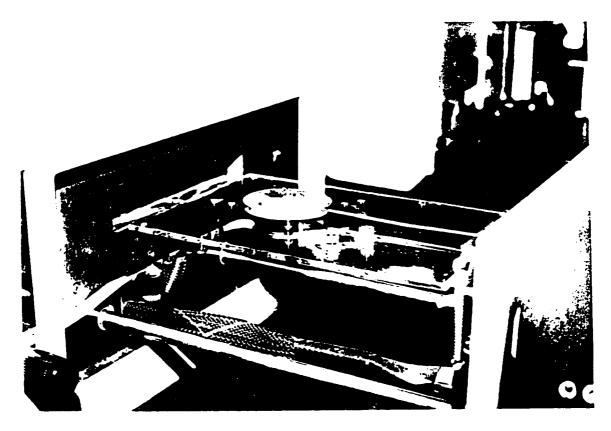

| Figure 5.26: | Photography of the tilt stage used for topside metallization of the samples. Stage a) at 0 degrees and b) tilted at 30 degrees                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.27: | SEM photography showing the cross-sectional view of an RIE sample subject to topside metallization with a tilt stage                                                                                                                                                                                                                                                                                                                                                                                                        |

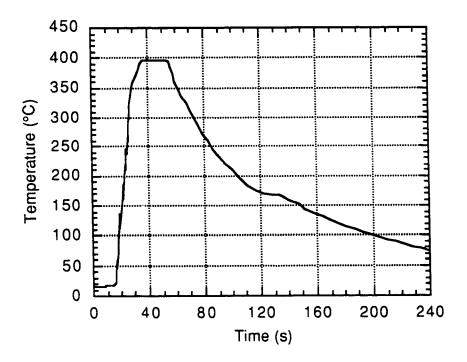

| Figure 5.28: | Annealing temperature profile used for ohmic contact formation. The annealing was performed in a rapid thermal annealer (RTA)                                                                                                                                                                                                                                                                                                                                                                                               |

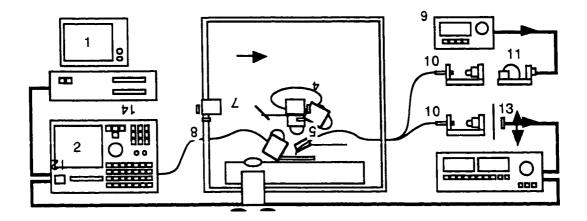

| Figure 6.1:  | Schematic representation of the experimental apparatus for electrical and optical characterization of ICT devices. 1) Microcomputer, 2) Semiconductor parameter analyzer, 3) Probe station enclosure, 4) Sample stage, 5) Electrical probe with co-axial cable connection, 6) Microscope, 7) Device under test, 8) Optical probe with optical fibre connection, 9) Laser diode driver, 10) Optical fibre coupler, 11) Laser diode and mounting, 12) Mechanical chopper, 13) InGaAs photodetector, and 14) Lock-in amplifier |

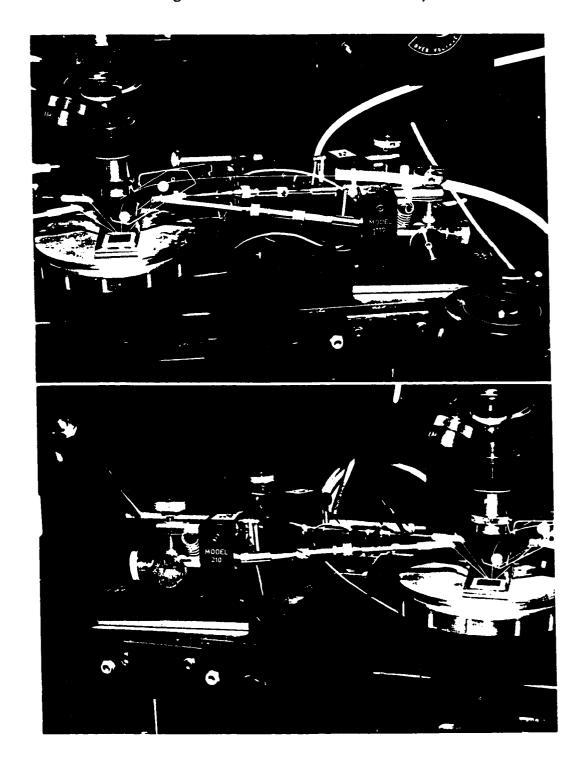

| Figure 6.2:  | Photograph of a) an xyz-manipulator modified to accommodate an optical fibre and b) a standard xyz-manipulator with tungsten probe                                                                                                                                                                                                                                                                                                                                                                                          |

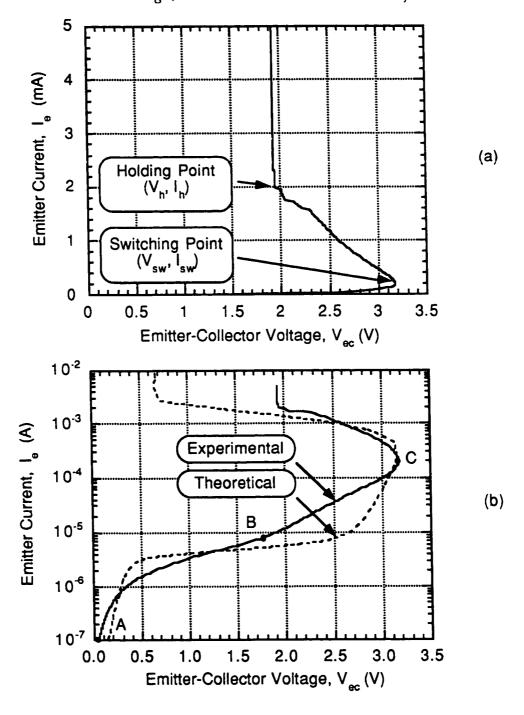

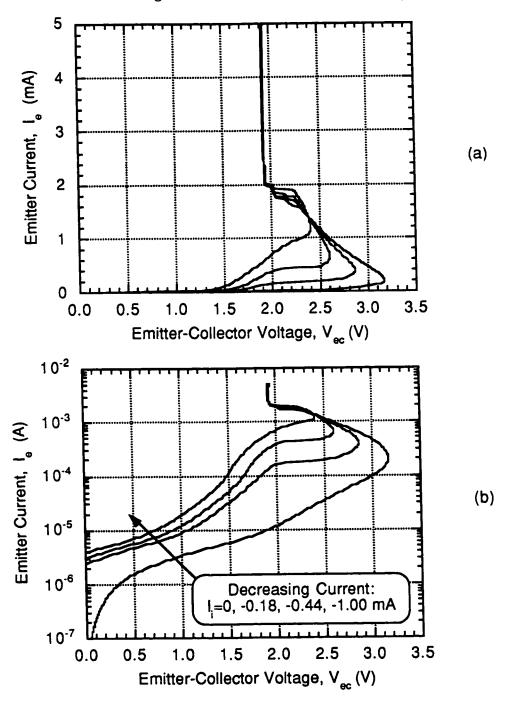

| Figure 6.3:  | Dark current-voltage (I-V) characteristic of an $80 \times 80 \ \mu\text{m}^2$ DOES device measured with a a) linear and b) logarithmic sweep of I <sub>e</sub> . Dotted I-V characteristic was generated by the model of Chap. 2 (see Fig. 2.7).                                                                                                                                                                                                                                                                           |

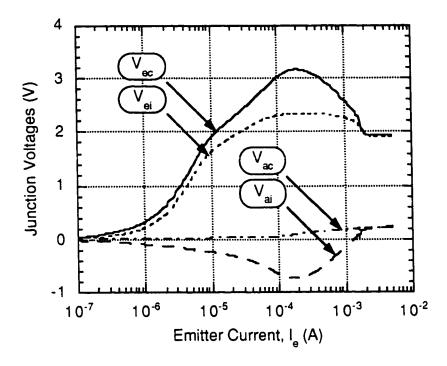

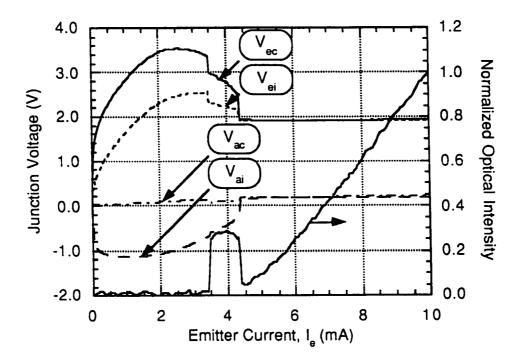

| Figure 6.4:  | Voltage across e-i, a-i and a-c junctions as a function of the emitter current166                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 6.5:  | Schematic cross-section of the DOES device highlighting the parallel conduction paths which exist between the emitter and inversion-channel contacts. Path A: pn-junction device characteristic, path B: pnpn-device characteristic                                                                                                                                                                                                                                                                                         |

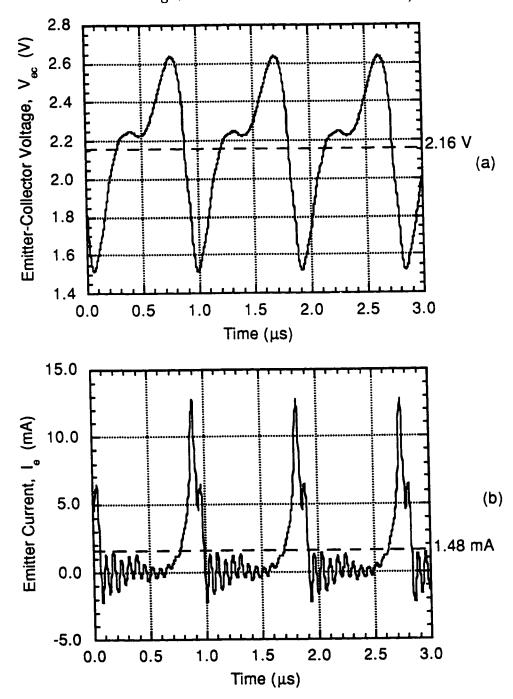

| Figure 6.6:  | Time dependent a) voltage and b) current waveforms of the DOES device biased in the NDR regime of operation. (DC bias applied: $L_1 = 1.50 \text{ mA}$ , $V_{CR} = 2.24 \text{ V}$ )                                                                                                                                                                                                                                                                                                                                        |

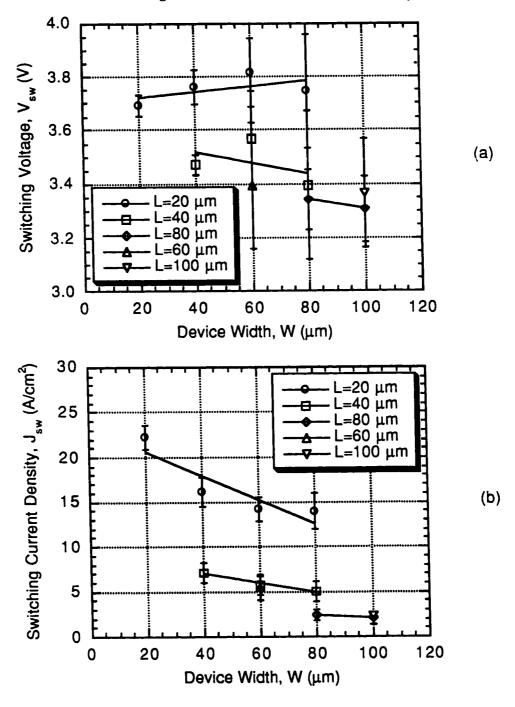

| Figure 6.7:  | a) Switching voltage and b) switching current density of the DOES as a function of device width (W) and device length (L)                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.8:  | a) Linear and b) logarithmic I-V characteristics of the DOES device with the inversion channel current as the parametric variable            |

| Figure 6.9:  | Voltage across the e-i, a-i and a-c junctions as a function of $I_e$ for $I_i$ = a) 0 $\mu$ A, b) -180 $\mu$ A and c) -440 $\mu$ A           |

| Figure 6.10: | a) Linear and b) logarithmic I-V characteristic the DOES device with active layer current as the parametric variable                         |

| Figure 6.11: | Voltage across the e-i, a-i and a-c junction as a function of $I_e$ for $I_a$ = a) 0 $\mu$ A, b) 0.5 mA and c) 3.0 mA178                     |

| Figure 6.12: | Switching voltage as a function of inversion channel and active layer current. Summary of Figs. 6.8 and 6.10179                              |

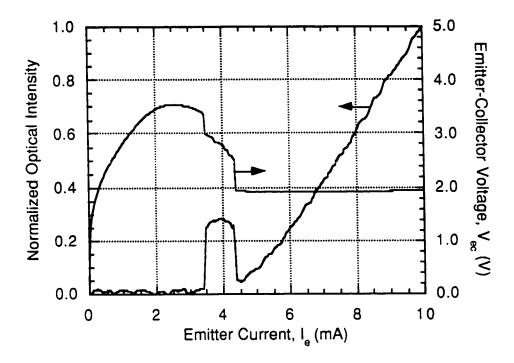

| Figure 6.13: | Light-current (L-I) characteristic of the DOES. Superimposed is the I-V characteristic of the device181                                      |

| Figure 6.14: | Voltage across the e-i, a-i and a-c junctions and the optical emission from the device as a function of $I_e$ 182                            |

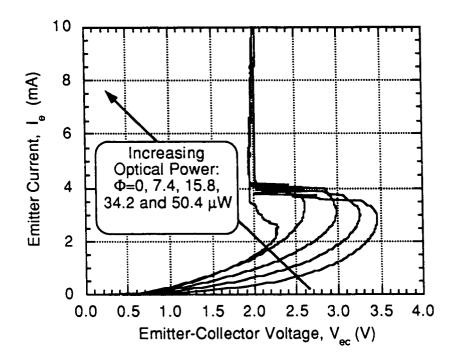

| Figure 6.15: | Linear I-V characteristic of the DOES device with incident optical power ( $\Phi$ ) at $\lambda$ = 1.3 $\mu$ m as the parametric variable183 |

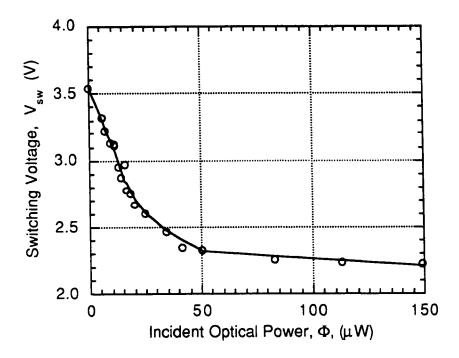

| Figure 6.16: | Switching voltage as a function of the incident optical power, $\Phi$ ( $\lambda$ = 1.3 $\mu$ m)                                             |

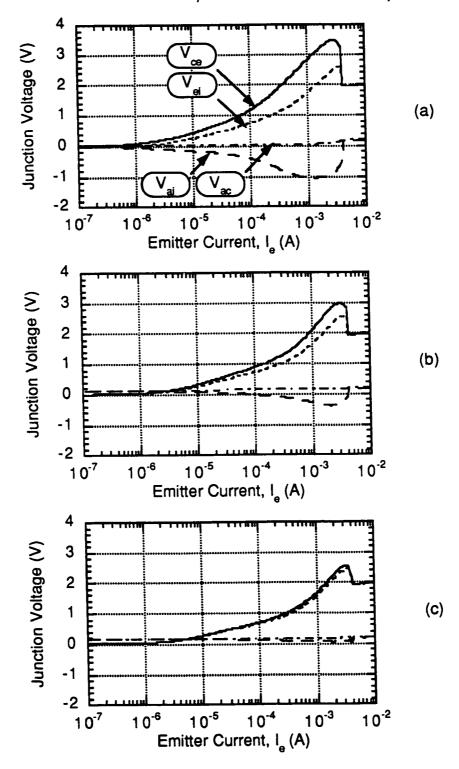

| Figure 6.17: | Voltages across the e-i, a-i and a-c junctions as a function of $I_e$ with $\Phi$ = a) 0 $\mu$ W, b) 7.4 $\mu$ W and c) 34.2 $\mu$ W185      |

| Figure 7.1:  | The input characteristics ( $I_g$ - $V_{gs}$ ) of the 6 x 100 $\mu$ m <sup>2</sup> HFET189                                                   |

| Figure 7.2:  | The output characteristics ( $I_d$ - $V_{ds}$ ) of the HFET with $V_{gs}$ as the parametric variable191                                      |

| Figure 7.3:  | Gate leakage current ( $I_g$ ) as a function of $V_{ds}$ for $V_{gs} = 2 V$ 192                                                              |

| Figure 7.4:  | Output resistance of the HFET as a function of V <sub>ds</sub> with V <sub>ds</sub> as the parametric variable194                            |

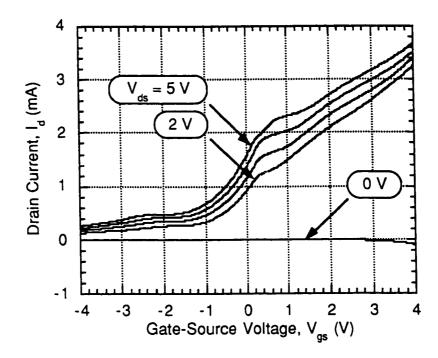

| Figure 7.5:  | Transfer characteristic ( $I_d$ - $V_{gs}$ ) with $V_{ds}$ as the parametric variable                                                                             | .195 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 7.6:  | Gate leakage current of the HFET as a function of $V_{gs}$ for $V_{ds} = 2 V$                                                                                     | 196  |

| Figure 7.7:  | Normalized transconductance of the HFET as a function of $V_{\text{gs}}$ with $V_{\text{ds}}$ as the parametric variable.                                         | 198  |

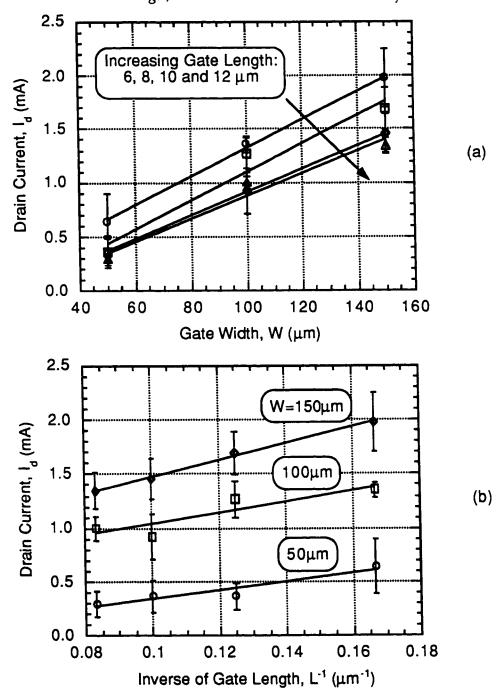

| Figure 7.8:  | Output characteristics ( $I_d$ - $V_{ds}$ ) of the HFET with a) gate width and b) gate length as the parametric variable. The HFETs were biased at $V_{gs}$ = 0 V | 201  |

| Figure 7.9:  | a) Saturation drain current as a function of gate width with gate length as the parametric variable                                                               | 202  |

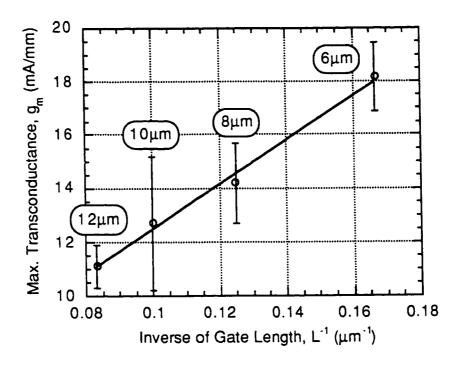

| Figure 7.10: | Effect of gate length (L) on the maximum normalized transconductance of the HFET. The devices were biased with $V_{ds} = 1.5 \text{ V}$ .                         | 203  |

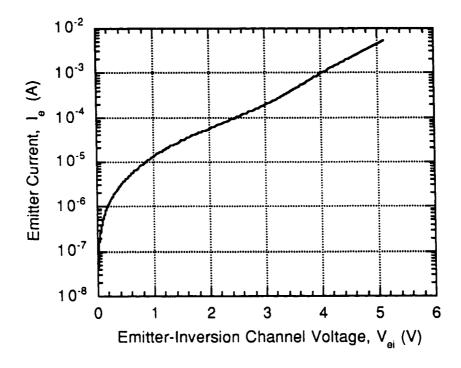

| Figure 8.1:  | Input current-voltage characteristics (I <sub>e</sub> -V <sub>ei</sub> ) characteristics of the BICFET                                                            | 207  |

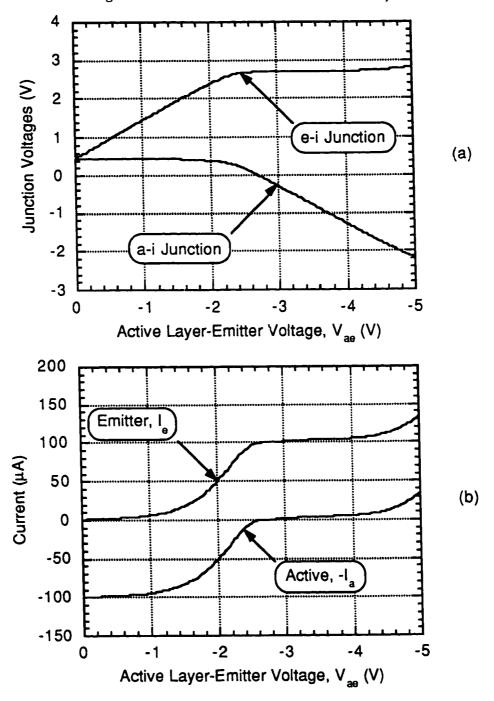

| Figure 8.2:  | a) $V_{ei}$ and $V_{ai}$ , and b) $I_{e}$ and $I_{a}$ as a function of $V_{ae}$ for $I_{i}$ = -100 $\mu A$ .                                                      | 208  |

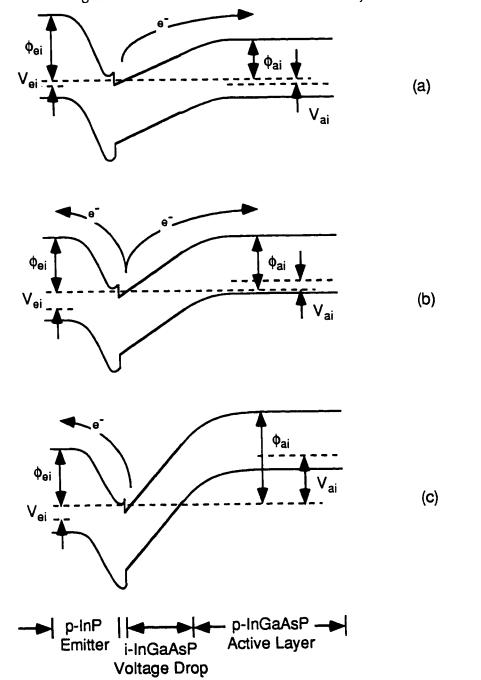

| Figure 8.3:  | Energy band representation of the BICFET under a) low $V_{ae}$ bias, b) moderate $V_{ae}$ bias and c) high $V_{ae}$ bias                                          | 210  |

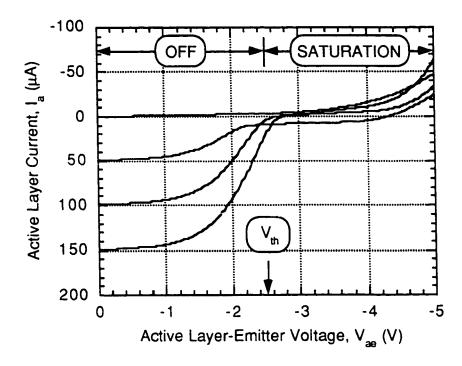

| Figure 8.4:  | Output I <sub>a</sub> -V <sub>ae</sub> characteristic of the BICFET with I <sub>i</sub> as the parametric variable                                                | 211  |

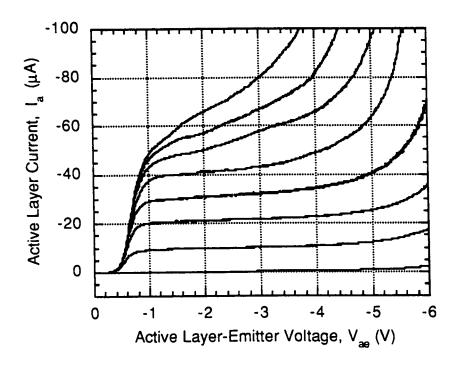

| Figure 8.5:  | Output $I_a$ - $V_{ae}$ characteristic of the BICPT with optical injection ( $\Phi$ ) as the parametric variable                                                  | 213  |

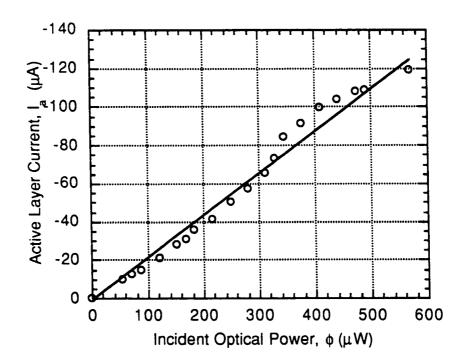

| Figure 8.6:  | $I_a$ as a function of $\Phi$ ( $\lambda$ = 1.3 $\mu$ m) for the BICPT                                                                                            | 215  |

### LIST OF TABLES

| Table 1.1: Transmission bandwidth requirements for various forms of media [2]                                                      | 4   |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1.2: Transmission capacity of various communication systems [3]                                                              | 4   |

| Table 2.1: Device structure used in modeling of the DOES                                                                           | 40  |

| Table 3.1: Device structure used in modeling of the HFET                                                                           | 73  |

| Table 4.1: Device structure used in modeling of the BICFET and BICPT                                                               | 91  |

| Table 5.1: Description, composition, thickness and doping concentrations of the layers in structures S1601, S1602, S1603 and S1604 | 105 |

| Table 5.2: Summary of photoluminescence and double crystal x-ray diffraction for structures S1601, S1602, S1603 and S1604          | 106 |

| Table 5.3: Specification of each mask level in the self-aligned 4-terminal ICT mask set                                            | 119 |

| Table 5.4: Process parameters for O <sub>2</sub> based plasma stripping of ion-implantation hardened photoresist                   | 125 |

| Table 5.5: Process parameters for chemical vapour deposition of SiO <sub>2</sub> used in the self-align mask process               | 129 |

| Table 5.6: Process parameters for CF <sub>4</sub> based RIE of SiO <sub>2</sub>                                                    | 129 |

| Table 5.7: Process parameters for CH <sub>4</sub> /H <sub>2</sub> /Ar based ECR-RIE of III-V compound.                             | 133 |

| Table 5.8: Process parameters for the removal of polymer with an O <sub>2</sub> based plasma                                       | 135 |

| Table 5.9:  | Process parameters for QMS optimized for maximum sensitivity for m/e=34                                                                                          | 138 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 5:10: | Process parameters for cleaning of the ECR-RIE chamber with 1) $O_2$ , 2) Ar and 3) Ar/ $H_2$ based plasmas                                                      | 140 |

| Table 5.11: | Range and lateral straggle for Se and Mg in InP and Photoresist.                                                                                                 | 144 |

| Table 6.1:  | Simplified device structures used in this project. See Table 5.1 for complete device structures                                                                  | 170 |

| Table 6.2:  | Influence of device structure on the switching voltage and switching current                                                                                     | 170 |

| Table 7.1:  | Simplified device structural parameters of the four HFET devices. See Table 5.1 for complete device structural parameters.                                       | 199 |

| Table 7.2:  | Influence of device structure on the threshold voltage $(V_t)$ , maximum transconductance $(g_{m,max})$ and saturation drain-source current $(I_d)$ of the HFETs | 199 |

### **CHAPTER 1**

### **INTRODUCTION**

### 1.1 TECHNOLOGICAL TRENDS AND DRIVING FORCES

The transition of our society from the industrial age to the information age began to take shape in the 1980's. This new age was brought about by the merger of telecommunication, microelectronic and microcomputer technologies to form information systems. Information systems are networks that provide a forum for electronic exchange of information. These networks rely on telecommunications for electronic transport of information, and microcomputers to source and process the information. The shift towards electronic distribution of information allows it to be gathered quickly and processed to the requirements of the user. This convenience and flexibility has fueled the demand for information systems.

Early information systems were used by the banking industry in the form of national networks to connect the head office with its branches. This allowed very quick, efficient and reliable exchange of information between geographically separated offices. The automated teller machines (ATM) allowed banking customers to experience the information age by allowing deposits, cash withdrawals, bill payments and account updates at numerous convenient

locations twenty-four hours of the day. Automated debit machines (ADM) are a further advancement of electronic banking. These machines, available at many retail stores, allow electronic exchange of money between the consumer, retailer and financial institution to take place within seconds.

Electronic access to national and international sources of information is available through the internet on the world-wide-web (WWW). Access to the web is easily accomplished by using a WWW browser on a personal computer. These sources of information are diverse in content and cover a wide range of topics including economics, politics, social issues, careers, health, weather and entertainment. This information is presented in multi-media format incorporating interactive data, audio and video. Public acceptance of information systems has also fueled the introduction of new video-based communication services including videophones, interactive video, switched video-on-demand and enhanced pay-per-view.

The information age offers widespread availability of multi-media sources made possible by information systems. This has been and will be instrumental in changing the structure of our society and economies. Information systems will form the backbone of society and also serve as the driving force for change in this era just as manufacturing did for the industrial age [1].

The vision for the information systems of the future is that of humans and machines exchanging information in a simple, reliable, secure and cost-effective manner at any time, in any place, using a combination of voice, video and data. This vision necessitates the evolution towards high speed microelectronics, powerful multi-media based microcomputer systems and high-bandwidth telecommunication systems.

### 1.2 TELECOMMUNICATION SYSTEMS

The information age has forced telecommunication systems to evolve from systems designed and optimized for voice to systems for multi-media: data, voice and video. Table 1.1 shows that there is, at least, a 100 times increase in bandwidth for active connections for real-time full-motion video compared with digitized voice. It is estimated that a metropolitan area with a population of 10 million requires an aggregate capacity of 1.5 Tb/s to support multimedia telecommunication [2].

Table 1.1 and 1.2 show that the large bandwidths required for multi-media transmission have limited twisted wire-pair and co-axial transmission systems to short-haul applications. These include intra-building networks or home-to-local switch networks. The enormous transmission capacity required between switches for trunking and distribution can only be satisfied by optical transmission. Optical transmission systems have a potential bandwidth of 10,000 GHz\* which can transported without repeaters over large distances with the use of Er3+-doped fibre amplifiers [4,5]. It is this apparently limitless transmission capacity that allows optical transmission systems to meet the present and future transmission requirements of the information age.

Although it is clear that optical transmission will become more important in telecommunications systems, how such systems are to be implemented and what form they will take is still a hotly debated issue. Much research in hardware and software is required to develop the systems of tomorrow and to exploit the large bandwidth potential of optical transmission.

Optical bandwidth for a 100 nm transmission window centered at  $\lambda = 1.55 \, \mu m$ .

Media Transmission Bandwidth Required

Voice 16–64 kb/s

Video (VCR Quality) 1.5 Mb/s

Video (NTSC Quality) 3–4 Mb/s

High Definition TV 20–40 Mb/s

**Table 1.1:** Transmission bandwidth requirements for various forms of media [2].

Table 1.2: Transmission capacity of various communication systems [3].

| Transmission System                      | Transmission Capacity |

|------------------------------------------|-----------------------|

| Twisted Wire Pair                        | 3 Mb/s·km             |

| Co-axial Fibre Optic (1st Generation)    | 270 Mb/s·km           |

|                                          | 1–3 Gb/s·km           |

| Fibre Optic (2 <sup>nd</sup> Generation) | 3–100 Gb/s·km         |

| Fibre Optic (3 <sup>rd</sup> Generation) | 100–1,000 Gb/s·km     |

| Fibre Optic (Current)                    | 10,000 Gb/s·km        |

### 1.3 OPTICAL COMMUNICATION SYSTEMS

Optical communications was made feasible by the advent of the semiconductor laser and the optical fibre [6,7]\*. The first commercial optical communication system introduced in the mid 1970's used AlGaAs-GaAs

<sup>\*</sup> First reports of lasing in semiconductor diode lasers is credited to Hall et al. in 1962 [6] while the first proposal for use of optical fibres for transport of light was made in by Kao and Hockham in 1966 [7].

semiconductor diode lasers as  $\lambda=0.85~\mu m$  optical sources, large core diameter multimode silica optical fibres and Si p-i-n photodetectors. This system had a transmission capacity of 0.1 Gb/s·km. Transmission capacities have increased exponentially with current systems capable of achieving 10,000 Gb/s·km [8].

Increases in the system capacity over the past decade has been achieved by improvement of laser diode and optical fibre technology. Specifically, these efforts have been focused on minimizing attenuation and dispersion, and increasing modulation speed. The four generations of evolution can be readily identified in Fig. 1.1. In the late 1970's there was a shift from large-core multimode fibre to much narrower-core single-mode fibre to eliminate modal dispersion. Also in this time frame, an increase in the transmission wavelength from  $0.85~\mu m$  to  $1.3~\mu m$  was made to exploit the dispersion minima of the silica

Figure 1.1: Progress of optical transmission system capacity [3].

fibre. In the early 1980's, there was another shift in the transmission wavelength to 1.55 μm to exploit the attenuation minima of the optical fibre. This evolution in transmission wavelengths has required a switch from AlGaAs-GaAs to InGaAs-InGaAsP-InP based semiconductor lasers. It has also required a change from Sibased photodetectors to Ge or InGaAs based devices.

Further increases in transmission capacity have been provided by the development of single frequency distributed feedback (DFB) and distributed Bragg reflector (DBR) lasers to further reduce dispersion, and Er<sup>3+</sup>-doped fibre amplifiers to significantly increase the distance between repeaters.

## 1.4 MONOLITHIC OPTOELECTRONIC INTEGRATED CIRCUITS (OEIC)

Monolithic optoelectronic integration is a technology where both electrical devices (laser drivers and photodetector amplifiers) and optical device (lasers and photodetectors) are grown and fabricated on a common substrate. This technology allows devices to be placed physically close to each other and interconnections between devices to be made during the fabrication sequence. The optoelectronic integrated circuit (OEIC) architecture minimizes the parasitic impedances associated with the circuit, allowing for increased operating bandwidth and signal-to-noise ratio. Monolithic fabrication of OEIC's also offers a cost advantage and improved system reliability which results from reduced component counts, and simplification in assembly and testing [9].

Furthermore, OEIC technology can also be adapted for photon transport between devices and circuit elements. This ability to achieve optical interconnectivity between devices and circuits on a wafer scale can overcome the interconnection bottleneck associated with electron transport and allow for a dramatic increase in the operational bandwidth of systems.

The ability to monolithically integrate electronics and optoelectronic components increases the functionality of OEIC's to applications beyond that of transmitters or receivers. With the integration of signal processing and decision making functions, it is possible to design complex application specific OEIC (ASOEIC) for use in residual gas sensing, structural-stress sensing and optical interconnections. These applications typically require a self-contained ASOEIC which is able to generate and detect light as well as perform signal processing.

The advantages offered by OEIC's are fundamentally important to achieving low cost, high functionality, high reliability, large bandwidth information systems. Although monolithic integration is relatively new to optoelectronics, it has been proven in Si-based microelectronics with microprocessors and application specific integrated circuits (ASIC), and in GaAs-based monolithic microwave integrated circuits (MMIC).

The Intelligent Sensing for Innovative Structures project (ISIS) sponsored by the Canadian Federal government is an example of an application that benefits from the use of OEIC's [10]. In this project an ASOEIC is required as part of a system to monitor the structural stresses of buildings. Structural stresses are measured by determining the wavelength shift which results from a deformation of an optical fibre that is embedded in the structure. The task requires an OEIC to generate the coherent light that is passed through the optical fibre and detecting the wavelength shift of the light after it travels through the fibre. This requires the integration of a laser diode and a laser driver, photodetector and amplifier as well as signal processing electronics.

### 1.5 OEIC TECHNOLOGY

Over the past two decades research into optoelectronic integration has been intense and many schemes for achieving monolithic integration have been demonstrated. These efforts at monolithic integration can be divided into three approaches: vertical integration (VI), horizontal integration (HI) and common structure (CS) [11].

In vertical integration, electronic and optoelectronic device structures are grown sequentially on top of each other. Isolation between different devices is achieved with the inclusion of an electrically insulating layer between devices. Contact is then made to the appropriate device layers to form the integrated circuit. This approach is difficult to implement, as it is difficult to grow sufficiently insulating layers to minimize coupling between devices. In addition, the non-planar nature of electrical interconnects between electronic and optoelectronic components causes severe difficulty in fabrication and limits the ultimate complexity that can be achieved.

Horizontal integration, on the other hand, utilizes multiple growth and selective area removal of epitaxy to localize individual device structures on a common substrate. This technique is able to overcome the isolation and planarity difficulties associated with vertical integration; however, it requires a complex set of growth-etch-regrowth sequences in order to achieve integration.

Although the advantages offered by OEIC's are staggering, the difficulties associated with materials and fabrication of very different device structures, photonic and electronic, on a single chip must be overcome for it to become a truly viable technology.

### 1.6 INVERSION CHANNEL TECHNOLOGY FOR OEIC'S

Inversion channel technology (ICT) was introduced by Taylor and Simmons in 1980 as an approach to achieving planar monolithic OEIC's with a single epitaxial growth and a common device fabrication sequence. This technology, in the n-channel manifestation, consists of a p-type wide-bandgap (WBG) emitter, a highly doped n-type WBG charge sheet, a p-type narrow-bandgap (NBG) active layer followed by an n-type WBG collector. The charge sheet is designed to be fully depleted under all bias conditions, and acts as a source of fixed charge which induces an electron inversion channel at the p-p heterointerface. All ICT devices have in common this inversion-channel based device structure.

Intense research effort to demonstrate and develop ICT based on the AlGaAs-GaAs material system has been carried out. This has culminated in the demonstration of an entire family of electronic and optoelectronic devices which include the double-heterostructure optoelectronic switch (DOES) [12–14], the heterojunction field effect transistor (HFET) [15–17], the bipolar inversion-channel field-effect transistor (BICFET) [18–20], the bistable field-effect transistor (BISFET) [19], two- and three-terminal switching lasers (SL) [22–24], field-effect detectors (HFED) [25] and optical modulators [26]. Small and large scale integrated circuits have also been demonstrated with ICT devices. These include transmitter, receiver and repeater circuits [27–31], re-configurable optical interconnections [32–34], logic gates and switches [35], and dynamic memory elements [36,37]. Although most of the work has been in the GaAs-based materials, several ICT devices have also been demonstrated in other material

systems. These include the DOES, HFET and BICFET in the SiGe-Si [38–40] and the two-terminal DOES in the InP based material system [41,42].

Inversion channel technology based on GaAs has been demonstrated as a potentially viable technology for application in  $\lambda$  = 0.85  $\mu$ m systems. The advantages of monolithic optoelectronic integration with ICT make it a promising candidate for implementation in InGaAs-InGaAsP-InP based materials for application in  $\lambda$  = 1.3  $\mu$ m and  $\lambda$  = 1.55  $\mu$ m based optoelectronic systems.

### 1.7 MOTIVATION AND SCOPE

This project was undertaken to demonstrate inversion channel technology for monolithic optoelectronic integration in the InGaAsP-InP material system. This work, being the first attempt, to achieve ICT in the InGaAsP-InP based material system is focused primarily on the development of technology for designing, fabricating and characterizing ICT devices. Four types of ICT devices, the DOES, HFET, BICFET and BICPT, were selected for integration as they are complementary in function and provide the circuit designer with all the basic elements for designing monolithic optoelectronic circuits: optical emitter, optoelectronic switches, bipolar and unipolar transistors and photodetectors.

Inversion channel technology is based on the common substrate (CS) approach to achieving monolithic optoelectronic integration. In this approach, all devices are fabricated from a common device structure with a common fabrication process. Such a technology requires the device structure and device fabrication process to be compatible with all the types of devices to be integrated.

This added constraint of requiring compatibility in device structure and fabrication is a considerable challenge that is overcome in this project.

The electrical and optical characteristics of the DOES, HFET, BICFET and BICPT are highly dependent on the composition and doping of the 5 primary layers that make up the device structure: emitter, charge sheet, undoped, active and collector layer. Fully optimizing for the performance of a particular device type will result in a severe degradation in the performance of other device types. A suitable device structure will trade-off the performance of each device type to ensure functionality of all devices. In this early stage of technology development, the device structure was designed solely to demonstrate operation of each type of device.

To design a suitable device structure requires a thorough understanding of device operation of each device type and also the influence of device structural parameters on the performance of each device. Device models for InGaAsP-InP based DOES, HFET, BICFET and BICPT are developed in Chapters 2–4. These device models identify the influence of device structural parameters on device performance and were used extensively in the design of the four device structures: S1601, S1602, S1603 and S1604. In addition, these device models also provide an understanding of device physics and operation by providing a view of the internal potentials, charge distribution and current flows. This allows for a comparison of experimental measurements with modeling results to verify the operation of the fabricated devices, critically analyze device performance and suggest improvements to the device structure or device fabrication process.

The device fabrication process and process recipes, discussed in Chap. 5, were designed to be compatible for all device types, to achieve self-alignment

between gate/emitter and inversion channel contacts, and to provide for maximum flexibility in electrical and optical characterization. In total, six styles of devices were fabricated with each device having up to four electrical contacts and an optical window. The entire fabrication process requires a total of 11 photolithography steps, 2 ion implantations, 4 metal depositions, 4 wet etch processes, 5 reactive ion etching steps and 2 thermal anneals.

This project represents the most complex set of devices that have been fabricated at the CEMD facilities. Since the CEMD facilities were in an early state of development when this project was undertaken, much effort was spent installing clean-room facilities and fabrication equipment, and developing fabrication recipes for InGaAsP-InP based materials processing. Fabrication technology designed specifically for fabricating InGaAsP-InP ICTs include:

- 1) Photomask set for self-aligned ICT devices

- 2) SiO<sub>2</sub> masking for self-aligned contact formation

- 3) SiO<sub>2</sub> sidewall passivation of mesas for ion-implantation

- 4) High accuracy (to within ± 100 Å) RIE mesa etching with in-situ QMS

- 5) Implant activation for n- and p-implants in InGaAsP-InP

- 6) Metallization over tall vertical mesa structures

More generic and conventional fabrication processing recipes and techniques that also had to be developed include: photolithography for etching, lift-off and ion-implantation, wet etching, CVD oxide deposition and p- and n-type metallizations for InGaAsP-InP based materials.

The ICT devices designed and fabricated provided for up to 4 contact pads for electrical probing and one window for optical probing allowing for detailed experimental characterization of each device. This is important in demonstrating

the functionality of these devices, and understanding their physics and operation.

Detailed experimental characterization of the input, output, transfer characteristics of the DOES, HFET, BICFET and BICPT was performed. Also examined were the internal junction voltages of the devices as a function of the driving bias. Chapters 6–8 also present these operational characteristics for the DOES, HFET, BICFET and BICPT. Comparisons between experimental and modeling results demonstrated that all types of devices were functional. In addition the full electrical and optical characterization of each device provided insight into device physics and operation, and into areas for future optimization of device performance.

The first part of Chap. 9 summarizes this project which involves the development of technology for design, fabrication and characterization of InGaAsP-InP based ICT devices. Through the course of this project many concerns and questions, beyond the scope of this project, were raised. These questions and concerns involve device modeling, structure, fabrication and characterization. The remainder of Chap. 9 attempts to identify the main concerns and proposes possible directions for future work.

#### REFERENCES

- [1] J. Naisbitt, and P. Aburdence, Megatrends 2000: Ten New Directions for the 1990's, Avon Books, New York, New York, 1990.

- [2] S.D. Personick, "Towards Global Information Networking," Proc. IEEE, vol. 81, no. 11, pp. 1549–1557, (1993).

- [3] R. Heidemann, B. Wedding, and G. Veith, "10-GB/s Transmission and Beyond," Proc. IEEE, vol. 81, no. 11, pp. 1558–1567, (1993).

- [4] T. Li, "The Impact of Optical Amplifiers on Long-Distance Lightwave Telecommunications," Proc. IEEE, vol. 81, no. 11, pp. 1586–1579, (1993).

- [5] E. Desurvire, "The Golden Age of Optical Fibre Amplifiers," Physics Today, pp. 20–27, January, (1994).

- [6] R.N. Hall, G.E. Genner, J.D. Kingsley, T.J. Soltys, and R.O. Carlson, "Coherent Light Emission from GaAs Junctions," Phys. Rev. Lett., vol. 9, no. 9, pp. 366–368, (1962).

- [7] K.C. Kao, and G.A. Hockham, "Dielectric Fibre Surface Waveguides for Optical Frequencies," Proc. IEE, vol. 113, no. 7, pp. 1151–1158, (1966).

- [8] N.K. Cheung, "The Infrastructure for Gigabit Computer Networks," IEEE Commn. Magazine, pp. 60–68, April, (1992).

- [9] O. Wada, "Optoelectronic Integration Based on GaAs Material," Opt. Quant. Electron., vol. 20, no. 6, pp. 441–474, (1988).

- [10] The Canadian Network of Centres of Excellence on Intelligent Sensing for Innovative Structures (ISIS Canada), Downsview, Ontario, (1995).

- [11] M. Dagenais, R.F. Leheny, H. Temkin, and P. Bhattacharya, "Applications and Challenges of OEIC Technology: A Report on the 1989 Hilton Head Workshop," J. Lightwave Technol., vol. 8, no. 6, pp. 846–862, (1990).

- [12] G.W. Taylor, J.G. Simmons, A.Y. Cho, and R.S. Mand, "A New Double Heterostructure Optoelectronic Switching Device Using Molecular Beam Epitaxy," J. Appl. Phys, vol. 59, no. 2, pp. 596–600, (1986).

- [13] G.W. Taylor, R.S. Mand, A.Y. Cho, and J.G. Simmons, "Experimental Realization of an N-Channel Double Heterostructure Optoelectronic Switch," Appl. Phys. Lett, vol. 48, no. 20, pp. 1368–1370, (1986).

- [14] G.W. Taylor, R.S. Mand, J.G. Simmons, and A.Y. Cho, "Ledistor–a Three-Terminal Double Heterostructure Optoelectronic Switch," Appl. Phys. Lett., vol. 50, no. 6, pp. 338–340, (1987).

- [15] G.W. Taylor, M.S. Lebby, T.Y. Chang, R.N. Gnall, N. Sauer, B. Tell, and J.G. Simmons, "Very High Transconductance Heterojunction Field-Effect Transistor (HFET)," Electron. Lett., vol. 23, no. 2, pp. 77–79, (1987).

- [16] J.G. Simmons, and G.W. Taylor, "New Heterostructure Junction Field-Effect Transistor (HJFET)," Electron. Lett., vol. 22, pp. 1167–1169, (1986).

- [17] G.W. Taylor, P.A. Kiley, P.A. Evaldsson, P. Cooke, and D.P. Doctor, "Buried Channel Heterojunction Field-Effect Transistor (BCHFET), " Electronic Lett., vol. 28, no. 9, pp. 858–860, (1992).

- [18] K. Matsumoto, Y. Hayashi, N. Hashizume, T. Yao, M. Kato, T. Miyashita, N. Fukuhara, H. Hirashima, and T. Kinosada, "GaAs Inversion-Base Bipolar Transistor (GaAs IBT)," IEEE Trans. Electron Devices, vol. 7, no. 11, pp. 627–628, (1986).

- [19] M.S. Lebby, G.W. Taylor, A. Izabelle, B. Tell, K. Brown-Goebeler, T-.Y. Chang, and J.G. Simmons, "A P-Channel BICFET in the InGaAs-InAlAs Material System," IEEE Electron Device Lett., vol. 9, no. 6, pp. 278–280, (1988).

- [20] G.W. Taylor, P.A. Kiley, A. Izabelle, D.L. Crawford, M.S. Lebby, T.-Y. Chang, B. Tell, K. Brown-Goebeler, and J.G. Simmons, "An N-Channel BICFET in the GaAs/AlGaAs Material System," IEEE Electron Device Lett., vol. 10, no. 2, pp. 88–90, (1989).

- [21] J.J. Ojha, J.G. Simmons, R.S. Mand, A.J. SpringThorpe, "Realization of an N-Channel GaAs/AlGaAs Bistable Field-Effect Transistor (BISFET)," IEEE Electron Device Lett., vol. 14, no. 8, pp. 385–387, (1993).

- [22] G.W. Taylor, and P. Cooke, "Double-Heterostructure Optoelectronic Switch as a Single Quantum Well Laser, "Appl. Phys. Lett., vol. 56, no. 14, pp. 1308–1310, (1990).

- [23] G.W. Taylor, P.R. Claisse, and P. Cooke, "Demonstration of a Heterostructure Field-Effect Laser for Optoelectronic Integration," Appl. Phys. Lett., vol. 58, no. 7, pp. 666–668, (1991).

- [24] T. Numai, M. Sugimoto, I. Ogura, H. Kosaka, and K. Kasahara, "Surface-Emitting Laser Operation in Vertical-to-Surface Transmission Electrophotonic Devices with a Vertical Cavity," Appl. Phys. Lett., vol. 58, no. 12, pp. 1250–1252, (1991).

- [25] S.K. Sargood, G.W. Taylor, T. Vang, P. Cooke, C.A. Burrus, B.Tell, and K. Brown-Goebeler, "Operation of a Single Quantum Well Heterojunction Field-Effect Photodetector," Appl. Phys. Lett., vol. 59, no. 16, pp. 1987–1989, (1991).

- [26] G.W. Taylor, T. Vang, S.K. Sargood, P. Cooke, and P. Claisse, "Demonstration of the Heterostructure Field-Effect Transistor as an Optical Modulator," Appl. Phys. Lett., vol. 59, no. 9, pp. 1031–1033, (1991).

- [27] P.W. Cooke, P.A. Evaldsson, G.W. Taylor, and B. Tell, "Strained Multi-Quantum Well Double Heterostructure Optoelectronic Switch and Associated Heterojunction FET," Electron. Lett., vol. 27, no. 12, pp. 1095-1097, (1991).

- [28] P.A. Evaldsson, G.W. Taylor, P. Cooke, P.R. Claisse, C.A. Burrus, and B. Tell, "Small Signal and Continuous Wave Operation of the Lateral Current Injection Heterostructure Field-Effect Laser," Appl. Phys. Lett. vol. 60, no. 14, pp. 1697–1699, (1992).

- [29] P. Cooke, P.A. Evaldsson, and G.W. Taylor, "Demonstration of the n-Channel Vertical-Cavity Double-Heterostructure Optoelectronic Switching Laser and Heterostructure Field-Effect Transistor," IEEE Photon. Technol. Lett., vol. 4, no. 6, pp. 605–608, (1992).

- [30] P.A. Evaldsson, T.A. Vang, G.W. Taylor, S.K. Sargood, P.A. Kiley, and P. Cooke, "Monolithic Integration of Lasers with FET and Bipolar Transistors in Inversion Channel Technology," Electron. Lett., vol. 129, no. 1, pp. 60–62, (1993).

- [31] P.A. Kiley, G.W. Taylor, D.P. Doctor, P.R. Claisse, T. Vang, P.A. Evaldsson, S.K. Sargood, S. Daryanai, P. Cooke, and K.F. Brown-Goebeler, "Demonstration of a Smart Pixel Using DOES Device Technology," IEE Proc.-I, vol. 139, no. 3, pp. 208–214, (1992).

- [32] K. Kashara, Y. Tashiro, and R. Lang, "Vertical to Surface Transmission Electrophotonic Device for Application to Massively Parallel Optical Interconnections and Optical Computing Systems," Tech. Dig. Adv. Proc. Character. Technol., Tokyo, pp. 271–281, Oct. 4–6, (1989).

- [33] K. Kasahara, Y. Tashiro, I. Ogura, M. Sugimoto, S. Kawai, and K. Kubota, "A Vertical to Surface Transmission Electrophotonic Device for the Application of Optical Interconnections and Processing," Conf. Solid State Dev. Mater., Tokyo, Extended Abstract, pp. 433–436, Aug. 28–30, (1989).

- [34] I. Ogura, Y. Tashiro, S. Kawai, K. Yamada, M. Sugimoto, K. Kubota, and K.Kasahara, "Reconfigurable Optical Interconnections using a Two-Dimensional Vertical to Surface Transmission Electro-Photonic Device Array," Appl. Phys. Lett., vol. 58, pp. 1250–1252, (1990).

- [35] S. Kawai, Y. Tashiro, H. Ichinose, K. Kashara, and K. Kubota, "Cascade Connected Optical Logic Processor Using 2-Dimensional Electro-Photonic Devices," Opt. Comput. Tech. Dig., vol. 9, pp. 193–196, (1989).

- [36] G.W. Taylor, D.L. Crawford, and J.G. Simmons, "Optoelectronic Dynamic Random Access Memory Cell Utilizing a three-Terminal N-Channel Self-Alighned Double Heterostructure Optoelectronic Switch," Appl. Phys. Lett., vol. 54, no. 6, pp. 543–545, (1988).

- [37] K. Kasahara, Y. Tashiro, and R. Lang, "Double Heterostructure Opto-Electronic Switch as a Dynamic Memory with Low Power Consumption," Appl. Phys. Lett. vol. 52, pp. 679–681, (1988).

- [38] R.C. Taft, J.D. Plummer, and S.S. Iyer, "Demonstration of a p-Channel BICFET in the Ge<sub>x</sub>Si<sub>1-x</sub>/Si System," IEEE Electron Device Lett., vol. 10, no. 1, pp. 14–16, (1989).

- [39] S.J. Kovacic, J.G. Simmons, K. Song, J.-P. Noel, and D.C. Houghton, "Si/SiGe Digital Optoelectronic Switch," IEEE Electron Device Lett., vol. 12, no. 8, pp. 439–441, (1991).

- [40] S.J. Kovacic, J.G. Simmons, J.-P. Noel, D.C. Houghton, and M. Buchanan, "Inversion-Channel Si/SiGe Heterojunction Field-Effect Transistor," Electron Lett., vol. 28, no. 24, pp. 2234–2235, (1992).

- [41] S.J. Kovacic, B.J. Robinson, J.G. Simmons, and D.A. Thompson, "InP/InGaAsP Double Heterostructure Optoelectronic Switch," IEEE Electron Device Lett., vol. 14, no. 2, pp. 54–56, (1993).

- J.H. Swoger, C. Qiu, J.G. Simmons, D.A. Thompson, F. Shepherd, D. Beckett and M. Cleroux, "Strained Layer (1.5 μm) InP/InGaAsP Lasing Opto-Electronic Switch (LOES)," IEEE Photon. Tech. Lett., vol. 6, no. 8, pp. 927–929, (1994).

# **CHAPTER 2**

# DESCRIPTION AND THEORY OF THE DOES

The double heterostructure optoelectronic switch (DOES) is a device from the ICT family which possesses bistable electrical and optical states. In the ON state, the device has low resistance and emits light. In the OFF state, the device has high resistance and does not emit light. This device can be switched between the ON and OFF states either electrically, optically or with a combination of both electrical and optical inputs. Such operating characteristics make it a potential candidate for application in electrical, optical or optoelectronic switching operations. The DOES device structure is fully compatible with other devices from the ICT family allowing it to be monolithically integrated with devices including the BICFET, HFET and BICPT.

This chapter is an introduction to the 4-terminal n-channel InGaAsP-InP based DOES device. It begins with a presentation of the DOES device structure followed by the development of a model to describe device operation. This semi-analytical model is derived on the basis of charge conservation and current continuity [1]. The model provides a view of the internal potentials, charge distribution and current flows under a variety of biasing conditions including