Algebraic Enhancements for Systolic Arrays

### ALGEBRAIC ENHANCEMENTS FOR SYSTOLIC ARRAYS

$\mathbf{B}\mathbf{Y}$

TREVOR E. POGUE, B.Eng., M.A.Sc.

A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

and the School of Graduate Studies

OF MCMASTER UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

© Copyright by Trevor E. Pogue, December 2024

All Rights Reserved

| Doctor of Philosophy (2024)         |  |

|-------------------------------------|--|

| (Electrical & Computer Engineering) |  |

### McMaster University Hamilton, Ontario, Canada

| TITLE:      | Algebraic Enhancements for Systolic Arrays                                                     |

|-------------|------------------------------------------------------------------------------------------------|

| AUTHOR:     | Trevor E. Pogue<br>B.Eng. (Electrical Engineering),                                            |

|             | M.A.Sc. (Electrical & Computer Engineering),<br>McMaster University, Hamilton, Ontario, Canada |

| SUPERVISOR: | Dr. Nicola Nicolici                                                                            |

NUMBER OF PAGES: xvii, 168

### Abstract

The field of deep learning has seen increasing breakthroughs and commercial adoption in recent years for enabling a wide range of applications including image and speech recognition, multimedia generation, information summarization, and human-like chatbots. This has led to a growing need for hardware that can quickly and efficiently perform deep learning inference, which increasingly requires massive amounts of computational power.

To address this need, recent years have seen many works for optimizing deep learning inference in hardware. Systolic arrays are an efficient class of hardware designs to use as a starting point for this application. However, after hardware-oriented deep learning model optimizations reach their limits, after the known parallelism for executing their compute patterns in hardware is exhausted, and after technology scaling slows to a halt, there is an accelerator wall that limits further improvement on the implementation side.

In this thesis, we contribute to this field through an under-explored direction by presenting new efficient matrix multiplication algorithms and/or their systolic-array hardware architectures that increase performance-per-area by reducing the workload at the algebraic level, and thus by computing the same result from a re-arranged compute pattern requiring fewer or cheaper operations to be performed in hardware. We evaluate our architectures in an end-to-end deep learning accelerator, demonstrating their ability to increase the performance-per-area of hardware accelerators beyond their normal theoretical limits.

### Acknowledgements

I would like to thank and acknowledge all those who contributed to the completion of this thesis. I had a lot of fun producing this work, but it is time to move on now. First of all, I want to express my gratitude to my supervisor, Dr. Nicola Nicolici, who has always been a great mentor both professionally and personally. He provided me with a creative environment and space to think freely, which allowed me to thrive and reach my full potential. I also would like to thank my supervisory committee members, Dr. Sorina Dumitrescu and Dr. Mohamed Hassan, as well as my external examiner Dr. Zeljko Zilic, for their time reviewing my thesis and their advice which improved my work. Despite our in-person time getting cut short from the pandemic, I thank all of the colleagues I have overlapped with during my time at the Computer-Aided Design and Test Research Group at McMaster University, both former and present members. I would also like to thank my family for supporting me along this chapter of my life. Finally, I thank my wife, Michelle Pogue, for her constant support which has played a major role in my success.

# Abbreviations

- ML: Machine Learning.

- **DNN**: Deep Neural Network.

- CNN: Convolutional Neural Network.

GEMM: General Matrix Multiplication.

**CPU**: Central Processing Unit.

GPU: Graphics Processing Unit.

FPGA: Field Programmable Gate Arrays.

ASIC: Application-Specific Integrated Circuit.

TPU: Tensor Processing Unit.

MXU: Matrix Multiplication Unit.

GOPS: Giga Operations per Second.

**PE**: Processing Element.

**DSP**: Digital Signal Processing.

MAC: Multiply-Accumulate.

# Contents

| 1 | Intr | oductio | n                                  | 1  |

|---|------|---------|------------------------------------|----|

|   | 1.1  | Deep l  | Learning                           | 2  |

|   | 1.2  | Hardw   | vare Acceleration                  | 3  |

|   | 1.3  | Efficie | ent Algebraic Algorithms           | 5  |

|   | 1.4  | Contri  | butions and Thesis Organization    | 6  |

| 2 | Bac  | kground | d and Prior Work                   | 9  |

|   | 2.1  | Deep l  | Learning and Matrix Multiplication | 9  |

|   |      | 2.1.1   | Fully-Connected Layers             | 11 |

|   |      | 2.1.2   | Convolutional Layers               | 13 |

|   |      | 2.1.3   | Transformers and Attention Layers  | 16 |

|   |      | 2.1.4   | Commonality                        | 17 |

|   | 2.2  | Deep I  | Learning Hardware Acceleration     | 17 |

|   |      | 2.2.1   | Systolic Arrays                    | 17 |

|   |      | 2.2.2   | Quantization                       | 20 |

|   |      | 2.2.3   | Precision-Scalable Architectures   | 21 |

|   |      | 2.2.4   | Pruning and Sparsity               | 22 |

|   |      | 2.2.5   | Memory Optimizations               | 23 |

|   |      | 2.2.6   | Hardware Architecture Design Automation       | 24 |

|---|------|---------|-----------------------------------------------|----|

|   |      | 2.2.7   | Hardware-Oriented DNN Model Design Automation | 26 |

|   |      | 2.2.8   | Fast Convolution Algorithms                   | 27 |

|   | 2.3  | Efficie | nt Algebraic Algorithms                       | 28 |

|   |      | 2.3.1   | Fast Inner Product (FIP)                      | 29 |

|   |      | 2.3.2   | Karatsuba Scalar Multiplication (KSM)         | 32 |

|   |      | 2.3.3   | Strassen Matrix Multiplication (SMM)          | 37 |

|   | 2.4  | Summ    | ary                                           | 41 |

| 3 | Deej | p Learn | ing Accelerator System Architecture           | 42 |

|   | 3.1  | Overvi  | ew                                            | 43 |

|   | 3.2  | Memo    | ry Subsystem                                  | 45 |

|   | 3.3  | GEMN    | 1 Unit                                        | 48 |

|   | 3.4  | Post-G  | EMM Unit                                      | 49 |

|   | 3.5  | Host A  | access and Accelerator Instructions           | 50 |

|   | 3.6  | Timing  | g Optimizations                               | 51 |

|   |      | 3.6.1   | Memory Subsystem Timing Optimizations         | 51 |

|   |      | 3.6.2   | MXU Timing Optimizations                      | 52 |

|   | 3.7  | Summ    | ary                                           | 54 |

| 4 | Fast | Inner-l | Product Algorithms and Hardware Architectures | 56 |

|   | 4.1  | Free-p  | ipeline Fast Inner Product (FFIP)             | 59 |

|   |      | 4.1.1   | Proof                                         | 60 |

|   |      | 4.1.2   | Deep Learning-Specific Optimizations          | 62 |

|   | 4.2  | Fast In | ner-Product Architectures                     | 62 |

|   |     | 4.2.1    | Definitions                                                          | 62 |

|---|-----|----------|----------------------------------------------------------------------|----|

|   |     | 4.2.2    | Processing Element (PE) Architectures                                | 3  |

|   |     | 4.2.3    | Matrix Multiplication Unit (MXU) Architectures 6                     | 8  |

|   |     | 4.2.4    | Deep Learning-Specific Optimizations                                 | 8  |

|   |     | 4.2.5    | Multiplier Compute Efficiency                                        | '1 |

|   | 4.3 | Result   | s7                                                                   | '4 |

|   |     | 4.3.1    | FFIP Compared to Baseline and FIP                                    | 5  |

|   |     | 4.3.2    | FFIP Compared to the State-of-the-Art on FPGA                        | 7  |

|   | 4.4 | Summ     | ary                                                                  | 4  |

| 5 | Kar | atsuba ] | Matrix Multiplication Algorithm and Hardware Architectures         8 | 6  |

|   | 5.1 | Notatio  | on                                                                   | 37 |

|   | 5.2 | Karats   | uba Matrix Multiplication (KMM)                                      | 9  |

|   |     | 5.2.1    | KMM Definition                                                       | 9  |

|   |     | 5.2.2    | KMM Complexity Analysis    9                                         | 91 |

|   |     | 5.2.3    | Mitigating the Accumulator Complexity Increase in KMM 9              | 6  |

|   | 5.3 | KMM      | Hardware Architectures                                               | 8  |

|   |     | 5.3.1    | Baseline $MM_1$ Architecture                                         | 8  |

|   |     | 5.3.2    | Fixed-Precision KMM Architecture                                     | )1 |

|   |     | 5.3.3    | Precision-Scalable KMM Architecture                                  | )1 |

|   |     | 5.3.4    | System Integration                                                   | 6  |

|   |     | 5.3.5    | Multiplier Compute Efficiency                                        | 17 |

|   |     | 5.3.6    | Area Unit (AU) Compute Efficiency                                    | 19 |

|   | 5.4 | Result   | s                                                                    | 3  |

|   |     | 5.4.1    | Evaluation Metrics                                                   | 3  |

|   |      | 5.4.2   | Comparison to Prior Work                              | . 114 |

|---|------|---------|-------------------------------------------------------|-------|

|   |      | 5.4.3   | Comparison to Baseline Designs                        | . 118 |

|   | 5.5  | Summ    | ary                                                   | . 122 |

| 6 | Stra | ssen M  | ulti-Systolic-Array Hardware Architectures            | 124   |

|   | 6.1  | Strasse | en Architecture                                       | . 126 |

|   |      | 6.1.1   | Memory Layout and Access Algorithm                    | . 126 |

|   |      | 6.1.2   | Strassen Multi-Systolic-Array Design                  | . 128 |

|   |      | 6.1.3   | Baseline Designs                                      | . 131 |

|   |      | 6.1.4   | System Integration                                    | . 134 |

|   |      | 6.1.5   | Multiplier Compute Efficiency                         | . 135 |

|   |      | 6.1.6   | Supporting Smaller Matrices with the Same Performance | . 136 |

|   | 6.2  | Result  | S                                                     | . 137 |

|   |      | 6.2.1   | Comparison to Baseline Designs                        | . 139 |

|   |      | 6.2.2   | Comparison to Prior Work                              | . 140 |

|   |      | 6.2.3   | Combining FFIP and SMM                                | . 143 |

|   | 6.3  | Summ    | ary                                                   | . 144 |

| 7 | Con  | clusion |                                                       | 145   |

|   | 7.1  | Summ    | ary of Contributions                                  | . 147 |

|   | 7.2  | Future  | Work                                                  | . 149 |

|   |      | 7.2.1   | Floating-Point Algorithms and Architectures           | . 149 |

|   |      | 7.2.2   | Toom-Cook Matrix Multiplication                       | . 150 |

|   |      | 7.2.3   | Non-Systolic-Array Architectures                      | . 150 |

|   |      | 7.2.4   | Transformer Acceleration                              | . 150 |

| 7.3 | Concluding Remarks |  |  |  | • |  |  |  | • |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 15 | 1 |

|-----|--------------------|--|--|--|---|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----|---|

|-----|--------------------|--|--|--|---|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----|---|

# **List of Figures**

| 1.1 | Categorization of the subfield of deep learning within the broader field of                      |    |

|-----|--------------------------------------------------------------------------------------------------|----|

|     | artificial intelligence.                                                                         | 2  |

| 2.1 | A neural network neuron in a fully-connected layer                                               | 10 |

| 2.2 | A deep neural network with an input layer, two hidden layers, and output                         |    |

|     | layer                                                                                            | 10 |

| 2.3 | Example of a convolutional layer in Alexnet [11]. The bottom portion of                          |    |

|     | the figure shows a convolutional layer where $N = 1$ , $C_{in} = 3$ , $C_{out} = 48$ ,           |    |

|     | $H = W = 55$ , $H_k = W_k = 11$ , and $H_s = W_s = 4$ . The input feature maps                   |    |

|     | have a width of 224 (before padding), and the next convolutional layer that                      |    |

|     | is partially shown has a kernel size of $H_k = W_k = 11$                                         | 15 |

| 2.4 | Demonstrating how matrix multiplication is performed on a systolic array                         |    |

|     | of processing elements                                                                           | 18 |

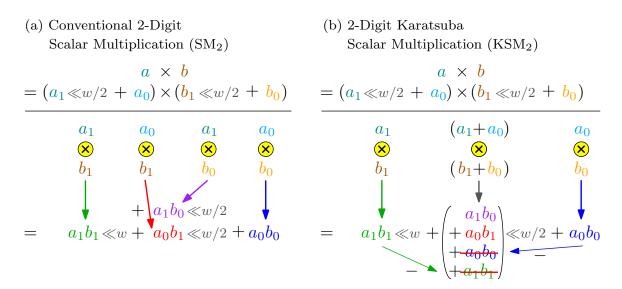

| 2.5 | $SM_2$ algorithm illustration on left, $KSM_2$ algorithm illustration on right.                  |    |

|     | Compared to $SM_2$ , $KSM_2$ requires only 3 single-digit multiplications, how-                  |    |

|     | ever, it requires 3 more additions, increasing the overall operation count                       | 33 |

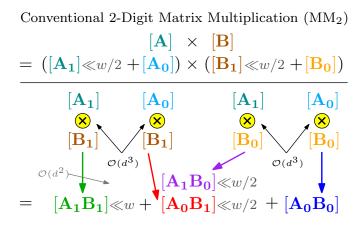

| 2.6 | $MM_2$ algorithm illustration. The 4 single-digit matrix multiplications of                      |    |

|     | complexity $\mathcal{O}(d^3)$ dominate the $\mathcal{O}(d^2)$ complexity of the matrix additions | 35 |

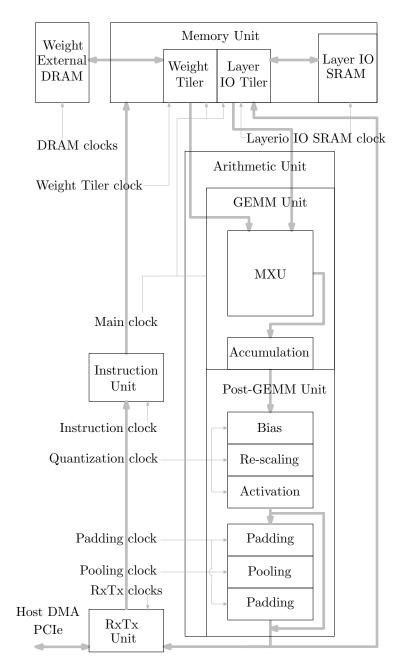

| 3.1 | The example accelerator system design used to host and evaluate the base-       |    |

|-----|---------------------------------------------------------------------------------|----|

|     | line and proposed MXUs when overlaid on top of systems based on the             |    |

|     | most efficient systolic array accelerators used in practice, e.g., the TPU [3], |    |

|     | [5], [6]                                                                        | 44 |

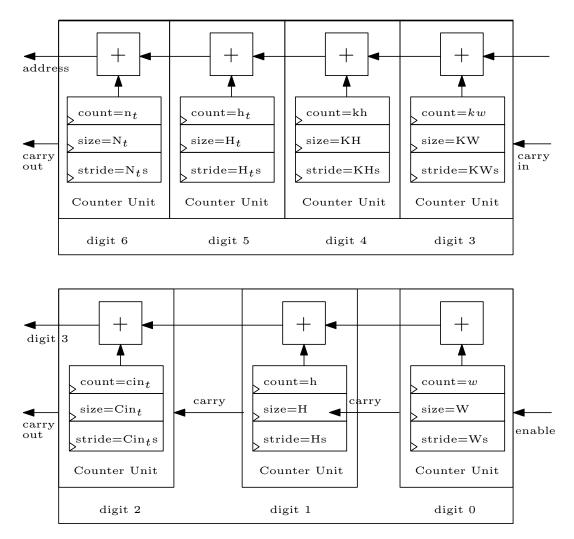

| 3.2 | Layer IO memory access counters for performing in-place mapping of 2-D          |    |

|     | convolution to GEMM.                                                            | 46 |

| 3.3 | Layer IO memory access and blocking scheme to partition the memory              |    |

|     | and perform in-place mapping of two-dimensional convolution to GEMM,            |    |

|     | provided for context.                                                           | 47 |

| 3.4 | The baseline MXU architecture.                                                  | 48 |

| 3.5 | MXU weight column shift register logic requiring control signal to be con-      |    |

|     | nected to each element in the column.                                           | 53 |

| 3.6 | MXU weight column shift register logic with control connections fully lo-       |    |

|     | calized to adjacent elements.                                                   | 53 |

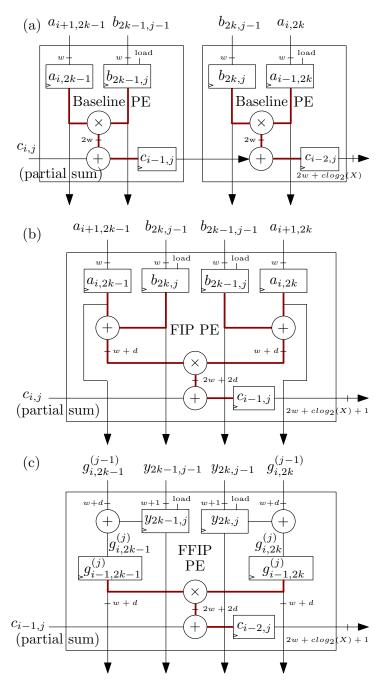

| 4.1 | The PE architectures for implementing the (a) baseline, (b) FIP, and (c)        |    |

|     | FFIP inner-product algorithms in hardware. The FIP and FFIP PEs shown           |    |

|     | in (b) and (c) each individually provide the same effective computational       |    |

|     | power as the two baseline PEs shown in (a) combined which implement the         |    |

|     | baseline inner product as in existing systolic-array deep learning accelera-    |    |

|     | tors. Critical paths are highlighted                                            | 64 |

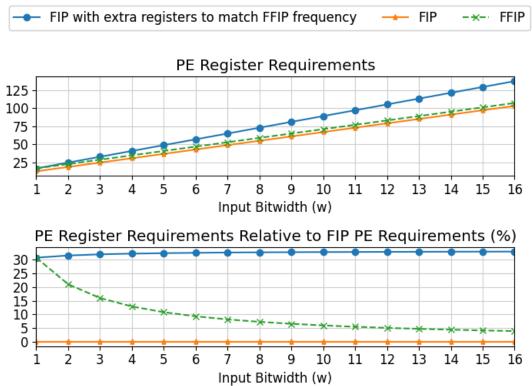

| 4.2 | PE register requirements at different $w$ bitwidths for the FIP PE, FFIP PE,    |    |

|     | and FIP PE with extra registers before the multiplier to match the frequency    |    |

|     | of the FFIP PEs. Values are calculated using Eqs. (4.11)- (4.13) for $X = 64$   |    |

|     | and $d = 1. \ldots \ldots \ldots$                                               | 67 |

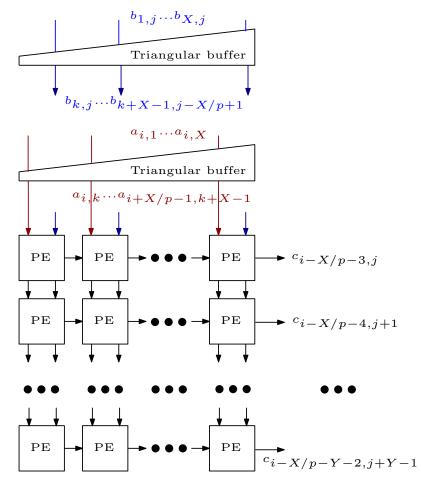

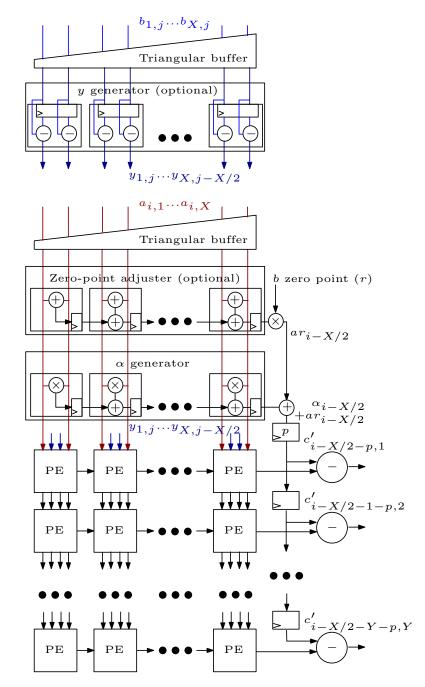

| 4.3 | The FFIP MXU architecture. The FIP MXU is the same except that FIP                              |   |

|-----|-------------------------------------------------------------------------------------------------|---|

|     | PEs are used instead and the $y$ generator block is not present, and $b$ inputs                 |   |

|     | are passed in instead of $y$ inputs. The $\alpha$ terms are calculated and subtracted           |   |

|     | as shown by first passing the $a$ inputs through an additional row of MAC                       |   |

|     | units before they enter the rest of the MXU                                                     | 9 |

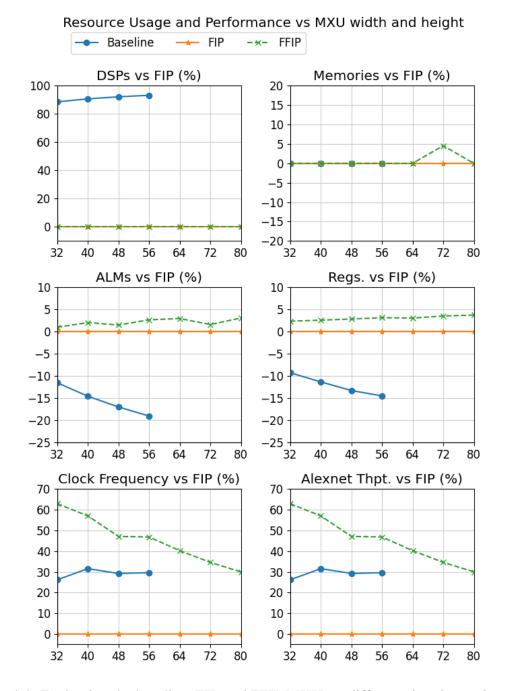

| 4.4 | Evaluating the baseline, FIP, and FFIP MXUs at different sizes instantiated                     |   |

|     | into an example deep learning accelerator system design used for valida-                        |   |

|     | tion, with 8-bit fixed-point inputs on an Arria 10 SX 660 FPGA                                  | 6 |

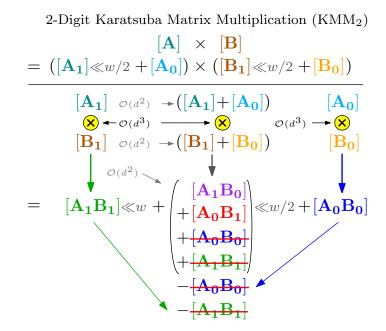

| 5.1 | $\text{KMM}_2$ algorithm illustration. Compared to the scalar algorithms $\text{KSM}_2$         |   |

|     | versus SM <sub>2</sub> , the increase in number of additions with complexity $\mathcal{O}(d^2)$ |   |

|     | in $\text{KMM}_2$ versus $\text{MM}_2$ is now insignificant relative to the reduction of 3      |   |

|     | instead of 4 single-digit matrix multiplications of complexity $\mathcal{O}(d^3)$ , al-         |   |

|     | lowing the overall #operations in $KMM_2$ to be less than conventional $MM_2$ .                 | 9 |

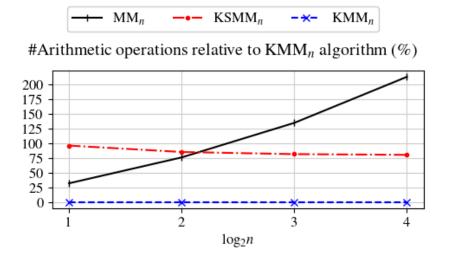

| 5.2 | Plotting (5.5) and (5.6) relative to (5.7) for different $n$ with $d = 64$ . As                 |   |

|     | can be seen, $\text{KSMM}_n$ requires over 75% more operations than $\text{KMM}_n$ .            |   |

|     | Additionally, $KMM_n$ and $KSMM_n$ require exponentially fewer operations                       |   |

|     | than $MM_n$ with respect to $n$ , however, $KMM_n$ requires fewer operations                    |   |

|     | than $MM_n$ even starting at $n = 2$ , while KSMM <sub>n</sub> does not fall below $MM_n$       |   |

| until $n > 4$ . | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 96 |

|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

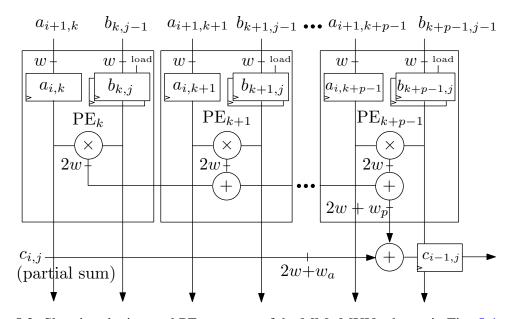

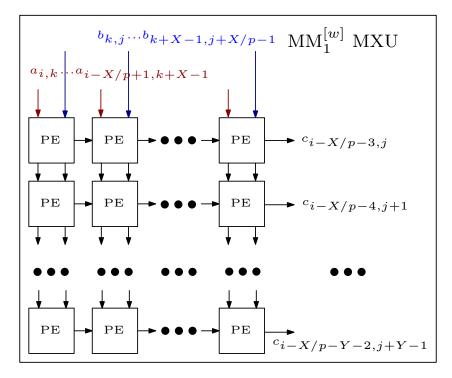

| 5.3 | Showing the internal PE structure of the $MM_1$ MXUs shown in Fig. 5.4 as                                                                                                          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | well as the structure for implementing Algorithm $6$ in hardware to reduce                                                                                                         |

|     | the hardware cost of the accumulator logic. $p$ is a hardware parameter                                                                                                            |

|     | equal to the number of multiplication products that are pre-accumulated                                                                                                            |

|     | on a smaller bitwidth to reduce the accumulation complexity before being                                                                                                           |

|     | added to the full-bitwidth accumulation sum. We use $p = 4$ in our evaluation. 99                                                                                                  |

| 5.4 | Baseline MM <sub>1</sub> MXU architecture present at the core of the KMM architec-                                                                                                 |

|     | tures, provided for context. $X$ and $Y$ refer to the MXU width and height in                                                                                                      |

|     | number of multipliers                                                                                                                                                              |

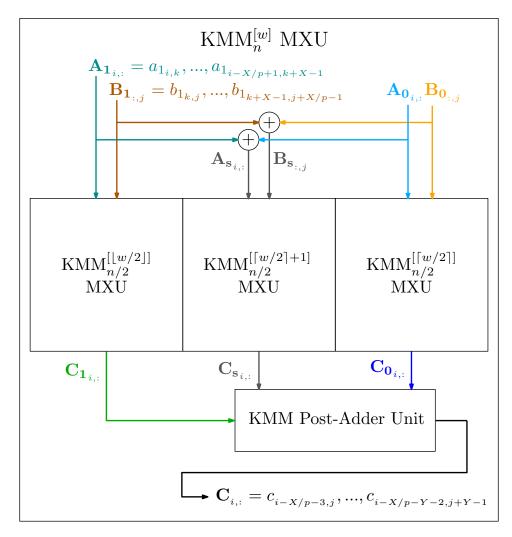

| 5.5 | Fixed-precision KMM architecture for executing on inputs of a fixed pre-                                                                                                           |

|     | cision of $w$ bits                                                                                                                                                                 |

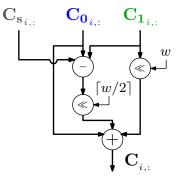

| 5.6 | KMM Post-Adder Unit from Fig. 5.5 for executing $\mathbf{C}_{1_{i,:}} \ll w + (\mathbf{C}_{\mathbf{s}_{i,:}} - \mathbf{C}_{1_{i,:}} - \mathbf{C}_{0_{i,:}}) \ll \lceil w/2 \rceil$ |

|     | $+C_{0_{i,:}}$                                                                                                                                                                     |

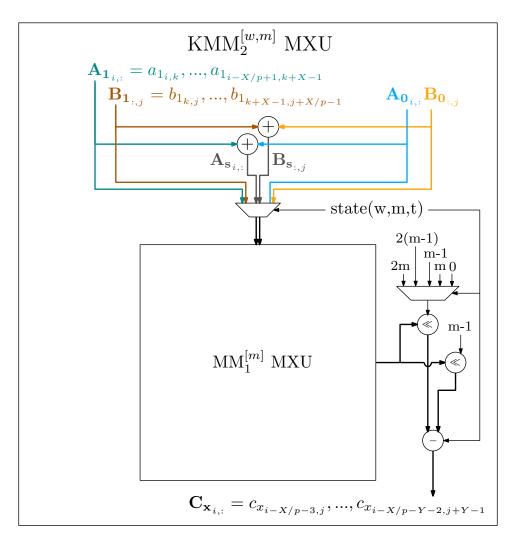

| 5.7 | Precision-scalable KMM architecture for more efficiently using $m$ -bit-input                                                                                                      |

|     | multipliers to execute across varying input precisions of bitwidth $w$ for ap-                                                                                                     |

|     | plications where the input bitwidths are expected to vary                                                                                                                          |

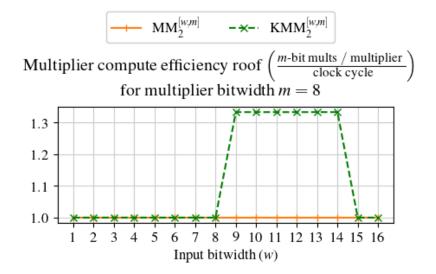

| 5.8 | Maximum achievable multiplier compute efficiencies (derived in Section                                                                                                             |

|     | 5.3.5) for the precision-scalable $MM_2$ and $KMM_2$ architectures                                                                                                                 |

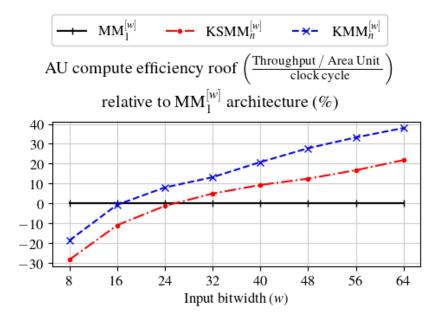

| 5.9 | Maximum achievable AU compute efficiencies (derived in Section 5.3.6)                                                                                                              |

|     | for the fixed-precision $MM_1$ , $KSMM_n$ , and $KMM_n$ architectures                                                                                                              |

|     |                                                                                                                                                                                    |

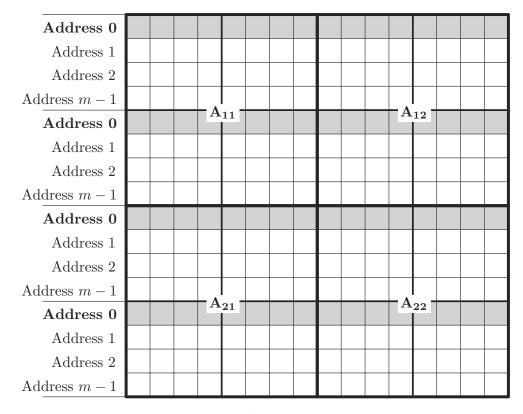

| 6.1 | Example data layout for the $\mathbf{A}$ matrix in memory for an architecture imple-                                    |

|-----|-------------------------------------------------------------------------------------------------------------------------|

|     | menting Strassen matrix multiplication for 2 levels of recursion ( $SMM_2$ ).                                           |

|     | Each address $i$ contains every $m^{th}$ row of A concatenated together starting                                        |

|     | at row $i$ (notated as $A_{i:m:,:}$ ). To help illustrate this, the gray coloured rows                                  |

|     | are all elements of A belonging to address 0, which forms $A_{0:m:,:}$ contain-                                         |

|     | ing row 0 of every A sub-block from the lowest level of recursion in $(2.24)$ .                                         |

|     | The organization for the B matrices in memory are the same, except that                                                 |

|     | the order of the elements is transposed compared to the $\mathbf{A}$ matrix layout                                      |

|     | shown here                                                                                                              |

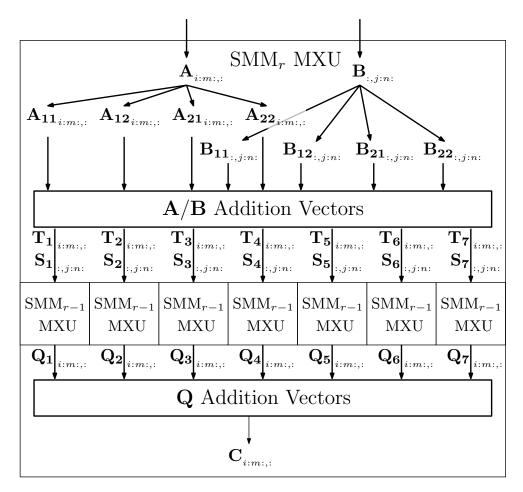

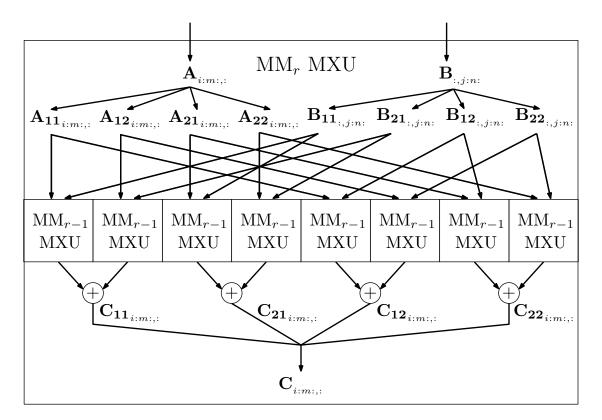

| 6.2 | Top-level diagram of the proposed multi-systolic-array architecture for im-                                             |

|     | plementing $r$ levels of recursion of Strassen matrix multiplication (SMM <sub>r</sub> ). 129                           |

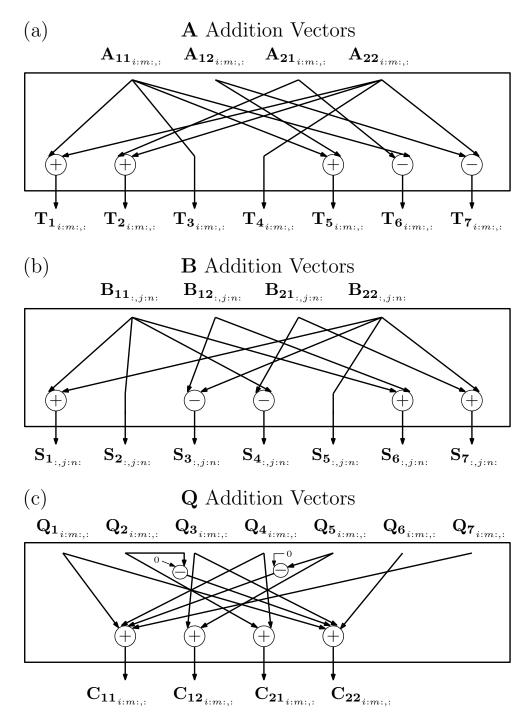

| 6.3 | Internal structure of the SMM <sub>r</sub> MXU addition vectors from Fig. 6.2 130                                       |

| 6.4 | Baseline multi-systolic-array architecture for implementing conventional                                                |

|     | matrix multiplication from (2.23) for $r$ levels of recursion (MM <sub>r</sub> ) in hardware. 132                       |

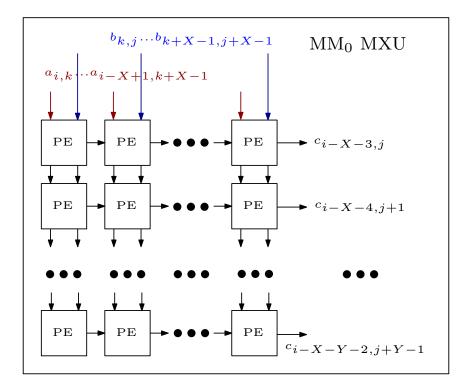

| 6.5 | Baseline MM <sub>0</sub> single-systolic-array architecture present at the lowest level                                 |

|     | of recursion in the SMM <sub><math>r</math></sub> and MM <sub><math>r</math></sub> MXU architectures, provided for com- |

|     | pleteness. $X$ here represents the width of the $a$ and $b$ vectors entering the                                        |

|     | $MM_0 MXU$ , and Y represents the width of the c vectors exiting the MXU 133                                            |

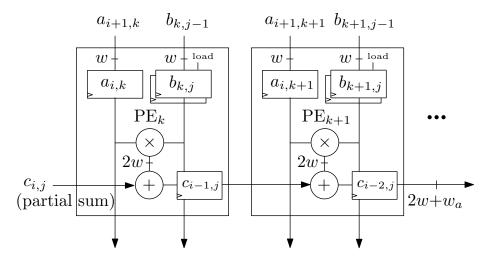

| 6.6 | The internal PE structure of each $MM_0$ MXU from Fig. 6.5, provided for                                                |

|     | completeness. Here, $w_a$ is the additional bitwidth added to account for                                               |

|     | accumulation, equal to $\lceil \log_2(X) \rceil$ , where X is the width of the a and b                                  |

|     | vectors entering the $MM_0$ MXU                                                                                         |

# **List of Tables**

| 4.1 | Comparison with state-of-the-art 8-bit-input accelerators for different mod- |

|-----|------------------------------------------------------------------------------|

|     | els on the same FPGA family                                                  |

| 4.2 | Comparison with state-of-the-art 16b-bit-input accelerators for different    |

|     | models on the same FPGA family                                               |

| 4.3 | Comparison with state-of-the-art accelerators on different FPGAs for the     |

|     | same models and input bitwidths                                              |

| 5.1 | Proposed precision-scalable KMM and baseline MM systolic-array archi-        |

|     | tectures integrated into a deep learning accelerator system compared with    |

|     | each other and prior state-of-the-art deep learning accelerators on Arria 10 |

|     | GX 1150 FPGA                                                                 |

| 5.2 | Comparison of an FFIP [8] systolic-array architecture, which doubles per-    |

|     | formance per MAC unit, with combined FFIP+KMM systolic-array archi-          |

|     | tectures when integrated into deep learning accelerator systems on Arria 10  |

|     | GX 1150 FPGA                                                                 |

| 5.3 | Comparison of proposed fixed-precision KMM and baseline $MM_1$ and KSMM      |

|     | systolic-array architectures in isolation (without integration into a deep   |

|     | learning accelerator system) on Arria 10 GX 1150 FPGA. All designs in        |

|     | this table contain 0 memory resources                                        |

| 6.1 | Comparison of $SMM_r$ multi-systolic-array architectures against the base-         |

|-----|------------------------------------------------------------------------------------|

|     | line $MM_0$ single-systolic-array architecture and baseline $MM_r$ multi-systolic- |

|     | array architectures. These results contain the systolic arrays in isolation        |

|     | (without integration into a deep learning accelerator system)                      |

| 6.2 | $SMM_r$ multi-systolic-array architectures integrated into a deep learning ac-     |

|     | celerator system compared with prior state-of-the-art deep learning accel-         |

|     | erators on the same FPGA                                                           |

| 6.3 | Comparison of an FFIP single-systolic-array architecture from Chapter 4,           |

|     | which doubles performance per MAC unit, with combined FFIP+SMM $_r$                |

|     | multi-systolic-array architectures when integrated into deep learning ac-          |

|     | celerator systems                                                                  |

## **Chapter 1**

# Introduction

Recent years have seen increasing breakthroughs and commercial adoption of deep learning, which has enabled ground-breaking applications ranging from human-like chatbots like ChatGPT, to generating realistic image and video content from prompts, self-driving cars [1], detecting cancer [2], and beating human champions at the complex game of Go [3]. However, deep learning inference increasingly requires massive amounts of computational power to perform, making it ever-more difficult to execute quickly and efficiently. This can be mitigated by building special-purpose computer hardware that can perform deep learning inference more efficiently than general-purpose hardware like conventional central processing units (CPU)s. In this thesis, we join this effort by identifying and advancing an under-explored area in the field of deep learning hardware design.

The rest of this chapter provides more background on deep learning in Section 1.1, and Section 1.2 goes over a high-level description of hardware acceleration and why it is necessary to meet the computational demands of deep learning. Section 1.3 then identifies under-explored areas in prior work on deep learning acceleration that form the basis for our contributions. Finally, our contributions and thesis organization are outlined in Section 1.4.

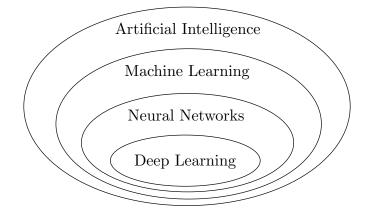

Figure 1.1: Categorization of the subfield of deep learning within the broader field of artificial intelligence.

### **1.1 Deep Learning**

Increases in computational power and available training data in recent decades have helped initiate an awakening for the field of deep learning, allowing models and theories to be proven and leveraged in real-world applications that previously were infeasible to test. This has led to a positive feedback loop between increasing adoption of deep learning into commercial applications and further funding and research interest leading to scientific advancements.

Deep learning (DL) is a category of machine learning (ML), which is subset of the broad field of artificial intelligence (AI). AI was founded as an academic discipline in the 1950s and, at a high level, is a field of research with the goal of creating artificial systems that exhibit intelligent human-like behaviour. Machine learning is a strategy to achieve AI through systems that train and learn to achieve tasks on their own or without explicit instructions. This saves humans much of the laborious efforts of working out all of the problem details and doing all the manual programming of the system, passing some of that effort onto the system itself.

Artificial Neural networks (ANN)s, also referred to as just neural networks (NN)s were first proposed in the 1940s and are a method within the field of ML inspired by the human brain, which is currently and originally the best known general intelligence system for learning and solving problems. NNs are built around the concept of a neuron, which is the primitive computational element in the human brain, and there are approximately 86 billion neurons in the average human brain [4]. Deep learning, first proposed in the 1960s, is the study of large neural networks, also called deep neural networks, and is the primary technology behind the applications currently labelled as using ML or AI today. In Section 2.1, we provide more details on DNNs and the computational patterns they map to.

#### **1.2 Hardware Acceleration**

Due to the increasing adoption of deep learning, there is high demand for ways to efficiently perform deep learning inference on a range of computational platforms ranging from smart phones to warehouse-scale distributed computing data centers alike; all of which aim to maximize execution speed and minimize power usage. However, the number of operations required to perform deep learning inference is commonly in the billions and is only increasing in newer deep learning models, making these performance goals ever-more difficult to reach. Fortunately, the deep learning inference commonly decomposes down to performing the same subclass of compute patterns which mainly consist of performing a large number of multiplications and additions that can be performed in parallel with one another. This makes it a great fit for hardware acceleration, in which custom hardware is designed to execute a specialized subset of compute patterns in parallel more efficiently than what is possible to be performed in general-purpose hardware like CPUs that can perform a wider range of operations but operate more sequentially and slowly.

Conventional CPUs are fit for any general or unknown computational patterns, making them the central part of a general-purpose computer. The intention of more specialized hardware, however, is to be more efficient at executing a smaller range of computational patterns. Specialized hardware typically achieves this by containing only the logic necessary for its specific subset of tasks, and by performing many subtasks in parallel.

GPUs are specialized at performing simple arithmetic operations such as multiplications and additions in parallel, making GPUs an initially natural fit for deep learning acceleration. However, one limiting factor of GPUs is that it can be difficult to load all of the inputs to the multiplications and additions and return their outputs quickly enough, causing this data movement to become the performance bottleneck. Specialized hardware such as the Google Tensor Processing Unit (TPU) [3], [5], [6] allows for many multiplications and additions to be performed in parallel while also requiring less intermediate data movement, leading to faster and more efficient deep learning acceleration compared to a GPU.

Specialized hardware can be implemented using two main types of technologies, application specific integrated circuits (ASIC) or field-programmable gate-arrays (FPGA). ASICs are specialized hardware designed strictly for a specific purpose where the functionality is permanent after the hardware is shipped. In contrast, an FPGA is a device that contains programmable circuitry that can be updated to implement a specified logic circuit at any time which makes design errors more forgivable, provides future-proofing by allowing hardware designs to be updated, and it is much cheaper to purchase a small number of FPGAs than manufacturing an ASIC for mass production. On the other hand, while the functionality of ASICs is permanent, they are more optimized and efficient at performing that specific functionality than an FPGA programmed for that same functionality. In Section 2.2, we discuss more background and prior works on custom deep learning hardware.

### **1.3 Efficient Algebraic Algorithms**

To address the increasing need for efficiently performing deep learning inference, a variety of methods for hardware designs and optimizing the deep learning inference in hardware have been explored in recent years. However, as all deep learning model and hardware implementation optimizations are becoming explored to their limits, optimizations for reducing deep learning workloads at the algebraic level remain a less travelled route for continuing progress. This involves rearranging the computation for carrying out a deep learning model's algebra such that it produces the same output but from fewer or cheaper operations performed in hardware.

For example, multiplications can require more circuitry to execute in hardware than additions. So if a deep neural network's algebra can be rearranged to produce the same output while trading half of the multiplications for additions, then the same result could be computed from a smaller and less power-consuming hardware circuit. Or the circuitry could be scaled up to execute the deep neural network faster while consuming the same amount hardware area and power as a circuit using conventional algebra. Additionally, there are under-explored efficient algebraic algorithms that can produce the same result from both fewer additions and multiplications being performed which have not been sufficiently studied for exploitation in custom hardware circuits.

This leaves opportunities to derive new contributions showing how to translate new or prior works on efficient algebraic algorithms into improvements in hardware accelerator architectures for deep learning, which is the focus of this thesis. In Section 2.3 we provide more background on relevant efficient algebraic algorithms and their hardware architectures.

#### **1.4** Contributions and Thesis Organization

In this thesis, we study the identified under-explored area of algebraic enhancements for matrix multiplication algorithms and hardware architectures with application to deep learning acceleration. We propose several advancements to efficient algebraic algorithms and/or their systolic-array hardware architectures in Chapters 4 - 6.

Chapter 2 provides more detailed background on deep learning and the computational patterns it maps to, prior approaches for deep learning acceleration, and prior work on efficient algebraic algorithms and their implementation in hardware, which builds the foundation for presenting our contributions.

Chapter 3 outlines the deep learning accelerator system used for evaluating the architectures proposed in Chapters 4 - 6. To evaluate each of our contributions, different proposed matrix multiplication architectures are swapped for the baseline matrix multiplication unit (MXU) in the system design, while the remaining components in the accelerator system remain largely unchanged for each method.

Chapter 4 presents an algorithm called the free-pipeline inner product (FFIP) and general hardware architecture that improve Winograd's under-explored inner-product algorithm called the fast inner product (FIP) [7] that can be seamlessly incorporated into deep learning accelerators to significantly increase the accelerator's performance-per-area. We implement and evaluate FIP for the first time in a deep learning accelerator system described in Chapter 3. We then identify a weakness of FIP and propose the new FFIP algorithm and generalized hardware architecture that inherently address that weakness. We provide deep learning-specific optimizations for the FIP and FFIP algorithms and hardware architectures. We derive how the (F)FIP architectures increase the theoretical compute efficiency and performance limits in the general case. The contributions from this chapter have been published in [8].

Chapter 5 proposes an algorithm and its hardware architectures that extend the Karatsuba algorithm [9] to matrix multiplication. While the Karatsuba algorithm reduces the complexity of large integer multiplication, the extra additions required minimize its benefits for smaller integers of more commonly-used bitwidths. In this chapter, we propose the extension of the scalar Karatsuba multiplication algorithm to matrix multiplication, showing how this maintains the reduction in multiplication complexity of the original Karatsuba algorithm while reducing the complexity of the extra additions. Furthermore, we propose new matrix multiplication hardware architectures for efficiently exploiting this extension of the Karatsuba algorithm in custom hardware. We show that the proposed algorithm and hardware architectures can provide real area or execution time improvements for integer matrix multiplication compared to scalar Karatsuba or conventional matrix multiplication algorithms, while also supporting implementation through proven systolic array and conventional multiplier architectures at the core. We provide a complexity analysis of the algorithm and architectures and evaluate the proposed designs both in isolation and in an end-to-end deep learning accelerator system described in Chapter 3 compared to baseline designs and prior state-of-the-art works implemented on the same type of compute platform, demonstrating their ability to increase the performance-per-area of matrix multiplication hardware.

Chapter 6 explores hardware architectures for exploiting Strassen's fast matrix multiplication algorithm. While Strassen's matrix multiplication algorithm reduces the complexity of naive matrix multiplication, general-purpose hardware is not suitable for achieving the algorithm's promised theoretical speedups, leaving the question of if it could be better exploited in custom hardware architectures designed specifically for executing the algorithm. However, there is limited prior work on this and it is not immediately clear how to derive such architectures or if they can ultimately lead to real improvements. We bridge this gap, presenting and evaluating new systolic-array architectures that efficiently translate the theoretical complexity reductions of Strassen's algorithm directly into hardware resource savings. Furthermore, the architectures are multi-systolic-array designs that can multiply smaller matrices with higher utilization than single-systolic-array designs. The proposed design implemented on FPGA for multiplying matrix sizes down to  $24 \times 24$  at 2 levels of Strassen recursion uses approximately 10% fewer soft logic resources and  $1.3 \times$  fewer DSP units than a conventional multi-systolic-array design. We evaluate the proposed Strassen systolic arrays in isolation as well as in an end-to-end deep learning accelerator system described in Chapter 3 compared to baseline designs and prior works implemented on the same type of compute platform, demonstrating their ability to increase compute efficiency and achieve state-of-the-art performance. Finally, Chapter 7 provides a summary of the contributions and results, possible directions for future work, and concluding remarks.

### Chapter 2

# **Background and Prior Work**

In this chapter, we provide more background on deep learning and how it maps to matrix multiplication in Section 2.1, followed by a literature review of prior work and approaches for deep learning hardware acceleration in Section 2.2. Section 2.3 then provides back-ground on an under-explored avenue for continuing progress in the field of deep learning hardware acceleration, which is advancement and application of efficient matrix multiplication algorithms to deep learning hardware architectures.

#### **2.1** Deep Learning and Matrix Multiplication

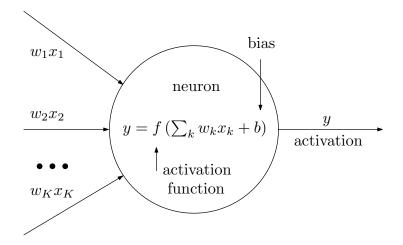

Neural networks are built around the concept of a neuron, which is the primitive computational element in the human brain. Neural networks contain interconnected layers of neurons, where each neuron outputs some function of its inputs like shown in Fig. 2.1, and passes its result called an *activation* as input to neurons in other layers. The functions that the neurons perform on their inputs contain constants or parameters called *weights* that determine properties such as the scaling factor to scale each of its input values by.

Figure 2.1: A neural network neuron in a fully-connected layer.

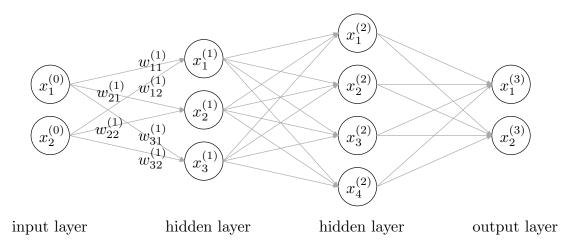

Figure 2.2: A deep neural network with an input layer, two hidden layers, and output layer.

A deep neural network (DNN) is a neural network consisting of four or more layers such that it contains two or more middle layers (called *hidden layers*) between the input and output layers such as the example shown in Fig. 2.2. While there are many variations of deep neural network model architectures, the computationally dominant portion of many common DNN models used today are based on several types of neural network layers discussed next that can all be mainly decomposed to matrix multiplication.

#### 2.1.1 Fully-Connected Layers

Fully-connected layers are a common building block included in many types of DNN models including convolutional neural networks (CNN)s and Transformer models that are discussed next. The hidden layers in Fig. 2.2 are an example of a fully-connected layer. Each output activation in a fully-connected layer is a weighted sum of all output activations from the previous layer, followed by the addition of a *bias* value, and finally the application of a non-linear activation function such as a sigmoid, hyperbolic tangent, or rectified linear unit (ReLU) function [10].

This computation translates to a matrix-vector multiplication-based computation between the weights and the previous layer's activations. For illustration, the leftmost hidden layer in Fig. 2.2 is a fully-connected layer that performs the following operation:

$$\begin{bmatrix} y_1^{(1)} \\ y_2^{(1)} \\ y_3^{(1)} \end{bmatrix} = \begin{bmatrix} b^{(1)} & w_{11}^{(1)} & w_{12}^{(1)} \\ b^{(1)} & w_{21}^{(1)} & w_{22}^{(1)} \\ b^{(1)} & w_{31}^{(1)} & w_{32}^{(1)} \end{bmatrix} \begin{bmatrix} 1 \\ x_1^{(0)} \\ x_2^{(0)} \end{bmatrix}, \begin{bmatrix} x_1^{(1)} \\ x_2^{(1)} \\ x_3^{(1)} \end{bmatrix} = \begin{bmatrix} f(y_1^{(1)}) \\ f(y_2^{(1)}) \\ f(y_3^{(1)}) \end{bmatrix}.$$

(2.1)

Multiple inferences can also be performed consecutively in batches when passing through neural network layers. Performing inference on a batch of inputs like this then translates to a matrix-matrix multiplication-based computation. For example, this would translate to the following operation in the fully-connected layer contained in the leftmost hidden layer in Fig. 2.2:

$$\begin{bmatrix} y_{11}^{(1)} & y_{12}^{(1)} & y_{13}^{(1)} \\ y_{21}^{(1)} & y_{22}^{(1)} & y_{23}^{(1)} \\ y_{31}^{(1)} & y_{32}^{(1)} & y_{33}^{(1)} \end{bmatrix} = \begin{bmatrix} b^{(1)} & w_{11}^{(1)} & w_{12}^{(1)} \\ b^{(1)} & w_{21}^{(1)} & w_{22}^{(1)} \\ b^{(1)} & w_{31}^{(1)} & w_{32}^{(1)} \end{bmatrix} \begin{bmatrix} 1 & 1 & 1 \\ x_{11}^{(0)} & x_{12}^{(0)} & x_{13}^{(0)} \\ x_{21}^{(0)} & x_{22}^{(0)} & x_{23}^{(0)} \end{bmatrix}$$

(2.2)

$$\begin{bmatrix} x_{11}^{(1)} & x_{12}^{(1)} & x_{13}^{(1)} \\ x_{21}^{(1)} & x_{22}^{(1)} & x_{23}^{(1)} \\ x_{31}^{(1)} & x_{32}^{(1)} & x_{33}^{(1)} \end{bmatrix} = \begin{bmatrix} f(y_{11}^{(1)}) & f(y_{12}^{(1)}) & f(y_{13}^{(1)}) \\ f(y_{21}^{(1)}) & f(y_{22}^{(1)}) & f(y_{23}^{(1)}) \\ f(y_{31}^{(1)}) & f(y_{32}^{(1)}) & f(y_{33}^{(1)}) \end{bmatrix}.$$

(2.3)

This can then be written as:

$$\mathbf{X}^{(1)} = f(\mathbf{W}^{(1)}\mathbf{X}^{(0)} + b^{(1)}).$$

(2.4)

Letting K and M respectively represent the number of layer inputs and outputs and N be the number of inferences being performed in a batch (the *batch size*),  $\mathbf{W}^{(1)}$  is then a matrix of size  $M \times K$  and **X** is a matrix of size  $K \times N$ . The majority of operations in a fullyconnected layer performing inference in batches is then contained in the matrix-matrix multiplication  $\mathbf{W}^{(1)}\mathbf{X}$  above, as it requires  $\mathcal{O}(MNK)$  operations, which dominates the complexity of the bias addition and activation function which require  $\mathcal{O}(MN)$  operations.

In this thesis, we instead refer to the matrix multiplications  $\mathbf{W}^{(d)}\mathbf{X}^{(d-1)}$  in these layers in the following format:

$$\mathbf{C} = \mathbf{A}\mathbf{B}\,,\tag{2.5}$$

where  $\mathbf{C} = (\mathbf{W}^{(\mathbf{d})}\mathbf{X}^{(\mathbf{d}-1)})^T$ ,  $\mathbf{A} = \mathbf{X}^{(\mathbf{d}-1)^T}$ , and  $\mathbf{B} = \mathbf{W}^{(\mathbf{d})^T}$ .

#### 2.1.2 Convolutional Layers

Convolutional neural networks (CNN)s are a common type of DNN that played a major role in the re-awakening of the field of deep learning in the early 2010's when AlexNet [11] enabled a sudden boost in the best achievable error rates for image classification tasks. They contain convolutional layers that typically perform 2-D convolutions between activations and weights.

The computationally dominant portion of CNNs are the convolutional layers. The input and output activations of a convolutional layer are 2-D and are referred to as *feature maps* or *channels*. For example, the input image to a CNN will contain 3 channels/feature maps to represent the red, green, and blue values of each pixel, and each feature map will have a height/width corresponding to the pixel height/width of the image. Each layer's set of input/output feature maps can be thought of as a single 3-D input/output.

Each 2-D input feature map is convolved with a different 2-D convolution filter called a *kernel*, and the convolution outputs for all input feature maps are summed together to produce an output feature map. The set of kernels that are used for each of the different input feature maps can then be thought of as a single 3-D kernel. This computation is then repeated with multiple distinct 3-D kernels to produce multiple output feature maps. Due to this, each layer's kernel can be thought of as a 4-D tensor. Finally, multiple inferences can be performed consecutively on a batch of multiple sets of features maps.

Each layer input can then be thought of as a 4-D tensor, letting  $C_{in}/C_{out}$  represent a layer's number of input/output channels or feature maps, H/W represent the height/width of a layer's output feature maps, N is the batch size, and n is the current inference being

performed in the batch. Each layer's kernel is then a 4-D tensor with dimensions of size  $C_{out}$ ,  $C_{in}$ ,  $H_k$ ,  $W_k$ , where  $H_k/W_k$  are the height/width of the kernel. A dimension's stride, which is explained below, is represented by the dimension with a  $_s$  subscript (e.g.  $W_s$  is the stride for the W dimension).

A convolutional layer's calculation for each output element is then described by the following, where  $\mathbf{X}^{(d)}$  is the layer output,  $\mathbf{X}^{(d-1)}$  is the layer input, and  $\mathbf{W}^{(d)}$  is the layer's weight/kernel:

$$\mathbf{X}^{(\mathbf{d})}[n][c_{out}][h][w] = \sum_{c_{in}=0}^{C_{in}-1} \sum_{w_k=0}^{W_k-1} \sum_{h_k=0}^{H_k-1} \mathbf{X}^{(\mathbf{d}-1)}[n][c_{in}][hH_s+h_k][wW_s+w_k] \mathbf{W}^{(\mathbf{d})}[c_{out}][c_{in}][h_k][w_k] \,.$$

(2.6)

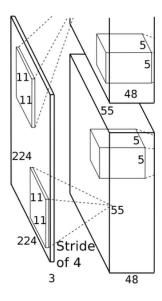

For illustration, Fig. 2.3 shows a visual representation of an example convolutional layer performing (2.6).

To understand how convolutional layers' computation in (2.6) can be mapped to matrix multiplication, consider how a 1-D convolution can be mapped to a vector-matrix multiplication as follows:

$$\begin{bmatrix} a_0 & a_1 & a_2 \end{bmatrix} * \begin{bmatrix} b_0 & b_1 & b_2 \end{bmatrix} = \begin{bmatrix} b_0 & 0 & 0 \\ b_1 & b_0 & 0 \\ b_2 & b_1 & b_0 \\ 0 & b_2 & b_1 \\ 0 & 0 & b_2 \end{bmatrix} \begin{bmatrix} a_0 \\ a_1 \\ a_2 \end{bmatrix} = \begin{bmatrix} b_0 a_0 \\ b_1 a_0 + b_0 a_1 \\ b_2 a_0 + b_1 a_1 + b_0 a_2 \\ b_2 a_1 + b_1 a_2 \\ b_2 a_2 \end{bmatrix} .$$

(2.7)

Similarly, a convolutional layer's computation in (2.6) can be mapped to a matrixmatrix multiplication C = AB [12], where each row of the A matrix is formed from

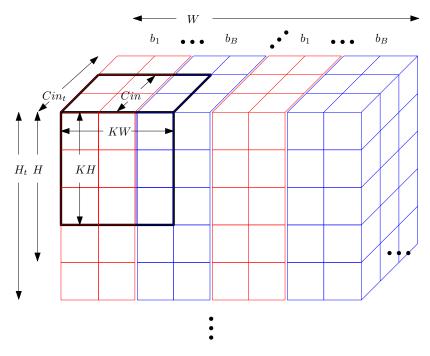

Figure 2.3: Example of a convolutional layer in Alexnet [11]. The bottom portion of the figure shows a convolutional layer where N = 1,  $C_{in} = 3$ ,  $C_{out} = 48$ , H = W = 55,  $H_k = W_k = 11$ , and  $H_s = W_s = 4$ . The input feature maps have a width of 224 (before padding), and the next convolutional layer that is partially shown has a kernel size of  $H_k = W_k = 11$ .

the  $X^{(d-1)}$  elements by iterating through the indices in (2.6) as described below:

$$\mathbf{A}[i][j] = \mathbf{X}^{(\mathbf{d}-1)}[N][c_{in}][hH_s + h_k][wW_s + w_k], \qquad (2.8)$$

where:

$$i = nC_{in}HW + hW + w \tag{2.9}$$

$$j = c_{in}H_kW_k + h_kW_k + w_k. (2.10)$$

Each column j of the B matrix is formed from  $\mathbf{W}^{(d)}$  by collapsing the  $C_{in}$ ,  $H_k$ ,  $W_k$

dimensions of  $W[c_{out}]$  as described below:

$$\mathbf{B}[i][j] = \mathbf{W}^{(\mathbf{d})}[c_{out}][c_{in}][h_k][w_k].$$

(2.11)

where:

$$i = c_{in}H_kW_k + h_kW_k + w_k \tag{2.12}$$

$$j = c_{out} \,. \tag{2.13}$$

#### 2.1.3 Transformers and Attention Layers

Transformer models, introduced in 2017 [13], are a more recent deep learning model that has since been shown to be superior in quality in many popular benchmarks compared to prior deep learning models like CNNs, and it is the base model used in popular works such as BERT [14] and GPT [15] models. The computationally intensive portion of transformer models are based around the following operations, which mainly consist of a sequence of large matrix multiplications as shown below:

Attention(

$$\mathbf{Q}, \mathbf{K}, \mathbf{V}$$

) = softmax( $\frac{\mathbf{Q}\mathbf{K}^{\mathrm{T}}}{\sqrt{d_{k}}}$ ) $\mathbf{V}$  (2.14)

$$\mathbf{H}_{i} = \text{Attention}(\mathbf{Q}\mathbf{W}_{i}^{\mathbf{Q}}, \mathbf{K}\mathbf{W}_{i}^{\mathbf{K}}, \mathbf{V}\mathbf{W}_{i}^{\mathbf{V}}) \tag{2.15}$$

$$MultiHead(\mathbf{Q}, \mathbf{K}, \mathbf{V}) = Concat(\mathbf{H}_1, ..., \mathbf{H}_h)\mathbf{W}^{\mathbf{O}}, \qquad (2.16)$$

where all bolded variables are matrices, and all matrices and variables are either derived from layer inputs or are a form of pretrained weight values or constants.

While the methods presented in our work may be well suited for accelerating these

types of deep learning models, further descriptions of transformer models and exploration of their acceleration are considered out of the scope of this thesis and left as a future work.

#### 2.1.4 Commonality

As shown in this section, the computationally most intensive portions of many common DNN models used today are based around the few types of neural network layers discussed above which can all mainly reduce to matrix multiplication. Therefore, increasing the efficiency of general matrix multiplication (GEMM) is a key area of interest to focus on for advancing the field of deep learning hardware acceleration.

### 2.2 Deep Learning Hardware Acceleration

This section provides a literature review of a range of prior works and common strategies used to improve the acceleration of deep learning workloads in custom hardware. It is impossible to evaluate all possible approaches and works due to the popular and fast-paced nature of this field. Nonetheless, we review a representative range of strategies and works relevant to the contributions in this thesis.

#### 2.2.1 Systolic Arrays

Systolic arrays, which will also be referred to as matrix multiplication units (MXU)s for convenience, are an effective choice for use in GEMM accelerators as they significantly reduce the required memory traffic and can reach high clock frequencies due to their short and regular interconnects. Systolic-array architectures have been used in state-of-the-art GEMM and deep learning accelerators such as the Tensor Processing Unit (TPU) [3], [5],

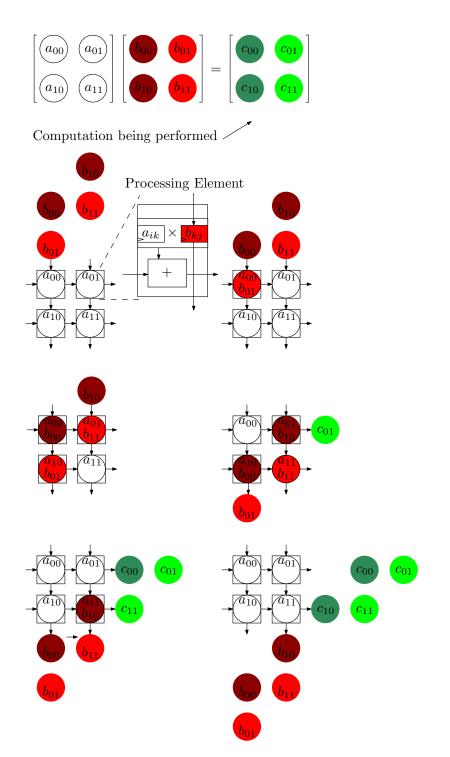

Figure 2.4: Demonstrating how matrix multiplication is performed on a systolic array of processing elements.

#### [6], among others [8], [16].

A systolic array consists of a 2-D array of simple connected processors. Each processor typically consists of only a multiplier and adder unit, and the processors pass data to adjacent processors in a consistent pattern, demonstrated in Figure 2.4. This makes the wire connections between processors very short and regular and increases the clock frequency of the circuit. In contrast, the processor arrays in GPUs can contain multiple longer and more complex physical connections between the various components and a central control unit.

This makes systolic arrays very efficient for deep learning acceleration. For example, while an 8-core CPU might be able to perform up to 8 multiplications or additions per clock cycle, systolic array accelerators such as the Google TPU will perform up to 64K multiplication and additions per clock cycle.

#### Multi-Systolic-Array Systems

However, a systolic array can only be fully utilized when the input matrix sizes at minimum match the dimensions of the systolic array or are larger, and real workloads have limits to the matrix sizes being multiplied. For example, the average matrix size that the computations reduce to in ResNet [17] DNN models are in the range of approximately  $300 \times 2000$ . There is then a limit to how fast the workload can be accelerated on a single systolic array design because, even if more compute resources are instantiated to scale up the size of the systolic array, the systolic array will begin to be underutilized after its size surpasses the workload's matrix sizes, and the workload will not be able to execute any faster.

This is particularly true in modern workloads such as DNN acceleration, where the matrix sizes that the workloads break down to are smaller than the maximum systolic array

size that could be instantiated in an accelerator. To combat this, multiple smaller systolic arrays can be used in parallel [5], [6], [18], [19], which allows for the total compute power in the systolic-array system to increase while the minimum supported matrix sizes remain the same.

#### 2.2.2 Quantization

The weight and layer inputs to a DNN can be scaled and given an offset such that they are represented on integer values [20]. The bitwidth of the representation in practice can range from 16 bits [21] to an extreme of 1 bit [22] [23] [24]. Following this quantization, GEMM can be performed directly with the integer values, and a re-scaling and new offset are given between each layer.

The benefit of using small-width integers instead of the conventional 32-bit floatingpoint (FP32) representation is very significant for hardware acceleration. The values are represented by fewer bits, which frees up space in memory and also reduces the memory bandwidth required to read/write the values from/to memory. Additionally, small-width integer arithmetic units consume far fewer hardware resources than their FP32 counterparts [25]. Table 3 from the work by Guo et al. [25] shows that an 8-bit adder or multiplier consumes roughly 10x fewer resources than a FP32 multiplier or adder on a Xilinx FPGA.

For 1-bit quantization, the XNOR operation is performed on the data instead of multiplication, followed by a bit count operation. These operations can be efficiently implemented using look-up tables (LUT)s which are one of the base logic elements used in FPGAs to allow for their re-programmable logic. Taking this concept further, networks with LUT-based neurons [26] have been explored. Modern FPGAs usually contain LUTS that can be programmed to perform any desired function which takes 6-7 binary inputs and produces 1-2 binary outputs. On the other hand, an XNOR operation takes 2 binary inputs and produces 1 binary output. This means that the number of XNOR operations that can be implemented per LUT will be constrained by the number of LUT outputs, and each LUT can then only implement at most 2 XNOR operations, which would consume at most 4 inputs, leaving 2-3 inputs unused. Therefore, a LUT-based network could use more accurate larger-than-1-bit inputs to make use of these unused LUT inputs, while consuming the same number of LUTs as a binary network using 1-bit inputs and XNOR operations.

The study from Nurvitadhi et al. [27] tested FPGA accelerators designed to support 8-bit and binary (1-bit) data and compared it to an accelerator designed for FP32 data. The 8-bit and binary designs had roughly an 8x and 75x increase in peak performance per watt, respectively, compared to the FP32 design. It has been shown that negligible error is introduced for as low as 8-bit representations [25]. For bitwidths below this, however, noticeable increases in error start to be introduced.

#### 2.2.3 Precision-Scalable Architectures

Precision-scalable architectures allow for a way to efficiently execute workloads across multiple input precisions for applications where the input bitwidths are expected to vary [28], [29], [30], [31], [32], [33], [34], [35], [36], [37], [38], [39], [40], [41]. Deep learning acceleration is a great use-case for precision-scalable hardware architectures, where neural networks can perform the majority of their inference on reduced-bitwidth operations with little to no loss in accuracy but the bitwidths required to provide sufficient accuracy vary across different deep neural network models, applications, and between individual layers within the same neural network model [28]. For example, some neural network models can be executed with high accuracy even when performing the majority of the operations

on small bitwidths, however, a smaller portion of the layers still need to be computed on larger bitwidths to preserve accuracy [28]. Therefore, a fixed-bitwidth accelerator must make a trade-off between either supporting only lower bitwidths while reducing the model's accuracy, or supporting larger bitwidths for higher accuracy but under-utilizing the MAC units during majority of computation as most stages require only lower-bit inputs.

Precision-scalable architectures address this trade-off by providing structures that can more efficiently support execution of varying input bitwidths. These designs are less optimized for accelerating inputs of a fixed bitwidth compared to a design made specifically for that certain bitwidth, however, they have the flexibility to provide more efficient acceleration when executing on other bitwidths. One approach is to use MAC units consisting of multiple smaller-bitwidth multipliers [29] which can either be individually used to multiply/accumulate multiple smaller-bitwidth products, or they can be reconfigured to collectively multiply/accumulate fewer larger-bitwidth products per clock cycle. Another approach referred to as bit-serial architectures [30], is to have MAC arrays which repeatedly perform fixed-size smaller-bitwidth vector operations on different bit slices of the vectors, summing up the separate vector products to get the final full-bitwidth result.

#### 2.2.4 **Pruning and Sparsity**

Pruning is a technique in which a neural network is intentionally trained in such a way that many of its weights become zero-valued. For example, it has been shown that AlexNet can be pruned so that 85% of the weights in the convolutional layers are removed with less than 1% degradation in accuracy [42]. This provides potential speedup opportunities for accelerators as the calculations then decompose to sparse GEMM, and all of the multiplications with zero values can be skipped.

In the works by Parashar et al. [43] and Zhang et al. [44], compression schemes for weights and intermediate data were developed such that they are stored in a compressed form and require fewer data transfers and fewer storage requirements throughout computation. In the study from Nurvitadhi et al. [27], an FPGA accelerator design for sparse networks gave a 4x speedup on FP32 data compared to their accelerator for dense FP32 models.

Criticisms of this technique are that creating a hardware design capable of scheduling zero skipping prevents the design from reaching the same high clock frequency as a systolic array architecture suitable only for dense GEMM [27]. For example, the sparse GEMM accelerator design from Nurvitadhi et al. [27] ran at a frequency of 300 MHz vs 440 MHz for the dense GEMM systolic array accelerator. Furthermore, quantizing pruned networks to integer widths under 12 bits can introduce large accuracy degradation [45], preventing the sparse GEMM engines from taking advantage of the many benefits of using small-width integer arithmetic 2.2.2.

#### 2.2.5 Memory Optimizations

While GEMM requires a large amount of computational power, it also requires large amounts of data to be moved and accessed by the computational logic [46]. Additionally, off-chip memory accesses can have higher energy costs than other operations [47]. Due to this, memory bandwidth, especially for off-chip memory access, can be a performance bottle-neck or energy concern. To address this, prior works have proposed solutions to mitigate these issues [46] [47] by increasing data reuse and using efficient data tiling and caching techniques. Additionally, quantization [20] and sparse neural networks [42] are used to reduce memory bandwidth requirements as discussed in Sections 2.2.2 and 2.2.4.

algebraic optimizations and hardware architectures proposed in this thesis are generally orthogonal to memory bandwidth optimizations and both techniques can be used in combination with each other.

#### 2.2.6 Hardware Architecture Design Automation

It can be a difficult engineering feat to design a single deep learning accelerator that supports execution of a wide range of DNN models like the Google TPU [3], [5], [6]. Furthermore, it may be possible to make certain design choices that are more resource-efficient when optimizing a hardware design for one specific DNN model. Prior works have explored automated design flows which map a neural network described in a deep learning software framework like Caffe [21] or Pytorch [48], and automatically generate an FPGA accelerator design optimized for that DNN model based on the target FPGA platform [49] [50] [51] [52] [53] [54] [55].

These design space exploration methods can automatically derive architectural features such as efficient off-chip memory layouts and efficient systolic array dimensions based on the DNN layer sizes and an FPGA platform's resource limitations. Pseudocode with for loops is derived to model a layer's computational schedule and represent the order in which data is fed into the systolic array, and the loop tile sizes can be used to model the dimensions of the systolic array. In some cases, automated loop transformations are applied to the layer's pseudocode in order to find transformations for increasing data reuse, reducing off-chip bandwidth, and increasing on-chip parallelization in the automatically generated designs [53] [16].

In the work by Wang et al. [56], a flow is presented for generating an FPGA design for a CNN model based on the dimensions and weights of a model obtained from Caffe [21]. The method chooses architecture elements obtained from a library of hand-coded Verilog to maintain more low-level optimizations than other techniques. Additionally, unlike other methods, the analysis works for highly irregular network topologies such as in GoogleLeNet [57] and ResNet [17] DNN models.

The loop transformation methods mentioned above use more trivial applications of an otherwise more robust compiler optimization theory called polyhedral compilation [58] [59]. Polyhedral compilation has been included in many compiler libraries including GCC [60] and LLVM [61]. In polyhedral compilation, all iterations of a loop nest are represented as different integer points in a space, all of which form a polytope that can be transformed as a whole, rather than manipulating individual iterations. The dependencies between different iterations are also modeled in this manner. Affine transformations on the polytopes can be found that produce execution schedules that reduce the average dependency distance between iterations to improve data reuse/locality. These techniques have also been used in DNN accelerator design automation [16] [55].

The techniques discussed in this subsection provide the opportunity for an additional level of optimization in an accelerator design by producing hardware designs optimized for specific DNN models and FPGA platforms. On the other hand, this prevents the designs from being suitable for ASIC implementation, which is inherently more optimized than FPGA designs. It also complicates usage scenarios where more than one single DNN model may be required to run on the accelerator, which may be a more practical real-life usage scenario. Furthermore, it has been shown by works such as Google's TPU design [3], [5], [6] that it is possible to make one hardware design that is highly efficient but still supports the execution of a wide range of DNN models.

#### 2.2.7 Hardware-Oriented DNN Model Design Automation

The architecture of a DNN model can be designed from the ground up in such a way that it can be executed more effectively on a specific hardware platform. The DNN model can be designed to support a given throughput and latency constraint based on given hardware budget or available hardware resources on a given hardware platform such as the on/offchip memory size, total registers, and/or total DSP units on the device. The design space dimensions can include the types of layers to use, size of the layers, as well as the pruning severity and quantization widths.

In the work from Jiang et al. [62], a method is presented in which the design space exploration steps first choose a DNN model and generate an FPGA design to accelerate it that meets certain throughput specifications. Other model designs are then explored in search of ones that reduce the implied hardware accelerator resource requirements. Next, the selected model architecture is trained and fine-tuned such that results providing both higher accuracy and hardware efficiency are rewarded. This has also been done specifically for mapping execution of binarized neural networks to a hardware platform [23]. DNN model architecture/hardware accelerator architecture co-design has also been explored in the work by Abdelfattah et al. [63], where a DNN model was produced that has 1.3% better accuracy than ResNet [17] on certain metrics, while at the same time, the resulting hardware accelerator architecture per area by 41%.

These methods have the benefit of making a DNN model meet given latency and throughput constraints on a wider range of devices. On the other hand, it restricts the usage of more well-known DNN models that might be already pre-trained on large data sets and have more well-analyzed success/error rates.

#### 2.2.8 Fast Convolution Algorithms

In 1980, Winograd presented a minimal-filtering algorithm [64] showing that the operations in a convolution can be re-arranged such that fewer multiplications and additions are performed for the same result compared to conventional convolution algorithms. The work from Lavin et al. [65] shows how this algorithm can be substituted into the compute pattern for convolutional layers of CNNs, resulting in a speedup of  $2\times$  or more in throughput for these layers. Furthermore, the algorithm can be used to speed up the computation in both custom hardware architectures as well as in software running on CPUs or GPUs. This algorithm has since been exploited in numerous CNN accelerator works [66] [67] [68].

This method is the most similar approach to the methods explored in this thesis of advancing and applying efficient algebraic algorithms to deep learning hardware architectures. While the work from Lavin et al. [65] provided a good initiative in this direction, the hardware research community has since focused primarily on application of this one efficient algebraic technique which is only beneficial for speeding up convolutional layers. However, as revealed in the work from this thesis, there are multiple other underexplored efficient algebraic algorithms that can be extended and applied to deep learning hardware architectures. Furthermore, the methods from this thesis are based around speeding up matrix multiplication and are therefore applicable to speeding up a wider range of common DNN model layers including fully-connected, convolutional, recurrent, and attention/transformer layers. Finally, the Winograd convolution technique [65] still results in matrix multiplication, which may therefore still be complementary to our methods and applicable in addition to the techniques presented in this thesis.

# 2.3 Efficient Algebraic Algorithms

As shown in Section 2.2, recent years have seen many works on hardware-oriented DNN model optimizations and system-level improvements for deep learning hardware architectures. At a certain point, however, after hardware-oriented DNN model optimizations reach their limit, after the known parallelism and system-level optimizations for executing their compute patterns are exploited, and after technology scaling slows to a halt, there is an accelerator wall which causes limited improvement on the implementation side [69]. A less-explored avenue to continue advancement after this point is to reduce the workload at the algebraic level, by calculating the same deep learning model algebra, nevertheless using a re-arranged compute pattern which produces the same output from fewer or cheaper operations performed in hardware.

Consider the matrix multiplication C = AB for A of size  $M \times K$  and B of size  $K \times N$ . Using the conventional inner product, C is calculated from MNK multiplications and MN(K-1) additions, where each element  $c_{i,j}$  of C is calculated as follows:

$$c_{i,j} = \sum_{k=1}^{K} a_{i,k} b_{k,j} \,. \tag{2.17}$$

As discussed in Section 2.1, the majority of the computational workload in deep learning models can commonly be mapped to the matrix multiplication shown in (2.17), and as can be seen, the operations in this equation are a series of multiply-accumulate operations. For all deep learning accelerators, unless additional algebraic innovations are used, the throughput is ultimately limited by the maximum number of multiply-accumulate operations from (2.17) that can be performed per clock cycle. Due to this, deep learning accelerators contain a large number of MAC units, causing multipliers and MAC units to commonly be one

of the area-dominant resources in GEMM and deep learning accelerators [70], [3], [5], and an accelerator's throughput can be directly limited by how many multipliers its hardware budget can afford.

As a result, surpassing this theoretical performance per multiplier limit should be a key area of interest for advancing the field of deep learning hardware acceleration. As discussed in Section 2.2.8, this approach has been touched upon with Winograd's minimal filtering algorithms applied to convolutional neural networks (CNN)s [65], [64], [66], [70]. However, this algorithm is applicable only to CNN deep learning models, and there are numerous other efficient algebraic algorithms that are also applicable to GEMM and therefore a broader range of DNN models.

In this thesis, we continue in this under-explored direction and provide further algebraic enhancements for matrix multiplication algorithms and their custom hardware implementations for the application of deep learning acceleration. This section provides the necessary background on prior efficient algebraic algorithms and their hardware implementations outside the application of deep learning to build the foundation for our contributions.

#### **2.3.1** Fast Inner Product (FIP)

In 1968, Winograd introduced an alternative inner-product algorithm [7] that we refer to as the Fast Inner Product (FIP). Compared to the traditional inner product in (2.17), FIP allows matrix multiplication to be performed with approximately half of the multiplication and accumulation operations traded for low-bitwidth additions. In FIP [7], each element  $c_{i,j}$  of C is calculated as follows:

$$c_{i,j} = \sum_{k=1}^{K/2} (a_{i,2k-1} + b_{2k,j})(a_{i,2k} + b_{2k-1,j}) - \alpha_i - \beta_j, \qquad (2.18)$$

where:

$$\alpha_i = \sum_{j=1}^{K/2} a_{i,2j-1} \cdot a_{i,2j} \tag{2.19}$$

$$\beta_j = \sum_{i=1}^{K/2} b_{2i-1,j} \cdot b_{2i,j} \,. \tag{2.20}$$

For even K, calculating C then requires the following number of multiplications:

$$\frac{MNK + MK + NK}{2}, \qquad (2.21)$$

and the following number of additions:

$$\frac{3 \cdot MNK + MK + NK}{2} - MN - M - N.$$

(2.22)

This means that an accelerator performing this equation instead of (2.17) can trade nearly half of its multipliers for low-bitwidth adders while achieving the same throughput. Since the hardware footprint of fixed-point multipliers dominates that of adders [71], [25], [72], FIP can theoretically significantly improve the throughput per compute area roof of an accelerator, where *roof* refers to the upper bound of that metric and *compute area* refers to the area of computational logic used to perform arithmetic operations. Despite the high impact potential of these benefits, the FIP algorithm [7] has never before been implemented in a deep learning hardware accelerator.

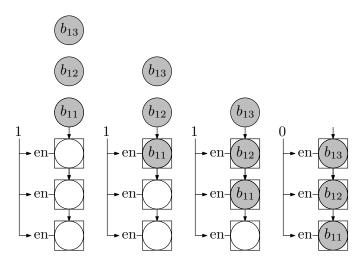

#### **Custom FIP Hardware Architectures**

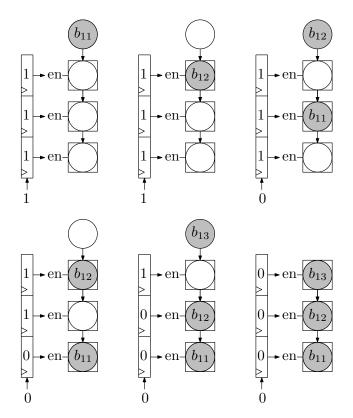

The FIP algorithm [7] has been explored by Gustafsson et al. for application to finite impulse response (FIR) filtering [73] in a non-systolic-array architecture proposal. Three prior works have also been proposed for systolic-array architectures for exploiting FIP [74] [75] [76].