# DEVELOPMENT OF AN OPTIMIZATION TOOL FOR THE GEOMETRY OF INTEGRATED POWER MODULE PIN FIN ARRAYS EMPLOYED IN ELECTRIFIED VEHICLES

# DEVELOPMENT OF AN OPTIMIZATION TOOL FOR THE GEOMETRY OF INTEGRATED POWER MODULE PIN FIN ARRAYS EMPLOYED IN ELECTRIFIED VEHICLES

BY

HASSAN ALEIAN, B.Eng.

A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

AND THE SCHOOL OF GRADUATE STUDIES

OF MCMASTER UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

© Copyright by Hassan Aleian, August 2021

All Rights Reserved

| Master of Applied Science (2021)      | McMaster University       |

|---------------------------------------|---------------------------|

| (electrical and computer engineering) | Hamilton, Ontario, Canada |

TITLE:

Development of an Optimization Tool for the Geometry

of Integrated Power Module Pin Fin Arrays Employed in

Electrified Vehicles

AUTHOR: Hassan Aleian B.Eng. (Electrical Engineering), McMaster University, Hamilton, Ontario, Canada

| SUPERVISOR: | Dr. Ali Emadi      |

|-------------|--------------------|

|             | Dr. Mehdi Narimani |

NUMBER OF PAGES: xv, 156

### Abstract

The mass-market adoption of electrification in the transportation sector mandates stringent and aggressive requirements in terms of cost, power rating, efficiency, power density, and specific density of power electronics. Modular packaging of power electronics is advantageous and thus ubiquitously used by the automotive industry. A trend of shrinking die sizes and increased integration is evident and will inevitably continue. The thermal management system has become ever more significant as it is one of the main obstacles to higher power densities. The cooling system must be cost-effective, simple, efficient, reliable, and compatible with system requirements.

Pin fins are a reliable and effective means of augmenting heat transfer. They rely on inducing turbulence, increasing the effective wetted surface, and accelerating fluid velocity. Unavoidably the pin fin array also produces an undesirable pressure drop that is commensurate to the pumping power required for the system. In this thesis, a tool is developed for the geometry optimization of pin fin arrays to dissipate the heat at a rate large enough to ensure junction temperatures do not exceed the maximum value possible at a minimal pressure drop. It is hoped that this tool would contribute to the multi-physics optimization and integration of power electronics for electrified vehicles. This optimization is confined to equalaterally spaced short pin fins, aspect ratios less than three. The tool employs empirical correlations since flow is too complex to solve analytically and numerical solutions or CFD-simulations are too time and computationally extensive.

The tool development is done in a comprehensive manner. Starting from the first principles of a two-level voltage source inverter's operation. Next, the inevitable power losses from the operation are explained and a method for their calculations is presented. Correlations in the literature related to both pressure drop and heat transfer are reviewed afterward. Then the methodology of the construction of the tool is explicated in detail. Employing a commercial power module to benchmark results; three scenarios with different flow rates and inlet temperatures are optimized for. Simulations in ANSYS Fluent are run to verify the accuracy of correlations used in the tool. Comparing the optimized geometry of pin fins to the original benchmarking geometry it is evident that employing this tool on a per-application basis provides superior performance.

## Acknowledgements

In part, this research is possible thanks to funding from the Natural Sciences and Engineering Research Council of Canada (NSERC). Special thanks goes to my supervisors Dr. Ali Emadi, and Dr. Mehdi Narimani, for all the guidance, advice, support, and mentorship that they provided to me. All of the things I learned during my Master's degree is primarily due to the opportunities made possible by them. I also want to thank everyone who is a member of the McMaster Automotive Resource Center (MARC) team, working as a part of this team was both a pleasure, and an honour for me.

Also, I would like to express my gratitude for being provided an opportunity to work in the power electronics research thrust area (PE RTA) project at MARC in collaboration with Fiat Chrysler Automobile (FCA). This project, lead by Dr. Berker Bilgin, was one of the highlights of my Master's degree. I am very thankful to Dr. Berker Bilgin, working on his team we gained a lot from both the technical and project management sides. He had unbounded faith in the team and managed to teach, lead, and inspire us through challenges, allowing us to always deliver results by the deadlines we had set. Even during the unprecedented COVID virus pandemic, the team continued to make progress, while, of course, taking all the safety precautions necessary. Fatemeh Abolqasemi, Alex Wang, and Jigar Mistry were also members of this team who contributed to my learning and overall experience at MARC. Although the overlap of Dr. Jing Guo and my time in this project didn't last long, she generously taught me an abundance of things in the early days of my work in the FCA PE RTA. After Dr. Jing Guo left the group, Dr. Peter Azer, a very good friend, took a more leading role in the PE RTA. I want to thank Peter for generously and frequently giving his time, knowledge, and advise, and I found that going to Dr. Azer was always fruitful.

I really appreciate Maryam Alizadeh who was very helpful in my early days working on thermal design for PE. This was when I became very interested in thermal design, leading me to do my thesis in this area of study. I am grateful to my good friend Sobhan Kashfi; he and I had many discussions related to thermal design, and he proved to be very helpful throughout my journey in this fascinating field. I would also like to take this opportunity to remember my dear friends and colleagues at MARC, Mehdi Eshaghian and Iman Aghabali, who perished in flight PS752, they were both close friends who will live on in our hearts and memories.

Lastly, a special thanks goes to my beloved parents, and siblings, for their unconditional love, and support, throughout my life.

# Contents

| A        | bstra | istract    |                                                                           |    |

|----------|-------|------------|---------------------------------------------------------------------------|----|

| A        | ckno  | wledge     | ements                                                                    | v  |

| 1        | Intr  | troduction |                                                                           |    |

|          | 1.1   | Backg      | round                                                                     | 1  |

|          | 1.2   | Motiv      | ation                                                                     | 3  |

|          | 1.3   | Thesis     | s Objectives                                                              | 4  |

|          | 1.4   | Thesis     | s Outline                                                                 | 6  |

| <b>2</b> | Ope   | eration    | of Two-Level Voltage Source Inverter                                      | 8  |

|          | 2.1   | Introd     | luction                                                                   | 8  |

|          | 2.2   | Topol      | ogy                                                                       | 10 |

|          | 2.3   | Modu       | lation Schemes                                                            | 13 |

|          |       | 2.3.1      | Sinusoidal Pulse Width Modulation (SPWM) $\ldots \ldots \ldots$           | 14 |

|          |       | 2.3.2      | Space Vector Modulation (SVM) $\ldots \ldots \ldots \ldots \ldots \ldots$ | 17 |

|          |       | 2.3.3      | SPWM with Zero Sequence Signal Injection                                  | 24 |

|          |       | 2.3.4      | Six Pulse Modulation                                                      | 28 |

|          | 2.4   | Summ       | nary                                                                      | 30 |

| 3        | Pov | ver Losses in Two-Level Voltage Source Inverters                | <b>31</b> |

|----------|-----|-----------------------------------------------------------------|-----------|

|          | 3.1 | Introduction                                                    | 31        |

|          | 3.2 | Switch Operation                                                | 32        |

|          |     | 3.2.1 Diode Operation                                           | 32        |

|          |     | 3.2.2 IGBT Operation                                            | 34        |

|          | 3.3 | Conduction Losses                                               | 38        |

|          |     | 3.3.1 Diode Conduction Losses                                   | 40        |

|          |     | 3.3.2 IGBT Conduction Losses                                    | 40        |

|          | 3.4 | Switching Losses                                                | 41        |

|          |     | 3.4.1 Double Pulse Test                                         | 41        |

|          |     | 3.4.2 Dynamic Switching Behavior                                | 47        |

|          |     | 3.4.3 Ascertaining Switching Energy                             | 65        |

|          | 3.5 | Switching Power Losses                                          | 66        |

|          | 3.6 | Total Power Loss                                                | 67        |

|          | 3.7 | Summary                                                         | 68        |

| 4        | Rev | view of The Heat Transfer and Flow Characteristics of Staggered | l         |

|          | Pin | Fins Used for Power Module Cooling Applications                 | 69        |

|          | 4.1 | Introduction                                                    | 69        |

|          | 4.2 | Heat Transfer                                                   | 72        |

|          |     | 4.2.1 Average Array Heat Tranfer Assuming Uniform Flow          | 72        |

|          | 4.3 | Pressure Drop                                                   | 86        |

|          | 4.4 | Summary                                                         | 89        |

| <b>5</b> | Des | sign of Pin Fin Heat Sink                                       | 91        |

#### viii

|   | 5.1 | Introd  | luction                                                                                              | 91  |

|---|-----|---------|------------------------------------------------------------------------------------------------------|-----|

|   | 5.2 | Proble  | em Setup and Objectives                                                                              | 93  |

|   |     | 5.2.1   | power losses                                                                                         | 98  |

|   | 5.3 | Model   | ling                                                                                                 | 99  |

|   |     | 5.3.1   | Basis for Heat Transfer Model                                                                        | 100 |

|   |     | 5.3.2   | Implementation of Heat transfer Model                                                                | 105 |

|   |     | 5.3.3   | Basis of Pressure Drop Correlation                                                                   | 108 |

|   |     | 5.3.4   | Implementation of a pressure drop model                                                              | 109 |

|   | 5.4 | Optim   | nization                                                                                             | 111 |

|   |     | 5.4.1   | Optimization Metric                                                                                  | 111 |

|   |     | 5.4.2   | optimization method $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 115 |

|   | 5.5 | Summ    | ary                                                                                                  | 115 |

| 6 | Res | ults ar | nd Simulations                                                                                       | 117 |

|   | 6.1 |         | luction                                                                                              | 117 |

|   | 6.2 |         | ng Optimization Problem                                                                              | 118 |

|   | 6.3 |         | S                                                                                                    | 121 |

|   |     | 6.3.1   | Finding Minimum Acceptable Effective Heat Transfer Coefficien                                        |     |

|   |     | 6.3.2   | Obtaining Optimum Geometry Variables                                                                 |     |

|   | 6.4 |         | Simulation Studies                                                                                   | 127 |

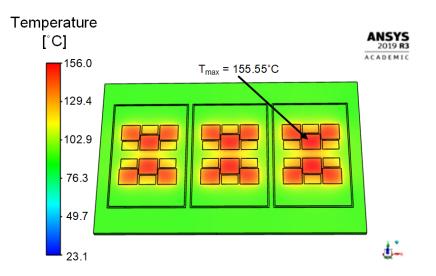

|   | 0   | 6.4.1   | Benchmarking Pin Fin Geometry Simulation                                                             | 129 |

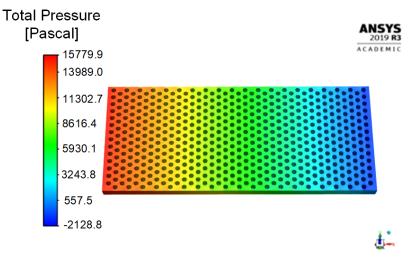

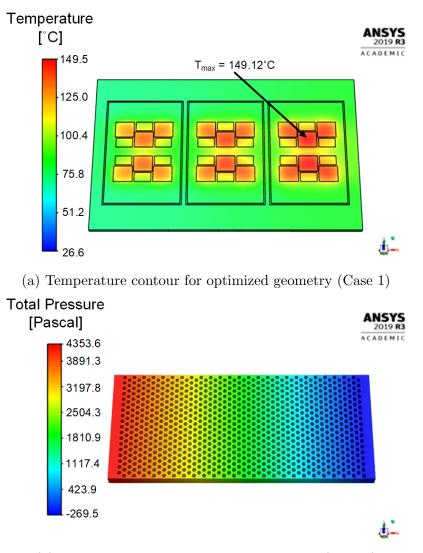

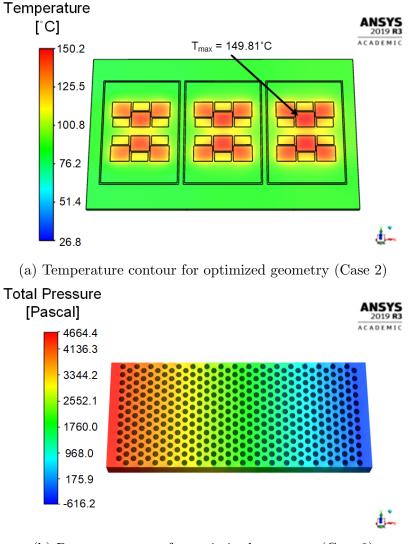

|   |     | 6.4.2   | Optimized Pin Fin Geometry Simulation                                                                | 133 |

|   | 6.5 |         |                                                                                                      | 137 |

|   | 6.6 |         |                                                                                                      | 197 |

|   | 0.0 | Summ    | lary                                                                                                 | 141 |

| 7 | Cor | nclusio | ns and Future Work                 | 142 |

|---|-----|---------|------------------------------------|-----|

|   | 7.1 | Summ    | ary                                | 142 |

|   | 7.2 | Contri  | ibutions                           | 145 |

|   | 7.3 | Future  | e Work                             | 146 |

|   |     | 7.3.1   | Heat Spreading Model               | 146 |

|   |     | 7.3.2   | Transient Thermal Analysis         | 147 |

|   |     | 7.3.3   | Vapor Chamber Baseplate            | 148 |

|   |     | 7.3.4   | Cooling techniques Studies         | 148 |

|   |     | 7.3.5   | Empirical Correlation Improvements | 148 |

|   |     |         |                                    |     |

#### References

150

# List of Figures

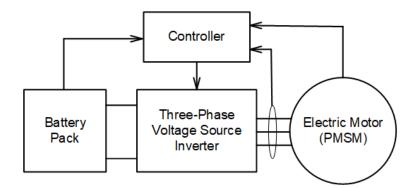

| 2.1 | Typical EV Powertrain                                                          | 9  |

|-----|--------------------------------------------------------------------------------|----|

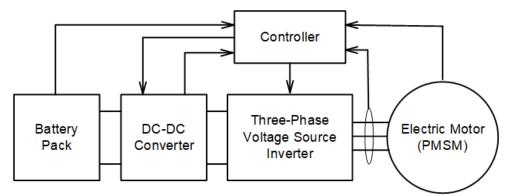

| 2.2 | Powertrain with DC-DC Converter                                                | 10 |

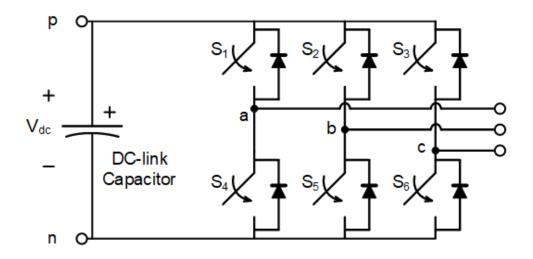

| 2.3 | Three-Phase Voltage Source Inverter                                            | 11 |

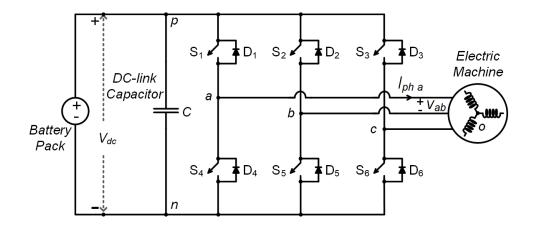

| 2.4 | Three-Phase Voltage Source Inverter                                            | 13 |

| 2.5 | SPWM for single phase-leg                                                      | 14 |

| 2.6 | Waveforms used to implement SPWM                                               | 17 |

| 2.7 | Space Vector Modulation Complex Plane Representation                           | 23 |

| 2.8 | SPWM with Zero-Sequence Injection                                              | 26 |

| 2.9 | 6-step modulation waveforms                                                    | 29 |

| 3.1 | Representative circuit diagram symbol for Diodes $\ldots \ldots \ldots \ldots$ | 32 |

| 3.2 | I/V Characteristics For a Diode portraying the different regions of            |    |

|     | operation                                                                      | 33 |

| 3.3 | Diode Equivalent Circuit in Forward Biased Mode                                | 34 |

| 3.4 | IGBT Circuit Diagram Symbol                                                    | 35 |

| 3.5 | Typical Output Characteristics of IGBT                                         | 35 |

| 3.6 | Typical Transfer Characteristics of IGBT depicting both the Active             |    |

|     | and Cut-off regions with the a Transconductance $g_m$                          | 37 |

| 3.7  | IGBT on-state equivalent model, includes a diode in series with a MOS-        |    |

|------|-------------------------------------------------------------------------------|----|

|      | FET in linear operation                                                       | 38 |

| 3.8  | Double Pulse Testing Setup                                                    | 42 |

| 3.9  | Double Pulse Testing Intervals defining turn on and turn off instants         | 43 |

| 3.10 | Interval i of Double Pulse Test in static operation $(t_0 < t < t_1)$         | 44 |

| 3.11 | Interval ii of Double Pulse Test in static operation $(t_1 < t < t_2)$        | 45 |

| 3.12 | Interval iii of Double Pulse Test in static operation $(t_2 < t < t_3)$       | 46 |

| 3.13 | Equivalent circuit of the IGBT during switching                               | 47 |

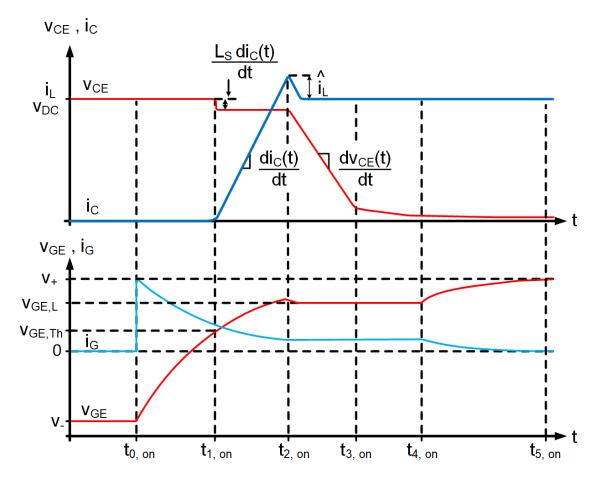

| 3.14 | Switching Waveform of IGBT $T_2$ Turn ON [24]                                 | 48 |

| 3.15 | Interval 1 of turn on: $(t < t_{0,on})$ of equivalent circuit with current    |    |

|      | commutation path $[24]$                                                       | 49 |

| 3.16 | Interval 2 of turn on: $(t_{0,on} < t < t_{1,on})$ of equivalent circuit with |    |

|      | current commutation path [24]                                                 | 51 |

| 3.17 | Interval 3 of turn on: $(t_{1,on} < t < t_{2,on})$ of equivalent circuit with |    |

|      | current commutation path [24]                                                 | 54 |

| 3.18 | Reverse Recovery Current that ejects stored charges in diode allowing         |    |

|      | for blocking                                                                  | 54 |

| 3.19 | Interval 4 of turn on: $(t_{2,on} < t < t_{3,on})$ of equivalent circuit with |    |

|      | current commutation path [24]                                                 | 55 |

| 3.20 | Interval 5 of turn on: $(t_{3,on} < t < t_{4,on})$ of equivalent circuit with |    |

|      | current commutation path [24]                                                 | 56 |

| 3.21 | Interval 6 of turn on: $(t_{4,on} < t < t_{5,on})$ of equivalent circuit with |    |

|      | current commutation path [24]                                                 | 57 |

| 3.22 | Switching Waveforms when IGBT $T_2$ is turned off [24]                        | 58 |

| 3.23 | Interval 1 of turn off: $(t < t_{0,off})$ of equivalent circuit with current             |    |

|------|------------------------------------------------------------------------------------------|----|

|      | commutation path $[24]$                                                                  | 60 |

| 3.24 | Interval 2 of turn off: $(t_{0,off} < t < t_{1,off})$ of equivalent circuit with         |    |

|      | current commutation path [24]                                                            | 61 |

| 3.25 | Interval 3 of turn off: $(t_{1,off} < t < t_{2,off})$ of equivalent circuit with         |    |

|      | current commutation path [24]                                                            | 62 |

| 3.26 | Interval 4 of turn off: $(t_{2,off} < t < t_{3,off})$ of equivalent circuit with         |    |

|      | current commutation path $[24]$                                                          | 62 |

| 3.27 | Interval 5 of turn off: $(t_{3,off} < t < t_{4,off})$ of equivalent circuit with         |    |

|      | current commutation path [24]                                                            | 64 |

| 3.28 | Interval 6 of turn off: $(t_{4,off} < t < t_{5,off})$ of equivalent circuit with         |    |

|      | current commutation path $[24]$                                                          | 65 |

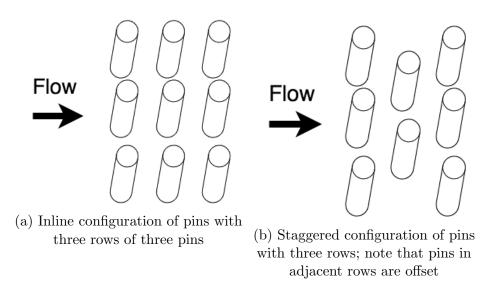

| 4.1  | Difference illustrated between pin fin configurations, namely between                    |    |

|      | inline and staggered                                                                     | 70 |

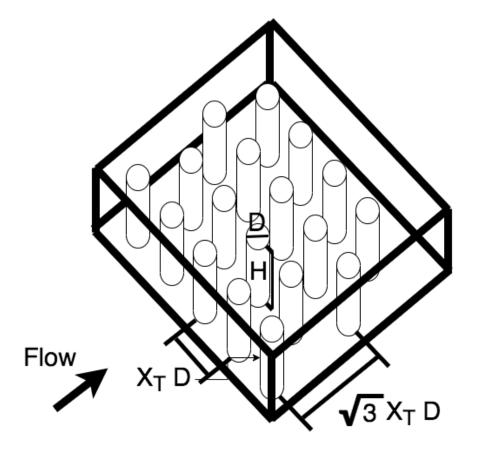

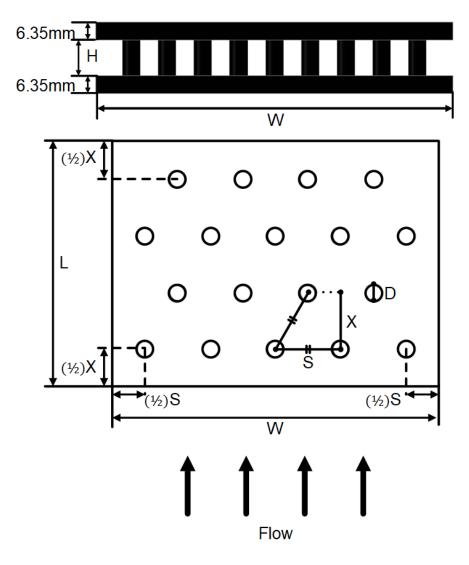

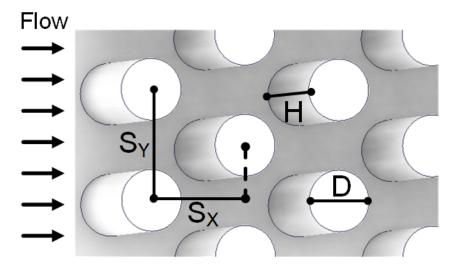

| 4.2  | Generalized setup used to study heat transfer of short pin fins $\ldots$                 | 73 |

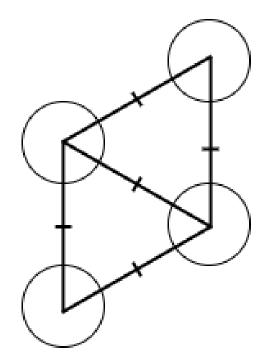

| 4.3  | Depiction of equilateral spacing between pins in staggered configuration                 | 74 |

| 4.4  | Pin Fin Channel Geometry Definition in VanFossen et. al.'s work $\ .$ .                  | 75 |

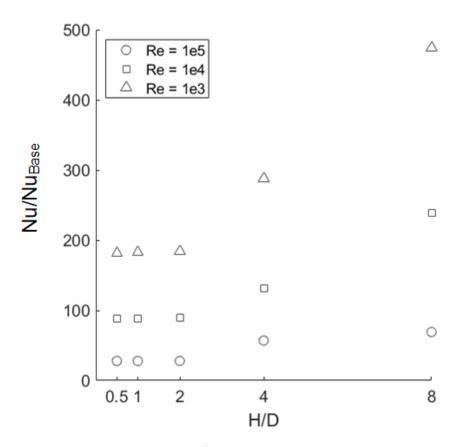

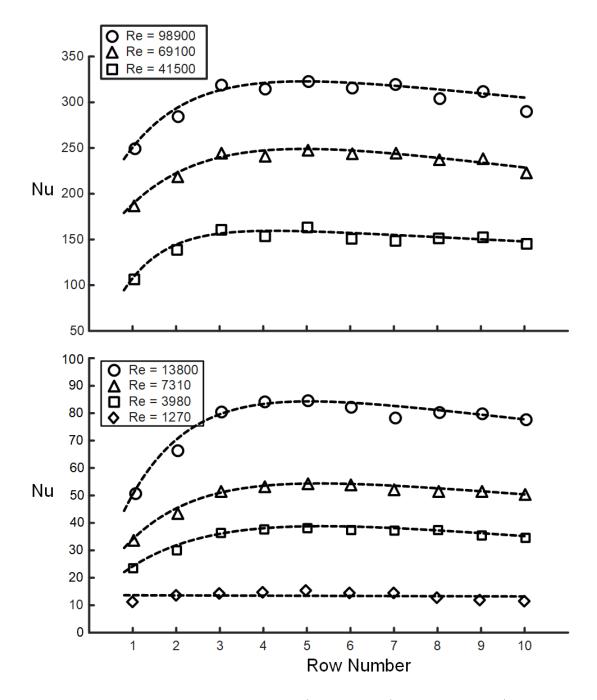

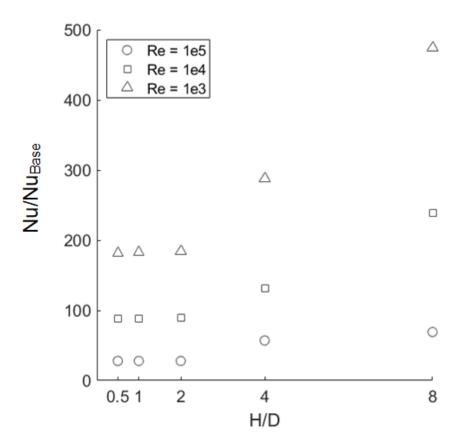

| 4.5  | Nusselt number gain; referenced to plain channel correlation versus pin                  |    |

|      | ${\rm length}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 79 |

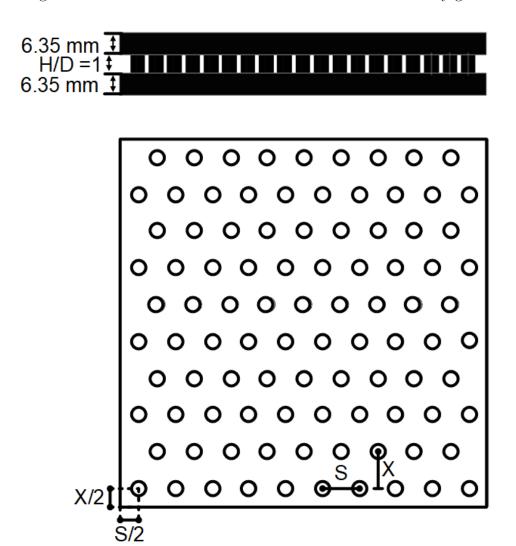

| 4.6  | Parametric geometry used by Metzger et al. for experimental testing                      | 81 |

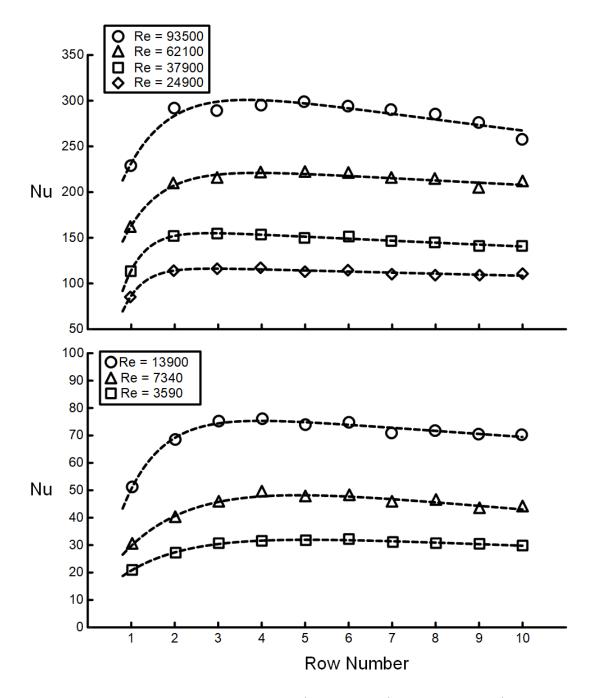

| 4.7  | Nu development for S/D = 2.5, X/D = 1.5, and H/D = 1 $\ . \ . \ .$ .                     | 83 |

| 4.8  | Nu development for S/D = 2.5, X/D = 2.5, and H/D = 1 $\ . \ . \ .$ .                     | 84 |

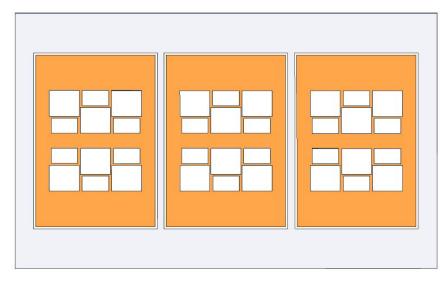

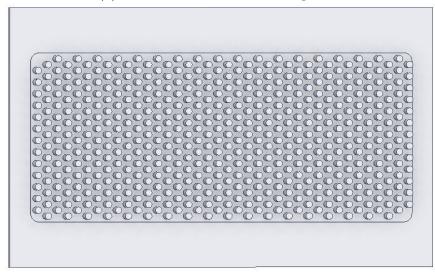

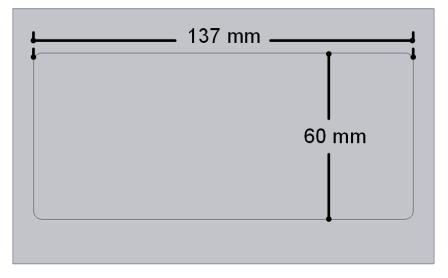

| 5.1  | CAD model of representative power module $\ldots \ldots \ldots \ldots \ldots$            | 94 |

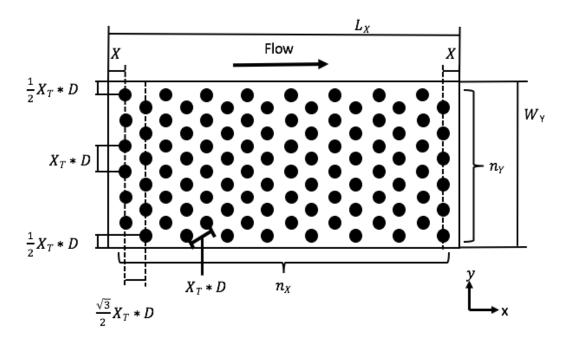

| 5.2  | Optimization Geometric Space                                                             | 95 |

| 5.3 | Optimization Variables                                                            | 95  |

|-----|-----------------------------------------------------------------------------------|-----|

| 5.4 | Geometric Dimension Constraints                                                   | 96  |

| 5.5 | Nusselt number gain; referenced to plain channel correlation versus pin           |     |

|     | length                                                                            | 104 |

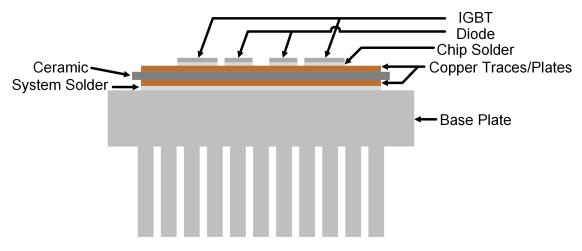

| 6.1 | Typical power module stack-up                                                     | 119 |

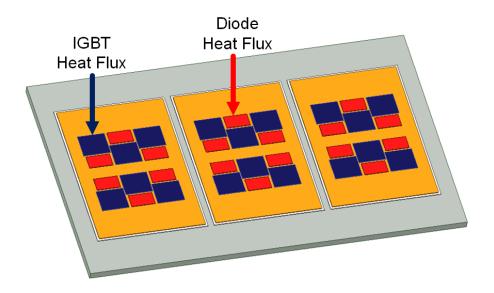

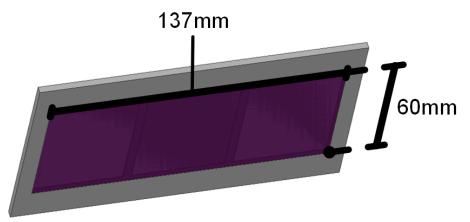

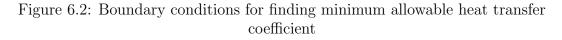

| 6.2 | Boundary conditions for finding minimum allowable heat transfer co-               |     |

|     | efficient                                                                         | 123 |

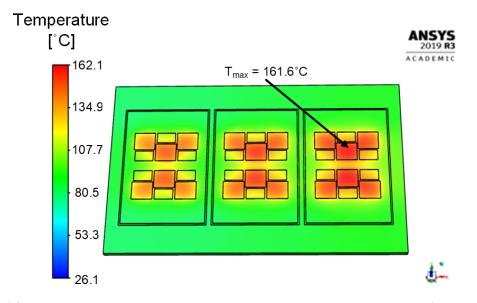

| 6.3 | Contours of benchmarking representative module for inlet temperature              |     |

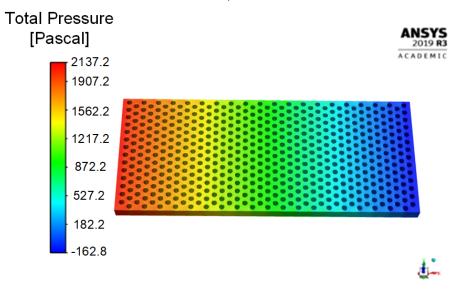

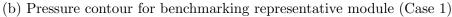

|     | $65^oC$ and a 5 LPM flow rate                                                     | 130 |

| 6.4 | Contours of benchmarking representative module for inlet temperature              |     |

|     | $75^oC$ and a 10 LPM flow rate $\ldots$                                           | 131 |

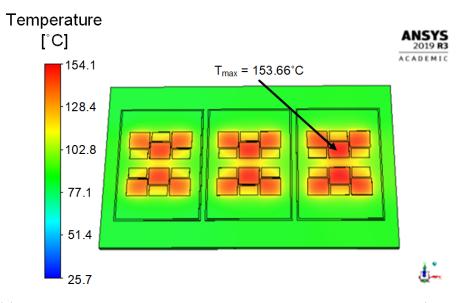

| 6.5 | Contours of benchmarking representative module for inlet temperature              |     |

|     | $85^oC$ and a 15 LPM flow rate $\hdots$                                           | 132 |

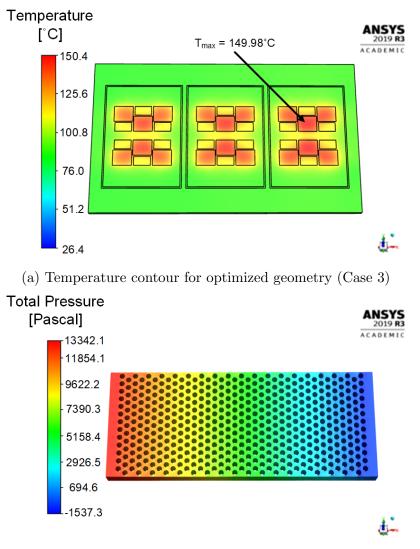

| 6.6 | Contours of optimized geometry for inlet temperature $65^oC$ and $5~\mathrm{LPM}$ |     |

|     | flow rate                                                                         | 134 |

| 6.7 | Contours of optimized geometry for inlet temperature $75^oC$ and $10$             |     |

|     | LPM flow rate                                                                     | 135 |

| 6.8 | Contours of optimized geometry for inlet temperature $85^{\circ}C$ and $15$       |     |

|     | LPM flow rate                                                                     | 137 |

# List of Tables

| 2.1 | Summary of switching states for Space Vector Modulation Scheme                    | 21  |

|-----|-----------------------------------------------------------------------------------|-----|

| 4.1 | Geometries used in the case study of [32] to study heat transfer $\ldots$         | 76  |

| 4.2 | Experimental geometries used to study effect of number of rows on                 |     |

|     | heat transfer [33] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 78  |

| 4.3 | Metzger et al. Non-dimensional Parameters for [36] and [35] $\ldots$ .            | 82  |

| 4.4 | Metzger et al. Non-dimensional Parameters for [36] and [35] $\ldots$ .            | 85  |

| 4.5 | Array geometry for Damerow's work                                                 | 87  |

| 4.6 | Metzger's pressure drop based experimental setup                                  | 88  |

| 5.1 | Variable constraints on Pin Fin Array                                             | 98  |

| 5.2 | Power Loss Results at worst-case scenario                                         | 99  |

| 6.1 | Stack-up Thermal Details                                                          | 120 |

| 6.2 | Summary of Results                                                                | 138 |

| 6.3 | Summary of Pressure Drop Modelling Accuracy:                                      | 139 |

| 6.4 | Accuracy of Both Thermal and Pressure Drop Models                                 | 140 |

## Chapter 1

## Introduction

#### **1.1** Background

Mobility is a very basic and critical factor in our lives. It is central to the economy and the living standard of all. Conventional internal combustion engine-based vehicles (ICE) are unsustainable and inefficient. Generating close to one-third of the total green house gas emissions, our current transportation sector is unsustainable. Additionally, ICE based vehicles peak at efficiencies less than 30 %, making them inefficient. In contrast, the electric energy storage system, the electric machines, and power electronic converters operate at much higher efficiencies; making electrified power trains the favoured transportation solution to our sustainability goals. As grid infrastructure is not yet prolifically adapted a transitional phase has come about. Ergo, in addition to fully electric vehicles (EVs), many automotive original equipment manufacturers have introduced Hybrid Electric Vehicles (HEVs) and Plug-in Hybrid Electric Vehicles (PHEVs) to mitigate the issue of inadequate grid infrastructure.

All electrified vehicle powertrains have an electric machine (EM) that works either

with an ICE or replacing it entirely to improve fuel economy. Today, the EMs most ubiquitous in EVs are of either the AC permanent magnet (PM) or AC induction machines (IM) types [1,2]. To drive EMs, a traction inverter is required to convert direct current from the battery pack to alternating current with controllable frequency and amplitude. Also the inverter is required to be bidirectional as to operate EMs in both motoring and generative modes. Focus is on the power electronics exclusively here in this thesis.

In 2012, the U.S. Department of Energy (DOE) defined a long term technological road map to cost effective, reliable, and high performance electrified vehicles [3]. The DOE intends to catalyze the development of compact and cost-effective electric traction drives that are competitive with the performance and reliability requirements of ICE-based vehicles, thereby, facilitating the mass market adaption of electrified vehicles of at least light-duty vehicle types. By 2020, power electronics were required to attain a continuous power rating of 30 KW (peak-power of 55KW for 18 seconds), a specific density of 14.1 KW/kg, a power density of 13.4 kW/L, at a cost of \$3.3/kW per 100,000 units [3]. Later, in 2017, requirements were updated for the year of 2025, the goal is to achieve a power density of 100kW/L at a cost of \$2.7/kW for power electronics with peak power rating of 100kW [4]. In other words, there is supposed to be an 18% cost reduction and 87% volume reduction with respect to the objectives of 2020. This implies an immense need for technological advancements as to meet such objectives and facilitate the mass market penetration of EVs.

#### 1.2 Motivation

Wide band gap (WBG) semiconductors can operate at a higher switching frequencies as compared to silicon-based semiconductors. Operating at higher switching frequencies allows for smaller dc-link capacitors and magnetic components, improving power density significantly. WBG semiconductors have higher thermal conductivity, higher allowable junction temperatures, higher breakdown voltage, and less switching losses than silicon-based semiconductors consolidating their superiority. The only thing that detracts from the utility of WBG devices is their higher costs. Anyways, a trend is seen where power ratings is increased as chip size is shrinking; the high heat flux introduces challenges to thermal management of power converters.

For every  $10^{\circ}C$  rise in operating temperature the rate of failure is shown to nearly double [5]. Thermal issues make up nearly 55% of electronic component failures [6], highlighting the importance of thermal management. Thermal behavior of power electronics influences the life time and reliability of electronic components in two ways that may be classified as destruction damage and fatigue of the components. Longterm exposure to junction temperatures exceeding the maximum possible value causes destruction damage. Fatigue of the components is mainly caused by the repetitive tensile and compressing stresses incurred by repetitive thermal stress due to fluctuating temperatures induced by power cycling and different coefficients of thermal expansion in materials [7].

There are many techniques to augment heat transfer. However, as was conveyed in the road-map of 2025 by the DOE, the thermal technique must be compatible with thermal techniques of other elements found in the vehicles. The coolant of Glycol-50 is selected as coolant, therefore, two-phase cooling methods are excluded. When it comes to single-phase cooling techniques there are many possibilities that are promising, yet there is always a trade off. Direct cooling finned heat sinks remain a simple, reliable, and effective cooling method that entails relatively low pressure drop.

As component-level integration is expected to increase, a tool is devised that optimizes circular pin fin array geometry to be integrated into baseplates. The focus is not on transient thermal behavior but steady-state thermal behavior, this means that thermal requirements are tailored to prevent destruction damage. So for any module, with any power electronic converter topology sub-optimal pin fin arrays can be designed.

#### **1.3** Thesis Objectives

Design of power electronics in the Electrified vehicle market tend to follow one of two philosophies [8]. Separately packaged or modular inverters used by many OEMs, for instance in the Nissan Leaf and Toyota Prius. These usually come in six-pack configurations but they can also come in customized configurations with charger or DC/DC-Booster typologies included, for example the Nissan Almera Hybrid. Alternatively, the inverter can be composed of discrete small and encapsulated components with single switch or half-bridge topology packages positioned in the mechanical compartment of the drive-train. Here it is common for the inverter to be integrated with the EM in same housing. The latter strategy requires the inverter to be exposed to the same climate and vibrational loading as the EM posing robustness risks and reliability issues for the inverter. Also, every discrete component is packaged and this does not allow for the optimal utility of volume. As such, in this thesis, only packaged or modular inverters are considered.

With the trend of increased integration and ever-growing power ratings, this thesis aims to design a tool capable of detailing the optimized geometry of pin fin array to be integrated into baseplate for any topology. Though the aim is that this design tool can be extended for use in any topology it is applied to a two-level voltage source inverter here. The scope of optimization is for cylindrical pins of uniform diameter and heights in the staggered configuration. ANSYS Steady-State Thermal Analysis is used to find the minimum possible value for the effective heat transfer coefficient given worst-case calculated power loss of assumed application and power module's chip layout of representative commercial benchmarking power module as to consider heat spreading. Our approach employs empirical correlations found in literature to optimize the geometry using the genetic algorithm for a given flow rate, coolant temperature, and minimum value of effective heat transfer coefficient. ANSYS-Fluent is later used to verify solution and results are compared to benchmarking commercial hybrid pack with integrated pins.

Note in addition to power loss and chip layout the pin fin array is optimized for a given flow rate and inlet coolant temperature this is because the cooling strategy must be compatible with the cooling strategy of other component in the EV.

There are restrictions in the geometry of pin fin arrays enforced by the nature of the empirical correlations that the tool depends on. The array is defined to have pin fins that are equalaterally spaced, spacing between adjacent pins may range from 1.5 to 4 diameters, length of pins range from 2 to 3 diameters long, and diameter of pins ranges from 1.5mm to 3mm. Defining the array in terms of the diameter, pin length, and distance between pins allows for the use of empirical correlations and genetic algorithm to ensure junction temperatures remains below the maximum value allowed while ensuring pressure drop is minimal.

#### 1.4 Thesis Outline

This thesis begins by explaining the operation of a two-level voltage source inverter in Chapter 2. This includes the topology and modulation scheme that converts dccurrent from the battery pack into AC-current with controllable amplitude and frequency. Inverter operation provides a basis that make calculating the power loss possible.

Next, in Chapter 3, Power losses are explained. This includes how losses arise during operation. Also method to calculate losses of a given application using data sheet is explicated. In addition, to provide reader a better understanding, the methodology of how the data sheet data is ascertained using an experimental setup called the double pulse test is provided.

In Chapter 4, a summary of the experimental correlations found in literature is given for both heat transfer and hydraulic friction factor. This forms the foundation of our optimization problem definition. Correlations facilitate a way to estimate pressure drop and heat transfer for a given pin fin array geometry allowing for optimization. CFD/numerical methods are very time and computationally extensive and because of the complex nature of flow analytical solutions are impossible.

Chapter 5 enunciates the optimization methodology used in the tool where for a maximum heat transfer coefficient value, flow rate, and coolant inlet temperature the optimized geometry can be found. In this chapter power losses for a given assumed application are also given. Lastly, in Chapter 6, three different scenarios are optimized for. It begins by defining the problem using a commercial hybrid pack power module in which the pin fin array is meant to be integrated into the bottom of baseplate. Using this representative power module and maximum expected calculated power loss calculated in chapter 5 the minimum value for the effective heat transfer coefficient is found using ANSYS Steady-State Thermal Analysis. The tool is employed to optimize for the three scenarios. Lastly CFD simulations are run as to validate results and evaluate the accuracy of the modelling in the optimization tool. Results are benchmarked to a commercially available Hybrid pack that is designed for.

### Chapter 2

# Operation of Two-Level Voltage Source Inverter

#### 2.1 Introduction

Electrified vehicle powertrains are mainly composed of an electric machine, an inverter, a controller, and a battery pack, as shown in Figure 2.1. Electric machines convert electrical energy into mechanical energy and vice versa. The battery pack supplies electrical power, which the inverter manipulates to form specific current waveforms. When applying these current waveforms to stator windings, the motor outputs desired torque. The controller ensures that the inverter produces current waveforms that correlate to the motor's desired torque.

Figure 2.1: Typical Electrified Vehicle Powertrain

Due to high power density, high torque, relatively simple control, and high efficiency over a wide operating range, Permanent Magnet Synchronous Motors (PMSMs) are generally the favored electric machine. Despite these advantages, PMSMs are costly and require rare earth materials to make permanent magnets. In addition, owing to their maturity, reliability, simple control, and relative low component count, three-phase Voltage Source Inverters (VSIs) are the most ubiquitously used traction inverter topology in automotive motor drive applications.

Although the battery pack is usually connected directly to the inverter, adding a DC-DC converter between the VSI and battery, as in Fig.2.2, has many benefits. These advantages include:

- Battery packs that are smaller and less expensive are permitted when utilizing a DC-DC converter because the output voltage only needs to meet the requirements of the DC-DC converter [9–11].

- When the VSI's DC-link bus is connected directly to the battery, the drive's performance can degrade as the state of charge drops. DC-DC converters can mitigate this issue [12].

• DC-DC converters add a degree of freedom, the DC-link voltage. Adjusting the DC-link voltage to an optimal value for all operating points can improve overall drive efficiency regardless of the losses generated by the DC-DC converter [9–11].

Despite this, the increased component count and cost usually detract from their utility. For the sake of minimizing the volume of power electronics (PE) and simplicity, it is assumed the inverter connects directly to the battery pack.

Figure 2.2: Electrified Vehicle Powertrain with DC-DC Converter

#### 2.2 Topology

As displayed vividly in Fig.2.3, each of the three legs consists of a high-side (HS) and low-side (LS) switch. Switches are composed of semiconductor transistors with accompanying anti-parallel free-wheeling diodes (FWD). Inductive loads like electric machines cause phase currents to lag phase-voltage waveforms by some angle  $\phi$ . More-over, inductive loads lead to considerable voltage spikes when the current experiences abrupt change. FWDs assure a continuous flow of current protecting transistors from deterioration or potential destruction due to voltage spikes. Also, FWDs facilitate a current path making regenerative braking feasible.

Figure 2.3: Three-Phase Voltage Source Inverter

A switch comprises of multiple semiconductor transistors in parallel and or in series to realize high current and voltage ratings in demanding applications. Power switch devices in inverters do not operate in the active region of i-v characteristics. Active region operation does exhibit a favorable attribute where line-to-ground voltage can be continuously varied, from  $0 \rightarrow V_{dc}$ , by applying a matching gate voltage. Despite this advantage, the active region suffers high power loss since both a high voltage drop across semiconductors and considerable current through the switching device coincide. On the other hand, if operating in saturation (On) region or cutoff region (Off), power losses remain relatively low. Although a high current traverses across the transistor, the voltage drop is negligible in the on-state region. Conversely, in the off-state region, a high voltage drop is applied across semiconductors, but the current is negligible. Since either voltage or current is negligible, losses remain low, the inverter consequently operates only in saturation or cutoff regions.

It follows that switches can either be on or off; a leg can therefore be in one of four states. However, there are only two permissible states due to practical restrictions. To elaborate, the HS switch and LS switch for a given leg must not have the same switching state. Turning both HS and LS switches simultaneously on leads to a short circuit across the dc-link. In contrast, turning both HS and LS switches off the phase voltage is undefined. In the latter scenario, phase voltage is undefined because it can be clamped, by a free-wheeling diode, to either the upper dc-link rail or lower dc-link rail, depending on the polarity of phase current at that instant. Therefore, each leg has two possible states, leaving the three-phase inverter with a total of eight switching states. Modulation techniques achieve desired waveforms by traversing between these eight different switching states.

The majority of EV traction inverters today are 400V based, Insulated-Gate Bipolar Transistor (IGBT) devices easily meet this requirement. IGBTs are inexpensive, well-established, and reliable, justifying their dominance in traction inverter applications. Upcoming Wide-bandgap semiconductors (WBG) can withstand higher temperatures, breakdown voltages, lower losses, and higher switching frequencies than Si-based IGBTs. Namely, the Silicon-Carbide (SiC) and Gallium Nitride (GaN) semiconductors are auspicious materials and are getting much attention. For now, IGBTs remain adequate, and unlike WBG devices, cheap.

DC-link capacitors enable the switching operations by providing reactive power. They also serve to suppress voltage ripples, attenuate current ripple, and reduce electromagnetic interference (EMI) emissions. They are heavy, expensive, and oversized, causing a significant obstacle for attaining high power density. Extensive studies have been conducted on analyzing and modeling the capacitor as not to overdesign it [13–17]. In the automotive industry, because of the high RMS current handling requirements of dc-link capacitor film capacitors are preferred to their electrolytic counterparts [18].

#### 2.3 Modulation Schemes

Three-phase voltage source inverters produce three-phase output voltage waveforms that are 120° electrically phase-shifted concerning each other. Phase, amplitude, and frequency of said waveforms are controllable. An inverter chops the dc-voltage into a pattern of pulses with deliberately varying pulse widths by switching, constituting a desired fundamental waveform with unavoidable harmonic components. This process is called pulse width modulation (PWM). Different PWM techniques are used to elicit the desired output phase voltage waveforms. Many studies have been undertaken to form vast works on the subject of modulation (SPWM), Space Vector Pulse Width Modulation (SVPWM), Sinusoidal Pulse Width Modulation with Zero-Sequence Signal Injection, and Square Wave Modulation. Notation and circuit in figure 2.4 is used to explain different modulation schemes.

Figure 2.4: Three-Phase Voltage Source Inverter, PMSM, and battery pack schematic used for following discussions

#### 2.3.1 Sinusoidal Pulse Width Modulation (SPWM)

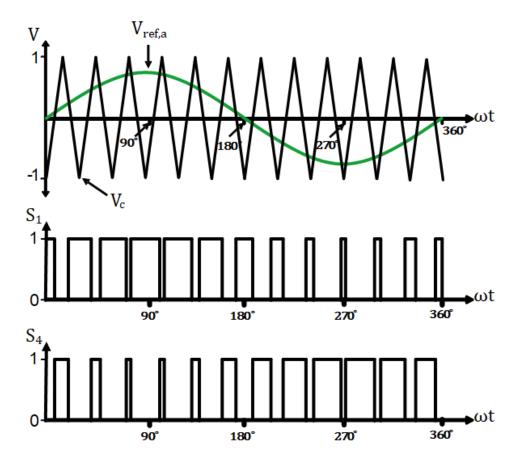

Figure 2.5: Illustration of SPWM pertaining to phase leg-a with resulting switch states.  $S_1$  and  $S_4$  are HS and LS switch of phase leg-a. A logic 1 denotes turned on and a logic 0 denotes switch being off.

SPWM is a classic technique, and the implementation is relatively straightforward. For simplicity, the discussion commences considering only a single phase-leg, namely leg-a. To produce a desired ac output phase voltage, a reference sinusoidal signal  $V_{ref}$  is compared to a high frequency triangular carrier signal  $V_c$ . Furthermore, when reference signal is greater than the carrier signal  $(V_{ref} > V_c)$ , the HS power switch is switched on and consequently the LS switch is off, this results in  $V_{an} = V_{dc}$ . Where,  $V_{an}$  is the voltage across the point labeled 'a', the output of leg-a, and point 'n,' the LS dc bus rail, as illustrated in figure 2.3. Alternatively, when the reference signal is less than the carrier ( $V_{ref} < V_c$ ), LS switch is conducting, and the HS switch is off leading to  $V_{an} = 0$ .

Carrier signals have a high frequency ( $f_c >> f_{ref}$ ), such that within a period of the carrier signal, the instantaneous value of the reference signal can be approximately assumed constant. When a reference signal is near its crest, the HS switch is turned on for the lengthiest duration of a carrier's period. On the other hand, in the proximity of a reference signal's trough, the HS switch conducts for the shortest duration for that given reference signal. Assuming the carrier signal oscillates between 1 and -1, the reference signal is defined as in eq 2.1.

$$V_{ref} = m\sin(\omega t) \tag{2.1}$$

Where  $\omega$  is the angular frequency of desired output waveform and can be described in terms of fundamental frequency of output phase voltage waveform  $(f_1)$  as  $\omega = 2\pi f_1$ and m is called a modulation index and is defined by eq 2.2.

$$m = \frac{\dot{V}_{ref}}{\dot{V}_c} \tag{2.2}$$

Where  $\hat{V_{ref}}$  and  $\hat{V_c}$  denote peak values of reference and carrier signals, respectively.

Any point along the reference signal corresponds to a pulse with a pulse duration

given by the duty cycle eq 2.3.

$$d = \frac{1 + m\sin(\omega t)}{2} \tag{2.3}$$

From equation 2.3 it is found that the train of pulses generated by this modulation technique is such that every pulse varies in pulse width proportionally to the instantaneous value of the reference wave. As time is traversed, the resulting fundamental component of the train of pulses has the same frequency as the reference waveform. Additionally, changing the modulation index within the range  $0 \le m \le 1$ , increases pulse widths of all points linearly. Modulation index can therefore control the amplitude of the fundamental component as conveyed in

$$\hat{V_{an\ 1}} = m \cdot \frac{V_{dc}}{2}.\tag{2.4}$$

Until now, only a single phase-leg was discussed, to establish three-phase voltage waveforms, three identical reference signals are used with a phase shift of  $\pm 120 \deg$  between them as shown below. Each reference wave is compared to the carrier signal and controls the switching of HS/LS power switches of the respective leg exactly in same manner as was discussed on leg-a.

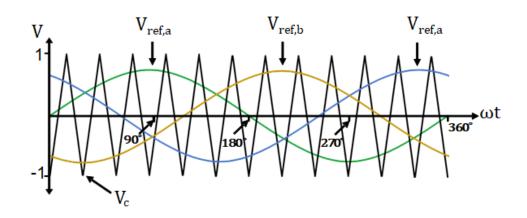

Figure 2.6: Waveforms used to implement SPWM

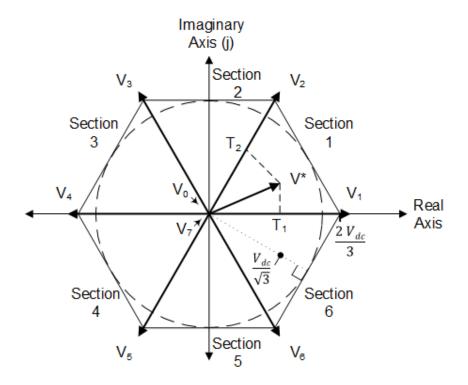

#### 2.3.2 Space Vector Modulation (SVM)

Two-level VSIs have eight possible switching states. Recall, the high-side and lowside switches must have alternative states to eliminate shoot-through current and undefined instantaneous phase voltage values. Here we will discuss the SVM modulation scheme based on [19]. The different switching states are denoted with three binary bits  $[b_1, b_2, b_3]$ , standing for the HS switching states of phase-a, phase-b, and phase-c, respectively. For each phase, the corresponding bit with a logic 1 means the HS switch is turned on, and the phase terminal is connected to the upper dc-link rail. In contrast, a logic 0 means the LS switch is turned on, and the corresponding phase terminal is connected to the lower dc-link rails. Referring to Fig.2.3, the voltage of phase with respect to lower dc-link rails "n" can be easily deduced. For example; if  $b_1 = 1$  than  $V_{an} = V_{dc}$ , conversely, if  $b_1 = 0$  than  $V_{an} = 0$ . Similarly, voltages of the phase terminals with respect to lower dc-link rail can be constructed from the switching states.

$$\begin{bmatrix} V_{an} \\ V_{bn} \\ V_{cn} \end{bmatrix} = V_{dc} \begin{bmatrix} b_1 \\ b_2 \\ b_3 \end{bmatrix}$$

(2.5)

Focusing on relating between phase voltages and voltage across output phase terminals to lower dc-link rails. Inverter is assumed three-phase balanced  $V_{ao} + V_{bo} + V_{co} = 0$  (no zero sequence component). Neutral of EM stator winding is denoted as point 'o' as is shown in 2.4. Performing KVL than yields equations 2.6.

$$V_{an} - V_{on} - V_{ao} = 0$$

$$V_{bn} - V_{on} - V_{bo} = 0$$

$$V_{cn} - V_{on} - V_{co} = 0$$

(2.6)

Adding equations of 2.6 and recalling that inverter is three-phase balanced  $V_{on}$  is found (i.e. voltage between neutral of machine's stator windings and lower dc-link rail)

$$V_{on} = \frac{(V_{an} + V_{bn} + V_{cn})}{3}.$$

(2.7)

Substituting eq 2.7 in eq 2.6; instantaneous output three-phase voltages are described:

$$\begin{bmatrix} V_{ao} \\ V_{bo} \\ V_{bo} \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & \frac{-1}{3} & \frac{-1}{3} \\ \frac{-1}{3} & \frac{2}{3} & \frac{-1}{3} \\ \frac{-1}{3} & \frac{-1}{3} & \frac{2}{3} \end{bmatrix} \begin{bmatrix} V_{an} \\ V_{bn} \\ V_{bn} \\ V_{cn} \end{bmatrix}$$

(2.8)

Until now, given a switching state the resulting instantaneous phase voltages can be computed. For example, by applying the switching state [1, 1, 0]. Using eq 2.5, it is found that  $V_{aN} = V_{dc}$ ,  $V_{bN} = V_{dc}$ , and  $V_{cN} = 0$ . Subbing the voltages of phase terminals with respect to lower dc-link rail into eq 2.8, it follows that  $V_{ao} = \frac{-V_{dc}}{3}$ ,  $V_{bo} = \frac{-V_{dc}}{3}$ , and  $V_{co} = \frac{2V_{dc}}{3}$ . Note that any phase voltage is equal to the negative sum of other two, a direct consequence of having three-phase balanced load. Hence computing all three phase voltages is redundant.

Since three-phase variables are not independent, they can be expressed as two-phase variables and therefore can be elegantly described by a planar vector. Using the complex plane, it is possible to construct a space vector containing two components a real component ( $\alpha$ ) and imaginary ( $\beta$ ). Space vectors are similar to phasors with the distinction that their magnitudes can be time-varying. Converting from three-phase voltages to the  $\alpha, \beta$  - phase voltages can be performed through the Amplitude Invariance Clarke Transform eq 2.9.

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{\sqrt{3}}{2} & \frac{-\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{ao} \\ V_{bo} \\ V_{co} \end{bmatrix}$$

(2.9)

A constant of 2/3 is employed in order that amplitude of  $V_{\alpha}$  and  $V_{\beta}$  matches that of balanced three-phase load voltages. Balanced 3-phase ac voltages can now be represented as  $V = V_{\alpha} + jV_{\beta}$ . Taking advantage of Euler's formula  $(e^{jx} = cos(x) + j sin(x))$ , it follows.

$$V = \frac{2}{3} \left( V_{ao} + V_{bo} e^{j2\pi/3} + V_{co} e^{j4\pi/3} \right)$$

(2.10)

Remarking that the two switching states [0, 0, 0] and [1, 1, 1] are redundant and constitute Zero Vectors. Later the importance of redundant zero vectors in how they facilitate lower switching frequency will become more obvious. The remaining space vectors for other switching states,  $V_1$  through  $V_6$ , are termed Active Vectors.

To summarize because balanced loads elicit three-phase voltage waveforms with inherent dependence between them that can be wholly described with two variables in a complex plane. Thus far, the instantaneous three-phase ac voltage waveform values generated by all possible switching states has been converted into stationary space vectors. Moving forward, recall that the objective is to produce controllable threephase ac-voltage waveforms with variable amplitude, phase, and frequency. Expressed in equation 2.3.2 is a definition for the target waveforms. Where the asterisk denotes

| Space Vectors                   |                                                                  |                                       |

|---------------------------------|------------------------------------------------------------------|---------------------------------------|

| Switching State<br>[b1, b2, b3] | Instantaneous $3\phi$<br>-Voltages<br>$[V_{aO}, V_{bO}, V_{cO}]$ | Space Vector                          |

| 0, 0, 0                         | 0, 0, 0                                                          | $V_0 = 0$                             |

| 1, 1, 1                         | 0, 0, 0                                                          | $V_{0} = 0$                           |

| 1, 0, 0                         | $\frac{2V_{dc}}{3}, \frac{-V_{dc}}{3}, \frac{-V_{dc}}{3}$        | $V_1 = \frac{2V_{dc}}{3} e^{j0}$      |

| 1, 1, 0                         | $\frac{V_{dc}}{3}, \frac{V_{dc}}{3}, \frac{-2V_{dc}}{3}$         | $V_2 = \frac{2V_{dc}}{3} e^{j\pi/3}$  |

| 0, 1, 0                         | $\frac{-V_{dc}}{3}, \ \frac{2V_{dc}}{3}, \ \frac{-V_{dc}}{3}$    | $V_3 = \frac{2V_{dc}}{3} e^{j2\pi/3}$ |

| 0, 1, 1                         | $\frac{-2V_{dc}}{3}, \ \frac{V_{dc}}{3}, \ \frac{V_{dc}}{3}$     | $V_4 = \frac{2V_{dc}}{3} e^{j\pi}$    |

| 0, 0, 1                         | $\frac{-V_{dc}}{3}, \ \frac{-V_{dc}}{3}, \ \frac{2V_{dc}}{3}$    | $V_5 = \frac{2V_{dc}}{3} e^{j4\pi/3}$ |

| 1, 0, 1                         | $\frac{V_{dc}}{3}, \ \frac{-2V_{dc}}{3}, \ \frac{V_{dc}}{3}$     | $V_6 = \frac{2V_{dc}}{3} e^{j5\pi/3}$ |

Table 2.1: Summary of switching states for Space Vector Modulation Scheme

that these are the target or desired waveforms,  $\hat{V}$  is the desired amplitude of said waveforms,  $\phi$  is desired phase shift, and lastly,  $\omega^*$  is the desired angular frequency.  $\omega^* = 2\pi f^*$ ,  $f^*$  is desired frequency of waveforms.

$$V_{ao}^{*} = \hat{V}sin(\omega^{*}t + \phi)$$

$$V_{bo}^{*} = \hat{V}sin(\omega^{*}t - 2\pi/3 + \phi)$$

$$V_{co}^{*} = \hat{V}sin(\omega^{*}t + 2\pi/3 + \phi)$$

(2.11)

If eq 2.3.2 is applied into eq 2.10, the expression simplifies into

$$V^* = \hat{V} e^{j(\omega^* t + \phi)}.$$

(2.12)

Unlike vectors representing switching states, the reference vector rotates with time at an angular frequency  $\omega^*$  and has a length equivalent to the amplitude of target phase voltages (Amplitude invariant transform). Specifically, the phase angle at instant t of reference vector with respect to the positive real axis is defined by

$$\theta(t) = \int_0^t \omega^* dt + \phi.$$

(2.13)

As commanded target phase voltages are embodied in a rotating reference vector, the vector is sampled periodically at a prescribed sampling frequency and synthesized by two adjacent stationary active vectors and the stationary Zero vector. Standard switching frequency in automotive motor drive applications typically ranges between 10-15 kHz. Stationary space vectors relating to eight switching states produce discrete instantaneous three-phase voltage values  $(0, \pm 1/3, \text{ and } \pm 2/3)$ ; however, sinusoidally varying values are desired. A compromise is made where reference vector adjacent space vectors are applied such that the average over a sampling period equals voltage values equivalent to the instantaneous sinusoidally varying target three-phase voltage output values. The compromise is that the fundamental component obtains the target ac three-phase voltage, but additionally, undesired higher-order components are presented as harmonic losses. Mathematically the technique is termed "Volt-Second Balancing". Initially, the stationary active vectors divide the complex plane into six sectors; the sector is denoted by k, depending on  $\theta$ .

Figure 2.7: Modulation range for space-vectr modulation

$$k(\theta) = \begin{cases} 1 & \text{if } 0 \le \theta \le \frac{\pi}{3} \\ 2 & \text{if } \frac{\pi}{3} \le \theta \le \frac{2\pi}{3} \\ 3 & \text{if } \frac{2\pi}{3} \le \theta \le \pi \\ 4 & \text{if } \pi \le \theta \le \frac{4\pi}{3} \\ 5 & \text{if } \frac{4\pi}{3} \le \theta \le \frac{5\pi}{3} \\ 6 & \text{if } \frac{5\pi}{3} \le \theta \le 2\pi \end{cases}$$

(2.14)

Stationary active vectors  $V_k$  and  $V_{k+1}$  are applied when reference vector is sampled. While reference vector traverses in sector "k",  $V_k$  and  $V_{k+1}$  are applied for durations derived by projecting the reference vector onto respective active vectors. Durations are denoted as  $T_k$  and  $T_{k+1}$  and are calculated using equations of 2.15.

$$T_{k} = \frac{\sqrt{3} T_{s} V_{ref}}{V_{d}} \sin(\frac{\pi}{3} (2 - k) - \theta)$$

$$T_{k+1} = \frac{\sqrt{3} T_{s} V_{ref}}{V_{d}} \sin(\frac{\pi}{3} (2 - k) - \theta)$$

$$T_{0} = T_{s} - T_{k} - T_{k+1}$$

(2.15)

Furthermore, sequence of applied switching states are selected to minimize switching frequency and optimize harmonic performance. Every switch must turn-on and turnoff a maximum of one time this establishes a switching frequency equating to sampling frequency. Meeting this requirement dictates that the sequence must start with a zero vector and toggle between active states until alternate zero vector is applied, then it sequence reverses ending with initial zero vector. For instance when in sector 1, a sequence of [0,0,0], [1,0,0], [1,1,0], [1,1,1], [1,1,0], [1,0,0], and [0,0,0]. The durations are based on eq 2.15; both [0,0,0] state is applied for  $T_0/4$ , [1, 1, 1] for  $T_0/2$ , each [1,0,0] and [1,1,0] for  $T_k/2$  and  $T_{k+1}/2$ , respectively.

#### 2.3.3 SPWM with Zero Sequence Signal Injection

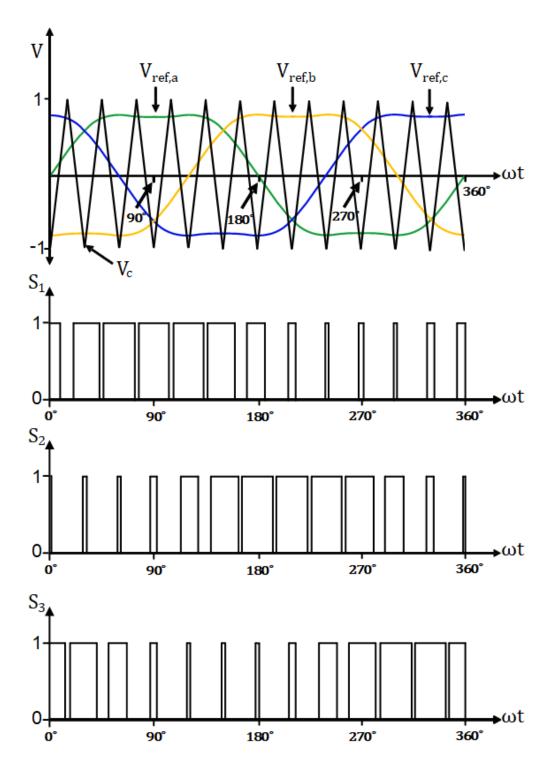

SVM requires a considerable amount of calculations, leading to an alternate modulation technique that is simpler to implement; SPWM with zero-sequence signal injection (third harmonics). Both modulation techniques extend the linear range by 15% and result in the same DC-bus voltage utilization. SPWM with zero-sequence signal injection is detailed in a simple and elegant manner in [20], based on this dissertation, a brief and concise description of this modulation scheme is provided here. Implementation of SPWM with zero-sequence signal injection is the same as SPWM with a minor distinction. Three reference signals ( $V_{ref,a}$ ,  $V_{ref,b}$ , and  $V_{ref,c}$ ) are compared to a triangular carrier signal ( $V_c$ ), except here, adding a term to the reference signals unlike in the standard SPWM.

Figure 2.8: Waveforms used to implement SPWM with Zero-Sequence Injection and resulting gate pulse for HS switches for three-phase legs

$$V_{ref,a} = m \sin(\omega t) + V_0$$

$$V_{ref,b} = m \sin(\omega t - \frac{2\pi}{3}) + V_0$$

$$V_{ref,c} = m \sin(\omega t + \frac{2\pi}{3}) + V_0$$

(2.16)

$V_0$  is the zero sequence signal, where

$$V_0 = -\frac{1}{2}(V_{max} + V_{min}) \tag{2.17}$$

and

$$V_{max} = max(sin(\omega t), sin(\omega t - \frac{2\pi}{3}), sin(\omega t + \frac{2\pi}{3}))$$

$$V_{min} = min(sin(\omega t), sin(\omega t - \frac{2\pi}{3}), sin(\omega t + \frac{2\pi}{3})).$$

(2.18)

By adding the zero-sequence signal, the fundamental component of the reference signal is the same while reducing the peak of the reference signal. Instead of the modulation index capping at 1 for linear range, like in SPWM, the modulation index now is limited to  $\frac{2}{\sqrt{3}}$ . The amplitude of the line-to-line fundamental voltage waveform for VSI in the linear range is delineated as

$$V_{ab} = m \frac{\sqrt{3}}{2} V_{dc}.$$

(2.19)

Recall  $V_{dc}$  is the dc-link voltage, or voltage across point 'p' and 'n' in fig 2.3. Pushing the modulation index 15.5% higher results in 15.5% higher dc-link voltage utilization.

#### 2.3.4 Six Pulse Modulation

Previously, a carrier based sinusoidal pulse width modulation technique was discussed. The discussion was restricted to linear range of modulation, that is where modulation index linearly controls amplitude of resulting fundamental three-phase voltage waveforms. Further increasing modulation index beyond  $M_a = 1$  prompts a non-linear rise in fundamental phase voltage amplitude and unavoidable low-order harmonics. Accompanied by a modulation index of 3.24,"full over-modulation", the largest fundamental phase voltage amplitude  $(\frac{4}{\pi}\sqrt{3}\frac{V_{dc}}{2})$  attainable by a two-level three-phase inverter is realized. Full over-modulation is also known as square-wave or six-pulse operation.

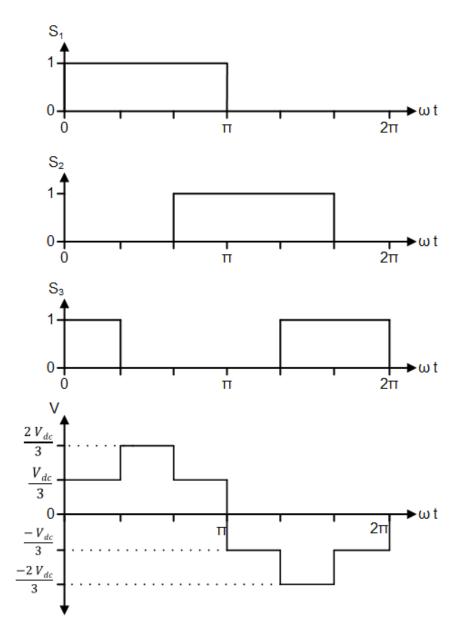

Six-pulse operation results in every switch conducting for  $\pi$  radians periodically [21]:

$$S_1$$

conducts from :  $0 \to \pi$  radians

$S_2$  conducts from :  $\frac{2\pi}{3} \to \frac{5\pi}{3}$  radians

$S_3$  conducts from :  $0 \to \frac{\pi}{3}$  and  $\frac{4\pi}{3} \to 2\pi$  radians

Figure below displays the switching states, ones denote on-state, and resulting phase voltage  $(V_{ao})$  produced from leg-a. Despite six-pulse operation maximizing fundamental phase voltage amplitude for given dc-link voltage, the higher non-contributing harmonic content are responsible for losses in system. Harmonics degrade efficiency, increase thermal load, and cause torque pulsations in machine (significant at low

Figure 2.9: Waveforms used to implement 6-step modulation, and phase voltage of leg-a  $(V_{ao})$ .

speeds). Line-to-line voltage harmonics have amplitudes inversely related to order of harmonic eq 2.20. Harmonics are found at orders "h" of fundamental, where h = 6 k

$$\pm 1 \ (k = 1, 2, 3, ...).$$

$$\hat{V}_{ab} = \frac{4}{h\pi}\sqrt{3}\frac{V_{dc}}{2}$$

(2.20)

## 2.4 Summary

Our development of the pin fin geometry optimization tool is tailored specifically for a basic two-level voltage source inverter. As such, it is valuable to begin our development from first principles such that power losses can be understood in detail and the thermal management system is described thoroughly. Two level-voltage source inverters are the main topology utilized in traction inverters for electrified vehicles and this is expected to remain true for the foreseeable future as a consequence of their reliability, efficiency, and low costs. Converting dc-current from battery pack to AC-current for EM operation is the responsibility of the traction inverter. This chapter detailed the topology along with the modulation schemes that facilitate the desired current manipulation. The operation of inverters comes with undesirable yet unavoidable losses. These losses take the form of heat, this heat must be estimated and dissipated as to ensure inverter components do not acquire temperatures beyond their limitations. If temperatures exceed the maximum value allowed for prolonged interval of time, semiconductor switches will get destroyed and the inverter will suffer failure. Power losses are the main topic of next chapter, it build on the concepts of this chapter.

## Chapter 3

# Power Losses in Two-Level Voltage Source Inverters

## 3.1 Introduction

Converting DC voltage into controllable AC waveforms results in higher undesired harmonics and generated heat. Inverters inadvertently convert electrical energy into heat commensurate to the inverter's instantaneous operating point. Cooling systems are entrusted with keeping semiconductors inside an operable temperature range by rapidly transmitting the generated heat to the ambient. Hence, accurately estimating the power losses provides a benchmark for the cooling system. Discussions are confined to IGBT based VSIs.

Losses in the semiconductors dominate power loss generated by the VSI. Said losses comprise both conduction and switching losses for IGBT devices and their FWD counterparts. Manufacturers provide datasheets that encompass, among other things, the conduction and switching characteristics of semiconductor devices. This chapter aims to comprehensively explain how to utilize datasheets in estimating power losses for IGBT modules applied to motor drives.

## 3.2 Switch Operation

Without a brief explication of the behavior of semiconductors forming a switch featuring their different regions of operation, a review of estimating power loss remains lacking. Switches of IGBT-based VSI comprise of IGBT Transistors and their freewheeling diode counterparts. First, pondering the diode's operation then considering the IGBT transistor's behavior.

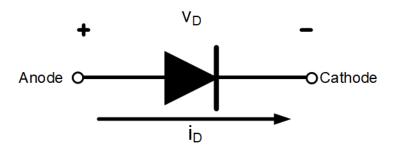

#### 3.2.1 Diode Operation

Diodes are semiconductors that serve as electrical valves conducting current in one direction. They have two electrodes, an anode, and a cathode, as is made apparent by Figure 3.1.

Figure 3.1: Representative circuit diagram symbol for Diodes

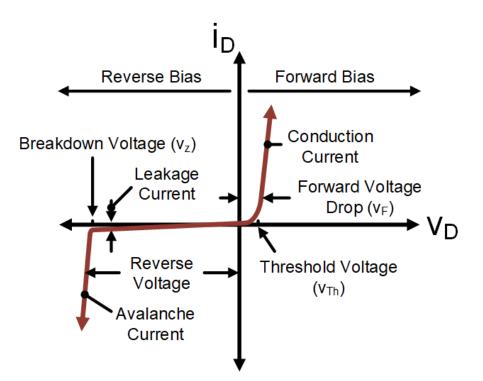

Outlining a diode's behavior, manufacturers supply a graphed asymmetric I/V characteristics of the diode, similar to Fig.3.2. Only the first quadrant is relevant in some applications, and other quadrants are not provided.

Figure 3.2: I/V Characteristics For a Diode portraying the different regions of operation

Referring to the illustrative I/V characteristic plot, two regions of operation for diodes arise, namely Forward Bias and Reverse Bias modes. The voltage across a diode,  $v_D$ , is the potential difference between the anode and cathode terminals. If voltage is positive,  $v_D > 0$ , diode operates in Forward Bias mode. Conversely, if voltage is negative,  $v_D < 0$ , diode is in Reverse Bias mode.

In reverse bias operation, diodes block applied reverse voltage while conducting leakage current. Leakage current is typically small enough to ignore, and here it is neglected. An application's operating conditions should never impose on a diode to block voltage beyond the breakdown voltage level,  $v_Z$ , to not incur Avalanche current. Diodes in reverse bias can be considered an open circuit. Consequently, diodes in Reverse bias mode are assumed to have negligible power loss.

In contrast, while in forward bias mode, a diode begins conducting current when a voltage beyond the threshold voltage level is applied,  $v_D > v_{D,Th}$ . Above threshold voltage, the current flowing through the diode is commensurate to the applied voltage on the device. The relation between current and Forward Voltage Drop,  $v_{D,FB}$ , is conventionally approximated by a linearization of the curve intercepting Voltage axis, i.e., x-axis, at the threshold voltage with a slope  $\frac{1}{R_D}$ . Thereby, diodes in the forward bias mode may be modeled as a resistor in series with a voltage source. Forward

Figure 3.3: Diode Equivalent Circuit in Forward Biased Mode

voltage drop is then a function of a diode's flowing current,

$$v_{D,FB} = R_D \, i_D + v_{D,Th}. \tag{3.1}$$

## 3.2.2 IGBT Operation

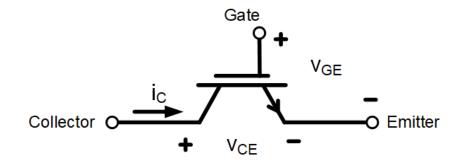

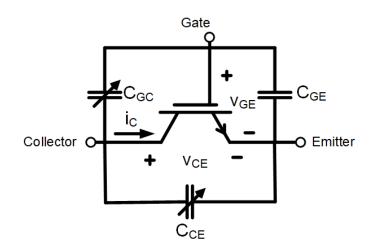

IGBT's have three electrodes, namely the Gate, Emitter, and Collector as is accentuated in Fig.3.4. Acting like a voltage-controlled switch, voltages applied across

Figure 3.4: IGBT Circuit Diagram Symbol

collector-emitter  $(v_{CE})$  and gate-emitter  $(v_{GE})$  determine the amount of current flowing through IGBT, i.e., into collector node and out of emitter node (by convention). Furthermore, output Characteristics for an IGBT like the typical plot shown in Fig.3.5 are necessary when inspecting an IGBT's operation.

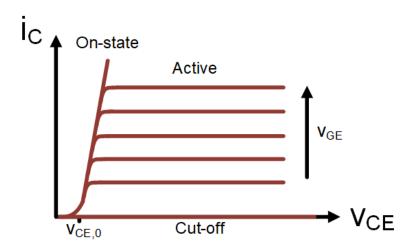

By examining the plot, it becomes evident that there are three modes of operation: Cut-off, Active, and Saturation (on-state) regions of operation.

Figure 3.5: Typical Output Characteristics of IGBT

• Cut-off

When gate voltage (across gate-emitter terminals  $v_{GE}$ ) is less than the threshold voltage level  $v_{GE} < v_{GE,Th}$  IGBTs won't conduct any current  $i_C = 0$ .

• Active regime

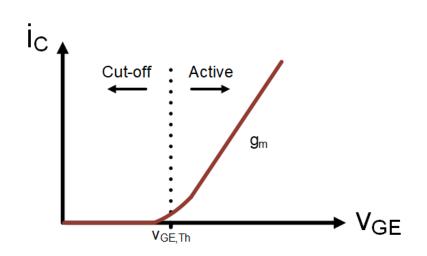

If the gate voltage is larger than the threshold level, i.e.,  $v_{GE} > v_{GE,Th}$ , and the applied collector-emitter voltage is large concerning gate voltage, then IGBT behaves according to its active region characteristics. Collector-emitter voltage is specifically defined as large when  $v_{CE} > v_{GE} - v_{GE,Th}$ . Interestingly, the IGBT current traversing through can be controlled with gate voltage, while the collector-emitter voltage has no influence. In Figure 3.5 the association between collector current  $i_C$ , gate voltage  $v_{GE}$ , and collector-emitter voltage  $v_{CE}$  is given by horizontal lines, where collector current stays constant with changing collector-emitter voltage magnitudes but shifts up with higher gate voltage levels. In the active regime, a transfer characteristic plot can be more meaningful. Referring to the graph of Fig. 3.6, one can promptly discern some basic points. Below the threshold voltage level (i.e., in cut-off), there is no collector current. However, a further increase of gate voltage beyond threshold level makes the collector current rise practically linearly, explaining why the active region is also called the linear region. Indeed, it is standard to linearize the curve over the active region for simplicity. The associated slope gives the IGBT's transconductance,  $g_m$ . As such, the collector current is prescribed by

$$i_C = g_m \left( v_{GE}(t) - v_{GE,Th} \right).$$

(3.2)

Figure 3.6: Typical Transfer Characteristics of IGBT depicting both the Active and Cut-off regions with the a Transconductance  $g_m$

• Saturation Region (on-state)

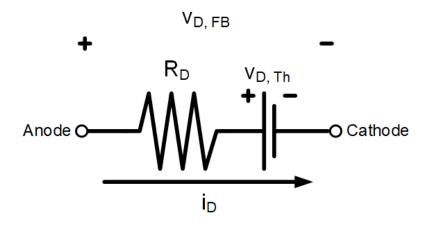

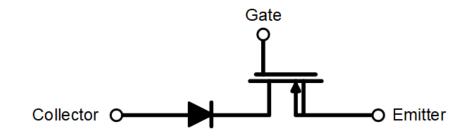

Similar to the active region, an IGBT must have a gate voltage larger than the threshold value  $v_{GE} > v_{GE,Th}$ . However, for the saturation regime to take effect, the collector-emitter voltage must be small. Precisely, collector-emitter voltage is said to be small, in this context, if  $v_{CE} < v_{GE} - v_{GE,Th}$ . An equivalent model, Figure 3.7, may be used to explicate IGBT's behavior. The model comprises a diode in series with a MOSFET in linear operation [22]. The diode in this model has a voltage drop of  $v_{CE,0}$ , and since MOSFET is in linear operation, it can be represented as a resistor  $R_I$ .

The IGBT has a low on-state voltage, and the current limit is based on thermal considerations. The collector-emitter voltage across IGBT is described by

$$v_{CE}(t) = v_{CE,0} + i_c(t)R_I, (3.3)$$

where resistance  $R_I$  accounts for the linear, "Ohmic," dependence between  $i_c$

Figure 3.7: IGBT on-state equivalent model, includes a diode in series with a MOSFET in linear operation

and  $v_{CE}$ .

In the previous chapter, it was made clear that only the on-state and cut-off modes are utilized for traction inverters. There is negligible leakage current in cut-off mode, and power losses can be assumed zero. In contrast, the on-state mode has a large current but a tiny on-state voltage drop resulting in considerably low power losses. Although the active region can be controlled simply by adjusting gate voltage, which has practical implications, the high current and voltage make this mode undesirable, as mentioned in the previous chapter. Albeit the active mode is not used in static operations, it inevitably arises during dynamic switching.

## 3.3 Conduction Losses

Pertaining to the on-state of semiconductors, conduction losses contribute to total power losses and must be ascertained. Assuming SPWM is implemented to operate a 3-phase VSI, symmetry can simplify conduction analysis to a single phase current half cycle. Because switching frequency is much larger than output fundamental frequency, treating switching frequency as infinite is justifiable and has advantageous implications. Deriving an elegant expression for conduction losses starts with considering a sing phase current,

$$i_a = \hat{i} \sin(\omega t). \tag{3.4}$$

Over the positive half cycle when reference wave is larger than the carrier waveform high-side IGBT  $T_1$  conducts, in contrast, if carrier is larger than reference waveform than low-side Diode conducts (refer to Chapter 1 for more thorough description). An infinite switching frequency implies that a switching event occurs at every infinitesimal point along the current waveform and that the current value remains constant for a switching period. Thereby, at every point along the waveform, a corresponding magnitude of current traverses through high-side IGBT for a time span  $\tau(t)$  normalized to switching period, where

$$\tau_{IGBT}(t) = \frac{1}{2} \left[ 1 + m \sin(\omega t + \phi) \right], \qquad (3.5)$$

and for the remainder time of the normalized switching period the current passes through low-side Diode,

$$\tau_{Diode}(t) = \frac{1}{2} \left[ 1 - m \sin\left(\omega \ t + \phi\right) \right]$$

(3.6)

[20, 22-26].

## 3.3.1 Diode Conduction Losses

Average conduction losses of diode over an output fundamental period is found by integrating instantaneous current through and voltage across a Diode over a half-period, as shown in eq. 3.7 [20, 22–26].. Where forward voltage drop was given in eq. 3.1 previously.

$$P_{cond, D} = \frac{1}{2\pi} \int_{0}^{\pi} (R_{D} i_{D}(t) + v_{Th,D}) i_{D}(t) d(\omega t)$$

$$= \frac{1}{2\pi} \int_{0}^{\pi} (R_{D} i_{a}(t) + v_{Th,D}) i_{a}(t) \tau_{Diode} d(\omega t)$$

$$= \frac{1}{2} \left( v_{Th,D} \frac{\hat{i}_{a}}{\pi} + R_{D} \frac{\hat{i}_{a}^{2}}{4} \right) - m \cos(\phi) \left( v_{Th,D} \frac{\hat{i}_{a}}{8} + R_{D} \frac{\hat{i}_{a}^{2}}{3\pi} \right)$$

(3.7)

## 3.3.2 IGBT Conduction Losses

Average conduction losses for an IGBT is analogous to that of Diode. The forward voltage drop was given before eq. 3.3 and by employing same methodology the expressions can be derived to be

$$P_{cond, I} = \frac{1}{2} \left( v_{CE,0} \, \frac{\hat{i}_a}{\pi} \, + \, R_I \frac{\hat{i}_a^2}{4} \right) \, + m \, \cos(\phi) \left( v_{CE,0} \, \frac{\hat{i}_a}{8} \, + R_I \frac{\hat{i}_a^2}{3\pi} \right). \tag{3.8}$$

In order to find the total on-state losses for a 3-phase VSI, expressions of conduction

loss for both IGBT and Diode (eq. 3.7 and eq. 3.8) which pertain to a fundamental half-period ought to be summed and multiplied by six,

$$P_{Total, cond} = 6 \left( P_{cond, D} + P_{cond, I} \right). \tag{3.9}$$

## 3.4 Switching Losses

Estimating the switching losses is more complex than conduction losses. Switching energies, provided in datasheets, are required to calculate the switching losses. Manufacturers use empirical data extracted from a double pulse test (DPT) to obtain switching energies for turn on and turn off at a range of operating points. The subsequent subsection describes the double pulse test. Following the double pulse test, a brief explication of the switching phenomenons during turn on and turn off is explained. This description of switching phenomenons provides valuable insight into behavior within the internal structure of semiconductor devices and the interplay between different devices of VSI. Lastly, to end the section dealing with switching losses, the employment of switching energies in estimate switching losses is delineated.

## 3.4.1 Double Pulse Test

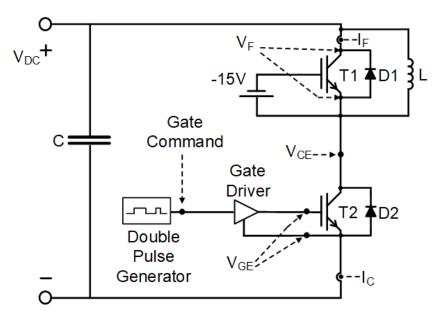

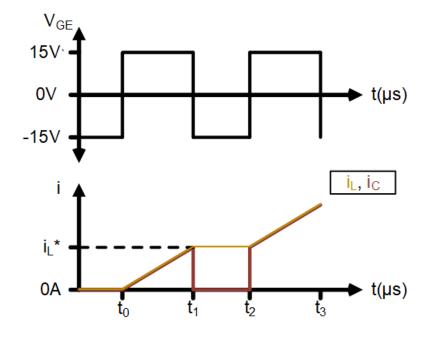

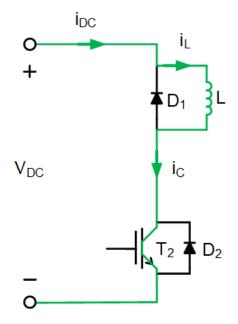

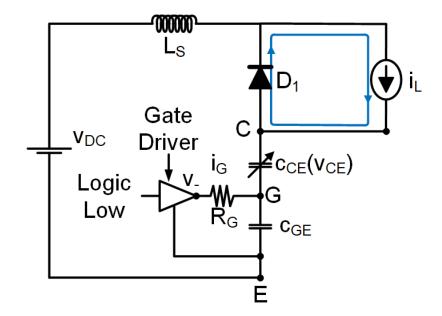

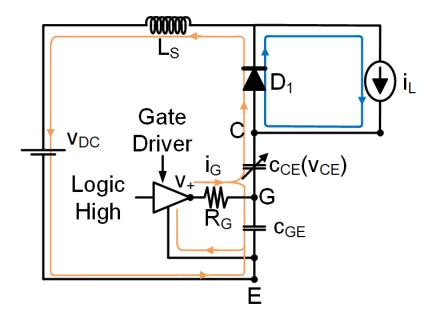

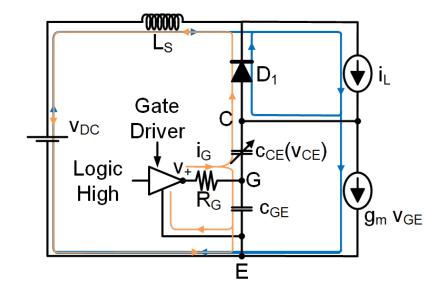

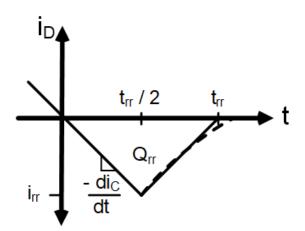

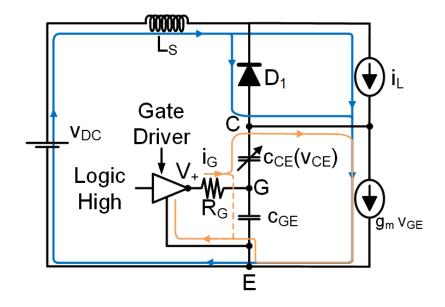

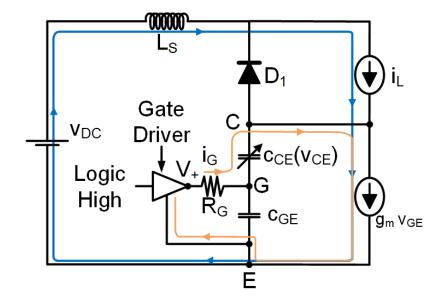

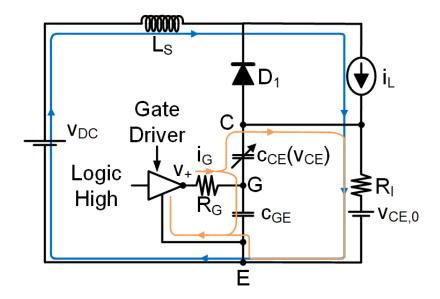

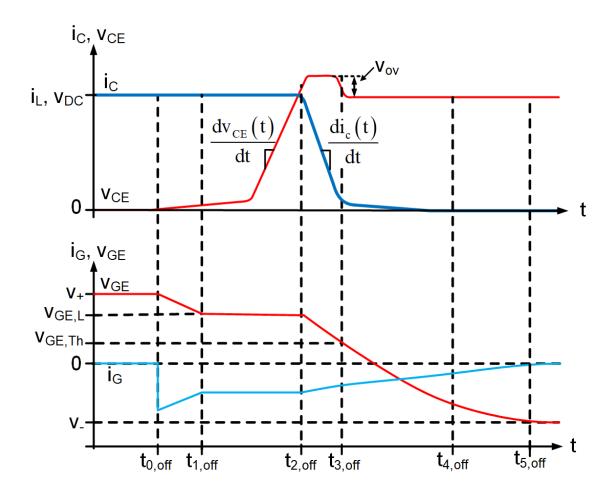

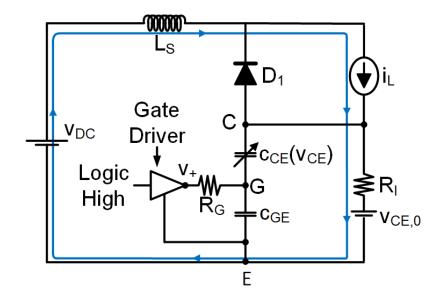

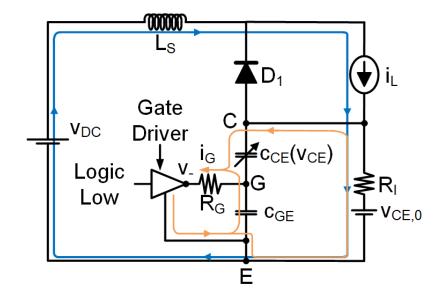

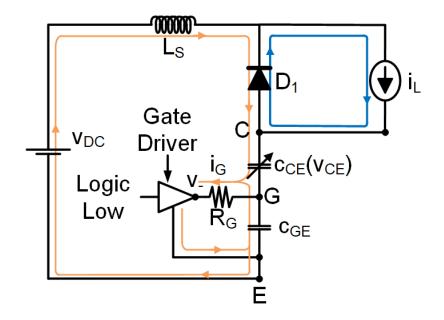

Energies pertaining to the turn on and turn off switching of an IGBT and diode are given in datasheets by manufacturers for specified applied current and DC-link voltage. Inside a half-bridge configuration, a semiconductor's behavior is impacted by the operation of other semiconductor devices. This interplay is accounted for by manufacturers when they are obtaining the energies. A half-bridge setup employing an inductor load is used in a Double Pulse Test (DPT) to evaluate the switching energies experimentally. Only the switching energies of one IGBT switch and its complementary FWD is needed due to symmetry. A typical testing setup characterizing IGBT  $T_2$  and Diode  $D_1$  is depicted in Figure 3.8.

Since the DPT setup experimentally measures the switching energies of IGBT  $T_2$  and FWD  $D_1$ , IGBT  $T_1$  is forced to be off by gating signal, and  $D_1$  happens to remain in blocking mode due to testing conditions. Because IGBT  $T_1$  is always off, it will be discarded from the discussion on the DPT.

Figure 3.8: Double Pulse Testing Setup

In pursuit of obtaining the switching energies of diode  $D_1$  and IGBT  $T_2$  two pulses are applied as gating signals to IGBT  $T_2$  triggering turn on and turn off for both IGBT  $T_2$  and diode  $D_1$ . A double pulse test can be divided into three intervals, as conveyed in Figure 3.9.

Figure 3.9: Double Pulse Testing Intervals defining turn on and turn off instants

• Interval i (spanning from  $t_0$  to  $t_1$ )

IGBT  $T_2$  is turned on for a time span of  $\Delta t_1$ , i.e.  $t_1 - t_0$ . For a given DC-link voltage and load inductance, the time period  $\Delta t_1$  is calculated to generate desired load current  $(i_L)$  for both turn on and turn off. Load current's dependence on the load inductance, DC-link voltage, and the time elapsed is encapsulated by

$$i_L(t) = \frac{v_{DC} \,\Delta t_1}{L}.$$

(3.10)

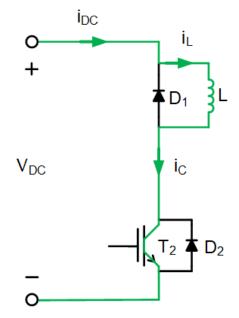

The current flows from DC-link into the load and IGBT  $T_2$  as shown in Figure 3.10.

Figure 3.10: Interval i of Double Pulse Test in static operation  $(t_0 < t < t_1)$

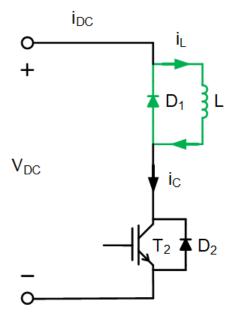

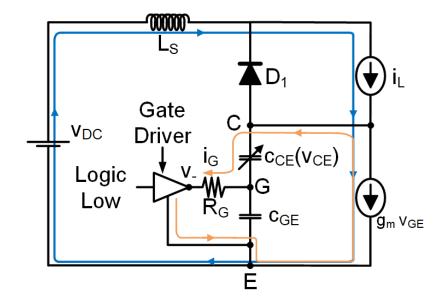

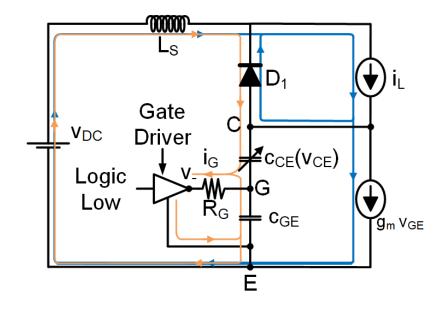

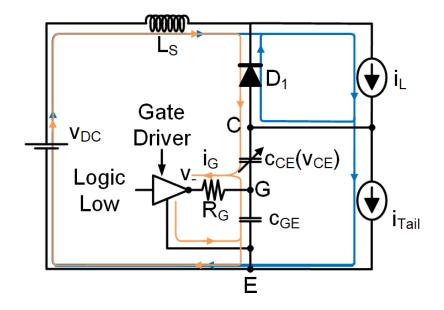

• Interval ii (spanning from  $t_1$  to  $t_2$ )

At  $t_1$ , IGBT  $T_2$  is turned off for a time period ending at  $t_2$ . The gate-driver sends a gating signal instructing IGBT  $T_2$  to turn off, i.e. at  $t_1$ , initiating the dynamic transition where the load current commutates from entirely flowing through the IGBT  $T_2$  to free-wheeling via complementary diode  $D_1$ . Moreover, the turn off interval for the IGBT  $T_2$  inducing a negative voltage on the inductive load turning diode  $D_1$  on. This transient dynamic behavior initiated at  $t_1$ simultaneously constitutes the turn off and turn on intervals where the energies are estimated for IGBT  $T_2$  and diode  $D_1$ , respectively. As previously explained, interval i produces a desired current, this means that the switching transitions used to evaluate the switching energies ,turn on and turn off of IGBT  $T_2$  and diode  $D_1$  respectively, are with respect to this current. When IGBT  $T_2$  is completely off due to the short time span and low parasitic resistance of commutation path a constant current circulates entirely between the free-wheeling diode  $D_1$  and the load as conveyed in Figure 3.11 and Eq. 3.10.

Figure 3.11: Interval ii of Double Pulse Test in static operation  $(t_1 < t < t_2)$

• Interval iii (spanning from  $t_2$  to  $t_3$ )