## Advanced Control of Regenerative Cascaded H-Bridge (CHB) Motor Drives

#### ADVANCED CONTROL OF REGENERATIVE CASCADED H-BRIDGE (CHB) MOTOR DRIVES

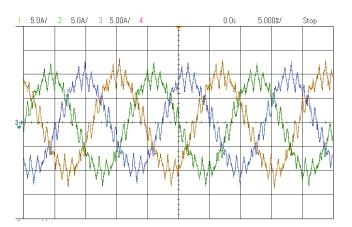

BY

ZHITUO NI, M.Sc.

A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

#### AND THE SCHOOL OF GRADUATE STUDIES

OF MCMASTER UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

© Copyright by Zhituo Ni, February 2021

All Rights Reserved

| Doctor of Philosohpy (2021)         |

|-------------------------------------|

| (Electrical & Computer Engineering) |

McMaster University Hamilton, Ontario, Canada

| TITLE: | Advanced Control of Regenerative Cascaded H-Bridge (CHB) |

|--------|----------------------------------------------------------|

|        | Motor Drives                                             |

| AUTHOR: | Zhituo Ni                                                 |

|---------|-----------------------------------------------------------|

|         | M. Sc. (Automotive Engineering)                           |

|         | Ontario Tech University, Canada                           |

|         | M. Sc. (Electrical Engineering)                           |

|         | Nanjing University of Aeronautics and Astronautics, China |

|         |                                                           |

SUPERVISOR: Dr. Mehdi Narimani

NUMBER OF PAGES: xix, 215

To my parents, Youlin & Guiying.

#### Abstract

Medium-voltage (MV) motor drives have found widespread applications in various heavy industries, such as in the oil and gas sectors, production plants, and process industries. Conventional cascaded H-bridge (CHB) multilevel inverters dominate the medium-voltage industrial drives domain due to their modularity, scalability, and reliability. The most prevalent CHB topology in the drive industry is based on the diodes-front-end (DFE) rectifier, which greatly limits the industrial application of the conventional CHB drives where the ability of handling regeneration is required. The main objective of this thesis is to develop a low-cost, high performance, reliable regenerative CHB drive. The thesis is concentrating on reducing the gridtied filter size, shrinking the DC-link capacitors, improving the system's performance and reliability through advanced control techniques.

First, to reduce the number of passive filter components, a new sideband harmonic active filtering strategy based on the carrier-shifting method is proposed for regenerative CHB drives. This proposed approach extends the carrier shifted PWM method for regenerative CHB drives to further reduce the required passive filter size significantly and thus improves the overall size, cost, and efficiency while complying with IEEE Std 519-2014 grid standard. Second, a novel voltage ripple controller is proposed to reduce the dc-link capacitance in the three-phase regenerative CHB drive without adding extra measurements. Third, to achieve a faster dynamic

response and the multi-objective performance during the control of CHB drives, a novel highperformance predictive control with long prediction horizons is proposed to improve the control performance of the CHB multilevel inverters. The formulation of the proposed high-performance finite control set model predictive control (FCS-MPC) is explained in detail and analyzed to reduce the real-time computation burden. Last, when a fault is detected in the regenerative CHB drive system, the reliability and fault-tolerant ability are considered as the main issues. To improve the drive system reliability, a non-symmetrical selective harmonic elimination (SHE) formulation is proposed to extend the output voltage range with a good harmonic profile under post-fault conditions.

Experimental validation of the proposed algorithms is presented for the operation of a scaled-down seven-level regenerative CHB drive system. These proposed techniques make the regenerative CHB drive a promising solution for future medium-voltage regenerative drive applications in terms of cost, performance, and reliability.

### Acknowledgments

First and foremost, I would like to express my sincere gratitude to my supervisor, Dr. Mehdi Narimani, for his generous supports during my whole Ph.D. career. He teaches me how to become a good researcher and how to deal with different dilemmas in my life. This would be a priceless treasure for me.

Many thanks also to my colleagues in HiPEL, especially Ahmed Hisham, Sarah Badawi, and Shaoyi Yuan, for their generous help in my research and common efforts in building up the experimental prototype and discussing the new ideas. I cannot forget the days and nights we worked together in HiPEL.

I would also like to thank Dr. Navid Zargari and Dr. George Cheng from Rockwell Automation Canada for their guidance and support. They generously share with us their opinions from an industrial perspective. Their discussions motivate me to widen my knowledge to deal with real-world challenges.

Great thanks go to my parents: Mr. Youlin Ni and Mrs. Guiying He. But for them, it is impossible to complete my Ph. D degree abroad.

### Contents

| 1 1                                                 |

|-----------------------------------------------------|

| tion 1                                              |

| Motivation 1                                        |

| Research Objectives and Contributions               |

| Publications                                        |

| Thesis Outlines                                     |

| 2                                                   |

| tion to Regenerative CHB Motor Drives14             |

| Introduction                                        |

| Grid-Tied Filter Design Challenges                  |

| 1. Optimal LCL Filter Design Challenge for CHB AFEs |

| 2. Optimal Filter Design Challenge for CHB AFEs     |

| DC-Link Capacitor Size Reduction Challenge          |

| High-Performance Controllers for CHB drives         |

| Fault-Tolerant Techniques for CHB drives            |

|                                                     |

| Chapter 3                                                               | . 39 |

|-------------------------------------------------------------------------|------|

| Optimal Filter Design for Regenerative CHB Drives                       | . 39 |

| 3.1. Introduction                                                       | . 39 |

| 3.2. L Filter Design for a Seven-level Regenerative CHB Drive           | . 43 |

| 3.2.1. Conventional L Filter Design Procedure                           | . 45 |

| 3.2.2. L Filter Design with 1980 Hz Switching Frequency                 | . 48 |

| 3.2.3. L Filter Design with 3000 Hz Switching Frequency                 | . 51 |

| 3.2.4. L Filter Design Summary                                          | . 53 |

| 3.3. Optimal LCL Filter Design of Regenerative CHB Drives               | . 54 |

| 3.3.1. Proposed Optimal LCL Filter Design for Regenerative CHB Inverter | . 55 |

| 3.3.2. Simulation Result and Discussion                                 | . 61 |

| 3.4. Proposed Active Filter Design (Method 1)                           | . 65 |

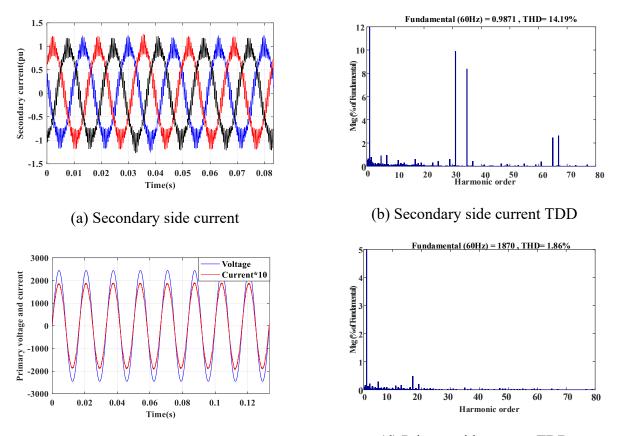

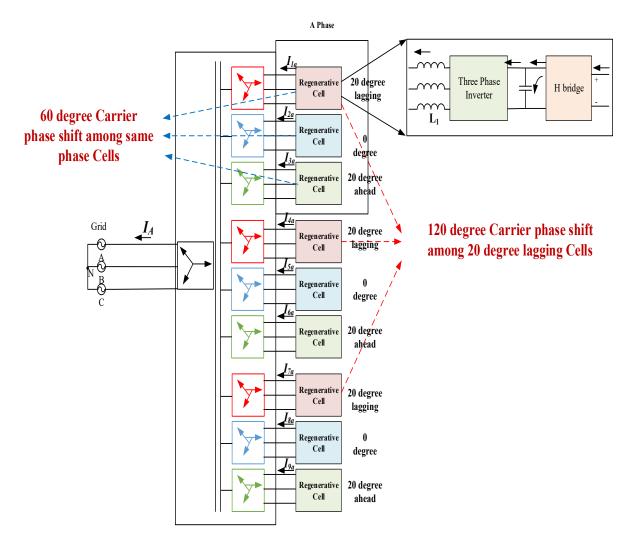

| 3.4.1. Carrier Shifted Control Scheme to Eliminate 31st Order Harmonics | . 66 |

| 3.4.2. Trap Filter Design for 35 <sup>th</sup> Order Harmonics          | . 68 |

| 3.4.3. Simulation Result for the Proposed Filter (Method 1)             | . 70 |

| 3.5. Proposed Active Filter Design (Method 2)                           | . 72 |

| 3.6. Proposed Active Filter Design (Method 3)                           | . 75 |

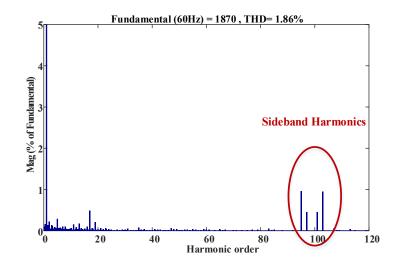

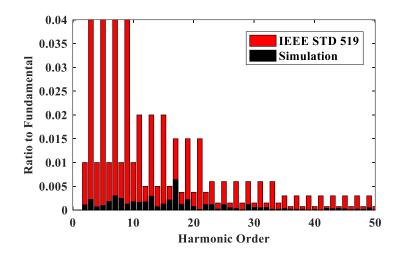

| 3.6.1. Simulation Result for the Proposed Filter Method 3               | . 79 |

| 3.7. Filter Design Summary for Regenerative CHB Drives                  | . 82 |

| 3.8. Experiment Result                                                  | . 82 |

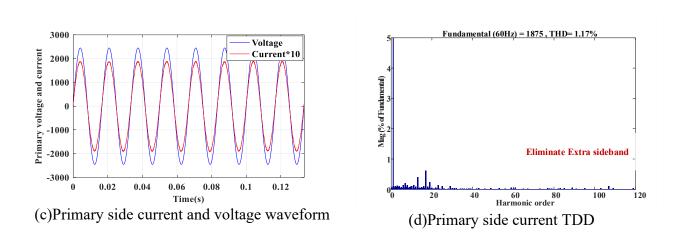

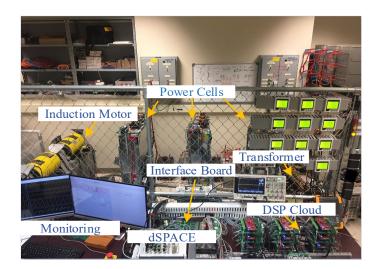

| 3.8.1. Prototype Description                                            | . 83 |

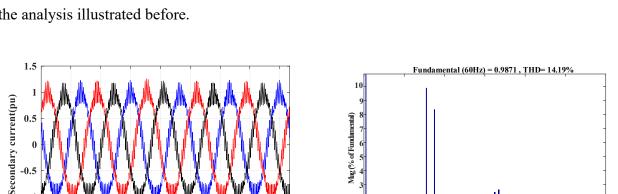

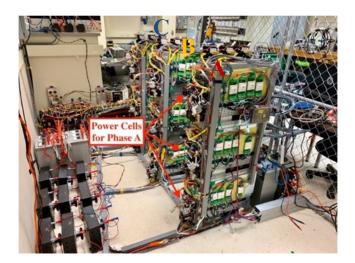

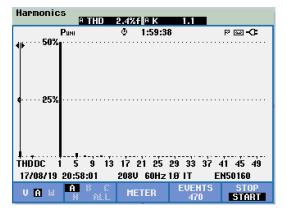

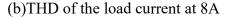

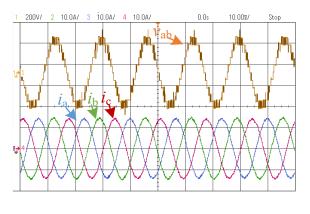

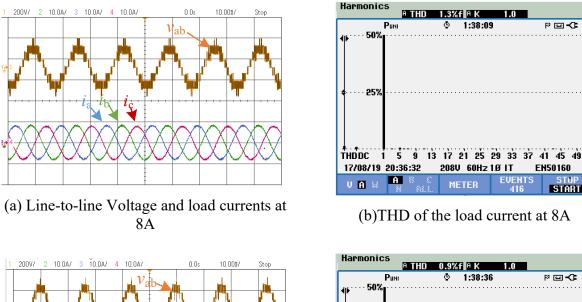

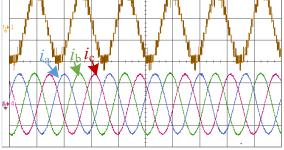

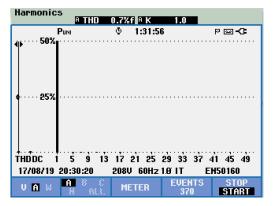

| 3.8.2. Experiment Results under 1980Hz Switching Frequency              | . 86 |

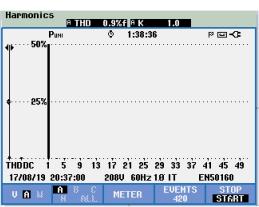

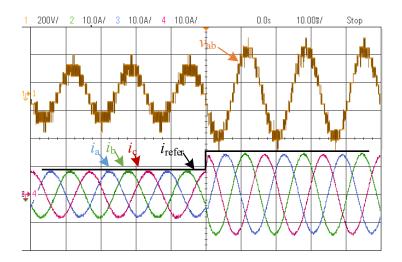

| 3.8.3. Experiment Results under 900 Hz Switching Frequency              | . 88 |

| 3.9. Conclusion                                                         | . 92 |

| Chapter 4                                                                         |

|-----------------------------------------------------------------------------------|

| A New DC-Link Ripple Voltage Controller for Regenerative CHB Drives to Reduce the |

| DC-link Capacitance                                                               |

| 4.1. Introduction                                                                 |

| 4.2. Instantaneous Power Flow Analysis                                            |

| 4.2.1. Root Cause of Large dc-link Capacitance                                    |

| 4.2.2. Constant Average Power Delivered through AFE                               |

| 4.2.3. Pulsating Power Ripple Delivered through AFE                               |

| 4.2.4. Ripple Current Component Cancellation 100                                  |

| 4.3. Proposed Voltage Ripple Controller                                           |

| 4.3.1. Structure of the Proposed Voltage Ripple Controller                        |

| 4.3.2. Stability Problem Illustration                                             |

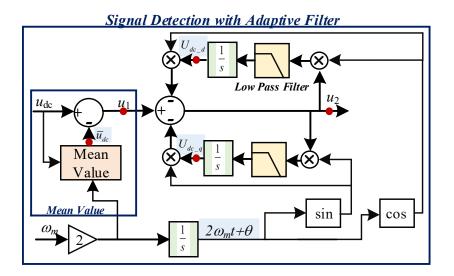

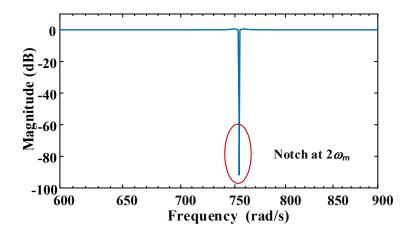

| 4.3.3. Signal Detection with Adaptive Filter 104                                  |

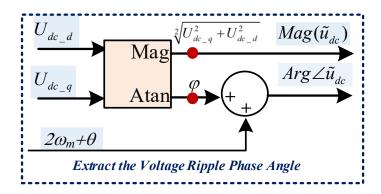

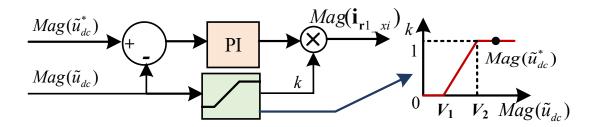

| 4.3.4. Proposed Voltage Ripple Control 108                                        |

| 4.4. Simulation Studies109                                                        |

| 4.5. Experiment Result                                                            |

| 4.6. Discussion                                                                   |

| 4.7. Conclusion                                                                   |

| Chapter 5                                                                         |

| A Novel High-Performance Predictive Control Formulation for CHB Drives            |

| 5.1. Introduction                                                                 |

| 5.2. Cost Function Based FCS-MPC for a Seven-level CHB Inverter                   |

| 5.2.1. Discrete Model of a Seven-level CHB Inverter                               |

| 5.2.2. Cost Function Based FCS-MPC Formulations                                   |

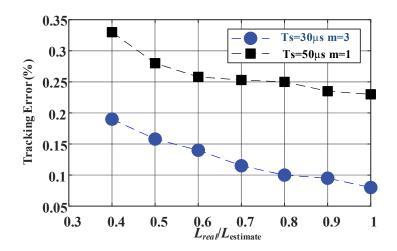

| 5.3. F      | Proposed Fast High-performance FCS-MPC Formulation                 | 129       |

|-------------|--------------------------------------------------------------------|-----------|

| 5.3.1.      | Reference Current Prediction                                       | 129       |

| 5.3.2.      | Proposed formulation for single-step prediction MPC                | 130       |

| 5.3.3.      | Proposed Formulation for <i>m</i> -step Prediction MPC             |           |

| 5.4. 8      | Simulation Results                                                 |           |

| 5.5. H      | Experimental Results and Discussions                               | 144       |

| 5.5.1.      | Single Step Prediction MPC Comparison                              |           |

| 5.5.2.      | Dynamic Performance                                                |           |

| 5.5.3.      | Long Prediction Horizon MPC Performance                            | 150       |

| 5.5.4.      | Sensitivity Analysis of the proposed MPC formulation               | 151       |

| 5.5.5.      | Discussion                                                         | 152       |

| 5.6. (      | Conclusion                                                         | 154       |

| Chapter 6.  |                                                                    | 155       |

| A New Fau   | alt-Tolerant Technique based on Non-Symmetrical Selective Harmonic | ;         |

| Elimination | n (SHE) for CHB Motor Drives                                       | 155       |

| 6.1. I      | ntroduction                                                        | 155       |

| 6.2. H      | Proposed Fault Tolerant Design Framework                           | 157       |

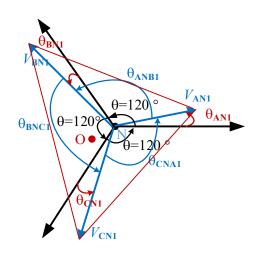

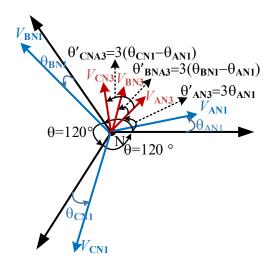

| 6.2.1.      | Fundamental Frequency Phase-Shifted Compensation                   | 157       |

| 6.2.2.      | Third-Harmonic Injection                                           | 159       |

| 6.2.3.      | Proposed Automated Fault Tolerant Design Optimization Framework    | k 162     |

| 6.3. S      | Simulation Results                                                 | 167       |

| 6.3.1.      | Maximum Line-to-line voltages without DC Component                 | 168       |

| 6.3.2.      | Maximum Line-to-line Voltages with DC Component Control for Br     | aking 171 |

| 6.4. H      | Experimental Results and Discussion                                |           |

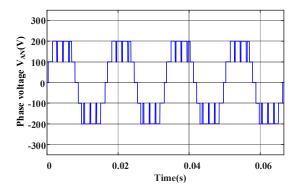

| 6.4.1.     | Maximum Output voltages without DC component Injection 1              | 75  |

|------------|-----------------------------------------------------------------------|-----|

| 6.4.2.     | Maximum Line-to-line voltages with DC component Control under fault 1 | .80 |

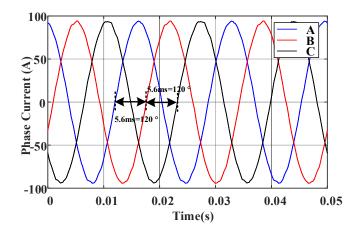

| 6.4.3.     | Dynamic Performance with the Induction Motor 1                        | .83 |

| 6.4.4.     | Discussion1                                                           | .86 |

| 6.5. C     | onclusion1                                                            | .89 |

| Chapter 7  |                                                                       | .91 |

| Summary a  | nd Future Work 1                                                      | 91  |

| 7.1. St    | ummary 1                                                              | .91 |

| 7.1.1.     | Optimal Filter Design 1                                               | .91 |

| 7.1.2.     | DC-Link Capacitance Reduction 1                                       | .93 |

| 7.1.3.     | High-performance FCS-MPC 1                                            | .94 |

| 7.1.4.     | Improving the Fault-tolerant Ability 1                                | .95 |

| 7.2 Futur  | e Work 1                                                              | .96 |

| References |                                                                       | .98 |

## **List of Tables**

|       | Table 3.1Current Distortion Limits for General Distribution Systems (120V through 69kV) |

|-------|-----------------------------------------------------------------------------------------|

|       | IEEE std 519-2014                                                                       |

|       | Table 3. 2 Seven-Level Regenerative CHB Drive Filter Design Requirement                 |

|       | Table 3. 3    L1    Per unit value for 1980 Hz under 1100V DC voltage                   |

|       | Table 3. 4       Harmonics Exceed the IEEE std 519 2014 Standards under 1980 Hz         |

|       | Table 3. 5    L1    Per Unit Value for 3000 Hz under 1100V DC voltage                   |

|       | Table 3. 6 Harmonics exceed the IEEE std 519 2014 standards under 3000 Hz 52            |

|       | Table 3. 7 Filter Comparison under Different Switching Frequency with 1100 V DC Bus     |

|       | Voltage                                                                                 |

|       | Table 3. 8 LCL Filter Design for a seven-level regenerative CHB Drive for 1980 Hz 62    |

|       | Table 3. 9 Trap Filter for 1980 Hz under 1100V DC Voltage    69                         |

|       | Table 3. 10 Comparison among the designed filters under 1980 Hz (pu) 1100V DC Bus       |

|       | voltage (pu)                                                                            |

|       | Table 3. 11 Seven-Level Regenerative CHB Inverter Prototype Parameters    85            |

|       | Table 3. 12 Performance of the Proposed Filtering Strategy at 900Hz Switching Frequency |

| ••••• |                                                                                         |

|       | Table 4. 1    Seven-level CHB Inverter Main Parameters for Simulation                   |

|       | Table 4. 2 Seven-level CHB Prototype Parameters    114                                  |

| Table 5. 1    Seven-level CHB Prototype Parameters for Experiment                    |

|--------------------------------------------------------------------------------------|

| Table 5. 2 Seven-level CHB Drive System Simulation Main Parameters       140         |

| Table 5. 3 Seven-level CHB Inverter Prototype Parameters    144                      |

| Table 5. 4 MPC Performance Summary based on a Seven-level CHB Inverter Prototype     |

|                                                                                      |

| Table 6. 1 Seven-level CHB inverter Prototype parameters    175                      |

| Table 6. 2 Maximum Balanced Output Voltage Amplitude without DC Injection under One  |

| Cell bypassed                                                                        |

| Table 6. 3 Maximum Balanced Output Voltage Amplitude without DC Injection under      |

| Different Fault cases                                                                |

| Table 6. 4 Comparison of Different Fault Tolerant Methods under One Cell Failure 189 |

| Appendix Table 6. 5. Optimized Gate Switching Angles with no DC Injection 190        |

| Appendix Table 6. 6. Optimized Gate Switching Angles with DC Injection 190           |

# **List of Figures**

| Fig. 1. 1 Seven Level CHB Drive [1]                                             |

|---------------------------------------------------------------------------------|

| Fig. 1. 2 Downhill Conveyor [13] 4                                              |

| Fig. 1. 3 Mine Shovel [14] 5                                                    |

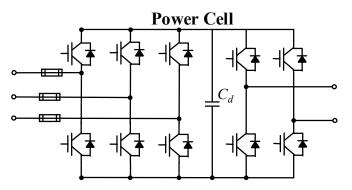

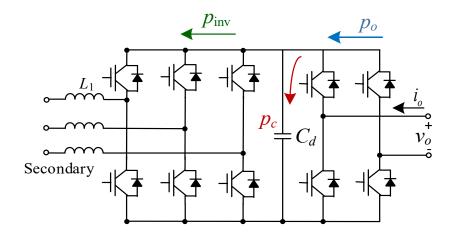

| Fig. 1. 4 Three-phase AFE Power Cell                                            |

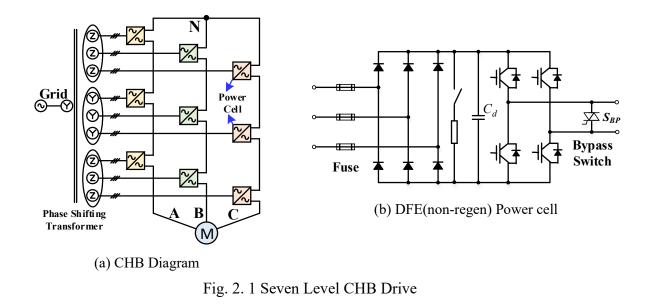

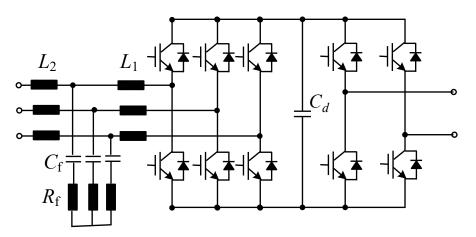

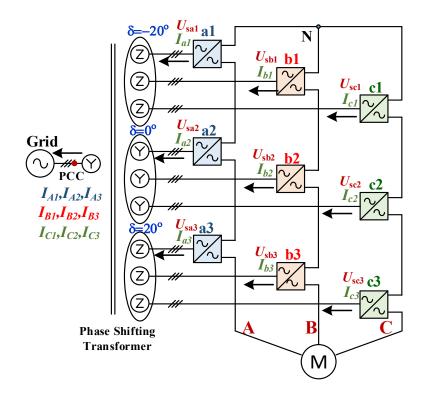

| Fig. 2. 1 Seven Level CHB Drive                                                 |

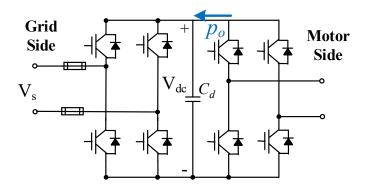

| Fig. 2. 2 Single-phase H-bridge AFE Regenerative Power Cell 17                  |

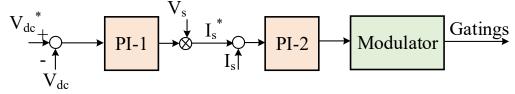

| Fig. 2. 3 Control Scheme of Full bridge AFE [16] 18                             |

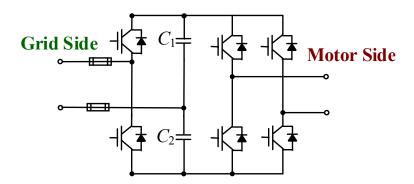

| Fig. 2. 4 Half-bridge AFE Regenerative Power Cell                               |

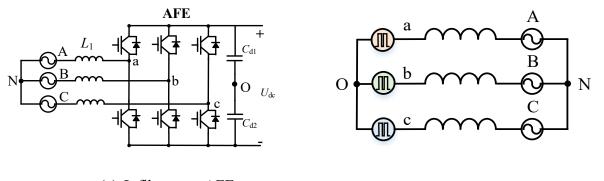

| Fig. 2. 5 Three-phase AFE Regenerative Power Cell 19                            |

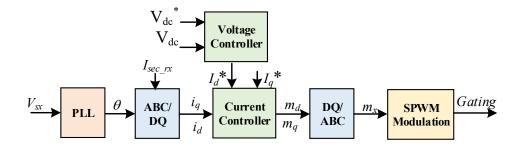

| Fig. 2. 6 Three-phase AFE Control Scheme                                        |

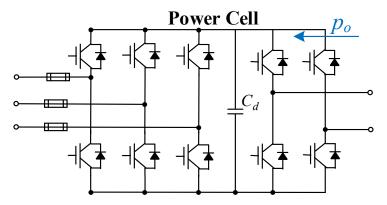

| Fig. 2. 7 Three-phase AFE Regenerative Power Cell                               |

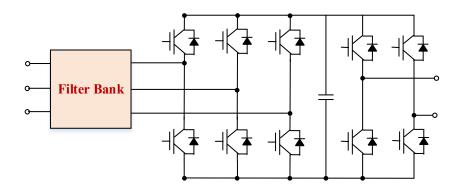

| Fig. 2. 8 Filters for the Three-phase AFE                                       |

| Fig. 2. 9 LCL Filter with Passive Damping Resistor for AFE                      |

| Fig. 3. 1 L-type grid-connected AFE 44                                          |

| Fig. 3. 2 Simplified Single-Phase Equivalent Circuit 46                         |

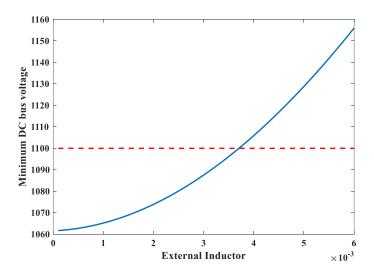

| Fig. 3. 3 Relation Between the $L_1$ Inductance and Minimum Required DC voltage |

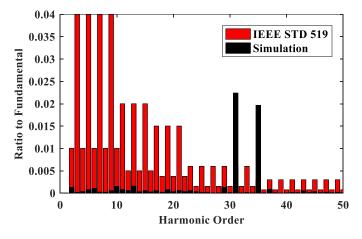

| Fig. 3. 4 Individual Harmonic Contents at 1980 Hz 49                            |

| Fig. 3. 5 Simulation Result under 1980Hz                                          | 50 |

|-----------------------------------------------------------------------------------|----|

| Fig. 3. 6 Individual Harmonic Contents at 3000 Hz                                 | 52 |

| Fig. 3. 7 Simulation Result under 3000 Hz Switching Frequency                     | 53 |

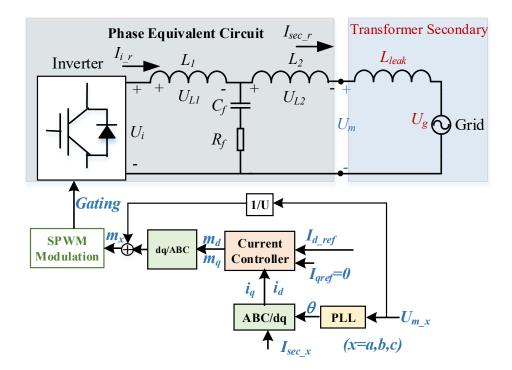

| Fig. 3. 8 Phase Equivalent Circuit and Control Scheme                             | 56 |

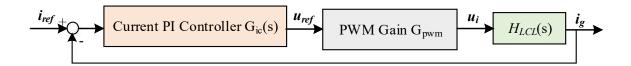

| Fig. 3. 9 Current Control Transfer Function on <i>dq</i> axis                     | 57 |

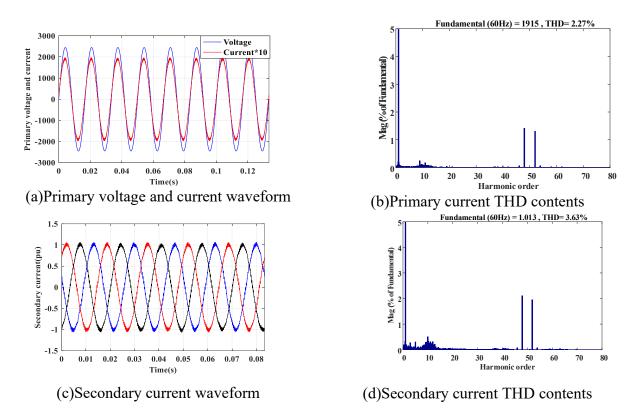

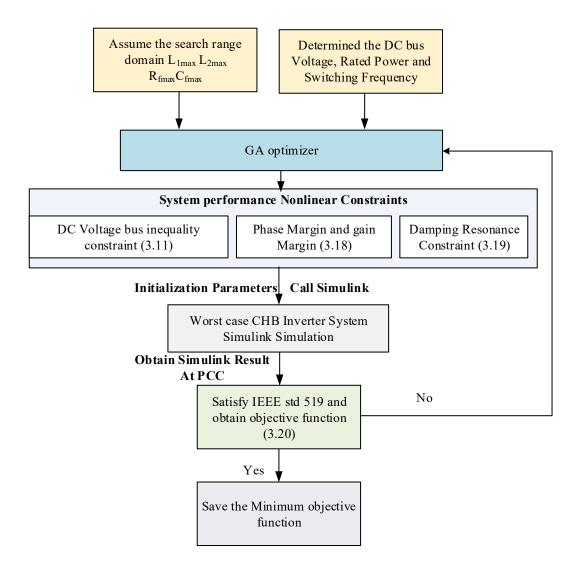

| Fig. 3. 10 Proposed Design Procedure of the LCL filter with GA                    | 60 |

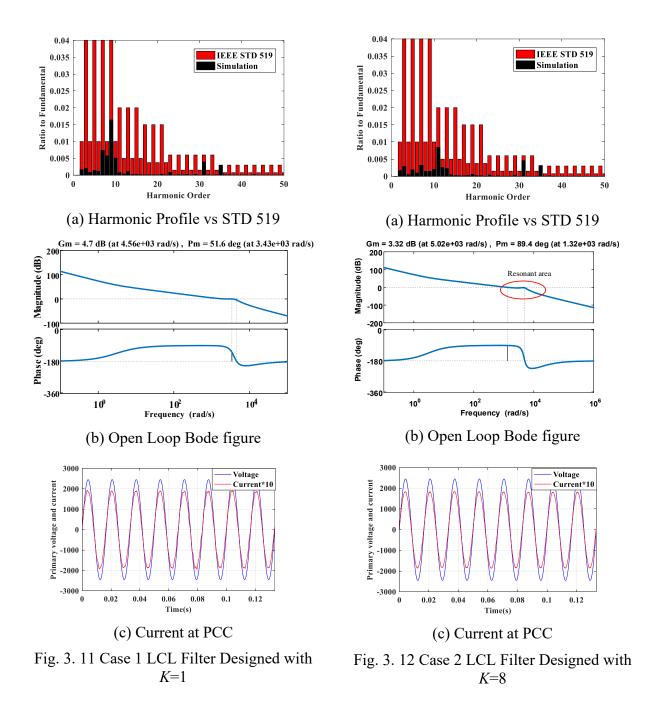

| Fig. 3. 11 Case 1 LCL Filter Designed with <i>K</i> =1                            | 63 |

| Fig. 3. 12 Case 2 LCL Filter Designed with <i>K</i> =8                            | 63 |

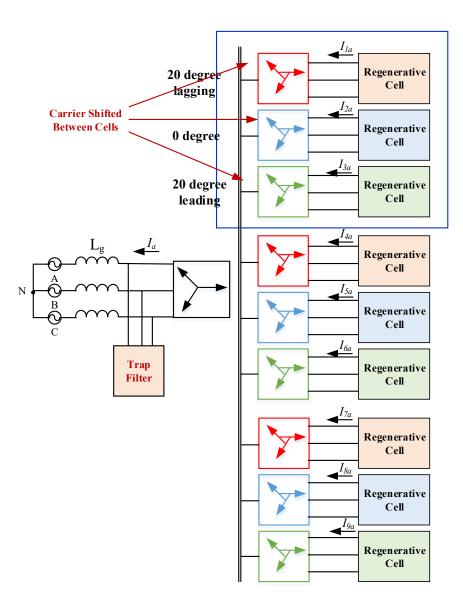

| Fig. 3. 13 Proposed Filter Structure (Method 1)                                   | 66 |

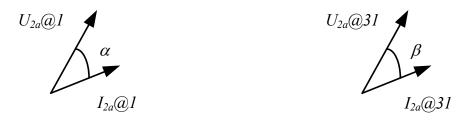

| Fig. 3. 14 Phase Angle Relation between Voltage and Current                       | 67 |

| Fig. 3. 15 Trap Filter for 35 <sup>th</sup> order Harmonic (single-phase diagram) | 69 |

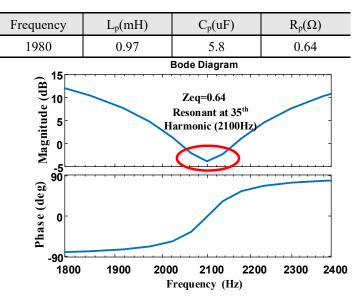

| Fig. 3. 16 Impedance Bode Figure for Trap Filter                                  | 69 |

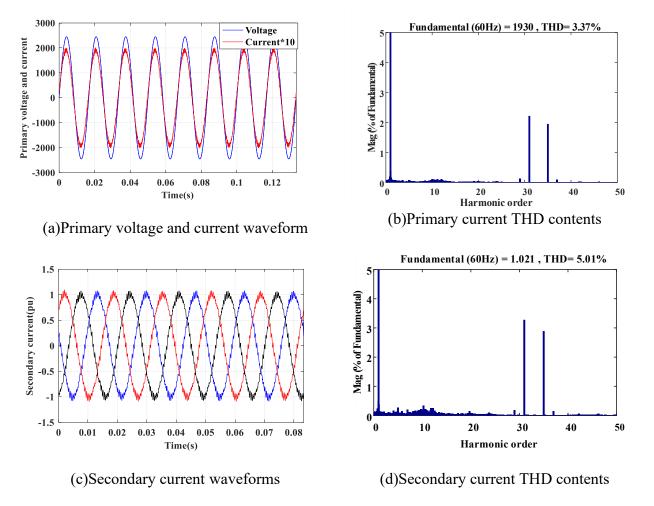

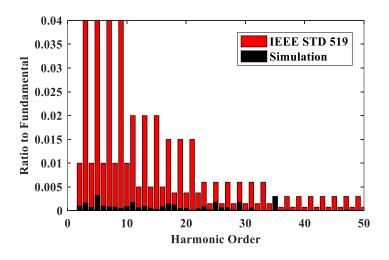

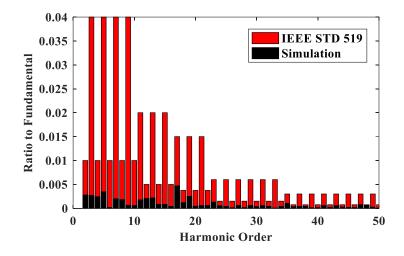

| Fig. 3. 17 Current Harmonic Content at PCC (Method 1)                             | 70 |

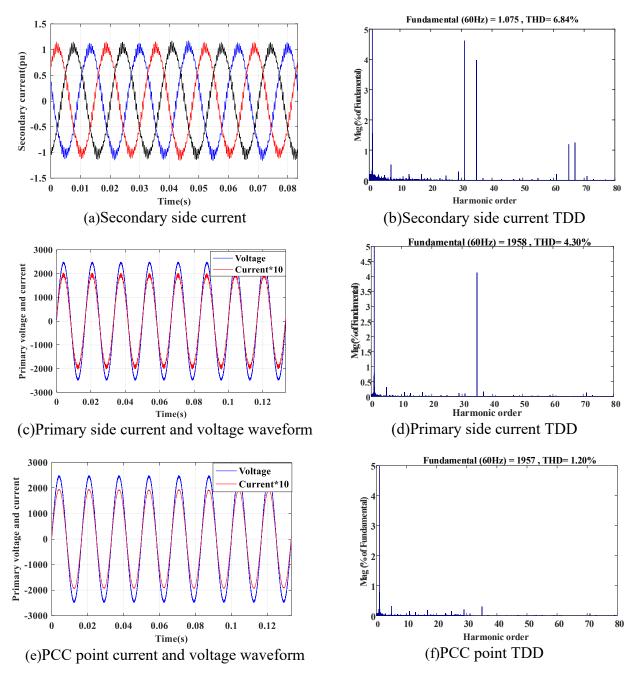

| Fig. 3. 18 Current and Voltage Waveforms for Filter Design (Method 1)             | 71 |

| Fig. 3. 19 Filter Design System Structure (Method 2)                              | 72 |

| Fig. 3. 20 Current Harmonic Content at PCC (Method 2)                             | 74 |

| Fig. 3. 21 Current and Voltage Waveforms for Filter Design (Method 2)             | 75 |

| Fig. 3. 22 Current Harmonic Profile at the PCC with the Proposed Method 2         | 76 |

| Fig. 3. 23 Proposed Filter Structure (Method 3)                                   | 77 |

| Fig. 3. 24 Current Harmonic Content at PCC (Method 3)                             | 79 |

| Fig. 3. 25 Current and Voltage Waveforms for Filter Design (Method 3)             | 80 |

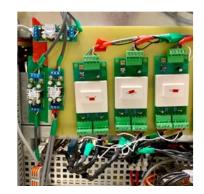

| Fig. 3. 26 Prototype of the Seven-level Regenerative CHB Drive System             | 83 |

| Fig. 3. 27 Prototype of the Seven-level CHB Inverter                              | 83 |

| Fig. 3. 28 One Regenerative Power Cell                                            | 84 |

|       | Fig. 3. 29 Cloud DSP System for AFEs                                                | 85  |

|-------|-------------------------------------------------------------------------------------|-----|

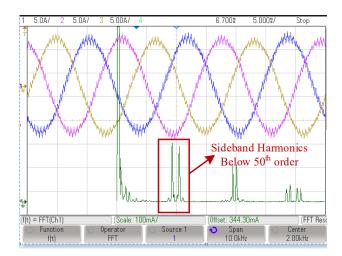

|       | Fig. 3. 30 AFE Three-phase Current at 1980 Hz                                       | 86  |

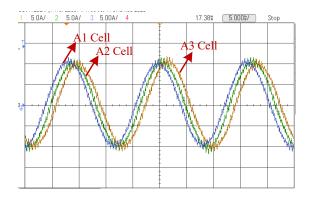

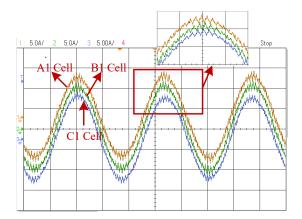

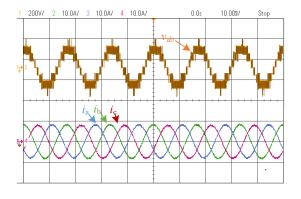

|       | Fig. 3. 31 Power Cells Input Currents in the Same Phase                             | 87  |

|       | Fig. 3. 32 Power Cell Input Current among ABC Phases                                | 87  |

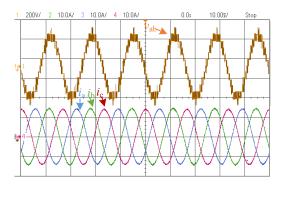

|       | Fig. 3. 33 Current at PCC                                                           | 88  |

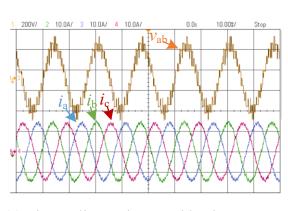

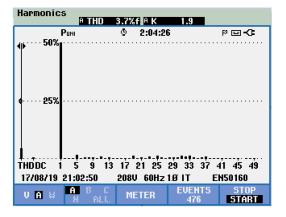

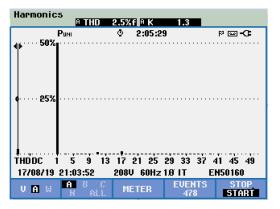

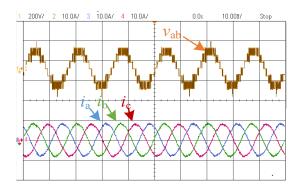

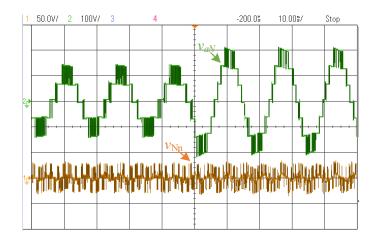

|       | Fig. 3. 34 Experimental Waveforms of the Proposed Optimal Filtering Strategy (M     |     |

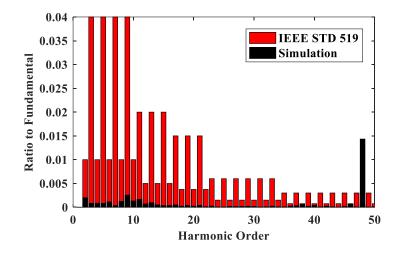

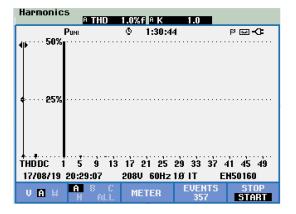

| ••••• | Fig. 3. 35 Current Harmonic Adopting the Proposed Method 2 at 900 Hz                |     |

|       | Fig. 4. 1 Instantaneous Power Flow during Regeneration                              |     |

|       | Fig. 4. 2 Seven-level CHB Drive Illustration for Capacitor Reduction                | 101 |

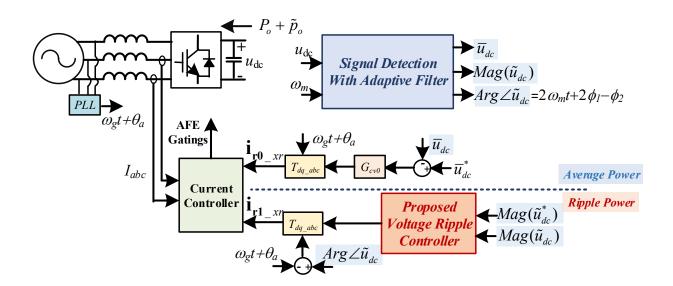

|       | Fig. 4. 3 Proposed DC Bus Voltage Control Scheme                                    | 102 |

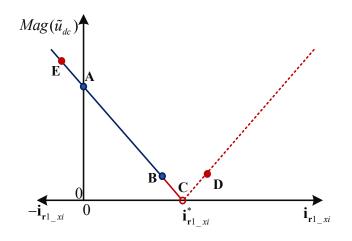

|       | Fig. 4. 4 Potential Operation Condition                                             | 103 |

|       | Fig. 4. 5 Signal Detection with Adaptive Filters                                    | 105 |

|       | Fig. 4. 6 Frequency Response of Adaptive Filter H(s) $T_1=0.1$ , $\omega_m=60*2\pi$ | 107 |

|       | Fig. 4. 7 DC Voltage Ripple Phase Angle Estimation                                  | 108 |

|       | Fig. 4. 8 Proposed Voltage Ripple Controller                                        | 108 |

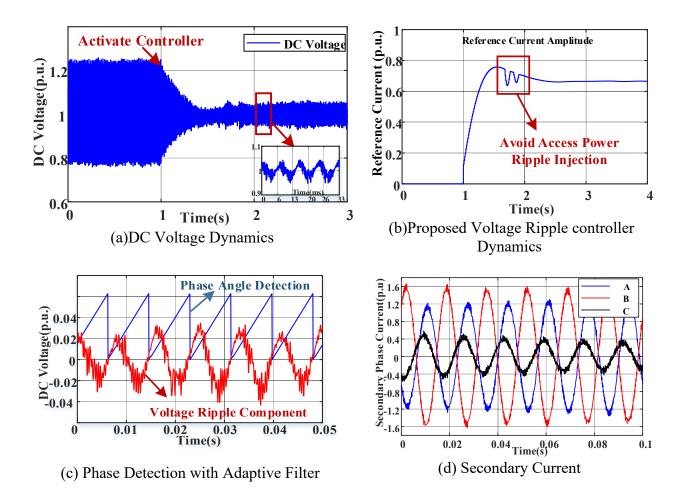

|       | Fig. 4. 9 Performance of the Proposed Capacitor Reduction Controller                | 111 |

|       | Fig. 4. 10 Simulation Result with Frequency Variation                               | 113 |

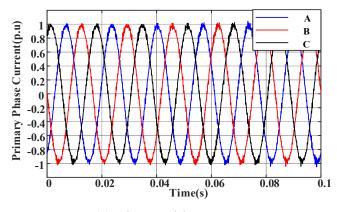

|       | Fig. 4. 11 Prototype of the seven-level CHB system                                  | 114 |

|       | Fig. 4. 12 Experiments at 60 Hz load                                                | 116 |

|       | Fig. 4. 13 Experiments at 40 Hz load                                                | 118 |

|       | Fig. 4. 14 Performance Under Conventional PI Controller                             | 119 |

|       | Fig. 5. 1 Diode-Front-End Seven-Level CHB Inverter                                  | 123 |

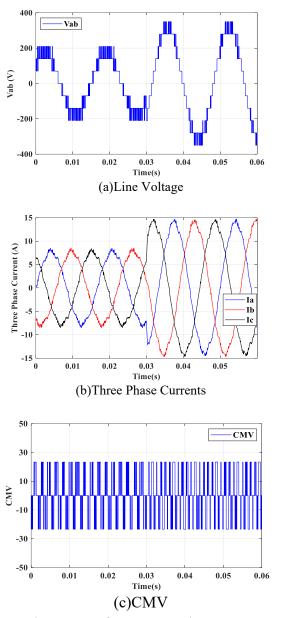

|       | Fig. 5. 2 Performance under Current Amplitude Change                                | 138 |

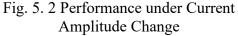

| Fig. 5. 3 Performance under Current Frequency Change                             | 138 |

|----------------------------------------------------------------------------------|-----|

| Fig. 5. 4 FCS-MPC Controller Structure based on IPM                              | 142 |

| Fig. 5. 5 Motor Acceleration Response                                            | 143 |

| Fig. 5. 6 Prototype Seven-level CHB Inverter                                     | 144 |

| Fig. 5. 7 Conventional Single-step prediction MPC Performance at $T_s$ 100 µs    | 146 |

| Fig. 5. 8 Proposed single-step prediction MPC Performance at $T_s$ 100 µs        | 147 |

| Fig. 5. 9 Proposed Single-Step Prediction MPC Performance at $T_s$ 50 µs         | 148 |

| Fig. 5. 10 Current Tracking Dynamic Performance                                  | 149 |

| Fig. 5. 11 CMV and Phase Output Voltage                                          | 150 |

| Fig. 5. 12 Proposed MPC Performance with Prediction Length to be 3               | 151 |

| Fig. 5. 13 Effect of the Modeling Error for the proposed MPC Formulation         | 152 |

| Fig. 6. 1 A Seven-level CHB drive Illustration for Fault Tolerant                | 157 |

| Fig. 6. 2 FPSC Method Voltage Vector Illustration                                | 158 |

| Fig. 6. 3 Unbalanced Third-order Harmonic under FPSC Method                      | 159 |

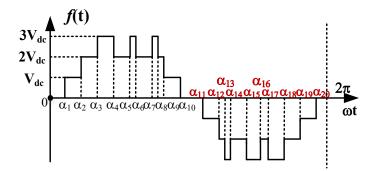

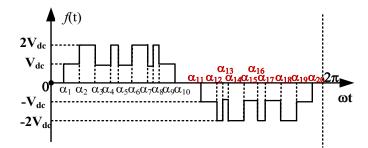

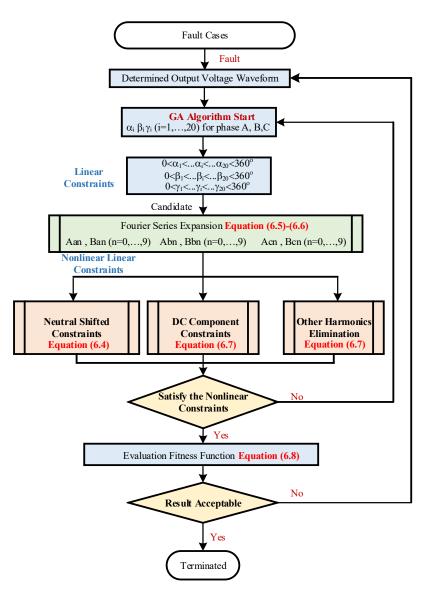

| Fig. 6. 4 Non-symmetrical SHE for CHB Drive                                      | 163 |

| Fig. 6. 5 Automated Optimization Framework for the FPSC Non-symmetrical SHE Meth | hod |

| under Fault                                                                      | 165 |

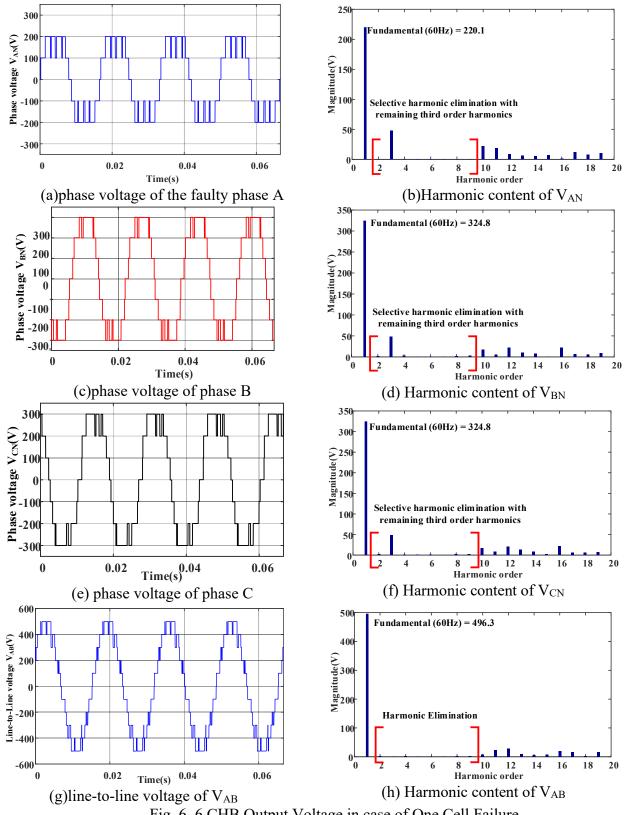

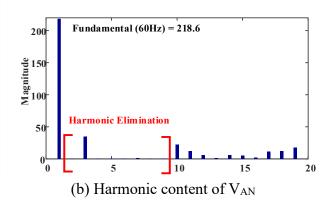

| Fig. 6. 6 CHB Output Voltage in case of One Cell Failure                         | 169 |

| Fig. 6. 7 Load Current Supplied by CHB with Fault Cell                           | 170 |

| Fig. 6. 8 CHB Voltage in case of One Cell Failure with DC Braking Situation      | 172 |

| Fig. 6. 9 Load Current with DC Circulating Current                               | 173 |

| Fig. 6. 10 Maximum Output Line Voltages Comparison                               | 174 |

| Fig. 6. 11 Prototype Seven-level CHB Inverter for Fault Tolerant                 | 175 |

| Fig. 6. 12 Switching Angle Map under Different Output Line Voltages              | 176 |

| Fig. 6. 13 Fault-tolerant Non-symmetrical SHE Method without DC Component Injection    |

|----------------------------------------------------------------------------------------|

|                                                                                        |

| Fig. 6. 14 DC Component Injection between Healthy Phase B and C 180                    |

| Fig. 6. 15 Switching Angle under different DC Injection while Output Voltage is 4.76pu |

|                                                                                        |

| Fig. 6. 16 Fault-tolerant Non-symmetrical SHE method with DC Component Injection. 182  |

| Fig. 6. 17 Fault Tolerant Controller with the Proposed Modulation Schemes 184          |

| Fig. 6. 18 Dynamic performance of the Proposed Motor Control Scheme                    |

| Fig. 6. 19 Line Voltage Harmonic Profile Comparison under the Same Fault Case 188      |

### Chapter 1

### Introduction

#### 1.1. Motivation

Medium-voltage (MV) motor drives have found widespread applications in various high power industries, such as in the oil and gas sectors, production plants, and process industries. The design of controlled high power MV drives is faced with a number of challenges that relate to the topologies and control of grid-side and motor-side converters [1]. On the one hand, high quality of voltage and current waveforms both at the input and output terminals is important, particularly with MV drives. Many different control schemes are applied to the converter to operate at low switching frequency with good performance [2]-[4]. On the other hand, to overcome the voltage and current limitation of power semiconductor devices, numerous different converter topologies have been developed for MV application in recent years [5].

Unlike the low voltage range application, where the two-level voltage source inverter has become the dominant solution, different MV converter topologies are available in the market. The circuit topologies used in MV industrial converters are divided into three categories: voltage source inverters (VSIs), current source inverters (CSIs), and cycloconverters (CCs). The insulated gate bipolar transistor (IGBT) and insulated gate-commutated transistor (IGCT) are usually adopted in the VSIs. In CSIs and CCs, gate-commutated transistors (GCTs) and symmetrical blocking thyristors are employed.

With the rapid development of power semiconductor devices, multilevel voltage-source converters have gained more interest due to their improvement in overall performance [1]. Some of the features of multilevel converters are a reduction in the total harmonic distortion of the AC output waveforms, less switching losses, less switching stresses (dv/dt), an increase in the operating voltage of the converter, and a reduction in the size of interface transformers and output filters [6][7]. Neutral point clamped (NPC) converter, modular multilevel converter (MMC) and Cascaded H-bridge (CHB) converter are the well-established multilevel converters, which are already commercialized by manufacturers in MV drive applications.

Siemens, ABB, and Rockwell Automation are the market leaders in medium voltage multilevel voltage source drives. In Siemens, the NPC topology-based drives GM150 are equipped with the high voltage IGBT/IGCT. The output voltage range of GM150 drives is from 2.3 kV to 4.16 kV [8]. There are two main issues for NPC topology operating at a higher number of levels: dc-link capacitor voltage balancing issue and a significant increase in the number of clamping diodes. At the same time, both the MMC drives GH150 and CHB drives GH180 can reach 11 kV with low voltage IGBTs due to their modular structures. The modular structure, which connects more devices in series and clamps the voltage between respective devices, are highly attractive due to their scalability in terms of voltage range and power levels. Modular technology is capable of reaching medium output voltage levels using only standard low-voltage

mature technology components. This characteristic allows one to achieve high-quality output voltages, input currents. However, the MMC converter has a voltage balancing issue for the motor operating at a lower speed. What's more, the ABB releases the counterparts CHB drives ACS580MV drives [9]. The converter output voltage range of ABB is the same as those at Siemens. Meanwhile, Rockwell Automation produces the PowerFlex 6000 CHB MV drives for the motor rated from 2.3 kV to 11 kV up to 11 MW [10]. From the industry perspective, CHB multilevel inverters are the most popular solution in the high-power MV drive industry.

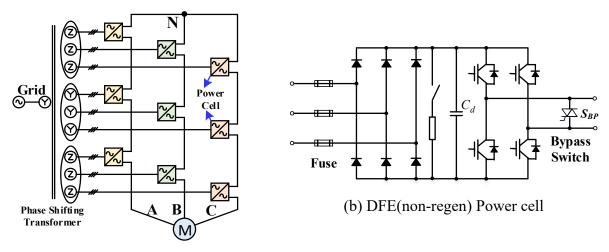

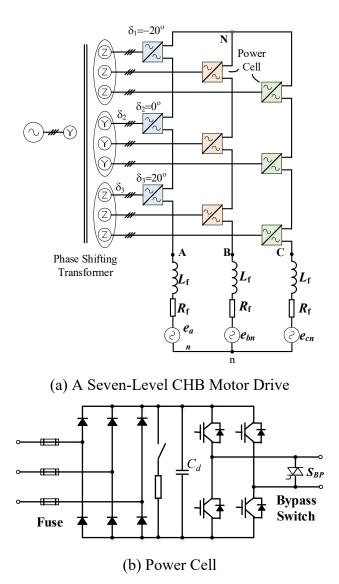

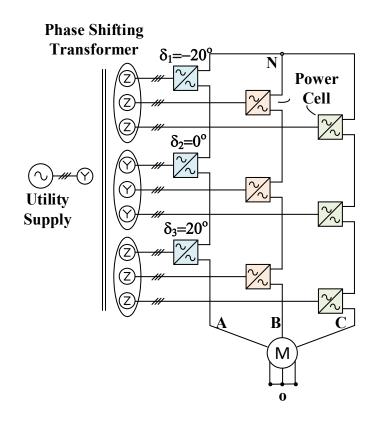

CHB inverter is composed of a number of H-bridge power cells, which are cascaded in the motor side to achieve the full medium voltage range with low harmonic distortion as shown in Fig. 1(a). An isolated DC supply is required to feed each H-bridge cell. The most prevalent CHB topology in the drive industry is based on the diodes-front-end (DFE) H bridge cell, shown in Fig. 1(b) [11].

(a) CHB Diagram

Fig. 1. 1 Seven Level CHB Drive [1]

The isolated DC supplies are obtained through a phase-shifting transformer and threephase diode rectifiers. The phase-shifting transformer can produce a three-phase set of secondary voltages shifted by a certain angle (depends on the number of secondaries) with respect to the primary voltage. The three-phase rectifiers are fed by secondary windings with phase angle shifted. The angles of the phase-shifting transformer help to eliminate low order harmonics on the primary currents. With a high number of secondaries (typically higher than 9), no additional passive filter or active filter is needed to satisfy the harmonics standards [12].

Due to the DFE, the most prevalent CHB medium-voltage drive illustrated can only operate in two quadrant modes. This limits the industrial application of the conventional CHB drives where the ability of handling regeneration is desired, such as downhill belt conveyors [13] and high power shovel applications [14]. The downhill conveyor is shown in Fig. 1.2 which transports the mineral from the mine to the concentrator.

Fig. 1. 2 Downhill Conveyor [13]

During the downhill moving, the motor will regenerate a large amount of electrical energy to the DC-link capacitors through the H-bridges. To protect the system, this regenerative energy is wasted on the damping resistor in the DC-link of the CHB drives, which leads to the low efficiency where regeneration happens for a long period. When the amount of ore to be handled is in the range of 100,000 tons/day, the power generated by the conveyor may exceed several megawatts and are wasted [13] [15].

Another example is the industry shovel as is shown in Fig. 1.3, which is a piece of critical high power equipment in every mining industry and their operational availability has an important impact on production. The regenerated energy is wasted during shovel cycle operation when the conventional CHB drives are adopted.

Fig. 1. 3 Mine Shovel [14]

The power regenerated by the load may exceed several megawatts and thus must be delivered to the electrical utility for saving energy. The drive system must be able to transmit the energy of the load back to the three-phase source. Therefore, the next generation of medium voltage CHB drives is preferred to be equipped with the regeneration ability to meet the diverse requirements from the industrial markets.

#### **1.2. Research Objectives and Contributions**

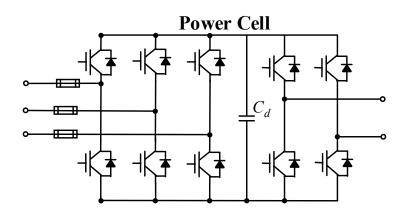

Regeneration capability can be achieved by adding an active front end (AFE) rectifier at the input side instead of the DFE in each power cell of the CHB drives as shown in Fig. 1.4. With the existing phase-shifting transformer, the IGBT anti-diodes can still work as the threephase rectifiers to provide the isolated DC supplies for the power cells during motoring operation.

Fig. 1. 4 Three-phase AFE Power Cell

The IGBT based AFE also allows a power flow from the load to the source during regeneration operation. With this regenerative CHB topology, however, there are several emerging challenges required to be tackled:

In regeneration operation, AFE introduces the switching harmonics that may deteriorate the grid current quality to the extent that violates the IEEE 519-2014 harmonic standard. Therefore, a filter bank is required between the AFE and the grid, to attenuate current harmonics. Reducing the required filter bank is the crucial point to the CHB drive system cost, volume, and thermal dissipation. However, it has been observed that there is very little information available describing the design of a filter bank for the regenerative CHB drives. Therefore, designing and optimizing the filter bank for the CHB regenerative drive is a challenge.

- 2. During regeneration operation, a DC-link voltage controller is required to stabilize the DC-bus voltage and avoid overvoltage damage. However, with the conventional DC-link voltage controller, the instantaneous power in each power cell between the three-phase AFE and the single-phase H bridge is not balanced. This unbalanced power ripple leads to a large designed DC-link capacitance, which increases the system's volume and cost and reduces the system reliability. DC-link capacitance reduction for the CHB regenerative drive is another challenge considering the system cost and life expectancy.

- 3. To achieve a faster dynamic response and the multi-objective performance during the control of the regenerative CHB drives, the finite control set model predictive control (FCS-MPC) method has been considered one of the most promising alternatives. However, the MPC method requires a high number of computations especially for higher-level power converter topologies due to the existence of a huge amount of switching combinations and redundancies. Real-time searching for the optimal switching state at a high sampling rate is sometimes impossible with the standard commercial processors. Thus, designing a high-performance predictive current controller for the regenerative CHB drive is a challenge.

- 4. The CHB converters have been widely used for high-power medium-voltage motor drives due to their reliability features. A significant indicator of the reliability is the maximum balanced line-to-line voltage amplitude under fault conditions. It is challenging to improve the fault-tolerant ability for the CHB drives with a good

harmonic profile under different fault situations after the fault is detected in the CHB drives.

#### **1.3. Publications**

This thesis researches the feasibility of the regenerative CHB drive for future mediumvoltage regenerative industrial drive domain. The author contributes to several original developments, which are presented in the dissertation and briefly summarized as follows:

- New sideband harmonic active filtering strategies are proposed for regenerative CHB drives to reduce the number of passive filter components, and thus improves the overall size, cost, and efficiency while complying with IEEE std 519-2014 grid standard.

- 2. A novel voltage ripple controller is proposed to reduce the dc-link capacitance in the three-phase AFE based regenerative CHB drive without adding extra measurements.

- A novel high-performance finite control set model predictive control (FCS-MPC) with long prediction horizons is proposed to improve the control performance of the CHB multilevel inverters.

- 4. In extremely high power applications where reliability and switching power loss are critical, the selective harmonic elimination (SHE) technique is more suitable for CHB drives which can eliminate a higher number of harmonics with a lower switching number. To improve the system reliability under high power applications, a non-symmetrical SHE formulation is proposed for CHB drives to extend the

output voltage range with a good harmonic profile under different post-fault conditions.

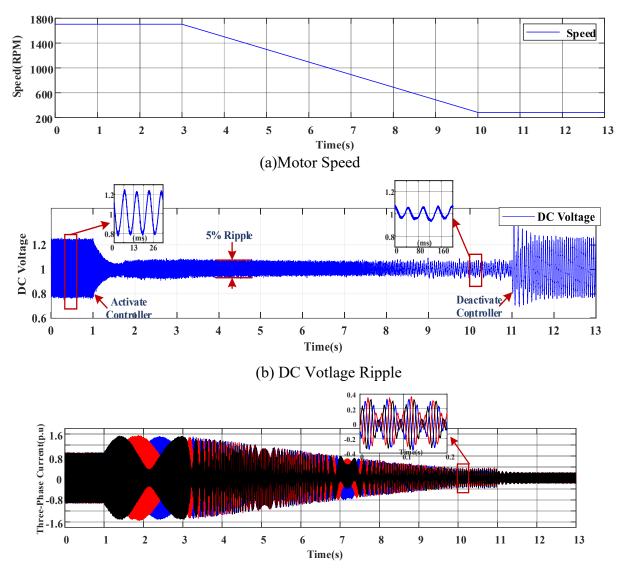

5. An experimental setup is developed to validate the feasibility of the proposed algorithms.

During the time spent working on the thesis, I was also involved in other research projects. Below is a list of all the journal papers and conferences as a result of my work during the Ph. D.:

#### Journal Papers:

- [J1] Z. Ni, A. Abuelnaga, and M. Narimani "A Novel High-Performance Predictive Control Formulation for Multilevel Inverters", IEEE Transactions on Power Electronics, vol. 35, no. 11, pp. 11533 - 11543, 2020.

- [J2] Z. Ni, A. Abuelnaga, and M. Narimani "A New Fault-Tolerant Technique based on Non-Symmetry Selective Harmonic Elimination for Cascaded H-Bridge Motor Drives", IEEE Transactions on Industrial Electronics, April 2020 (Early Access, DOI: 10.1109/TIA.2020.3000712), 11 pages.

- [J3] Z. Ni, A. Abuelnaga, S. Yuan, S. Badawi, M. Narimani, Z. Cheng, and N. Zargari, "A New Approach to Input Filter Design for Regenerative Cascaded-H-Bridge (CHB) Drives," accepted in IEEE Transactions on Industrial Electronics.

- [J4] Z. Ni, A. Abuelnaga and M. Narimani, N. Zargari, "DC-link Voltage Ripple Control of Regenerative CHB Drives for Capacitance Reduction," accepted in IEEE Transactions on Industrial Electronics.

- [J5] S. Yuan, Z. Ni, A. Abuelnaga, B. Sarah, M. Narimani, and N. Zargari, "A New Method to Reduce Current Harmonics of DC-link Capacitors in Grid-tied Cascaded H-bridge Converters," submitted to IEEE Transaction on Industry Application, under review.

- [J6] S. Badawi, A. Abuelnaga, Z. Ni, S. Yuan, M. Narimani, Z. Cheng, N. Zargari, "Reduced Switch-Count Topology for Regenerative Cascaded H-Bridge (CHB) Medium-Voltage Drives," submitted to IEEE Transaction on Power Electronics, under review.

- [J7] M. Norambuena, F. Carnielutti, A. Mokhtar, M. Narimani, Z. Ni, and A. Abuelnaga, "Finite Control Set Model Predictive Control for Multilevel Converters with Reduced Switching Frequency," submitted to IEEE Transaction on Industrial Electronics, under review.

Conference Papers:

- [C1] Z. Ni and M. Narimani, "A New Fast Formulation of Model Predictive Control for CHB STATCOM," IECON 2019 - 45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, pp. 3493-3498, 2019.

- [C2] Z. Ni, M. Narimani and N. R. Zargari, "Optimal LCL Filter Design for a Regenerative Cascaded H-Bridge (CHB) Motor Drive," 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, pp. 3038-3043, 2020.

- [C3] Z. Ni, and M. Narimani, "A New Model Predictive Control Formulation for CHB Inverters," 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, pp. 2462-2466, 2020.

- [C4] Z. Ni, M. Narimani, J. Rodriguez. "A New Model Predictive Control to Reduce Common-Mode Voltage (CMV) of a Four-Level T-NNPC Inverter ", accepted in Applied Power Electronics Conference (APEC), 2021.

The following project is under development and will be published soon:

- [1] **Z. Ni**, M. Narimani, and J. Rodriguez "A Novel Fast MPC Formulation Considering Lineto-Line Redundancy based on 5L T-NNPC", to be submitted to IEEE Transaction on Power Electronics.

- [2] Z. Ni, M. Narimani " A Filterless Control of Regenerative CHB Drives with Maximum DC Voltage Utilization", Under developing, to be submitted to IEEE Transactions on Industrial Electronics.

#### 1.4. Thesis Outlines

This thesis will be concentrated on the advanced control techniques to tackle the illustrated four challenges of the three-phase AFE based regenerative CHB drives. The thesis is comprised of the following six chapters to targeting the mentioned issues one by one. Following is a brief of each chapter:

Chapter 1 provides the motivation and challenges regarding regenerative CHB MV drives and outlines the contributions.

Chapter 2 conducts a review of the conventional CHB drives and analysis the requirements for grid-tied filter size, challenges of the size of the DC-link capacitors, and reliability issue of the CHB drives.

In Chapter 3, first of all, an optimal LCL filter design procedure for a regenerative CHB motor drive is proposed to satisfy the grid harmonic requirement of IEEE Std 519-2014. To take system performance (such as grid impedance, PLL performance, controller saturation) into consideration while minimizing the LCL filter, an optimization framework based on the genetic algorithm (GA) is proposed directly based on the Simulink nonlinear model instead of the tedious mathematical model. Simulation validates the performance of the designed LCL filter using a seven-level regenerative CHB motor drive. Moreover, to further reduce the number of passive filter components, new sideband harmonic active filtering strategies based on the carrier-shifting method are proposed for regenerative CHB drives. This proposed approach extends the carrier shifted PWM method for regenerative CHB drives to further reduce the required passive filter size significantly and thus improves the overall size, cost, and efficiency while complying

with IEEE Std 519-2014 grid standard. The proposed optimal active filtering strategy method is validated experimentally using a seven-level regenerative CHB drive with only small L filters.

In Chapter 4, the relation between the DC-link capacitance and the instantaneous power flow is researched in detail for the regenerative CHB drives. Then a novel voltage ripple controller is proposed to reduce the dc-link capacitance in the three-phase AFE based regenerative CHB drive without adding extra measurements. A high-performance adaptive filter is proposed to accurately detect the dc-bus voltage ripple amplitude and phase angle, which are later employed to determine the reference current of the AFE. Moreover, the potential instability issue is pointed out and discussed. The proposed voltage ripple controller can avoid unstable operation points, which is ignored by the existing control strategies. The effectiveness of the proposed controller is validated on a regenerative seven-level CHB drive to reduce the dc-link capacitance and dc-link voltage ripple.

In Chapter 5, to achieve a faster dynamic response and the multi-objective performance during the control of CHB drives, a novel high-performance predictive control with long prediction horizons is proposed to improve the control performance of the CHB multilevel inverters. First of all, the conventional cost function based FCS-MPC for the seven-level CHB drive is illustrated. Then the formulation of the proposed high-performance FCS-MPC is explained in detail and analyzed to reduce the real-time computation burden. Experimental results obtained from a prototype are represented to confirm the effectiveness and feasibility of the proposed FCS-MPC formulation. The proposed FCS-MPC controller in Chapter 5 for the CHB drives is targeting at improving the system dynamic performance and the multi-objective performance. However, in some applications, reliability is the main objective for the controller, especially when operating with extremely high power applications. This leads to the reliability research of chapter 6 when the faults are detected in the CHB drives.

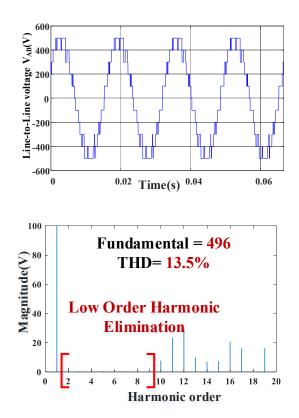

When a fault is detected in the regenerative CHB drive system, the reliability and faulttolerant ability are considered as the main issues. To improve the drive system reliability in high power applications, Chapter 6 proposed a non-symmetrical SHE formulation to extend the output voltage range with a good harmonic profile under post-fault conditions. The conventional faulttolerant method fundamental frequency phase-shifted compensation method (FPSC) is extended with the third-order harmonic injection technique to improve the output voltage range. The mathematical formulation of the proposed FPSC non-symmetrical SHE method under different fault situations is introduced and analyzed in detail. The effectiveness of the proposed method is validated through experiments based on a seven-level CHB drive under fault situations.

Different modulation schemes such as SPWM, MPC and SHE are adopted at the motor side in this thesis to satisfy different industrial requirements. For extremely high power MV CHB drives, it is preferrable to operate at a low switching frequency where SHE is a better solution compared with SPWM and MPC. When high dynamic performance is desired, the MPC is a better solution at a higher switching frequency. It is noted that, in a real MV CHB drive product, different modulation schemes can be adopted for different application purposes. In Chapter 7, the contents of the thesis are summarized and the conclusions that have been reached as a result of the work are presented. The main contributions of the thesis are illustrated. The chapter also concludes by suggesting potential future research that can be done based on the thesis work.

### Chapter 2

# Introduction to Regenerative CHB Motor Drives

#### 2.1. Introduction

The general structure block diagram of the conventional CHB MV drive is shown in Fig. 2.1. It is comprised of a phase-shifting transformer and a number of H-bridge power cells. The output of the H-bridge power cells is series-connected (cascaded) together on the motor side to achieve the full medium voltage range with low harmonic distortion. The output voltage step for each power cell is relatively small and a phase-shifted pulse width modulation (PSPWM) switching pattern is used, so output harmonics and torque pulsations at the motor are minimal, even at lower speeds. This technology allows standard motors to be used for new applications without the requirement for output filtering. The number of the cascaded power cells is mainly

determined by the desired output voltage, harmonic content, and cost. In commercial CHB drive products [10], the number of power cells ranges from 9 cells at 2.3 kV to 24 cells at 11 kV up to 11 MW.

An isolated DC supply is required to feed each H-bridge cell. As it is shown in Fig. 2.1 (b), the most prevalent CHB topology in the drive industry is based on the three-phase diodes-frontend (DFE) H bridge power cell. The isolated DC supplies are obtained through a phase-shifting transformer and three-phase diode rectifiers. The phase-shifting transformer can produce a three-phase set of stepping-down secondary voltages shifted by a certain angle with respect to the primary voltage. The three-phase diode-rectifiers are fed by secondary windings with phase angle shifted. The angles of the phase-shifting transformer help to eliminate low order harmonics on the primary currents. In the case of CHB MV drives, the phase-shifting transformer is feeding 6-pulse diode rectifiers in each cell. Typically, the secondary winding groups are designed to be shifted from each other by (60°/m), where m is the number of cells in each phase. With a high number of secondaries (typically higher than 9), no additional passive filter or active filter is needed to satisfy the IEEE std 519-2014 harmonic standard.

Due to the DFE, the most prevalent CHB medium voltage drive illustrated in Fig 2. 1 can only operate in two quadrant modes. This limits the industrial application of the conventional CHB drives where the ability of handling regeneration is desired, such as downhill belt conveyors and high power shovel applications. The power generated by the load may exceed several megawatts and thus must be delivered to the electrical unity. Therefore, the next generation of medium voltage CHB drives is preferred to be equipped with the regeneration ability to meet the diverse requirements from the industrial markets.

Regeneration capability in conventional CHB drives can be achieved by replacing the diode-ridge front end (DFE) with either a single-phase or three-phase active front end (AFE) rectifier at the input of each power cell of the CHB drives. An AFE rectifier allows a bidirectional power flow between load and source. The drive system can transmit the energy of the motor back to the three-phase power source. Different topologies for the regenerative CHB drives are proposed in the existing literature.

As is shown in Fig. 2.2, a regenerative power cell for CHB drives is proposed in [16]. In this structure, instead of a three-phase DFE in Fig. 2.1 (b), a single H-bridge rectifier is adopted in the AFE. The single-phase transformers, instead of three-phase transformers, are utilized for the isolation.

Fig. 2. 2 Single-phase H-bridge AFE Regenerative Power Cell

As is shown in Fig. 2. 2, any amount of the regenerative power  $p_0$  that comes from the load motor has to be delivered by the single-phase AFEs immediately. If not, the reversal of regenerative power flow will accumulate at the DC-link and consequently raise the DC link voltage above the system safety range, which is very dangerous for the drive system. Therefore, a DC-link voltage controller is required to be designed for the AFEs to stabilize the DC-bus voltage and avoid overvoltage damage during regeneration. The main objective of the DC-link voltage controller is to control the DC-link voltage within the system safety range by delivering the "suitable" amount of power to the grid.

The block diagram of the control system for the single-phase AFE is shown in Fig. 2.3, where  $V_{dc}$  is the dc voltage measurement and Vs is the grid voltage. PI-1 is adopted to control the dc capacitor voltage by setting a "suitable" current reference to be injected to the grid. PI-2 is employed to track the reference current generated by the PI-1 through modulation waveform. The modulator generates the gating signals for the AFE based on the modulation waveform. The control strategy of the PWM single-phase rectifier is well known and is explained with more details in [16].

Fig. 2. 3 Control Scheme of Full bridge AFE [16]

Beyond the full-bridge AFE topology, in [17] and [18], the single-phase half-bridge PWM rectifiers shown in Fig. 2. 4 are utilized as the front end of cascaded H-bridge modules. Only two power semiconductors are needed in each of the rectifiers. The single-phase transformers are utilized for isolation. An extra dc offset compensation control loop is required to tackle the voltage imbalance issue between the capacitors  $C_1$  and  $C_2$ .

Fig. 2. 4 Half-bridge AFE Regenerative Power Cell

However, the CHB inverters comprised of single-phase front-end power cells are vulnerable to grid disturbance [19], which increases the concerns related to harmonic pollution [20]. On the other hand, CHB drives with a three-phase PWM rectifier front end had gained a lot of attention from the manufacturers.

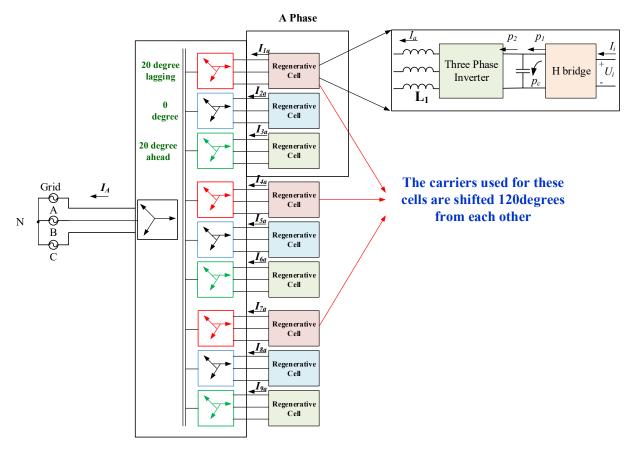

In [21]-[23], the three-phase two-level PWM rectifiers are utilized as the front end of cascaded H-bridge modules shown in Fig. 2. 5. During the motoring operation, the IGBTs are kept off-state to avoid switching loss. The IGBT anti-diodes work as the three-phase rectifiers to

provide the isolated DC supplies for the power cells, which is equivalent to the conventional DFE CHB drives. Meanwhile, during the regeneration mode, the AFEs start to operate to deliver the energy from the motor side to the grid. The bidirectional power flow between the motor and the grid is achieved with the minimum changed to the conventional CHB drives, which is a big advantage to manufacturers.

Fig. 2. 5 Three-phase AFE Regenerative Power Cell

As mentioned, a DC-link voltage controller is required to be designed for the AFEs to stabilize the DC-bus voltage and avoid overvoltage damage during regeneration. It is shown in Fig. 2.6, the DC voltage controller is implemented with the help of the dq rotating frame, where the measured grid voltage and current are denoted as  $V_{sx}$  and  $I_{sec\_rx}$ , where x=(a, b, c). The voltage controller is adopted to control the dc capacitor voltage by injecting a suitable amount of  $I_d^*$ . The current controller does nothing more than tracking the reference current by generating the modulation waveform. The reference currents are represented in dq axis as  $I_d^*$  and  $I_q^*$ . The reference current in q axis  $I_q^*$  is set to zero to avoid reactive power injection. The sinusoidal pulse width modulation (SPWM) modulation is adopted to generate the IGBTs gating of the AFEs. The dc-link voltage is controlled both in regeneration mode, which allows a bidirectional power flow between load and source.

Fig. 2. 6 Three-phase AFE Control Scheme

The main focus of the research for this thesis has been focused on the three-phase AFE based regenerative CHB drives shown in Fig. 2. 7. This is because this power cell configuration can provide four-quadrant operation with minimal changes to the conventional DFE CHB drives with the same transformer structure. Meanwhile, the IGBT anti-diodes work as the three-phase rectifiers to provide the isolated DC supplies for the power cells during motoring. With the phase-shifting transformer, the merits of the conventional DFE CHB drives are kept in the regenerative drives, which is desirable from the engineering perspective [24].

Fig. 2. 7 Three-phase AFE Regenerative Power Cell

# 2.2. Grid-Tied Filter Design Challenges

Although the regeneration capability can be achieved by the three-phase AFE regenerative CHB drives. However, in regeneration mode, AFE introduces the switching harmonics that may not be canceled by the phase-shifting transformer. The resulting harmonics may deteriorate the grid current quality to the extent that violates the IEEE 519-2014 harmonic standard [25]. Therefore, a filter bank is required between the AFE and the grid, to attenuate current harmonics [26], which is shown in Fig. 2.8. Reducing the required filter bank is the crucial point to the CHB drive system cost, volume, and thermal dissipation. However, it has been observed that there is very little information available describing the design of a filter bank for the regenerative CHB drives.

Fig. 2. 8 Filters for the Three-phase AFE

### 2.2.1. Optimal LCL Filter Design Challenge for CHB AFEs

An L filter is simple, but it is relatively bulky to achieve a good filtering performance. The alternative solution is the LCL filter [26], which achieves a good filtering performance with a smaller size due to its third-order transfer function. LCL filter suffers from resonance problem and active or passive damping methods should be adopted to stabilize the resonance area of the

LCL filter. In practice, as is shown in Fig. 2. 9, the damping resistor in series with a filter capacitor has been widely adopted to suppress the resonance since the power loss in the damping resistor is low [27]. There are other high order filters such as LTCL and LLCL filter [28][29]. The higher-order filters usually possessed a relatively better frequency attenuation performance, which is suitable for the power inverters. However, it involved more passive components that increase the cost and complexity of the system. Thus, in general, the LCL filter is the most adopted solution since it provides the best trade-offs between the different features.

Fig. 2. 9 LCL Filter with Passive Damping Resistor for AFE

In terms of designing the passive damping LCL filters, there are several criteria and design methods discussed in the previous literature. The majority of these proposed methods [26]-[30] are based on the harmonic current amplitude and resonance frequency. It can be summarized as the following steps [26] [30]:

- Select the converter side inductance L<sub>1</sub> based on the desired maximum current ripple in the inductor.

- 2. Select the filter capacitance  $C_f$  to be no more than 5 % of the base capacitance.

- Select grid side inductance L<sub>2</sub> based on harmonic current suppression at the switching frequency.

- 4. Select passive damping resistor R<sub>f</sub> based on the resonance frequency.

These LCL filter designing procedures are easy to follow. It is worth mentioning that following these design procedures only based on maximum current ripple suppression may result in a "bad" solution that doesn't necessarily meet the system requirements in different applications. First of all, the designed LCL filter is not necessarily satisfy the IEEE std 512-2014 standard since only the current ripple magnitude is considered in the designing process. Moreover, this design process doesn't take the DC-link voltage capability and power ability limitation [31] into consideration. It may sometimes lead to excess inductance which requires a higher DC-link voltage to deliver the full power. This point has to be taken into consideration since the DC-link voltage is limited by the IGBT rating. Another critical point is that the calculated LCL filter through these procedures is not optimized since minimizes the total inductance and the total capacitance is the ultimate goal.

The LCL filter design procedures applied to the regenerative CHB drives are seldom mentioned. The existing LCL design and optimization methods can be applied to a voltage source inverter. But they cannot be directly applied to the regenerative CHB drives LCL filter design due to the following reasons:

To assure the Point of Common Coupling (PCC), the point the power converter connects to the grid, satisfies the grid harmonic requirement of IEEE STD 519 2014. It is required to obtain the current harmonic content at the PCC point (the primary side of the phase-shifting transformer). The existing LCL filter design methods only consider the current profile at the transformer secondary. The phaseshifting transformer for a seven-level CHB inverter can eliminate the low order harmonics under 17th order harmonics [1]. Moreover, the leakage inductance of the transformer can be considered as an extra filtering inductor;

- With the phase-shifting transformer, as is shown in Fig. 2. 1, the equivalent grid inductance L<sub>leak</sub> exists between the ideal power grid and the inverter which cannot be neglected. This inductance can deteriorate the harmonic performance, PLL performance, or even the system stability [32].

- 3. The DC-link voltage capability and power ability should be taken into consideration [31] to assure that the maximum power can be delivered to the grid with the determined DC voltage.

All in all, to design an optimal LCL filter for a given regenerative CHB inverter, beyond the harmonic performance and filter size, it is necessary to take system performance (such as grid impedance, PLL performance, controller saturation) into consideration due to the existence of the transformer. To consider all these factors while minimizing the LCL filter, a new LCL filter design framework is required to be investigated.

### 2.2.2. Optimal Filter Design Challenge for CHB AFEs

Increasing the switching frequency can effectively reduce the output current ripple and, thus decrease the filter bank size. However, in high-power applications, a high switching frequency increases the switching loss of the power switches, which leads to low efficiency and the increased heat sink size. Switching frequencies higher than 1 kHz is not desirable in highpower applications [33]. Therefore, designing and optimizing the filter bank for the CHB regenerative drive operating at a low switching frequency is a challenge.

Second, an extensive amount of literature is available describing filter design for the gridtied AFE rectifier to satisfy the grid harmonic standard [26],[34]-[36]. Generally speaking, a high order filter is better since it can achieve a better filtering performance with a smaller size such as LCL [26] [34] and LTCL filters [35]. A high-order filter is often adopted to interconnect to the utility grid to suppress the harmonic currents. However, the inherent resonance of the high order filter may trigger the potential instability problem of the system [36]. Moreover, considering the number of power cells in a CHB drive, a large number of passive components increase the overall cost and size of the drive system. Although, with a good filtering performance, these high-order filters are not desirable for the regenerative CHB drives.

All in all, there is a demand for the new filtering strategy for the regenerative CHB drives that tackle the previous challenges. It should allow the system to operate at a low switching frequency with a good grid current quality satisfying the IEEE std 519-2014. More important is that the number and the size of the passive filter components are required to be reduced at the same time.

Researchers have attempted to eliminate the PWM sideband harmonic using the active filtering strategies for parallel-interleaved rectifier/inverters [37]-[39]. With *n* identical parallel AFEs, where *n* is the cell number per phase, switching current harmonics can be effectively attenuated when carriers are evenly phase-shifted  $360^{0}/n$  [40]. Carrier interleaving is an effective strategy to improve the input waveform quality of the parallel-connected converters [41]. [41] minimizes the grid current distortion in interleaved grid-connected converters with unequal

terminal voltages. An enhanced carrier interleaved strategy is proposed in [42] to improve both the current THD and line-to-line voltage quality. [43] [44] propose to optimize the harmonic profile by real-time calculating the phase-shifting carrier angles.

It is important to recognize that, in parallel rectifiers, carrier sideband harmonic cancellation is done with the inverters supplied from the equal transformer secondary terminal voltages. But the phase-shifting transformers in the regenerative CHB drive can affect the phase of current sideband harmonics in an unfavorable manner. Although intensive work has been done on the carrier shifting strategies, not enough work has been done on carrier shifting PWM methods with filter reduction for regenerative CHB drives in the existing literature.

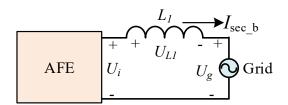

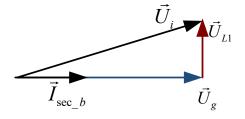

# 2.3. DC-Link Capacitor Size Reduction Challenge

As is shown in Fig. 2. 8, during regeneration, the reversal of regenerative power flow  $p_0$  from the load motor has to be delivered by the three-phase AFEs to the grid immediately. Otherwise, this reversal energy can accumulate at the DC-bus and consequently raise the DC link voltage above the system safety range, which is very dangerous for the drive system. Therefore, a DC-link voltage controller is required to be designed for the AFEs to stabilize the DC-bus voltage and avoid overvoltage damage during regeneration. The main objective of the DC-link voltage controller is to control the DC-link voltage within the system safety range by delivering the "suitable" amount of power to the grid.

With the conventional DC-Link voltage controller [45], only a constant power is delivered by the three-phase AFE. The instantaneous power in each power cell between the three-phase AFE and the single-phase H-bridge is not balanced. This unbalanced power ripple has to be absorbed by designing a large DC-link electrolytic capacitor to maintain a stable dc voltage, which increases the system's volume and cost [46]. Moreover, the pulsating power ripple flowing through the DC-link electrolytic capacitors raises the DC-link voltage fluctuation with twice the output frequency. The temperature rise caused by voltage ripple accelerates the evaporation of the electrolyte, thus reducing the capacitor's life expectancy and the system reliability as well [47],[48].

To reduce the size of the DC-link electrolytic capacitor and to suppress DC-link voltage fluctuation, it is desirable to deliver both the average power and pulsating ripple power through the three-phase AFE in each power cell [46]. In this way, the ripple power is prevented from flowing across the DC-link capacitors, which reduces the required dc-link capacitance to maintains a stable dc voltage. Beyond that, it is worth mentioning that the pulsating ripple power from all the secondary power cells cancels out with each other at the primary side of the transformer in the regenerative CHB [49]. This superb merit allows for injecting the pulsating ripple power to reduce the capacitance in each power cell without deteriorating the grid harmonic profile at the transformer primary side.

Although different control algorithms have been proposed to reduce the dc-link capacitance of regenerative CHB drives, however, the theory beneath these control algorithms is identical: deliver the instantaneous ripple power through the three-phase AFE instead of flowing across the dc capacitors. The control procedure involves the following two stages:

The reference input current waveforms of the three-phase AFE is determined based on the instantaneous power [46][49][50][51] or DC-link voltage [52] assuring that the instantaneous power is provided by the AFE instead of the dc-link capacitors; 2. The current controller tracks the determined reference current to suppress the DC-link voltage ripple. It is noted that the reference current may contain different frequency components such as  $\omega_g$ ,  $2\omega_m - \omega_g$  and  $2\omega_m + \omega_g$  [49], where  $\omega_m$  is the H-bridge output frequency and  $\omega_g$  is the grid frequency.

[46][51] propose to direct inject the instantaneous power of the H-bridge into the *d*-axis of the current controller ( $I_d$ ) of the three-phase AFE. But the capacitance reduction is not as good as expected since the proportional-integral (PI) based current controller can not track fast enough the generated reference [46]. [51] improves the performance by adopting the high-performance model predictive current controller. The dc-link voltage ripple is reduced significantly. [49] propose to open-loop inject the instantaneous power using a proportional (P) based current controller. However, in these controllers, it is assumed that the motor side instantaneous power is known. The current and power angle of the motor is required to be measured to determine the reference currents. But these measurements are rarely available in a typical induction motor control system such as V/F control.

Recently, to avoid adding extra sensors while reducing the DC-link capacitance, [52] proposed to determine the reference current for the three-phase AFE based on the DC-link voltage measurement directly. This concept is developed from [53], where one more control loop is established for the voltage ripple. However, a resonant controller with a lead-compensated phase is required to be tuned to gain enough stability margin [52]. This is not an easy task due to the load frequency variation.

Design a high-performance current tracking controller is an important stage for capacitor reduction. The high-performance current controllers have been extensively researched, which is not consider as the main challenge so far. A multitude of solutions have been developed includes: hysteresis control [54][55], dead-beat control [56], model predictive control [57], resonant control [58], multiple rotating frames control [59]. These control algorithms can be directly implemented to improve current tracking performance.

To shrink the DC-link capacitance, determining the reference currents for the three-phase AFE directly based on the DC-link voltage ripple is a promising solution when the instantaneous power at the motor side is not measured [52]. A voltage ripple controller can be designed to deliver the instantaneous ripple power through the AFE. However, this voltage ripple controller should be carefully designed since it may impact system stability. This potential instability issue hasn't been given enough attention. Two main challenges of implementing the voltage ripple controller to reduce the DC-link capacitance are:

- 1. The DC-link voltage ripple frequency varies with the motor speed, which makes it difficult to real-time detect the voltage ripple amplitude and phase angle with accuracy. But these parameters are critical for the three-phase AFE to deliver "suitable" instantaneous ripple power.

- 2. A more critical issue is the fact that the voltage ripple control system may lose stability in some operation range when excess pulsating power ripple is injected by the AFE.

To tackle the ahead mentioned problems, a novel voltage ripple controller to reduce the dclink capacitance in the regenerative CHB drive is developed which is explained in Chapter 4 in detail.

# 2.4. High-Performance Controllers for CHB drives

Besides the filter and capacitor design challenges for the grid-side AFEs in the regenerative CHB drives, there are other challenges for the motor-side cascaded H bridge multilevel inverters in terms of high-performance control. The commercial multilevel inverters are available for decades, however, there is still undergoing research mainly on the new control strategies and modulation techniques to improve the performance [60]-[62] and to achieve multi-objective such as suppressing common-mode voltage (CMV) [63], increasing fault-tolerant ability [64], and balancing floating capacitors [65].

To achieve a faster dynamic response and multi-objective performance during the control of power converters, the finite control set model predictive control (FCS-MPC) method has been considered one of the most promising alternatives in recent years [65]. FCS-MPC predicts the future behavior of the power converter based on the "transient" mathematic model. The switching states of the power converters are determined through a cost function, which represents the system performance. FCS-MPC actually searches the best switching state with minimal cost function among all the available switching states at each sampling step. Compared with classical linear control strategies and modulation techniques based on the average small-signal model and rotating frame [66][67], FCS-MPC combines the current control and modulation into a single computational problem, providing a powerful alternative to conventional proportional-integral (PI) and proportional-integral-resonant (PIR) controllers with a very fast dynamic response.

The implementation challenge in multilevel inverters has motivated the researchers to study different fast computationally efficient MPC formulations. Several model predictive control schemes are proposed to reduce the computational load by only estimating a reduced subset of redundant switching states or a subset of redundant voltage vectors. In [68][69], Petri nets are introduced to accomplish both current tracking and voltage balancing objectives by estimating only a subset of the switching combinations. However, it requires to calculate the best output voltage level for current regulation in the design process. Instead of estimating the subset of the switching states, [70] proposed to estimate the output voltage vectors to reduce the calculation load. Furthermore, [71] proposed to use the non-redundant voltage vectors instead of all the voltage vectors to shrink the candidate pool of the MPC formulation. For example, a seven-level CHB inverter, all the available switching combinations reach 49 (around 0.26 million). And the available voltage vectors reach 73 (343), 127 of which are non-redundant voltage vectors [71]. With the increase of the output voltage levels, searching for the optimal output voltage vector still remains an issue. To tackle this issue, recently, an online sphere decoding algorithm (SDA) is discussed to speed up the process of searching the optimal output voltage vector [72][73]. The MPC problem is reformulated as an integer least-square optimization problem and then solve by SDA, which is more efficient than exhaustive enumeration methods. But this algorithm requires significant storage of the processor [74]. Beyond that, [75] proposed to replace the optimization problem by solving Diophantine equations over a large set of output voltage vectors. However, this method hasn't been extended into long horizon prediction MPC situations. In the existing MPC formulations, a considerable real-time computation burden is required and the determination of the weighting factors may affect the MPC performance.

It has been recently shown that power converters with long prediction horizon MPC can improve the system steady-state performance, by either reducing the switching frequency or the total harmonic distortion of output currents when compared to the basic single-step MPCs [76]. However, using long prediction horizons FCS-MPCs in multilevel inverters increases the computation burden for the already exhausted processors. Only limited literature and reference are available on long-horizon prediction FCS-MPC on multilevel inverters due to its huge computation burden. One existing long horizon prediction method is named simplified model predictive direct current control (MPDCC) [77]-[80]. The switch positions are frozen and switching is not allowed when the output currents are within the designed bounds. The number of switching sequences to be evaluated is greatly reduced as a result [79]. Another known long prediction horizon length FCS-MPC adopts enhanced SDA for accelerating the voltage vector optimization process [72]-[74]. The existing algorithm has been demonstrated on a three-level NPC inverter.

Besides the feature of high dynamic performance, FCS-MPC can also achieve multiobjective capability. Especially in the medium-voltage drive application, a large common-mode voltage (CMV) can result in large leakage currents which may cause electromagnetic interference (EMI) problems and bearing failure [63]. In recent years, MPC-based CMV reduction strategies have been studied in different multilevel topologies. In [81][82], a separate cost function is added and designed to suppress CMV. The theory has been tested on a dSPACE based on a matrix converter. The execution time under this case is 80 µs for single-step FCS-MPC. At the same time, to reduce the complexity while reducing the CMV, [63] and [83] proposed to select only part of the adjacent voltage vectors and zero vectors during the MPC optimization. But this means an extra estimation process is still required for the adjacent voltage vectors, which will hinder the application of this method when the inverter output voltage levels increase. To obtain multi-objective with the long prediction horizon length MPC, a modified long prediction horizon SDA-MPC formulation is explored with reduced CMV in [84]. The experimental validation of the proposed method has been implemented on a dSPACE system. By adopting the SDA optimization in the MPC formulation [84], the execution time of a five-level CHB inverter is 92.2  $\mu$ s when the prediction length to be 3. In [85], the SDA-MPC formulation is implemented on a three-level converter with dSPACE system, the minimum sampling interval was set to 125  $\mu$ s in order to real-time find the optimal voltage vector solution when the prediction time step is 4. However, it has to be mentioned that an extra weighting factor is required in the modified SDA optimization process. The chosen of the weight factor for the cost function directly affects the system's stability and performance. A large number of simulations or experiments are required to be done to design the suitable weight factors in order to achieve expected objectives [84][86].

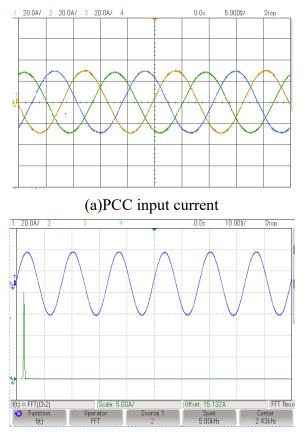

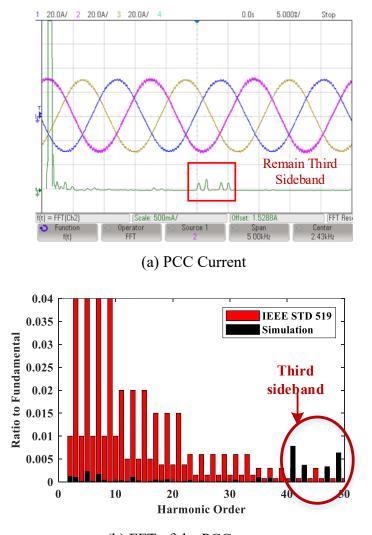

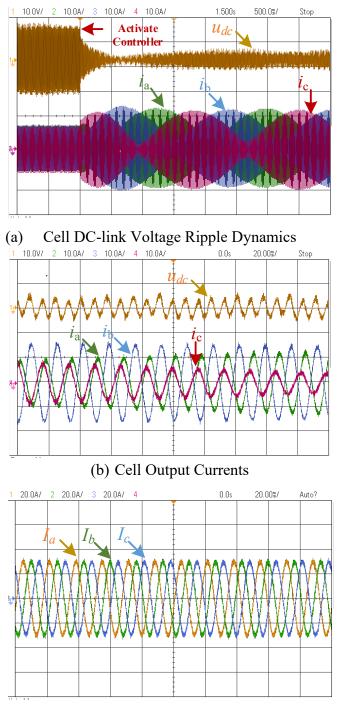

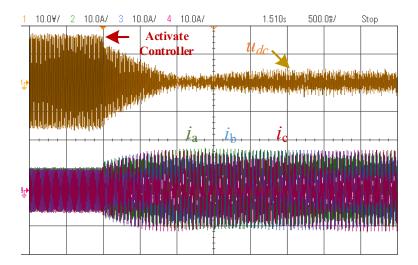

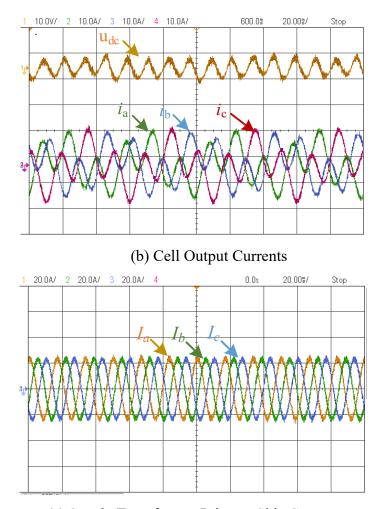

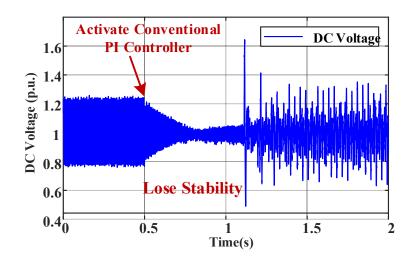

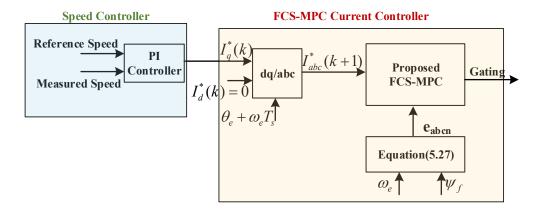

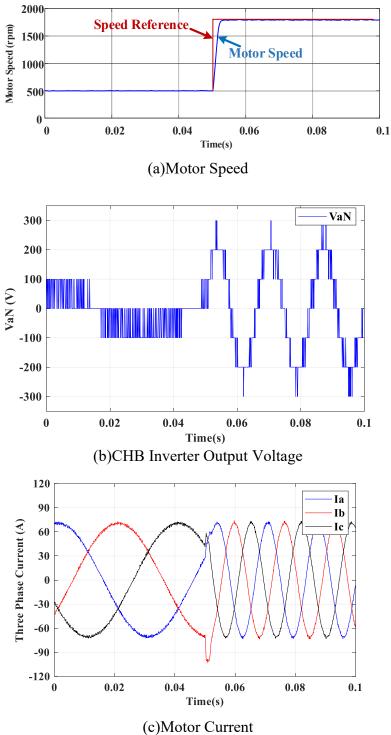

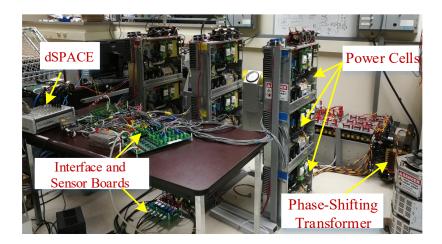

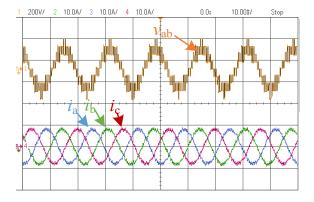

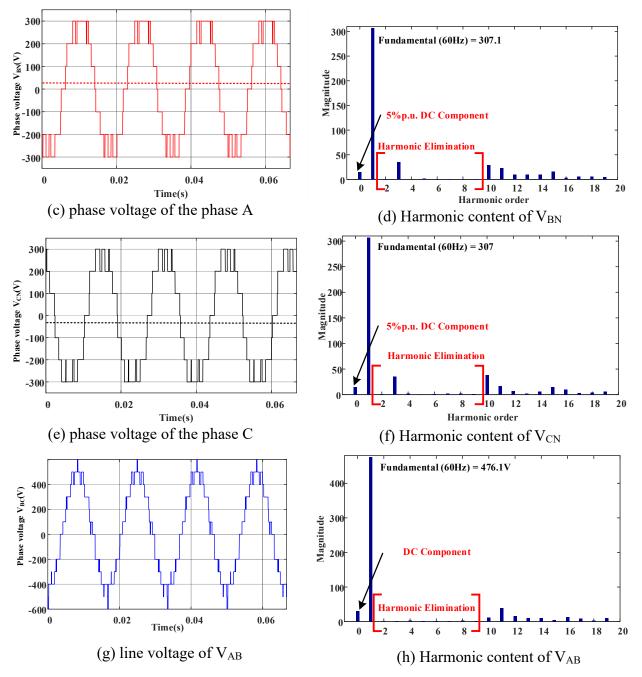

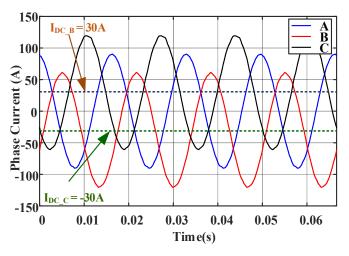

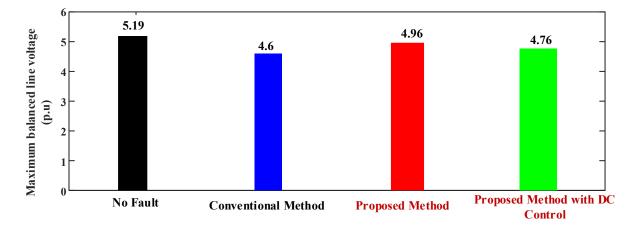

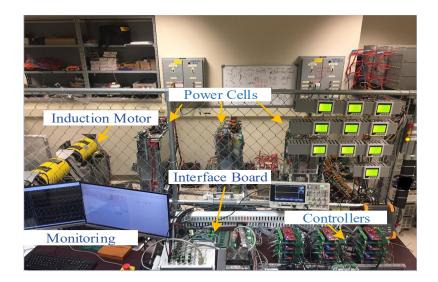

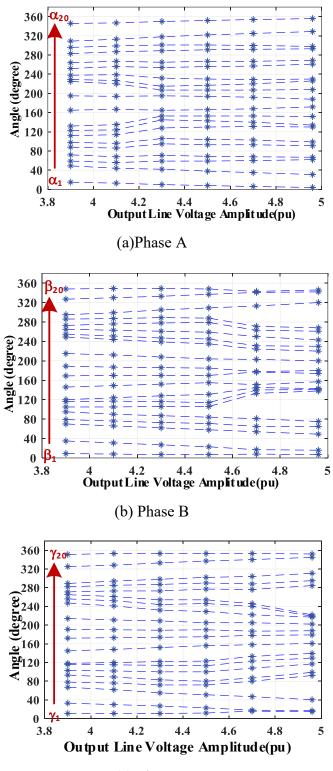

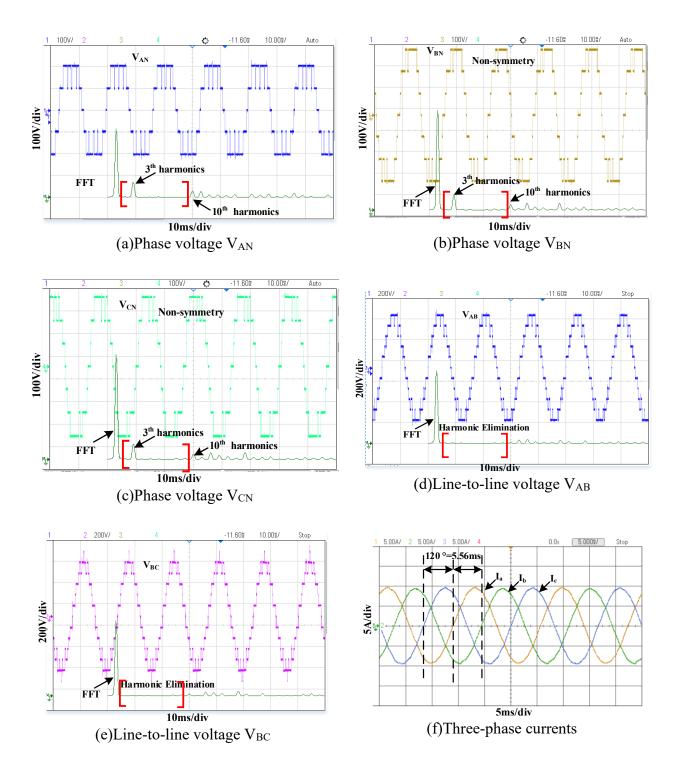

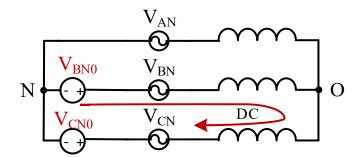

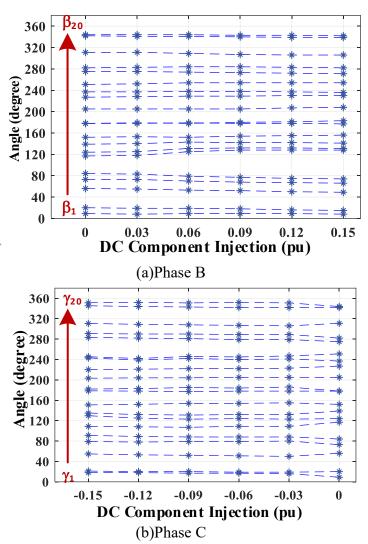

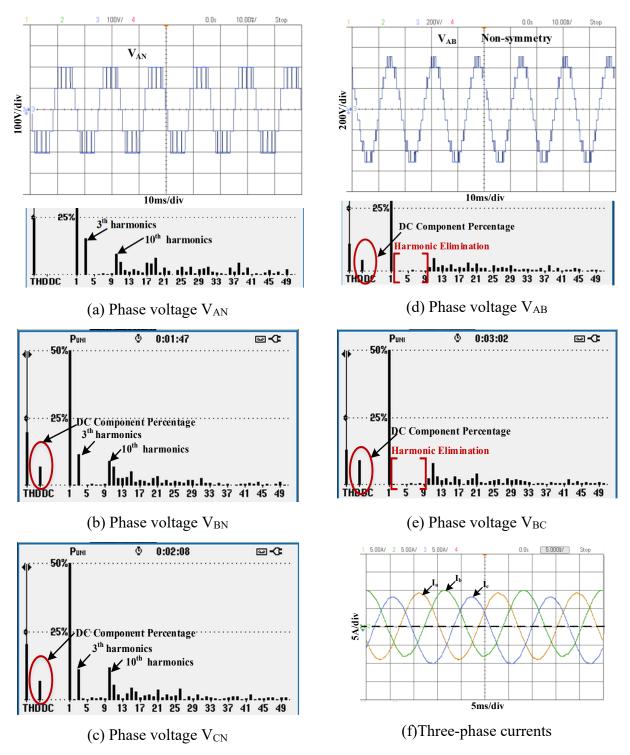

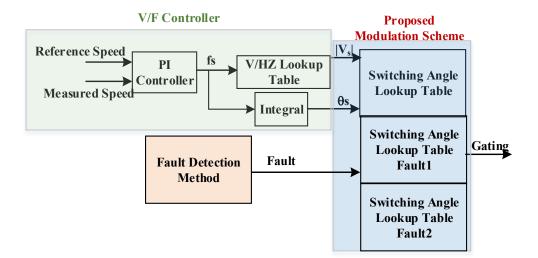

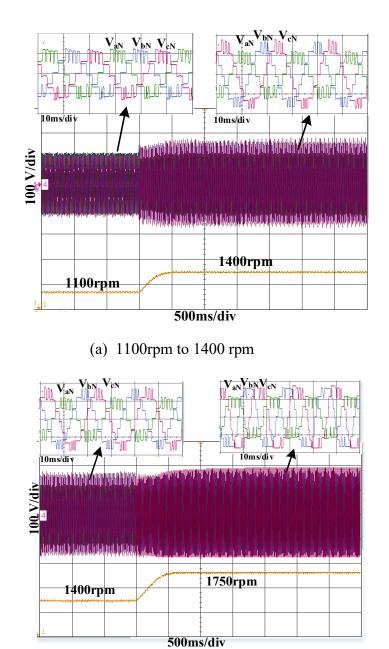

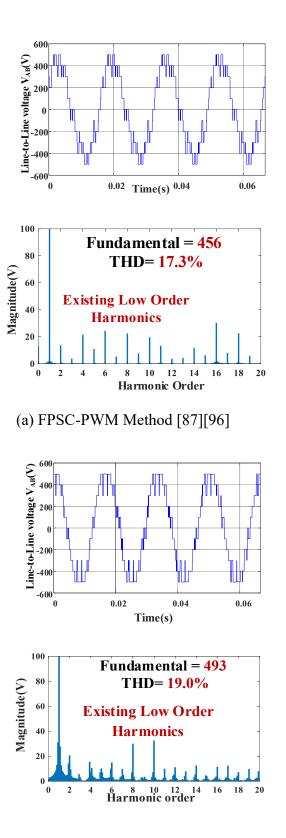

A CHB drive is composed of a number of modular H-bridge power cells and isolated DC voltage sources. The H-bridge cells are cascaded on the load side to achieve medium-voltage with low harmonic distortion. Due to its structure, the CHB inverter is known to have a huge number of switching combinations and voltage vectors. For a 2C+1 level CHB inverter, the number of non-redundancy voltage vectors will boost up to  $12C^2+6C+1$  [71], which poses a challenge for implementing the online FCS-MPC algorithm at a high performance!