Algorithms for Embedded Memory Binding in FPGAs

### ALGORITHMS FOR EMBEDDED MEMORY BINDING IN FPGAS

#### BY

#### KAVEH GHORBANI ELIZEH, B.Sc.

#### A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

AND THE SCHOOL OF GRADUATE STUDIES

OF MCMASTER UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

© Copyright by Kaveh Ghorbani Elizeh, November 2008 All Rights Reserved Master of Applied Science (2008)

(Electrical & Computer Engineering)

$\label{eq:McMaster University} \mbox{Hamilton, Ontario, Canada}$

TITLE:

Algorithms for Embedded Memory Binding in FPGAs

AUTHOR:

Kaveh Ghorbani Elizeh

B.Sc., (Computer Engineering)

AmirKabir University of Technology, Tehran, Iran

SUPERVISOR:

Dr. Nicola Nicolici

NUMBER OF PAGES:

x, 108

To Zahra,

for her endless passion for life.

## Abstract

Recent advancements in semiconductor fabrication technology have enabled field-programmable gate arrays (FPGAs) with hundreds of embedded memories. Usually, these embedded memories can be configured to work with different widths of address and data buses. In some FPGAs there is also a variety of different types of embedded memories with different capacities and configuration sets. As a consequence, it is becoming cumbersome to bind the data memory of an algorithm to these embedded memories manually. A computer-aided design tool that automates the process of binding embedded memories can save the engineering time for a design, as well as explore different alternatives to bind the data memory with the use of less embedded memories and less amount of peripheral hardware in terms of logic cells of the FPGA.

In this thesis, we first motivate the need for an algorithmic solution to the memory binding problem in FPGAs and explain the design trade-offs. Then we present an exact solution for the problem using a branching method to search the solution space exhaustively. However, due to the large solution space and the plenitude of choices in each step of the algorithm, the runtime of the algorithm is far from being acceptable for realistic problems. To manage the runtime, we have developed a fast heuristic approach. Our experimental results show that the heuristic method can achieve a suboptimal solution, which for small problem instances is shown to be close to the optimal in acceptable runtime. Moreover, when compared to manual solutions, besides substantially improving the implementation time, the heuristic can often enable a more efficient usage of the FPGA logic resources and embedded memories.

## Acknowledgements

I would like to thank all the people who helped me while I was working on this research. First, I give a sincere gratitude to my supervisor, Dr. Nicola Nicolici, for all the effort, energy, and patience he put in this research. He taught me many things much more important than research, and it was a pleasure for me to work under his supervision for the past two years.

I also wish to thank my colleagues in Computer-Aided Design and Test Research Group, Adam Kinsman, Henry Ko, Ehab Anis, Jason Thong, Mark Jobes, Rumi Sahi, and Zahra Lak, who always assisted me during the coarse of my study.

My love and appreciation goes to my parents, Behrouz and Fattaneh, who where always beside me and led me to find the true values in life. My sisters Shaghayegh and Sara were always a great source of energy for me, and I am really thankful to them for my success.

I want to acknowledge all my Iranian friends in Hamilton who always cheered me up and spent time with me to ease my life in Canada. Without their help it was impossible to finish this work. Also, I am deeply indebt to Dr. Mehdi Sedighi, the source of my knowledge and passion for digital electronics.

Above all, I am thankful to God, who gave me the strength and the chance to do this work, and for placing these wonderful people in my life.

## Contents

| A            | Abstract |                   |                                             |    |

|--------------|----------|-------------------|---------------------------------------------|----|

| $\mathbf{A}$ | ckno     | $\mathbf{wledge}$ | ements                                      | v  |

| 1            | Intr     | roducti           | ion                                         | 1  |

|              | 1.1      | Digita            | l circuits                                  | 2  |

|              | 1.2      | Moore             | e's law                                     | 3  |

|              | 1.3      | Imple             | mentation technologies for digital circuits | 6  |

|              |          | 1.3.1             | Off-the-shelf packages                      | 7  |

|              |          | 1.3.2             | Programmable logic designs                  | 8  |

|              |          | 1.3.3             | Standard cell based designs                 | 10 |

|              |          | 1.3.4             | Full-custom designs                         | 12 |

|              | 1.4      | FPGA              | As                                          | 14 |

|              | 1.5      | Thesis            | s organization                              | 18 |

| 2            | Lite     | erature           | e Review                                    | 19 |

|              | 2.1      | Bindir            | ng problem in CAD                           | 20 |

|              |          | 2.1.1             | Binding in architectural synthesis          | 20 |

|              |          | 2.1.2             | Binding in logic synthesis                  | 24 |

|   | 2.2 | Data memory organization                                  | 26  |

|---|-----|-----------------------------------------------------------|-----|

|   | 2.3 | Physical memory binding                                   | 27  |

|   | 2.4 | Motivation for our work                                   | 29  |

|   | 2.5 | Problem formulation                                       | 31  |

| 3 | Alg | orithms for Binding Virtual Memories to Physical Memories | 35  |

|   | 3.1 | Single VM - Single PM Type                                | 38  |

|   |     | 3.1.1 Binding for Leftover Minimization                   | 41  |

|   |     | 3.1.2 Binding for Multiplexer Cost Minimization           | 49  |

|   | 3.2 | Multiple VMs - Single PM Type                             | 53  |

|   | 3.3 | Single VM - Multiple PM Types                             | 55  |

|   | 3.4 | Multiple VMs - Multiple PM Types                          | 61  |

|   | 3.5 | A Heuristic Approach                                      | 65  |

|   |     | 3.5.1 Heuristics for Leftover Reduction                   | 65  |

|   |     | 3.5.2 Heuristics for Multiplexer Cost Reduction           | 70  |

| 4 | Exp | perimental Results                                        | 81  |

|   | 4.1 | Case Study                                                | 82  |

|   | 4.2 | Experimental Results                                      | 91  |

| 5 | Con | nclusion                                                  | 100 |

|   | 5.1 | Future Work                                               | 101 |

## List of Tables

| 1.1  | Comparison of different task-realization approaches          | 13 |

|------|--------------------------------------------------------------|----|

| 1.2  | Memory elements in EP3SL340 FPGA from Stratix III family [1] | 18 |

| 2.1  | Memory elements in EP2S180 FPGA from Stratix II family [1]   | 30 |

| 4.1  | Specifications of Stratix II EP2S60 FPGA [1]                 | 84 |

| 4.2  | Heuristic algorithm and a manual solution comparison         | 90 |

| 4.3  | Virtual memory sets                                          | 91 |

| 4.4  | Configuration sets of the first physical memory type (M8K)   | 92 |

| 4.5  | Configuration sets of the second physical memory type (M512) | 92 |

| 4.6  | Experiments on V1 with 2 configurations for M512             | 93 |

| 4.7  | Experiments on V1 with 5 configurations for M512             | 95 |

| 4.8  | Experiments on V2                                            | 96 |

| 4.9  | Experiments on V3                                            | 97 |

| 4.10 | Experiments on V4                                            | 97 |

| 4.11 | Experiments on V5                                            | 98 |

| 4.12 | Experiments on V6                                            | 98 |

| 4.13 | Experiments on V7                                            | 99 |

# List of Figures

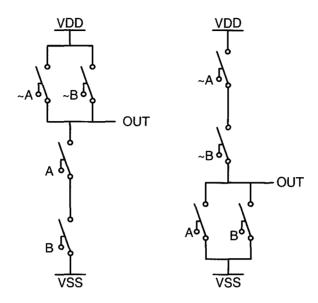

| 1.1  | NAND and NOR gates designed with switches            | 2  |

|------|------------------------------------------------------|----|

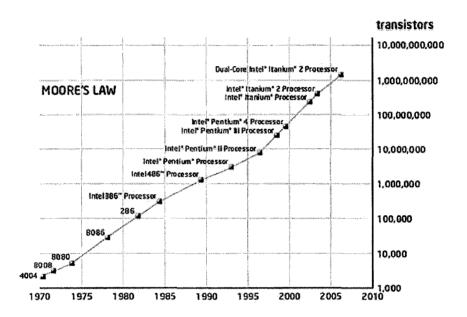

| 1.2  | Moore's law [20]                                     | 4  |

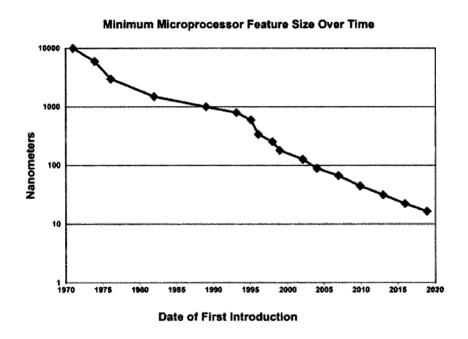

| 1.3  | Moore's law for minimum feature size [16]            | 5  |

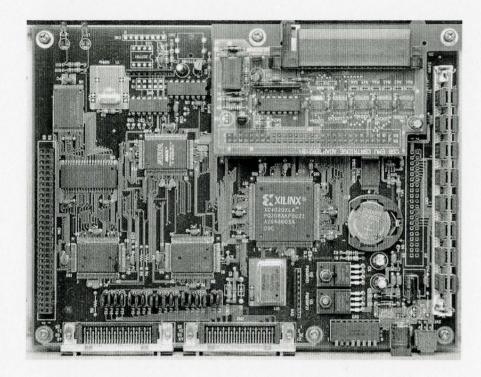

| 1.4  | Discrete logic method[19]                            | 7  |

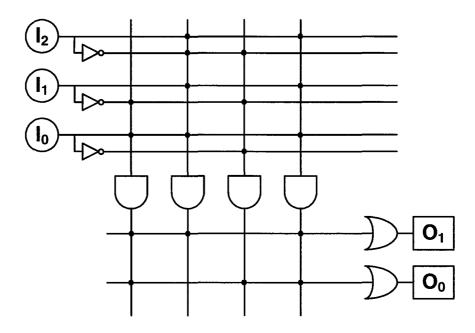

| 1.5  | Programmable logic array                             | 9  |

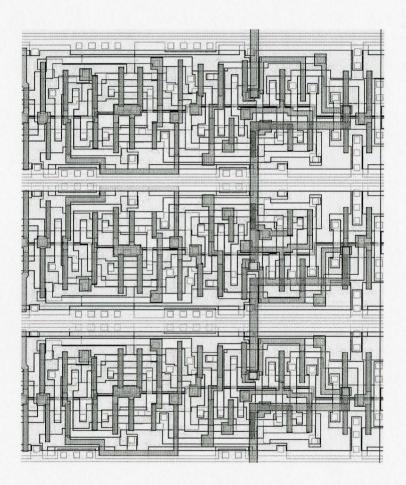

| 1.6  | Connections between three rows of standard cells [2] | 11 |

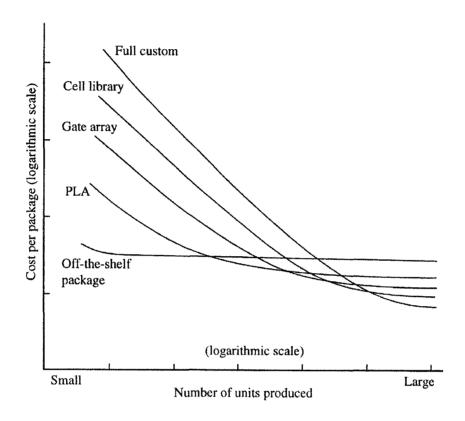

| 1.7  | Package cost vs. product volume [21]                 | 13 |

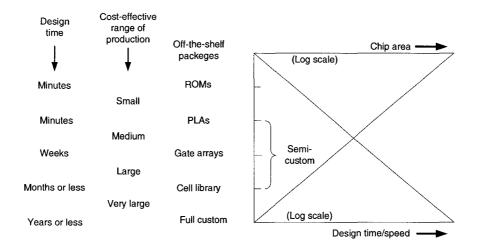

| 1.8  | Chip area vs. design time [21]                       | 14 |

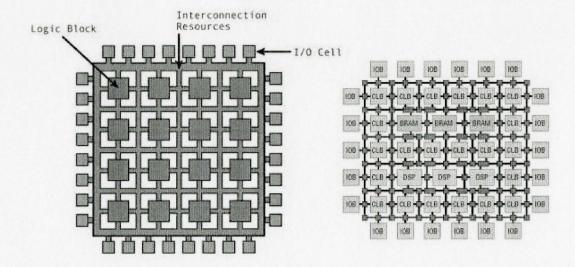

| 1.9  | FPGA structure[5]                                    | 15 |

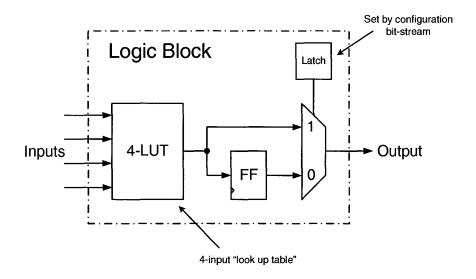

| 1.10 | 4-input logic block                                  | 16 |

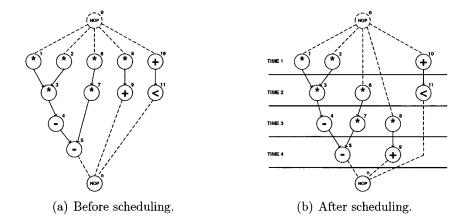

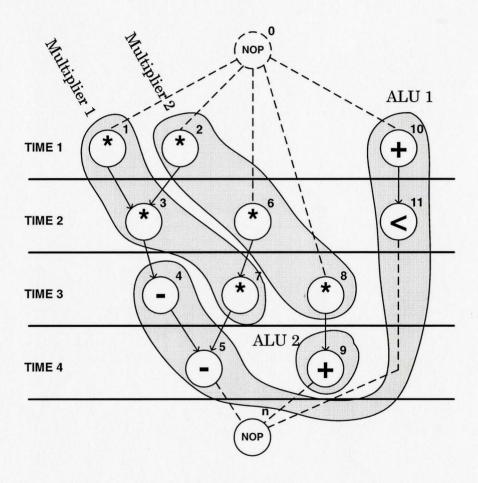

| 2.1  | A sample design before and after scheduling[8]       | 21 |

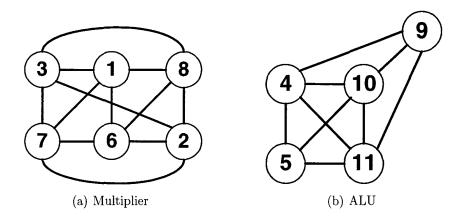

| 2.2  | Compatibility graphs for resource binding[8]         | 22 |

| 2.3  | A sample binding of our example[8]                   | 23 |

| 2.4  | Different binding approaches[8]                      | 24 |

| 2.5  | Memory levels of a sample design[23]                 | 27 |

| 2.6  | Generated peripheral logic in memory mapping         | 33 |

| 2.7  | Vertical and horizontal leftover                     | 34 |

| 3.1  | Elimination of unnecessary multiplexers              | 39 |

| 3.2  | Division of the virtual memory into two parts                           | 40 |

|------|-------------------------------------------------------------------------|----|

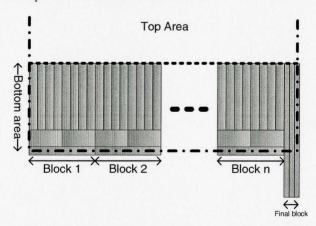

| 3.3  | Decreasing the vertical leftover                                        | 43 |

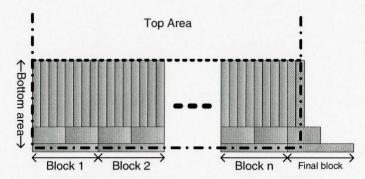

| 3.4  | Blocks of physical memories                                             | 44 |

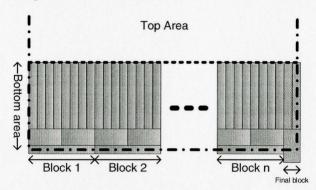

| 3.5  | Different choices for the final block to reduce the overall leftover    | 46 |

| 3.6  | Minimum multiplexer cost binding                                        | 49 |

| 3.7  | A sample combination of different blocks to reduce the multiplexer size | 51 |

| 3.8  | Comparison between two placements                                       | 58 |

| 3.9  | Filling the virtual memories in the first step                          | 67 |

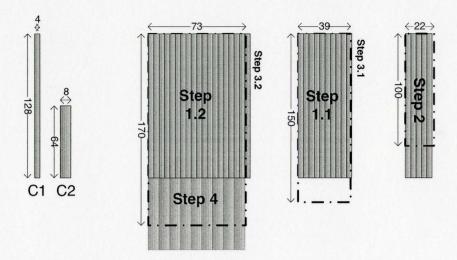

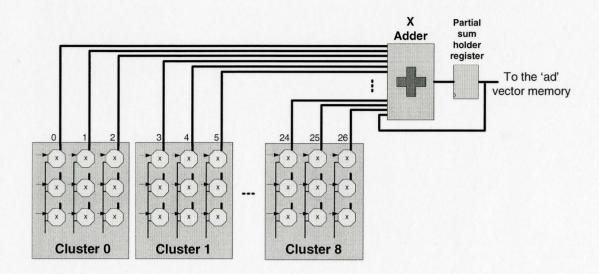

| 3.10 | Steps 1 to 4 of the multiplexer cost heuristic algorithm                | 74 |

| 3.11 | Steps 5 to 8 of the multiplexer cost heuristic algorithm                | 78 |

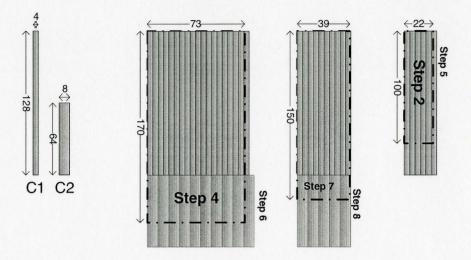

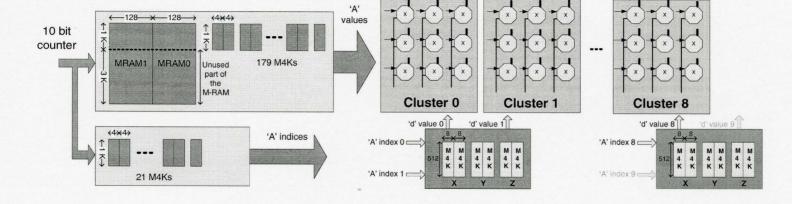

| 4.1  | A cluster of multipliers                                                | 85 |

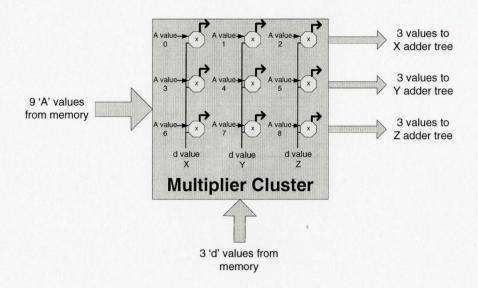

| 4.2  | Connection of the clusters to the X adder                               | 86 |

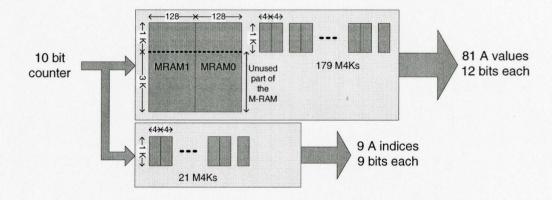

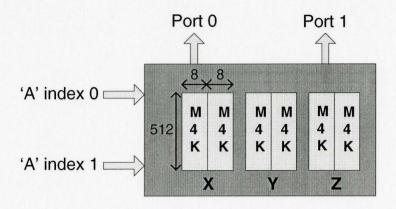

| 4.3  | Memory architecture for storing matrix ' $A$ '                          | 87 |

| 4.4  | Memory architecture for storing vector ' $d$ '                          | 88 |

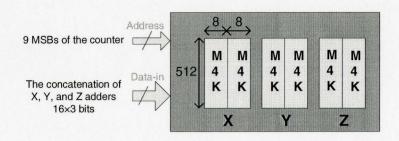

| 4.5  | The overview of the architecture                                        | 89 |

| 46   | Memory architecture for storing vector 'Ad'                             | 90 |

## Chapter 1

## Introduction

Digital electronics is playing a key role in society. The advancements in digital electronics have made it more useful and reliable over the past few decades. In fact, the transition from electromechanical machines to high performance computers with a fraction of power consumption has enabled us to use digital circuits in a vast variety of areas in modern life. Small and simple circuits in children's toys or more complex designs in cell phones, portable audio players, or laptops are all different examples of the usage of digital electronics. Their reliable operation and the ability to handle complex tasks has facilitated their application in economic sectors that require very high dependability, such as banking or aerospace engineering.

In this chapter we will start with a brief history of digital electronics in section 1.1. In section 1.2 we will describe the Moore's law and its different aspects. The section 1.3 will cover different implementation technologies for digital circuits and their pros and cons. In section 1.4 we will introduce Field Programmable Gate Arrays (FPGAs), which are the platform used for the research presented in this thesis. Finally, a short explanation of thesis organization is provided in section 1.5.

Figure 1.1: NAND and NOR gates designed with switches

### 1.1 Digital circuits

A digital circuit consists of logic gates and Boolean functions. All of these gates and functions can be built by switches. An example is presented in figure 1.1. Therefore, all digital circuits are based on 0-1 logic because a switch can only have 2 states: "ON" or "OFF".

The invention of the transistor was the beginning of a new era in electronics. Along with their ability to act like a current valve, transistors can be designed and configured to work like electronic switches. Their advantages over mechanical switches (relays) became evident between 1940 and 1960 [24]. Transistors were consuming significantly less power and had a much faster response time than mechanical switches and vacuum tubes. These two important facts were the main motivations for the new branch of electronics which is the "digital electronics".

The potential of digital circuits became evident soon thereafter, and advancements in digital circuit design and logic made them more useful everyday. Digital circuits started to handle more complex problems. Therefore, the number of transistors in a single circuit began to increase. The increase in the number of transistors has a direct effect on the power consumption of the circuit. To handle the power consumption of complex circuits with lots of transistors and also increase the processing speed of the circuit, engineers started to build smaller and smaller transistors. Shrinking the size of transistors has been known as the most effective method to increase the speed and reduce the power consumption of digital circuits in the physical design phase [24]. Also, it helps designers to embed more transistors in a limited area. The traditional transistors, which were components with their dimensions in the range of few inches and three wires attached to them, got phased out by microscopic transistors which were embedded on layers of silicon called "wafers", and engineers began to develop Integrated Circuits (ICs) which were the new generation of electronic circuits. The decreasing size of the transistors over the past few decades is explained by Moore's law in the next section.

#### 1.2 Moore's law

In 1965, Intel's co-founder Gordon E. Moore made an observation about the increasing speed and complexity of digital circuits. His prediction was that the minimum feature size will continue to decrease at a rate of roughly a factor of two per year [20].

In other words, Moore claims that the number of transistors in an integrated circuit doubles every year. Figure 1.2 presents the growing number of transistors in actual digital circuits over the past few decades. This increase in the number of

Figure 1.2: Moore's law [20]

transistors is only possible by advancements in reducing the feature size to control the power consumption and area of the chip. Figure 1.3 illustrates the relation between the Moore's law and minimum feature size over the past few decades [16].

In conclusion, we can assume that the Moore's law still holds only because of the advancements in physical design to reduce the size of transistors. The next section discusses different technologies to implement a digital circuit and their pros and cons.

Figure 1.3: Moore's law for minimum feature size [16]

## 1.3 Implementation technologies for digital circuits

There are a few methods to implement a digital circuit. Each method has its own advantages and disadvantages. Therefore, a designer chooses the implementation technology or even a certain combination of them to meet the specific requirements of a product. The designer should take a number of parameters into account such as:

- Performance

- Cost

- Design time

- Production volume

Basically, we can divide the implementation technologies into four groups [21]:

- Off-the-shelf packages

- Programmable logic designs

- Standard cell based designs

- full-custom designs

We will try to give a brief explanation for each approach and its limitations.

Figure 1.4: Discrete logic method[19].

### 1.3.1 Off-the-shelf packages

Many useful and essential logic functions are available in market as standalone ICs. One of the ways to design a logic circuit is to use these products in your design and connect them together in a proper way on a printed circuit board (PCB). In this method we are using individual logic parts in our design, so it is also called "Discrete logic". The discrete components in a design can vary from simple logic gates to more sophisticated elements like micro-controllers and programmable logic devices. Figure 1.4 shows a sample design using discrete logic approach.

Discrete logic designs can be very expensive for high product volumes because of the numerous parts which should be bought individually, also the cost for PCB and other peripheral costs increases the product cost. Furthermore, the test process for this family of designs is relatively time-consuming because of the number of devices. Also, they are not very reliable because of the connections outside of the chips. We should add the bulkiness to the disadvantages list of this family of designs.

On the other hand, off-the-shelf packages are flexible for performing partial changes or replacing faulty parts. Also, discrete logic designs can be very economical in low product volumes.

#### 1.3.2 Programmable logic designs

This family of designs can be categorized in the semi-custom approaches. The simplest programmable logic device (PLD) is a read-only memory (ROM). We can place the truth table of a function in a ROM. The inputs of the function are the address lines and the contents of the memory are the outputs for each combination of the inputs. This approach is limited due to the exponential increase in the memory size with respect to increasing the number of inputs.

A more sophisticated approach to design programmable logic is to use programmable logic arrays (PLAs) or programmable array logics (PALs). PALs and PLAs are simple programmable ICs with prefabricated AND-OR or OR-AND logic system. Therefore, they are suitable to implement product-of-sum (PoS) or sum-of-products (SoP). We can program the interconnects from input pins to the inputs of the logic in the first level (ORs in PLAs and ANDs in PLAs). This enables us to create the products in SoP form or the sums in PoS form. Figure 1.5 shows the structure of a PLA and how a designer can program its interconnects. PLAs and PALs can also have registers embedded in them to hold the current state of the circuit and use it in the next clock

Figure 1.5: Programmable logic array (black dots represent the programmed interconnects).

cycle. Therefore, they can be used to implement state machines.

Today, the most sophisticated programmable logic ICs are field programmable gate arrays (FPGAs). FPGAs have both programmable interconnect network and programmable logic functions ability. We will discuss them more deeply in section 1.4.

#### 1.3.3 Standard cell based designs

Similar to programmable logic designs, this approach is in the category of semi-custom designs. However, standard cell based designs are moving toward more integration. This family of designs consists of rows of standard cells. Each cell performs a fundamental logical function such as: NAND, NOR, register, inverter, and many other more sophisticated functions like single bit adders with different fan-outs. Therefore, a proper combination of different cells can create any digital circuit. These cells are designed with certain standards and parameters in order to match with each other in rows.

To implement a circuit with this approach, the designer should first synthesize the design using a certain cell library. The next step is to place the cells in the design in a proper way which minimizes the complexity of routing. Finally, a routing algorithm should be used to connect the cells in a proper way using different layers of metal.

In this method the masks of the design for different layers are created by computer aided design (CAD) tools, which is more time consuming than the previous approaches. However, predesigned cells are helpful to reduce the duration of the design process with the cost of losing a relatively small percentage of performance.

For small product volumes this method can be very expensive due to the cost of engineering tools and time, and the cost of preparing the masks. However, the increasing the volume of the product will vanish these costs. The performance of this method is higher than the previous ones because of the level of integration. Figure 1.6 shows a design with its three rows of standard cells, and the connections among cells with different metal layers.

Figure 1.6: Connections between three rows of standard cells[2].

#### 1.3.4 Full-custom designs

This method is the most expensive and time consuming method to design a digital circuit. However, the result has the smallest size and highest performance. Also, this method is the most economical method for high product volumes because the reduction in size of each chip offsets the high cost of mask development.

Unlike the standard cell based method, this method does not use predesigned cells, and the designer should design the physical layers of the design from scratch. Therefore, the engineering cost of this method is higher than the previous one because the designer has to deal with the masks of all layers. This extra effort pays back when it comes to the area of the chip and its performance. By designing all physical layers from scratch, the designer is now able to use all possible methods to enhance the performance of the product. Moreover, the product of this method is the most reliable among all of the digital circuits' development technologies.

We discussed the four main methods to develop digital circuits and their advantages and limitations. Figure 1.7 gives a rough idea about the relation between the cost and product volume for all technologies. Figure 1.8 presents a diagram to compare chip area versus design time for all technologies. A summary of what we discussed in this section so far is available in table 1.1.

It is obvious that in many cases an intelligent design can use a number of these technologies together to take advantage of each one in the best way. Today, many advanced processors have a programmable part which can be configured to do certain tasks much faster. Also, many designs are a combination of both standard cell and full-custom approaches together, and the reason is that in some parts of the design the performance is critical unlike other parts. Therefore, the designers use

Figure 1.7: Package cost vs. product volume [21]

Table 1.1: Comparison of different task-realization approaches.

| Feature     | Full-custom | Standard-cell based | Programmable logic | Off-the-shelf |

|-------------|-------------|---------------------|--------------------|---------------|

|             |             |                     |                    | package       |

| Performance | Fastest     | Fast                | Medium             | slow          |

| Unit cost   |             |                     |                    |               |

| High volume | Lowest      | Low                 | Medium             | Highest       |

| Low volume  | Highest     | High                | Medium             | Lowest        |

| Development |             |                     |                    |               |

| time        | Longest     | Long                | Medium             | Short         |

Figure 1.8: Chip area vs. design time [21]

full-custom technology for those parts, and develop the other parts with cell-based methods because this method is much faster while giving a reasonable performance. Another good example for using a combination of technologies in one design is a modern FPGA. These FPGAs have custom designed multipliers and basic signal processing units in them; the reason is that these units are used frequently in digital designs in FPGAs. Therefore, FPGAs try to provide some of these units to enhance the performance of the designs running on them.

### 1.4 FPGAs

As discussed earlier the advantage of FPGAs over other programmable logics is that they have both programmable logic blocks and programmable interconnects. FPGAs consist of a large set of basic blocks with the ability to be programmed. Each blocks usually has a four to six input look-up table (LUT) along with one or two registers

Figure 1.9: FPGA structure[5].

with some peripheral logic. Figure 1.9 shows a FPGA and the position of its logic blocks and interconnects.

Based on the complexity of the logic blocks in a FPGA we can categorize FPGAs into two categories:

- Fine grain FPGAs

- Coarse grain FPGAs

The disadvantage of coarse grain FPGAs is that usually designers can not use the entire embedded logic in each block, so the amount of unused logic increases when we use this kinds of FPGAs. On the other hand, the complexity of the logic blocks helps the designers to use less number of blocks for a certain circuit compared to a fine grain FPGA. It means that coarse grain FPGAs use less interconnect resources

Figure 1.10: 4-input logic block

because of the enhanced ability of each block. Figure 1.10 shows the schematic of a sample 4-input logic block. For more detailed schematics please refer to [1, 29].

The logic blocks in fine grain FPGAs are designed in such a way that they are simple enough that a synthesis tool can use most of the embedded logic in each block. However, the simplicity of the blocks makes the synthesis tool use more of them for a certain task. Therefore, we will have a pressure on the routing resources to connect all the used cells together in a proper way.

We can also categorize the FPGAs based on the technology used to program the interconnects:

- Fuse based FPGAs

- Memory based FPGAs

The advantage of memory based FPGAs is that they can be programmed several times. However, due to the use of memories they are a bit slower than fuse based ones. On the other hand, the disadvantage of the fuse based FPGAs is that we only can program them one time.

Most of modern FPGAs are coarse grain and memory-based. In this case, they can be programmed several times, and having more complex logic blocks reduces the amount of required interconnects which increases their performance. Today, FPGAs have more components embedded in them such as processing units and memories.

Many digital applications use a basic set of arithmetic functions such as multiplication. Many of today's FPGAs have a set of embedded arithmetic functions such as multipliers to help the designers. These multipliers have a limited number of bits. For example in the Stratix II FPGA (manufactured by Altera), each multiplier has 9-bit inputs. However, these multipliers can be chained together to create multipliers with a higher number of bits.

Embedded memories are important components of FPGAs. Almost all FPGAs have embedded memories in them. The architecture of the FPGA is designed in such a way that it has thousands of small embedded memory chunks all over it between logic blocks and interconnects. These memory parts are usually identical in their capacity and dimensions. However, some FPGAs, such as Altera's Statix family, have more than one type. Each type has a different capacity and available bit widths for its address and data. For example, the Stratix III has three types of memories embedded in it.

Memory parts can have several configurations (address and data bus bit width), and in each configuration they can have different properties such as different number

| Feature             | MLABs   | M9K Blocks | M144K Blocks |

|---------------------|---------|------------|--------------|

| Maximum performance | 600 MHz | 600 MHz    | 600 MHz      |

| Quantity            | 6750    | 1040       | 48           |

| Configurations      | 64*8    | 8K*1       | 16K*8        |

| (depth*width)       | 64*9    | 4K*2       | 16K*9        |

|                     | 64*10   | 2K*4       | 8K*16        |

|                     | 32*16   | 1K*8       | 8K*18        |

|                     | 32*18   | 1K*9       | 4K*32        |

|                     | 32*20   | 512*16     | 4K*36        |

|                     |         | 512*18     | 2K*64        |

|                     |         | 256*32     | 2K*72        |

|                     |         | 256*36     |              |

Table 1.2: Memory elements in EP3SL340 FPGA from Stratix III family [1].

of ports. Therefore, we can configure each memory block differently. All these types and configurations are there to make FPGAs more flexible and more usable for a large spectrum of applications. Table 1.2 shows the types and configurations for embedded memories of EP3SL340 FPGA from the Stratix III family by Altera.

### 1.5 Thesis organization

This thesis presents a solution for an emerging problem in CAD tools for FPGAs, which is the memory management problem. Chapter 2 is provides a literature review of similar problems tackled in the past. Also, in this chapter we will formulate the problem we are dealing with in this thesis. Chapter 3 discusses the problem in depth, and gives a solution to it in some special and common cases. Also, in this chapter we discuss an acceptable heuristic method to solve the problem.

Chapter 4 contains a case study along with some experimental and analytical results of the proposed method. Finally, chapter 5 concludes what we discussed in the thesis and covers the future work and open problems.

## Chapter 2

## Literature Review

In the previous chapter we briefly discussed the digital electronics and the rate of the advancement in this field captured by Moore's law. We have also introduced different implementation technologies and their advantages and disadvantages, which make each of them suitable for a certain family of designs with their specific parameters and requirements.

In this chapter we will address the problem which we investigate in this thesis. To better understand our problem we will introduce the general binding problem in computer aided design (CAD), and its role in behavioral and logic synthesis in section 2.1. Then to create a link between the resource binding and data path of a design, we will discuss data path and memory organization in digital designs in section 2.2.

The connection between the binding problem and data path organization of a design is in physical memory binding. Physical memory binding, which is a step in data memory organization, will be discussed in section 2.3. In section 2.4 we will discuss the reasons why we cannot use the traditional binding approaches to attack the problem of physical binding and why this was not an issue in the past. Finally,

we will formulate the problem, and define the important metrics in section 2.5.

### 2.1 Binding problem in CAD

The design flow of a digital circuit consists of different layers of abstraction from behavioral descriptions to physical descriptions. The binding problem can be discussed in two different layers of abstraction: architectural-level and logic-level. The binding problem in the architectural-level, which is a higher-level description, is discussed first. Later, we will focus on the logic-level binding.

### 2.1.1 Binding in architectural synthesis

Architectural synthesis is the process of constructing a gate-level description of the design from a behavioral model, such as data-flow or sequencing graph. Architectural synthesis consists of two main steps: scheduling and binding.

Scheduling is responsible for the timing of each operation in the design. In other words, we define exactly when to start each operation in terms of clock cycles. There are various methods for scheduling, from basic methods such as "as soon as possible" (ASAP) and "as late as possible" (ALAP) to more sophisticated approaches with different purposes such as minimizing the runtime or minimizing a certain type of a required physical resource. Figure 2.1(a) illustrates the flow of a simple design which consists of 6 multiplications and 5 ALU operations. This design is scheduled with a sample scheduling algorithm in figure 2.1(b).

Resource binding is the process of assigning operations of the design to the physical resources. In this mapping we move from an abstract functional description toward

Figure 2.1: A sample design before and after scheduling[8].

a more feasible physical description. In many cases resource binding is accompanied with resource sharing, which is a crucial task in hardware design. Resource sharing is the process of sharing a physical resource between two or more logical operations which are not concurrent.

Resource sharing has an important role in managing the physical size of a design. By sharing the same resource between multiple non-concurrent operations in the design we can reduce the number of physical resources which results in the reduction of the design area in many cases. The area of a design has a direct effect on its working frequency and power consumption.

Assuming that we have two types of physical resources (multipliers and ALUs), we can create the compatibility graphs of each resource type. The compatibility graphs for this example are presented in figure 2.2. The compatibility graph presents the information about the operations we can assign to the same physical resource because each edge in the graph represents a possible sharing of a physical resource between

Figure 2.2: Compatibility graphs for resource binding[8].

to operations because they are not concurrent.

There exist different resource binding algorithms with different concerns. Figure 2.3 shows a sample binding of our example based on the compatibility graphs of figure 2.2. Apparently, in this example the binding is done with two multipliers and two ALUs. It is apparent that we could do the binding with only one resource of each type. However, it would make the design slower in terms of latency because we had to stall some operations until the required resource is available.

Besides binding logical operations, register binding is an important part of each design which influences the overall architecture and performance of the design. There are many approaches for register binding, each of them working on different parameters of the design. A helpful tutorial to all of the steps discussed above can be found in [8].

Figure 2.3: A sample binding of our example[8].

Figure 2.4: Different binding approaches[8].

### 2.1.2 Binding in logic synthesis

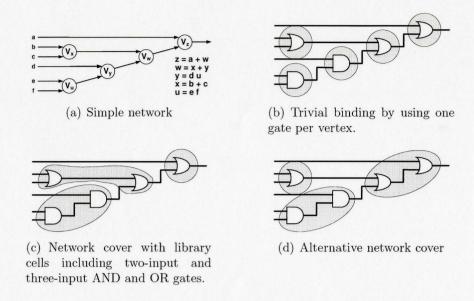

The logical-level problem of binding is library binding, which is often referred to as "technology mapping". The difference between the architectural-level binding and library binding is that in architectural-level binding we assign each logical operation to a gate. However, in library binding most of the physical resources in the library are more complex than a single logical gate. Moreover, the elements of the library have some other parameters beside their structure which are important in the design, such as area and delay. Figure 2.4 shows the difference between the basic binding problem and the practical library binding.

Library binding is important in standard-cell and FPGA based circuit design because it provides an interface to the physical implementation. Moreover, library binding provides the means for retargeting logic design to different implementation technologies.

A library contains a set of physical resources in different forms with different parameters. Therefore, the binding algorithm should use these parameters to do the binding process with respect to some objectives, such as area, delay, or testability of the design.

The practical approaches to library binding can be classified into two major groups [8]:

- Heuristic algorithms

- Rule based approaches

The heuristic approach to solve the library binding problem is based on its likeliness to code generation in compilers. In both cases we deal with a matching problem, and the choice of optimal matches. The proposed methods to solve the matching problems can be categorized into two major groups:

- Boolean approaches

- Structural approaches

Both of these approaches have been used in the algorithmic library binding. The Boolean method is explained in depth in [3, 30]. For more information about the structural methods please refer to [8].

The rule based approaches for binding are usually used as a complement to algorithmic binding. The basic idea of this method is to refine the circuit step by step.

In other words, these refinements are some local changes to the circuit which do not change the circuit behavior, and just replace an equivalent sub-circuit. Moreover, these rules can have priorities over each other [7, 4, 6].

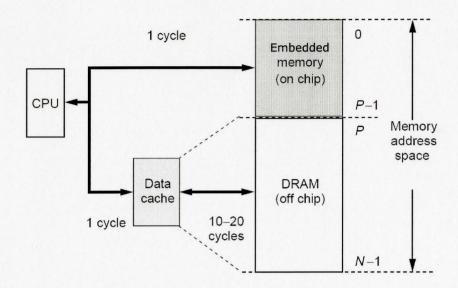

# 2.2 Data memory organization

So far we have only discussed the logical functions in a design, which define the control path. In the following section we will focus on the complementary part of digital circuits, which is the data path. The flow of the data in the design is through different functional units, registers and memory units. Therefore, the arrangement of these units and their contents is an important part of the design.

There are several methods for memory architecture, and each method has its own properties and usage. There is a lot of research done in this field, and a proper summary of all different approaches for memory organization can be found in [23, 15, 13].

All these methods focus on different ways to access data from physical memories with minimum cost. They try to manage the storage of the data based on the way the design accesses them with a high level vision. The bottom line of all these approaches is to keep the data which is more frequently accessed within the algorithm closer to the processor and in the memory units with lower access cost. Figure 2.5 shows the different memories in the addressable memory space of a Central Processing Unit (CPU) with different access-times.

In other words, the focus of this area of research is to decide which parts of data to keep in on-chip memories, and how to cache data to reduce cache misses. The proposed approaches in this field perform a study on the algorithm behavior in its

Figure 2.5: Memory levels of a sample design[23].

data accesses, and try to enhance the performance of the data access process [14]. Therefore, they do not work on the details of the physical implementation of the memory architecture, which we refer to as physical memory binding.

# 2.3 Physical memory binding

Similar to logical resource binding, physical memory binding is crucial in migrating between different implementation technologies because each technology has its own specific parameters in logical and memory units. We can divide the research on memory binding into two main branches:

- Memory binding in ASICs

- Memory binding in FPGAs

In the case of ASICs, the problem is to select suitable memory components from a memory library, and performe an acceptable placement, and design the interfaces to access the memories. In this case there is some research done on how to store data vectors in physical memories, guarantee the access to each data element within an acceptable time, and with an acceptable cost [12, 25, 26, 28].

In the case of FPGAs, the problem is different because the hardware is fixed, and the designer can only decide on a suitable configuration within the given choices as well as the interconnects and peripheral logic around each memory unit. The research in this field is limited to an approach to bind a single data vector to multiple types of physical memories which are not reconfigurable [11]. There is also an Integer Linear Programming (ILP) formulation presented in [22] to give an exact solution to the problem with some simplifying assumptions which affect the real problem radically. The assumptions in this formulation are:

- Different ports of a single physical memory can have completely different configurations.

- All the physical memories used in covering a single data structure are from the same type.

Moreover, this method does not account for the peripheral logical resources nor the minimization of the amount of physical storage we need to use. It only works based on the latency and access-time cost. On the other hand, this method tries to expand itself to the external memory banks and some of the parameters which they imply to the design, which makes it unique in this case. There are also some industrial efforts to solve the problem of physical memory binding in FPGAs [1]. However, these tools are not powerful enough to handle the complexity of today real-world problems because:

- They work on only one data vector.

- They only use one type of physical memories in each solution.

- They only use one configuration of the used physical memory.

- In many cases the user should provide the suitable configuration to the tool.

Having these limitations, the industrial tools are not able to work on the peripheral logic and leftover minimization. Optimization aside, in some cases these tools are not even able to generate a solution for the given problem.

## 2.4 Motivation for our work

The main motivation for this research is that the physical memory binding in FPGAs is a new problem in CAD tools for FPGAs, and so far this task was mainly done by engineers. However, the following two reasons are increasing the complexity of this task beyond the ability of an engineer during an acceptable time:

a) The advancements in the fabrication technology have enabled FPGAs with hundreds and even thousands of physical (also called embedded) memories with different types and configurations [1, 29]. However, early FPGAs had very limited embedded memory resources or even none, so we did not need a tool to

Table 2.1: Memory elements in EP2S180 FPGA from Stratix II family [1].

| Feature             | M512 RAM Block | M4K RAM Block | M-RAM Block |

|---------------------|----------------|---------------|-------------|

| Maximum performance | 500 MHz        | 550 MHz       | 420 MHz     |

| Quantity            | 930            | 768           | 9           |

| Configurations      | 512*1          | 4K*1          | 64K*8       |

| (depth*width)       | 256*2          | 2K*2          | 64K*9       |

|                     | 128*4          | 1K*4          | 32K*16      |

|                     | 64*8           | 512*8         | 32K*18      |

|                     | 64*9           | 512*9         | 16K*32      |

|                     | 32*16          | 256*16        | 16K*36      |

|                     | 32*18          | 256*18        | 8K*64       |

|                     |                | 128*32        | 8K*72       |

| ]                   |                | 128*36        | 4K*128      |

|                     |                |               | 4K*144      |

map the data vectors to those resources. Table 2.1 shows the types and configurations for embedded memories of EP2S180 FPGA from Stratix II family designed and manufactured by Altera company.

b) The advancements in FPGAs have made them very powerful. Therefore, they are able to process a larger amount of data. The huge parallelism that FPGAs provide today has increased the data volume which we have to feed to them. Consequently, the number and volume of processing data vectors have increased recently. Another important reason for this increase is the migration of different algorithms from floating-point to custom floating-point or fixed-point algorithms. This migration is very critical to fully utilize the provided parallelism by FPGAs because it reduces the size of processing units, so we can fit more of them in a single FPGA chip.

We cannot use the traditional binding algorithms to solve the physical memory binding problem because these two types of binding have some key differences between them. Two examples for these differences are:

- In the physical memory binding problem we have the challenge of reducing the peripheral logic required to guarantee the proper access to all data elements.

This problem does not exist in logical resource binding.

- In physical memory binding we want to create a solution with the minimum wasted storage in the physical memories. We have the same problem in library binding in FPGAs because we wish to use all the logic prepared in each cell to reduce the overall number of used cells. However the methods we need for these two minimizations are different. This variation comes from the differences in the way we map data vectors and operations to the physical resources.

In the next section we define the problem which we investigate in this thesis.

#### 2.5 Problem formulation

This thesis addresses the problem of physical memory binding in FPGAs. The physical memories in FPGAs are also commonly referred to as embedded memories. Assuming that we have multiple types of physical memories, and from each type we have a limited number, and each type has a set of different configurations, we want to store in them a set of data vectors called virtual memories.

It is important to stress that efficient use of embedded memories in FPGAs is very important in the overall performance of the design because it enables us to store a larger amount of data close to the processing units. Therefore, it minimizes the access to the external memories which is usually slower compared to on-chip memories. Moreover, the bandwidth of the on-chip memory units is not comparable to the external memories because we have to deal with the limitations of the number of I/O pins of the FPGAs. However, we can access a large amount of data from several embedded on-chip memories in the FPGA without these I/O limitations.

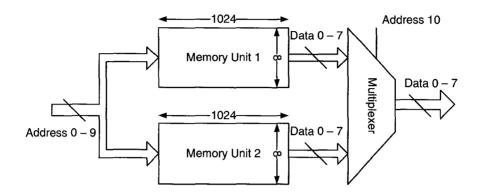

We have defined two cost functions in the process of embedded memory binding in FPGAs:

- Amount of required peripheral logic in terms of logic cells in the FPGA (multiplexer cost)

- Amount of wasted embedded memory bits (leftover)

The peripheral logic size in our case can be translated to the multiplexer cost of the design. In other words, when we divide a virtual memory which is larger than a single physical memory into several physical memories, in some cases we have to choose the physical memory we want to work with based on the provided address, so we will need a multiplexer. Figure 2.6 presents the multiplexers in a sample mapping. Obviously, we need eight 2:1 multiplexers to create this mapping.

An embedded memory binding which is wasteful in logical resources can affect the entire design in an FPGA because it is possible that we have to reduce the size or the number of the processing units in order to save some logic to do the memory binding. However, by performing the binding process with less logical resources, we will be able to use that logic in the processing part of the design to enhance parallelism and increase the processing speed or resolution. Furthermore, when the binding is done

Figure 2.6: Generated peripheral logic in memory mapping

with an extensive use of logic cells in the FPGA, this added logic will increase the timing between the memory and the processing units because it is placed between the memory and logic part of the design.

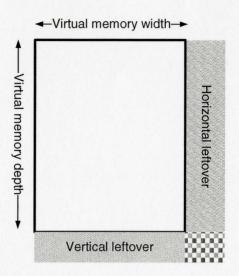

The leftover is the amount of unused bits of physical memories which we have used to cover the virtual memories. We can define two types of leftover: horizontal leftover and vertical leftover. This categorization will help us later in the design of the algorithms. Figure 2.7 shows the two types of leftovers in a sample coverage.

In this project we have only worked with on chip physical memories because it simplifies the timing properties. The access times of all on chip physical memories in today FPGAs are close to each other, so we can assume that it takes the same number of clock cycles. Moreover, due to limited amount of embedded memory resources, we cannot guarantee the minimization of the cost functions by working on virtual memories individually. Consequently, we should perform the mapping problem for all virtual memories in the problem concurrently.

In order to simplify the reading of this thesis, we should explain some of the terms which we will use in the following chapters: VM stands for "virtual memory",

Figure 2.7: Vertical and horizontal leftover

and PM refers to "physical memory". Also, when we discuss the configurations of a physical memory, we refer to the number of their address entries as their *height*, and the number of data bits in each address location is denoted as their *width*. Therefore, we can define the concept of a *short* (wide) or *tall* (thin) configuration based on its height compared to other possible configurations.

# Chapter 3

# Algorithms for Binding Virtual Memories to Physical Memories

In the previous chapter we discussed the general binding problem in CAD, and more specifically the physical memory binding problem. We also discussed some reasons why the memory mapping process in FPGAs was not a major concern in the past, and why it is getting more complicated for existing and future designs. Furthermore, we summarized the differences between the memory mapping problem in FPGAs and other binding problems in CAD.

In this chapter we present a solution for the physical memory binding in FPGAs through some intermediate steps which are simplified subproblems. These subproblems will help us understand the role of different parameters involved in the complexity of the problem and its solution space. However, the ultimate goal is to solve the problem in the case of multiple virtual memories and multiple types of reconfigurable physical memories.

Because the problem we are tackling (physical memory binding for FPGAs) involves fitting small physical memories (rectangles) into large virtual memories (bins), one may argue that it is similar to the well-studied bin-packing or knapsack problems. We first outline the differences between our problem the above known-problems. The bin packing problem involves fitting a number of rectangular objects in as few bins as possible [10]. The rectangular objects have different sizes, and the dimensions of the bins are defined. We can also relate the problem to the 2-dimensional knapsack problem, which is putting a number of different-sized rectangular objects with different values in a 2-dimensional knapsack with known dimensions to maximize the overall value in the knapsack [18].

However, our problem is different because we allow the creation of leftover which is not defined in any of the prior problems. Moreover, the rectangular objects which we deal with are not random-sized because the depth (and in many cases the width) of the physical memories are powers of 2 and multiples of each other. The fact that physical memories are in most cases reconfigurable (i.e., although the memory capacity stays the same, the aspect ratio changes from one configuration to another) adds an additional dimension to our problem. In addition, the concept of multiplexer cost cannot be introduced in any of the prior problems.

Although both problems of bin-packing and 2-dimensional knapsack are known as NP-complete problems, we cannot assume that our problem is also NP-complete. Nonetheless, our experience with it indicates that the problem is intractable. Therefore, due to the lack of a formal proof, we conjecture that the problem is NP-complete. For the rest of this thesis we focus on understanding its solution space and designing effective algorithms that can be adopted in the industrial practice.

Based on the problem definition in the previous chapter, we can list the parameters with a significant role in the complexity of the problem as follows:

- Number of virtual memories,

- Number of different types of physical memories,

- Number of physical memories in each type,

- Number of different configurations for each type of physical memories,

The factors mentioned above help us to notice and understand the subproblems which can help us to design a solution for the problem in its general format. Each subproblem is created with elimination of at least one of the complexity factors of the general problem. In the next three sections of this chapter we will try to discuss the following three subproblems:

- Single virtual memory & one type of reconfigurable physical memory,

- Multiple virtual memories & one type of reconfigurable physical memory,

- Single virtual memory & multiple types of reconfigurable physical memories,

After discussing the above subproblems we will try to attack the problem in its general format, which is "multiple virtual memories & multiple types of reconfigurable physical memories". This is discussed in the fourth section of this chapter. Finally in section 3.5 we will describe a heuristic method to attack the problem in its general format.

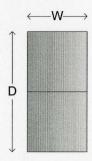

# 3.1 Single VM - Single PM Type

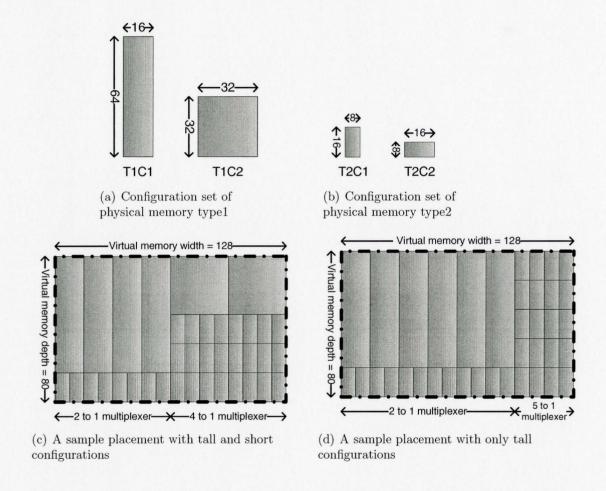

In this problem we intend to map one virtual memory to a number of identical physical memories. Each used physical memory has a configuration chosen from a variety of predefined configurations. The only complexity factor in this case is the decision about the configuration of the used physical memories. It is needless to mention that the capacity of all configurations are equal, and the difference lies in the differences in their dimensions, so as the height of configurations grows their width starts to shrink.

#### **Observation 1:** Using tall configurations reduces the multiplexer cost.

By using tall configurations we will be able to cover the depth of the virtual memory with a smaller number of physical memories on top of each other. Therefore, we will have a smaller multiplexer cost. Figure 3.1 shows a sample area which we can cover with two different configurations. It can be seen that the first case creates a 2:1 multiplexer which easily can be eliminated by using the taller configuration in second case. However, this method does not always guarantee the minimum leftover.

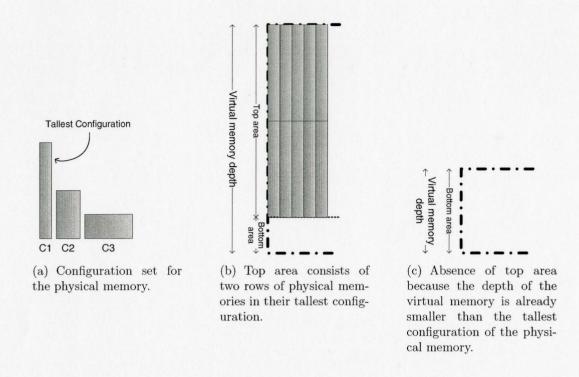

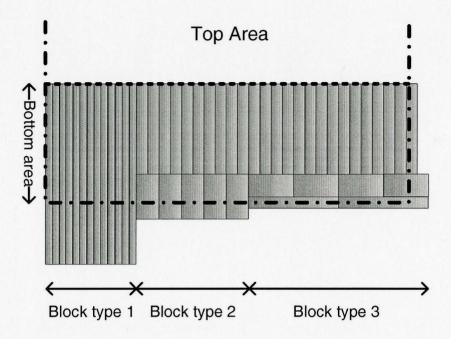

To attack the problem in this case (one virtual memory and one type of physical memories) we can divide the virtual memory into two areas and work on them separately. This division is done based on the depth of the tallest configuration of the used physical memory.

The first area, which is at the top of the virtual memory, is an area which we can cover by using the physical memories in their tallest possible configuration without creating any vertical leftover. Therefore, we can simply cover all of this area by putting the physical memories in their tallest configuration next to and at the top of each other. This method also creates the minimum amount of horizontal leftover

(a) Formation of 2 to 1 multiplexers due to the chosen configurations.

(b) Elimination of the multiplexers for the same area by changing the configuration of the used physical memories.

Figure 3.1: Elimination of unnecessary multiplexers.

for this area because tall configurations have smaller widths compared to short configurations. Therefore, the leftover area which is created by the unused width of the physical memories in the last column is minimized in this case.

#### Observation 2: Using tall configurations reduces the horizontal leftover.

This observation is always true assuming that the widths of the physical memory in its different configurations are multiple of each other. This assumption is valid in all the regular configurations of the physical memories of today FPGAs. Regular configurations are the configurations which do not use the allocated parity bits as data bits to increase the capacity of the physical memory, which may affect the reliability of the design in environments that are prone to soft errors.

The second area is the remaining part at the bottom of the physical memory. This area cannot be filled with the tallest configuration without creating any vertical leftover. Figure 3.2 shows an example of different configurations of a sample physical

Figure 3.2: Division of the virtual memory into two parts.

memory and the division of the virtual memory into two areas based on the given configurations.

In conclusion, by dividing the virtual memory into two areas based on the depth of the tallest configuration of the physical memory we can cover the top part with minimum leftover and multiplexer cost. This is simply done by using the physical memories in their tallest configuration to cover the top area. However, the binding process for the bottom area depends on the objective of the algorithm. Hence, this area can be filled with two different strategies:

- Minimizing the amount of leftover.

- Minimizing the multiplexer cost.

In the following subsections of this section we will discuss the methods for binding the bottom part of the virtual memory for minimization of leftover and multiplexer cost respectively.

#### 3.1.1 Binding for Leftover Minimization

As introduced in section 2.5, there are two types of leftovers in a physical memory binding problem: vertical and horizontal. To minimize the overall leftover we have to minimize the sum of these two amounts. In this section we will start with minimizing the vertical leftover in a binding problem, and then we will relate it to the horizontal leftover minimization.

Vertical leftover is the result of using configurations of the physical memory which are taller than the uncovered area at the bottom of the virtual memory. The larger the difference between the depth of the configuration and the depth of the uncovered area, the more leftover will be created. Therefore, we can reduce the vertical leftover by using the configurations which are shorter than the depth of the bottom part.

In other words, it is likely to reduce the vertical leftover by replacing a tall configuration used in the bottom area with a combination of the configurations which are shorter than the depth of the bottom area. It is obvious that this optimization in vertical leftover comes with an increment in the multiplexer cost because we will have more physical memories on top of each other.

Observation 3: The depths of different configurations of a physical memory are a multiple of each other.

A simple method can help us find the set of configurations which minimize the vertical leftover using the third observation. Each time we want to add a memory to cover the remaining depth of the virtual memory, we have two options:

- Choosing the shortest configuration which is taller than the remaining depth (this option creates leftover).

- Choosing the tallest configuration which does not create leftover (this option decreases the remaining uncovered depth of the virtual memory which we will try to cover in the next level by repeating this decision again).

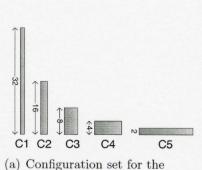

By choosing the second option every time we can find the desired set of configurations. The only concern is that having two identical configurations on top of each other is not acceptable because it will violate the first observation. Figure 3.3 shows the bottom area of two virtual memories and all the configurations of a certain physical memory which should be used to cover them.

It is apparent that as we proceed in the algorithm, we can come up with less leftover with the penalty of increasing the multiplexer cost. It should be emphasized that in some cases it is impossible to have different ways to cover an empty area. For example, with the given configurations in figure 3.3 and a depth of 31, we only have one option to cover the empty area because all other options lead to two identical configurations on top of each other which violates the first observation.

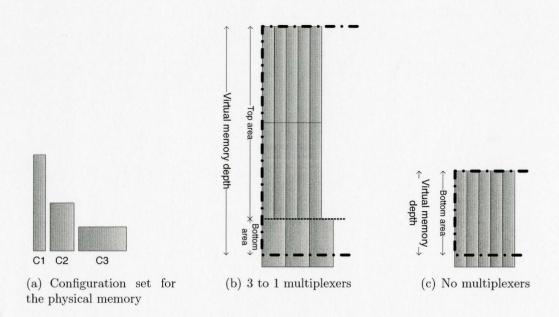

So far we have worked on the reduction of the vertical leftover in the bottom area of the virtual memory. However, the reduction of the vertical leftover can lead to more horizontal leftover because short configurations have a larger width. This

(a) Configuration set for the physical memory.

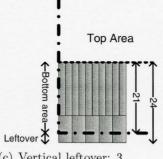

(b) Vertical leftover: 11. Bottom area mux size: 0.

(c) Vertical leftover: 3. Bottom area mux size: 2.

(d) Vertical leftover: 1. Bottom area mux size: 3.

(e) Vertical leftover: 3. Bottom area mux size: 0.

(f) Not acceptable.

(g) Not acceptable.

(h) Vertical leftover: 1. Bottom area mux size: 4.

Figure 3.3: Decreasing the vertical leftover.

43

(b) Block of physical memories used in figure 3.3(h).

Figure 3.4: Blocks of physical memories.

increase in the width of the configurations of physical memories can lead to a higher horizontal leftover.

Observation 4: The widths of different configurations of a physical memory are a multiple of each other.

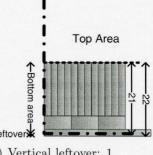

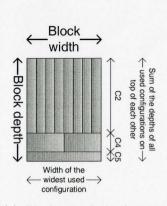

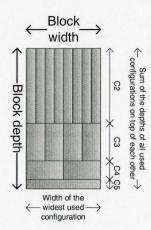

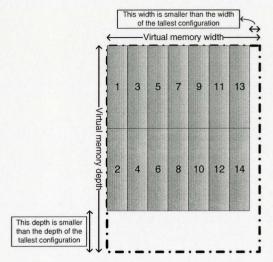

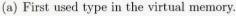

In order to solve this problem we can create blocks of physical memories with the best configuration set we have found to minimize the vertical leftover. These blocks have a rectangular shape because the widths of different configurations are a multiple of each other (observation 4). Therefore, the width of the block will be the width of the shortest (widest) configuration which we use in the bottom, and the depth of the block is the sum of depths of the used configurations. Figure 3.4 shows the blocks in the two cases of figures 3.3(d) and 3.3(h).

We can put these blocks of physical memories next to each other to cover the

bottom area of the virtual memory. These blocks create the minimum possible vertical leftover. However, the final block which we use at the very right side of the virtual memory can create horizontal leftover. In some cases the replacement of this block with other configurations which we have found in the previous step to cover the depth of the region is helpful to reduce the overall leftover. It is obvious that this replacement causes a greater vertical leftover. However, on the other hand the decrease in the horizontal leftover can make up for this in many cases. We have to calculate the leftover, and choose the minimum case. Figure 3.5 shows the use of different configurations instead of the last physical memory block and the effect of each configuration on the overall leftover.

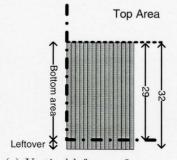

Apparently, the set of configurations used in the figure 3.5(c) results in the best overall leftover and multiplexer size. All the sets of configurations used in the final blocks of figure 3.5 are the results of intermediate steps of reducing the vertical leftover which are visible in figures 3.3(b) to 3.3(d).

To review what we have discussed in this subsection, algorithm 1 presents a pseudo code for the leftover minimization approach in a binding problem with one virtual memory and one type of physical memories. The inputs are:

- " $VM_{dimensions}$ ": The depth and width of the virtual memory.

- " $PM_{quantity}$ ": The number of available physical memory resources.

- " $PM_{configuration\_set}$ ": The list of available configurations (their widths and depths) for the physical memories.

The outputs are the solution to the problem which are the configuration of the

(a) Number of physical memories in the final block: 4. Multiplexer size of the final block: 3.

(b) Number of physical memories in the final block: 3. Multiplexer size of the final block: 2.

(c) Number of physical memories in the final block: 3. Multiplexer size of the final block: 0.

Figure 3.5: Different choices for the final block to reduce the overall leftover.

physical memories we have used in the solution (" $used\_PMs_{configuration}$ ") and their exact position in the virtual memory (" $used\_PMs_{disposition}$ ").

The "divide" function in the first line of the algorithm performs the procedure of dividing the virtual memory into "top" and "bottom" areas. This division is done based on the depth of the tallest configuration of the physical memory and the depth of the virtual memory, and as illustrated in line 1, these two parameters are the inputs of the "divide" function.

Then, we use the "cover" function in the second line to cover the top area of the virtual memory with the tallest configuration of the physical memory, and we save the coverage for the top area by updating the information of physical memories we have used in the solution by using the "update" function.

In line 4, the "block\_creator" function creates all possible combinations of the physical memory configurations on top of each other to cover the depth of the bottom area of the virtual memory with respect to the first observation, and stores them in "block<sub>list</sub>". The "while loop" in the fifth line covers the bottom area of the virtual memory with the block with the smallest heights among all blocks in the "block<sub>list</sub>" as long as it does not create any horizontal leftover, which is captured in the condition of the "while loop".

The "for loop" in line 9 covers the bottom-right part of the virtual memory with one of the blocks in " $block_{list}$ " each time. The "leftover\_calculator" function in the twelfth line calculates the leftover of the generated solution by subtracting the capacity of the virtual memory from the sum of the capacities of the used physical memories in the solution, and stores the result in " $leftover_{current}$ ". Also, the " $leftover_{best}$ " stores the leftover of the best solution so far. If the currently generated solution has a

smaller leftover than the best solution so far, we will overwrite the best solution and its leftover by the current solution. This procedure is captured in the "if statement" in line 13, and as presented in line 14; the "save" function stores the solution by saving the configuration and position of the used physical memories in the solution. Finally, the algorithm will return these values as its output.

```

Algorithm 1: Single VM - Single PM type leftover minimization

\overline{\text{Input}}: VM_{dimensions}, PM_{quantity}, PM_{configuration\_set}

Output: used\_PMs_{configuration}, used\_PMs_{disposition}

1 (top\_area, bottom\_area) = divide(VM_{dimensions},

PM_{tallest\_configuration} \in PM_{configuration\_set});

2 cover(top\_area, PM_{tallest\_configuration} \in PM_{configuration\_set});

3 update(used\_PMs_{configuration}, used\_PMs_{disposition});

4 block_{list} = block\_creator(bottom\_area_{depth}, PM_{configuration\_set});

5 while (leftover_{horizontal} = 0) do

//to reduce vertical leftover

cover(bottom\_area, block_{shortest} \in block_{list});

update(used\_PMs_{configuration}, used\_PMs_{disposition});

end

s leftover_{best} = \infty;

9 foreach block \in block_{list} do

cover(bottom\_area, block);

10

update(used\_PMs_{configuration}, used\_PMs_{disposition});

11

leftover_{current} = leftover\_calculator(VM_{dimensions}, used\_PMs_{configuration});

12

if (leftover_{current} < leftover_{best}) then

13

save(used\_PMs_{configuration}, used\_PMs_{disposition}); //save current solution

14

leftover_{best} = leftover_{current};

15

end

end

```

16 Return  $used\_PMs_{configuration}$ ,  $used\_PMs_{disposition}$ ;

Figure 3.6: Minimum multiplexer cost binding.

### 3.1.2 Binding for Multiplexer Cost Minimization

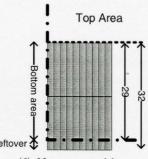

When we intend to minimize the multiplexer cost, we can simply choose the shortest configuration which completely covers the depth of the bottom area. Figure 3.6 shows the result of applying this method for two different virtual memories.

In fact, the solution with the minimum leftover gives the minimum number of required physical memories to cover the virtual memory, and the solution with the minimum multiplexer cost is the one with the maximum number of physical memories which we use in a reasonable solution. Therefore, when the number of available physical memories is less than the number we need to create the minimum leftover, the problem does not have a solution. Also, when the given number of physical memories is greater than or equal to the number of required physical memories to come up with the minimum multiplexer cost, we can easily solve the problem without

any concerns. However, we need to have a different approach to solve the problem when the given number of physical memories is between the minimum (number of required physical memories for minimum leftover) and the maximum (number of required physical memories for minimum multiplexer cost).

In this case, we have no problem with the minimum leftover solution because it consumes a lower number of physical memories than the given amount. However, when calculating the binding for the minimum multiplexer cost solution we have to deal with a new constraint, which is the number of used physical memories, so we cannot simply accept the solution mentioned at the beginning of this subsection. Instead, we want to use all of the given physical memories in a way that minimizes the multiplexer cost.

As mentioned earlier, we have filled the top part in an optimum way. Therefore, the solution in this case lies in the arrangement of physical memories in the bottom area of the virtual memory.

In subsection 3.1.1 we went through a number of steps to find all the sets of different configurations of physical memories to fill the bottom area of the virtual memory. Also, we defined blocks of physical memories based on each set of configurations. Now, the solution we are looking for is the correct combination and arrangement of these blocks. We may exclude some configurations or change the amount of area they cover to create all possible combinations. Figure 3.7 shows a sample combination of different configurations for the first virtual memory in figure 3.3.

The pseudo code for minimum multiplexer cost binding is presented in algorithm 2. In the first 3 lines of the algorithm we perform the exact procedure that we did in algorithm 1, and cover the top area of the virtual memory. In line 4, the

Figure 3.7: A sample combination of different blocks to reduce the multiplexer size

"max\_PM\_calculator" function calculates the maximum number of required physical memories to solve the problem in the case of minimum multiplexer cost, and stores this number in " $PM_{max\_required}$ ". Based on this number, in line 5 we choose the suitable strategy for multiplexer cost minimization. If we have sufficient available physical memories we cover the bottom part with the shortest configuration of the physical memory which is taller or equal to the depth of the bottom area ( $PM_{suitable\_configuration}$ ). This strategy is captured in lines 6 to 8.

In the other case, which is captured in lines 9 to 18, we create all blocks of physical memories with respect to the depth of the bottom area, and save them in " $block_{list}$ ". The "for loop" in line 12 is in charge of creating all possible combinations of blocks next to each other ( $block_{set}$ ) to cover the bottom area. The multiplexer cost

#### Algorithm 2: Single VM - Single PM type multiplexer cost minimization

```

Input : VM_{dimensions}, PM_{quantity}, PM_{configuration\_set}

Output: used\_PMs_{configuration}, used\_PMs_{disposition}

1 (top\_area, bottom\_area) = divide(VM_{dimensions});

2 cover(top\_area, PM_{tallest\_configuration} \in PM_{configuration\_set});

a update(used\_PMs_{configuration}, used\_PMs_{disposition});

4 PM_{max\_required} = \max\_PM\_calculator(VM_{dimensions}, used\_PMs_{configuration},

used\_PMs_{disposition});

5 if ((PM_{guantity} - \# of used\_PMs) \ge PM_{max\_required}) then

PM_{suitable\_configuration} =

shortest(PM_{configuration} \in PM_{configuration\_set}) > bottom\_area_{depth};

cover(bottom\_area, PM_{suitable\_configuration});

update(used\_PMs_{configuration}, used\_PMs_{disposition});

end

9 else

block_{list} = block\_creator(bottom\_area_{depth}, PM_{configuration\_set});

10

multiplexer\_cost_{best} = \infty;

11

foreach block_{set} \subseteq block_{list} do

12

cover(bottom\_area, block_{set});

13

update(used\_PMs_{configuration}, used\_PMs_{disposition});

14

multiplexer\_cost_{current} = \max\_cost\_calculator(VM_{dimensions},

15

used\_PMs_{configuration}, used\_PMs_{disposition});

if (multiplexer\_cost_{current} < multiplexer\_cost_{best}) then

16

save(used\_PMs_{configuration}, used\_PMs_{disposition}); //save current solution

17

multiplexer\_cost_{best} = multiplexer\_cost_{current};

18

end

end

end

19 Return used_PMs_{configuration}, used_PMs_{disposition};

```

of each generated solution is calculated with "mux\_cost\_calculator" function using the dimensions of the virtual memory and all used physical memories in the solution, and stored in " $multiplexer\_cost_{current}$ ". The "if statement" in line 16 compares the multiplexer cost of the current solution with the multiplexer cost of the best solution so far (" $multiplexer\_cost_{best}$ "), and overwrites the best solution and its multiplexer cost so far if the current solution gives a smaller multiplexer cost.

# 3.2 Multiple VMs - Single PM Type

To make the problem we discussed in the previous section more general we can work with multiple virtual memories. Therefore, in this section we will work on minimization of leftover and multiplexer cost in the case of multiple virtual memories and one type of physical memories. The overall multiplexer cost and leftover will be the sum of all multiplexer costs and leftovers for all virtual memories.

In many cases, working on the virtual memories independently can lead to minimization of the overall leftover and multiplexer cost because the resources are identical, so the use of a certain physical memory in a virtual memory does not limit the choices for other virtual memories. However, this is not always the case. We will discuss the problem in its different cases in more details below.

To minimize the overall leftover, we can minimize the leftover in each virtual memory independently. Therefore, the same method introduced in the previous section can be applied to each virtual memory to minimize the leftover in binding process. In the case of minimizing the overall multiplexer cost with adequate number of physical memories, we can apply the same algorithm in the previous section and work on the virtual memories independently.

The minimum number of physical memories we need to solve the problem is the number of used physical memories in all virtual memories when the leftover is minimized. Also, the maximum number of physical memories we will consume to solve the problem is the number of used physical memories in all virtual memories when the multiplexer cost is minimized.

Therefore, when the given number of physical memories is less than the minimum required amount, the problem does not have a solution, and if the given number is larger than or equal to the maximum consumption, we can easily create the solution as discussed above (working on virtual memories independently). However, when we do not have enough number of physical memories to generate the minimum overall multiplexer cost, we cannot work on the virtual memories independently, and this is the only added complexity in this section.

In this case coming up with the minimum leftover solution does not change. However, finding the minimum multiplexer cost solution needs some extra effort. We have to use all the given physical memories to reduce the multiplexer cost as much as possible. In order to do that, we will divide all the virtual memories to top and bottom areas, and fill all top areas by employing the method in the previous section. To fill the bottom areas of the virtual memories we have to create all combinations of physical memory blocks for all the virtual memories. The combinations for each virtual memory are produced from its own blocks, and the blocks are generated with the same method we used in the previous section for each virtual memory.

The pseudo code for generating the minimum multiplexer cost binding in the case of multiple virtual memories and one type of physical memories is presented in algorithm 3. In the first 4 lines of the algorithm we perform the procedures of the

previous algorithm on each virtual memory individually. Also, in line 5 the maximum number of required physical memories is calculated for each virtual memory, and the overall number of required physical memories is stored in " $PM_{max\_required}$ ". In the case of having enough number of physical memories we work on virtual memories individually, and use the method that we use in the case of a single virtual memory for each virtual memory (lines 6 to 10).