## An Integrated Power Electronic System for Off-Grid Rural Applications

#### AN INTEGRATED POWER ELECTRONIC SYSTEM FOR OFF-GRID RURAL APPLICATIONS

BY

#### DAVID SCHUMACHER, B.Sc.

A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

AND THE SCHOOL OF GRADUATE STUDIES

OF MCMASTER UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

© Copyright by David Schumacher, September 2017

All Rights Reserved

| Master of Applied Science (2017)    | McMaster University       |

|-------------------------------------|---------------------------|

| (Electrical & Computer Engineering) | Hamilton, Ontario, Canada |

| TITLE:      | An Integrated Power Electronic System for Off-Grid Ru- |

|-------------|--------------------------------------------------------|

|             | ral Applications                                       |

|             |                                                        |

| AUTHOR:     | David Schumacher                                       |

|             | B.Sc., (Electrical Engineering)                        |

|             | McMaster University, Hamilton, Ontario, Canada         |

|             |                                                        |

| SUPERVISOR: | Dr. Ali Emadi and Dr. Nigel Schofield                  |

|             |                                                        |

NUMBER OF PAGES: xxii, 216

To my family.

### Abstract

Distributed energy is an attractive alternative to typical centralized energy sources specifically for remote locations not accessible to the electricity grid. With the continued advancement into new renewable technologies like solar, wind, fuel cell etc., off-grid standalone systems are becoming more attractive and even competing on a cost basis for rural locations. Along with the environmental and sustainable movement, these technologies are only going to get more and more popular as time goes on. Power electronic converters are also advancing which will help the shift in electricity options. Creating innovative power electronic systems will be important when moving toward smaller, more efficient and higher power density solutions.

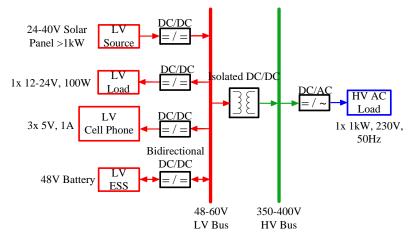

As such, this thesis will aim to design and create an integrated power electronic system for an off-grid standalone solar application designed for remote rural locations with no access to electricity, or in locations which could benefit from such a system. It is designed for a DC input source from 24V-40V, such as a solar panel, and can operate four different loads; one 12V-24V 100 W DC load, charge a 48V battery, run three 5V cell phone charger outputs and run one 230V, 50Hz, 1 kW AC load. A boost converter, buck converter, phase shifted full bridge isolated DC-DC converter and a single phase inverter are implemented in the integrated system to achieve these outputs. A comparison of similar products on the market are presented and compared with the proposed design by showing the product specifications, advantages and disadvantages of each.

A discussion of each converter in the system is presented and will include operation, design and component selection. An in-depth design process for the inductor within the boost converter is presented and will cover core, winding design and an optimization algorithm using the Genetic Algorithm (GA) is used to compare different ferrite based C-C shaped inductors. More specifically, the core material selected is Ferroxcube 3C97 and the inductor comparisons are between different Litz bundled windings from New England Wire Technologies and a customized rectangular winding. The GA optimizes around the lowest volume by comparing the different inductor designs using the different Litz winding constructions and the custom rectangular winding constriction. The rectangular winding achieves the lowest volume and will be compared with a three phase interleaved boost design implementing a CoilCraft inductor. The buck converter is the simplest converter and is designed using the traditional methods in literature. An in-depth design process for the phase shifted full bridge converter is also done wherein the zero voltage switching (ZVS) is achieved. The DC-AC inverter is the last converter designed within the integrated system and covers input capacitor sizing, and output filter design. There are specific distributed energy standards that must be followed when connecting loads to the system and so the purpose of the filter is to filter out the voltage harmonics. The control techniques for each converter is also discussed and shown to operate in both simulation and in experimentally.

The losses within the system are discussed and the required equations are defined so that a comparison between the experimental and simulated system can be made. Indepth discussion on gate driver mosfet turn-on and turn-off operation is discussed, which is required for determining the switching losses. MATLAB/Simulink models are made for both the system level simulation in which the control and operation of the entire system is shown over three seconds, and also for individual converter simulations which model the losses to determine the converter efficiency over varying loads. These individual simulations are compared to the experimental tests to show the modeling accuracy. For the system level control, different loading powers and voltages are applied to see how the system reacts to real life expected changes that system would normally see.

A prototype of the integrated system is designed, manufactured and tested to verify correct operation of each converter within the system and to compare the estimated losses. A few challenges occured during the prototyping which is discussed in more detail in the following chapters, however, each converter will be tested at their full load conditions.

#### Acknowledgements

I would like to express my deep gratitude and appreciation to my supervisors Dr. Ali Emadi and Dr. Nigel Schofield, their attitude and mentality are valuable to me, and all students under their supervision. I have learned a great deal from the opportunities they have provided from my time at McMaster and McMaster Automotive Resource Centre (MARC).

I would like to thank Dr. Berker Bilgin, Dr. Pierre Magne, and Dr. Omid Beik for their support and encouragement as a young engineer. With their help and guidance, I gained tremendous experience in engineering and writing.

I want to thank Deqiang Wang for helping me test my phase shifted full bridge converter and inverter. Without his help, I doubt I would have achieved as much as I have. And all the other students at MARC who have assisted me when I required it and for being such a great team to work with.

Finally, I would like to thank my family and friends for their love and support. Without which I could not have reached this far.

This research was undertaken, in part, thanks to funding from the Canada Excellence Research Chairs Program. The author also gratefully acknowledges Powersys Solutions for their support with JMAG software in this research.

## Notation and abbreviations

- CCM Continuous Conduction Mode

- PSFB Phase shifted full bridge converter

- GA Genetic Algorithm

- DC direct current AC alternating current

- MPPT max power point tracking

- ESS energy storage system

- HV high voltage

- LV low voltage

- iGSE improved generalized Steinmetz equation

- $i^2$ GSE- improved-improved generalized Steinmetz equation

- MTL mean turn length

- AP area product method

- Kp core geometry method

- E core width

- D core depth

- WAW window width

- WAH window height

- Lg space air gap space

- NG number of air gaps

- Pos wire row position

- H wire height

- W wire width

## Contents

| A        | ostra          | $\mathbf{ct}$                                               | iv   |

|----------|----------------|-------------------------------------------------------------|------|

| A        | cknov          | wledgements                                                 | vii  |

| N        | otati          | on and abbreviations                                        | viii |

| 1        | Intr           | oduction                                                    | 1    |

|          | 1.1            | Background and Motivation                                   | 1    |

|          | 1.2            | Thesis Outline                                              | 7    |

| <b>2</b> | Rev            | iew of Off-Grid System Products and Past Applications       | 11   |

|          | 2.1            | Portable Applications                                       | 12   |

|          | 2.2            | Stationary Applications                                     | 14   |

| 3        | Pro            | posed Integrated Power Electronic System for Off-Grid Rural |      |

|          | App            | olications                                                  | 18   |

|          | 3.1            | System Topology Comparison                                  | 18   |

|          | 3.2            | Proposed Integrated Converter                               | 23   |

| 4        | $\mathbf{Des}$ | ign of Integrated Power Electronic System                   | 30   |

| 4.1 | Boost  | Converter                                    | 30 |

|-----|--------|----------------------------------------------|----|

|     | 4.1.1  | Boost Converter Overview                     | 30 |

|     | 4.1.2  | Design of Boost Converter                    | 34 |

|     | 4.1.3  | Inductor Design                              | 35 |

|     |        | 4.1.3.1 Core Design                          | 37 |

|     |        | 4.1.3.2 Winding Design                       | 43 |

|     |        | 4.1.3.3 GA Implementation                    | 48 |

|     |        | 4.1.3.3.1 GA Parameters                      | 49 |

|     |        | 4.1.3.3.2 GA Constraints                     | 51 |

|     |        | 4.1.3.4 Results                              | 52 |

|     | 4.1.4  | Boost Component Selection                    | 59 |

| 4.2 | Buck   | Converter                                    | 62 |

|     | 4.2.1  | Buck Converter Overview                      | 62 |

|     | 4.2.2  | Design of Buck Converter                     | 64 |

|     | 4.2.3  | Buck Component Selection                     | 65 |

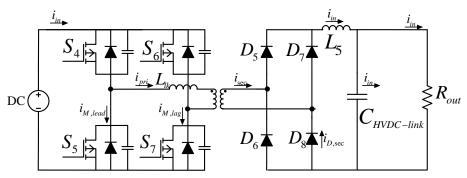

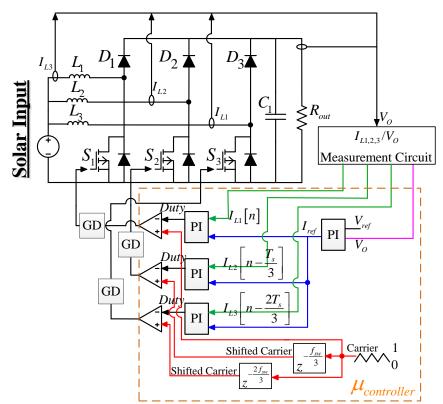

| 4.3 | Phase  | -Shifted Full-Bridge Isolated Converter      | 66 |

|     | 4.3.1  | Phase-Shifted Full-Bridge Converter Overview | 66 |

|     | 4.3.2  | Design of PSFB Converter                     | 75 |

|     | 4.3.3  | Component Selection                          | 82 |

| 4.4 | Invert | er                                           | 85 |

|     | 4.4.1  | Inverter Overview                            | 85 |

|     | 4.4.2  | Design of Inverter                           | 86 |

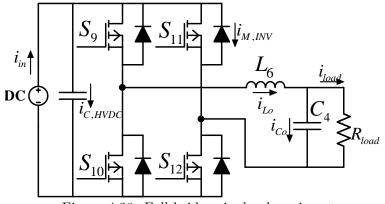

|     |        | 4.4.2.1 Input Capacitor                      | 86 |

|     |        | 4.4.2.2 Output Filter                        | 88 |

|          |                   | 4.4.3                                      | Component Selection                                      | 91                                                                                                                              |

|----------|-------------------|--------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| <b>5</b> | Cor               | ntrol a                                    | nd Hardware Implementation                               | 95                                                                                                                              |

|          | 5.1               | Imple                                      | mented Control Technique                                 | 95                                                                                                                              |

|          |                   | 5.1.1                                      | Boost/Buck Converter Control                             | 97                                                                                                                              |

|          |                   | 5.1.2                                      | PSFB Converter Control                                   | 100                                                                                                                             |

|          |                   | 5.1.3                                      | Single Phase Inverter Control                            | 103                                                                                                                             |

|          | 5.2               | Hardv                                      | vare                                                     | 105                                                                                                                             |

|          |                   | 5.2.1                                      | Gate Driver                                              | 105                                                                                                                             |

|          |                   | 5.2.2                                      | DSP                                                      | 106                                                                                                                             |

|          |                   | 5.2.3                                      | Current and Voltage Measurement                          | 106                                                                                                                             |

|          |                   | 5.2.4                                      | PCB                                                      | 108                                                                                                                             |

| C        | <b>C</b>          | . <b>"</b>                                 |                                                          | 110                                                                                                                             |

| 6        | Sys               | tem M                                      | lodeling, Simulation, Analysis and Efficiency Assessment | 112                                                                                                                             |

| 0        | <b>5ys</b><br>6.1 |                                            | Equations of System Components                           | 112<br>113                                                                                                                      |

| 0        | ÷                 |                                            |                                                          |                                                                                                                                 |

| 0        | ÷                 | Loss I                                     | Equations of System Components                           | 113                                                                                                                             |

| 0        | ÷                 | Loss I<br>6.1.1                            | Equations of System Components                           | 113<br>113                                                                                                                      |

| 0        | ÷                 | Loss H<br>6.1.1<br>6.1.2                   | Equations of System Components                           | 113<br>113<br>115                                                                                                               |

| 0        | ÷                 | Loss H<br>6.1.1<br>6.1.2<br>6.1.3          | Equations of System Components                           | <ol> <li>113</li> <li>113</li> <li>115</li> <li>120</li> </ol>                                                                  |

| 0        | ÷                 | Loss H<br>6.1.1<br>6.1.2<br>6.1.3          | Equations of System Components                           | <ol> <li>113</li> <li>113</li> <li>115</li> <li>120</li> <li>122</li> </ol>                                                     |

| 0        | ÷                 | Loss H<br>6.1.1<br>6.1.2<br>6.1.3          | Equations of System Components                           | <ol> <li>113</li> <li>113</li> <li>115</li> <li>120</li> <li>122</li> <li>122</li> </ol>                                        |

| 0        | ÷                 | Loss H<br>6.1.1<br>6.1.2<br>6.1.3          | Equations of System Components                           | <ol> <li>113</li> <li>113</li> <li>115</li> <li>120</li> <li>122</li> <li>122</li> <li>122</li> <li>127</li> </ol>              |

| 0        | ÷                 | Loss H<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4 | Equations of System Components                           | <ol> <li>113</li> <li>113</li> <li>115</li> <li>120</li> <li>122</li> <li>122</li> <li>122</li> <li>127</li> <li>129</li> </ol> |

|              |     | 6.2.2  | Boost Converter Efficiency Simulation  | 147 |

|--------------|-----|--------|----------------------------------------|-----|

|              |     | 6.2.3  | Buck Converter Efficiency Simulation   | 148 |

|              |     | 6.2.4  | PSFB Efficiency Simulation             | 149 |

|              |     | 6.2.5  | Inverter Efficiency Simulation         | 150 |

|              |     |        |                                        |     |

| 7            | Exp | erime  | ntal Results and Simulation Comparison | 152 |

|              | 7.1 | Boost  | Converter Experimental Results         | 152 |

|              | 7.2 | Buck   | Converter Experimental Results         | 157 |

|              | 7.3 | Cell P | Phone Converter Experimental Results   | 160 |

|              | 7.4 | PSFB   | Converter Experimental Results         | 161 |

|              | 7.5 | Invert | er Experimental Results                | 169 |

| 8            | Cor | clusio | ns and Future Work                     | 178 |

| $\mathbf{A}$ | A1. | GA N   | ATLAB Code                             | 184 |

## List of Figures

| 1.1 | Impacts of Electricity Consumption for Households Reported in Liter-     |    |

|-----|--------------------------------------------------------------------------|----|

|     | ature [2]                                                                | 2  |

| 1.2 | World population without access to electricity by region (millions) [6]. | 2  |

| 1.3 | Geographical distribution of technologies with electricity costs lower   |    |

|     | than 25 c per kWh and conservative assumption on grid extension [11].    | 5  |

| 1.4 | Geographical distribution of technologies with electricity costs lower   |    |

|     | than 30c per kWh and conservative assumption on grid extension [11].     | 6  |

| 1.5 | Economic Comparison of Diesel Versus PV [11]                             | 6  |

| 2.1 | Smart village universal charge controller [27]                           | 16 |

| 2.2 | Sunblazer II unit [29]                                                   | 16 |

| 3.1 | Single bus topologies (a) single AC bus (b) single HV DC bus (c) single  |    |

|     | LV DC bus                                                                | 20 |

| 3.2 | Double bus topologies (a) LVDC and HVDC bus (b) LVDC and HVAC            |    |

|     | bus (c) HVDC and HVAC bus.                                               | 21 |

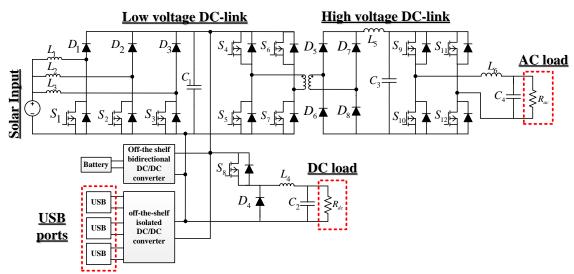

| 3.3 | Proposed standalone off-grid integrated power converter system topology. | 23 |

| 3.4 | Proposed standalone off-grid integrated power converter system for       |    |

|     | rural applications                                                       | 28 |

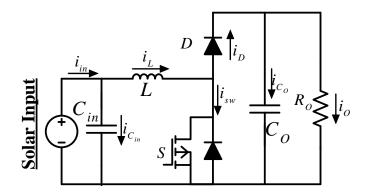

| 4.1 | Boost converter circuit.                                                 | 31 |

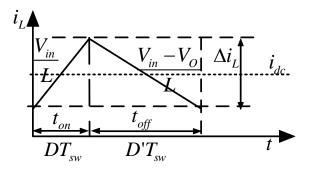

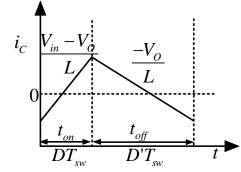

| 4.2  | Boost converter inductor current waveform [40],[45]                            | 31 |

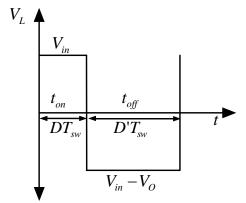

|------|--------------------------------------------------------------------------------|----|

| 4.3  | Boost converter inductor voltage waveform [40],[45]                            | 32 |

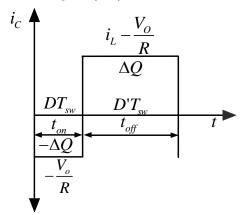

| 4.4  | Output capacitor current waveform [40],[45]                                    | 33 |

| 4.5  | Input capacitor current waveform [40],[45]                                     | 33 |

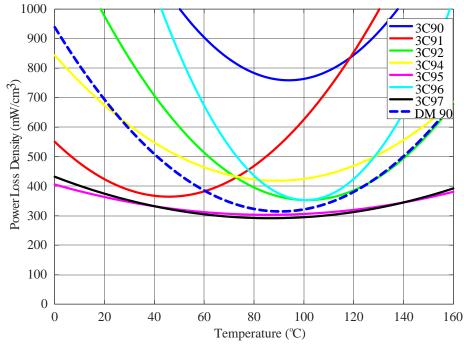

| 4.6  | Core loss material comparison at 0.2T 100kHz                                   | 39 |

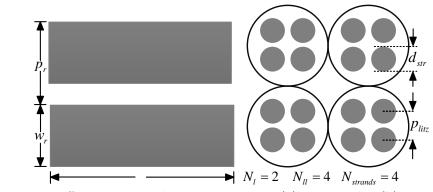

| 4.7  | Difference in winding constructions (a) rectangular (b) Litz winding           | 46 |

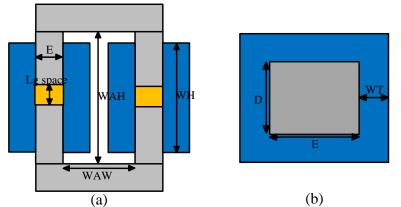

| 4.8  | C-C core inductor (a) Cross sectional view (b) top view of single column.      | 51 |

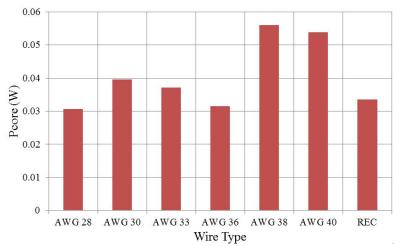

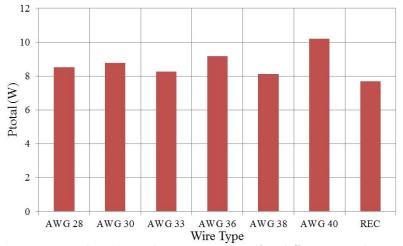

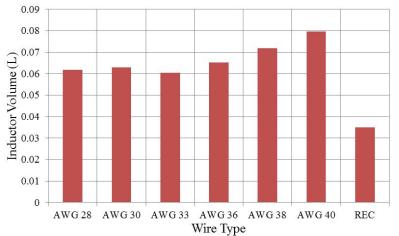

| 4.9  | Core loss comparison for different winding types                               | 53 |

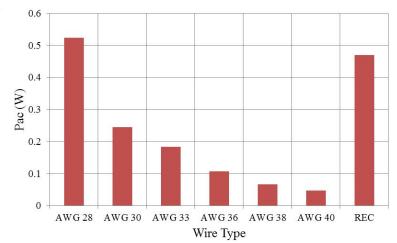

| 4.10 | AC winding loss comparison for different winding types                         | 54 |

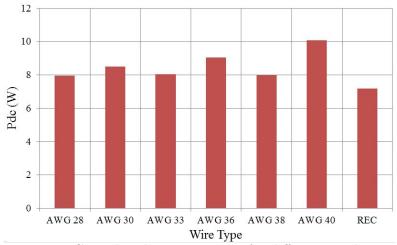

| 4.11 | DC winding loss comparison for different winding types                         | 54 |

| 4.12 | Total inductor loss comparison for different winding types                     | 54 |

| 4.13 | Total inductor volume comparison for different winding types                   | 56 |

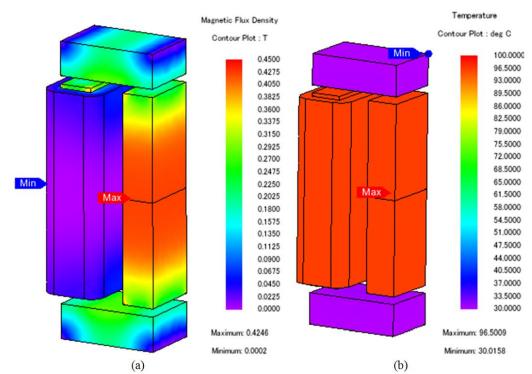

| 4.14 | JMAG simulation results (a) magnetic simulation (b) thermal simulation.        | 58 |

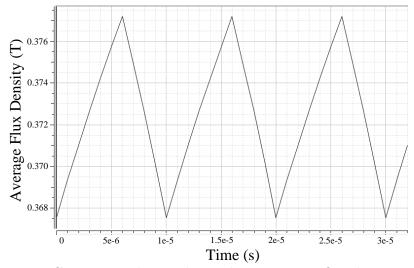

| 4.15 | 3C97 rectangular winding inductor average flux density vs time                 | 58 |

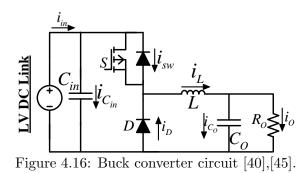

| 4.16 | Buck converter circuit [40],[45]                                               | 62 |

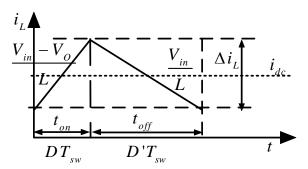

| 4.17 | Buck converter inductor current waveform [40],[45]                             | 62 |

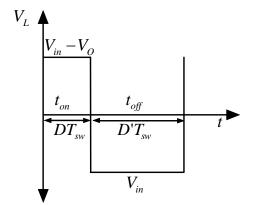

| 4.18 | Buck converter inductor voltage waveform [40],[45]                             | 63 |

| 4.19 | Phase shifted full bridge converter circuit.                                   | 67 |

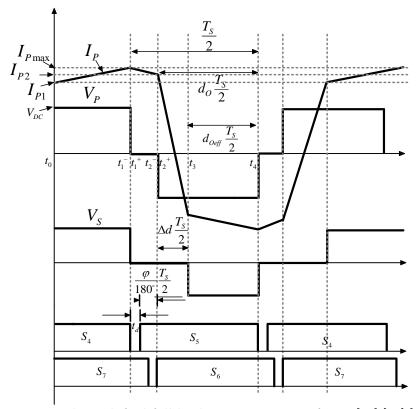

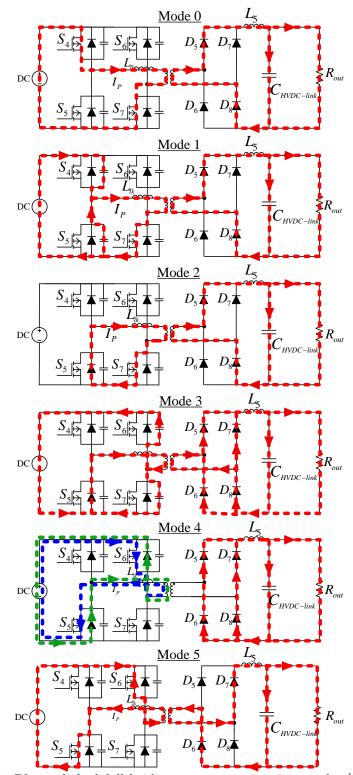

| 4.20 | Phase shifted full bridge converter waveforms [56],[62],[63]                   | 67 |

| 4.21 | Phase shifted full bridge converter operation modes $[56], [62], [63], \ldots$ | 68 |

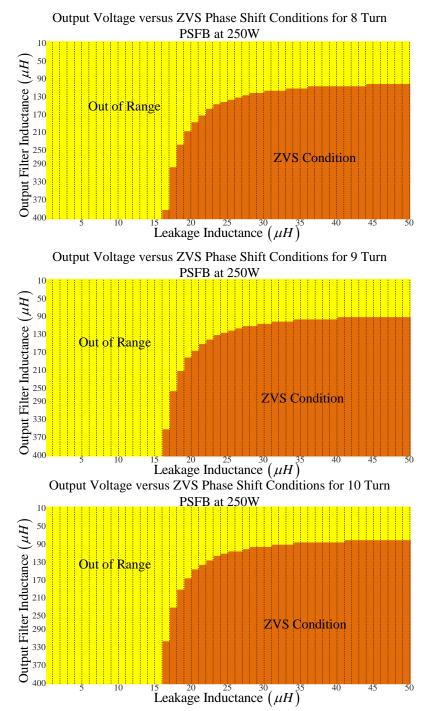

| 4.22 | Comparison between output voltage and ZVS phase shift constraints              |    |

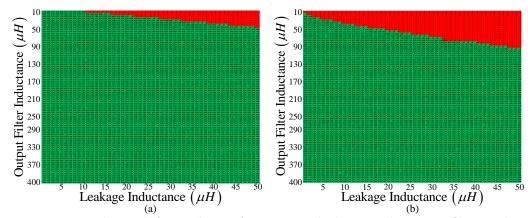

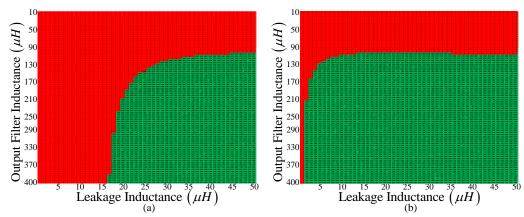

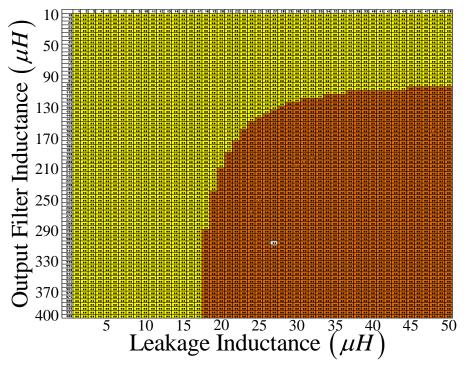

|      | for different $L_{lk}$ , $L_O$ and number of turns for 250W load               | 78 |

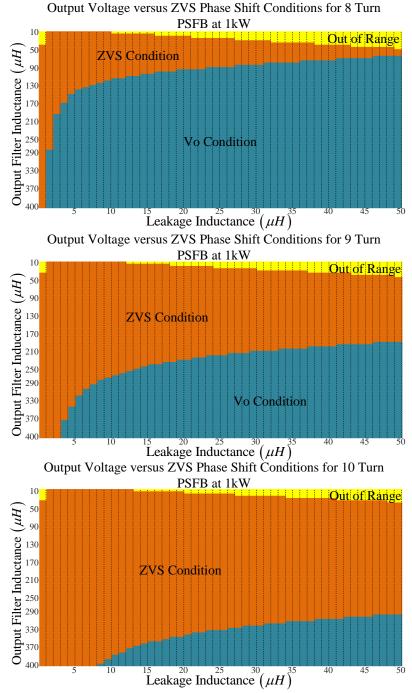

| 4.23 | Comparison between output voltage and ZVS phase shift constraints              |    |

|      | for different $L_{lk}$ , $L_O$ and number of turns for 1 kW load               | 79 |

| 4.24                                                                                                               | Vo phase shift condition for varying leakage and output filter induc-                                                                                                                                                                                                                                                                                               |                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                    | tance values at different dead-time values (a) normal dead-time calcu-                                                                                                                                                                                                                                                                                              |                                                                                                                                           |

|                                                                                                                    | lation via (4.55) (b) 50ns extra dead-time                                                                                                                                                                                                                                                                                                                          | 80                                                                                                                                        |

| 4.25                                                                                                               | ZVS phase shift condition for varying leakage and output filter in-                                                                                                                                                                                                                                                                                                 |                                                                                                                                           |

|                                                                                                                    | ductance values at different dead-time values (a) normal dead-time                                                                                                                                                                                                                                                                                                  |                                                                                                                                           |

|                                                                                                                    | calculation via (4.55) (b) 50ns extra dead-time                                                                                                                                                                                                                                                                                                                     | 80                                                                                                                                        |

| 4.26                                                                                                               | ZVS vs output voltage conditions for 8 turn converter.                                                                                                                                                                                                                                                                                                              | 81                                                                                                                                        |

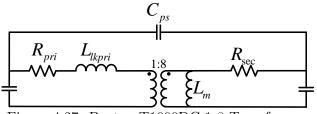

| 4.27                                                                                                               | Payton T1000DC-1-8 Transformer.                                                                                                                                                                                                                                                                                                                                     | 84                                                                                                                                        |

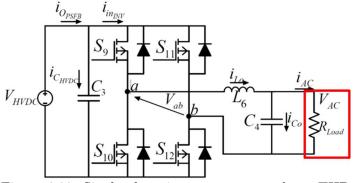

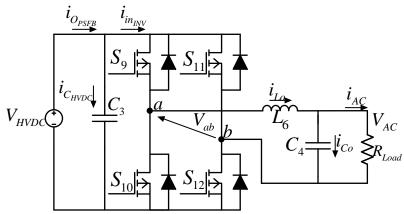

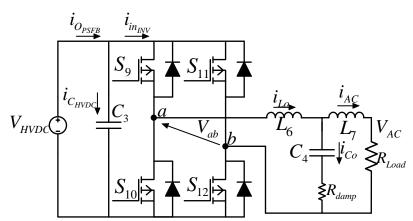

| 4.28                                                                                                               | Full bridge single phase inverter                                                                                                                                                                                                                                                                                                                                   | 86                                                                                                                                        |

| 4.29                                                                                                               | HVDC link voltage waveform.                                                                                                                                                                                                                                                                                                                                         | 87                                                                                                                                        |

| 4.30                                                                                                               | Compatibility levels for individual harmonic voltage in low-voltage net-                                                                                                                                                                                                                                                                                            |                                                                                                                                           |

|                                                                                                                    | works (rms values as a percentage of rms values of the fundamentals                                                                                                                                                                                                                                                                                                 |                                                                                                                                           |

|                                                                                                                    | component [69]                                                                                                                                                                                                                                                                                                                                                      | 89                                                                                                                                        |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                     | 05                                                                                                                                        |

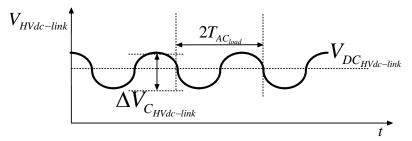

| 5.1                                                                                                                | Average mode current control for Buck converter                                                                                                                                                                                                                                                                                                                     | 97                                                                                                                                        |

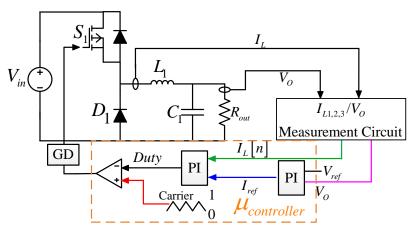

| 5.1<br>5.2                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                           |

|                                                                                                                    | Average mode current control for Buck converter                                                                                                                                                                                                                                                                                                                     | 97                                                                                                                                        |

| 5.2                                                                                                                | Average mode current control for Buck converter                                                                                                                                                                                                                                                                                                                     | 97<br>98                                                                                                                                  |

| $5.2 \\ 5.3$                                                                                                       | Average mode current control for Buck converter                                                                                                                                                                                                                                                                                                                     | 97<br>98<br>99                                                                                                                            |

| 5.2<br>5.3<br>5.4                                                                                                  | Average mode current control for Buck converter                                                                                                                                                                                                                                                                                                                     | 97<br>98<br>99<br>100                                                                                                                     |

| 5.2<br>5.3<br>5.4<br>5.5                                                                                           | Average mode current control for Buck converter                                                                                                                                                                                                                                                                                                                     | 97<br>98<br>99<br>100<br>102                                                                                                              |

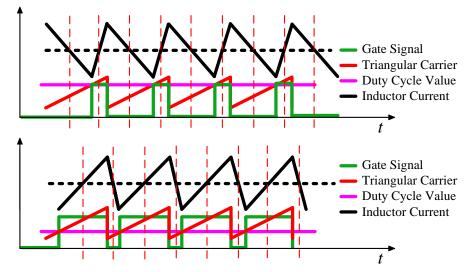

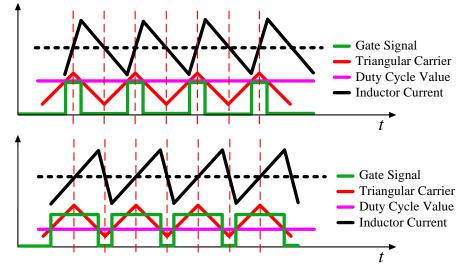

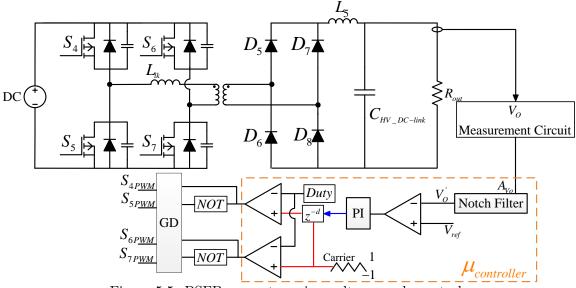

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ol>                                        | Average mode current control for Buck converter.Average mode current control for 3 phase interleaved boost converter.saw-tooth carrier PWM generation.triangular carrier PWM generation.PSFB converter using voltage mode control.PSFB PWM generation 50 percent phase shift.                                                                                       | <ul> <li>97</li> <li>98</li> <li>99</li> <li>100</li> <li>102</li> <li>102</li> </ul>                                                     |

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> </ol>                           | Average mode current control for Buck converter.Average mode current control for 3 phase interleaved boost converter.saw-tooth carrier PWM generation.triangular carrier PWM generation.PSFB converter using voltage mode control.PSFB PWM generation 50 percent phase shift.PSFB PWM generation 25 percent phase shift.                                            | <ul> <li>97</li> <li>98</li> <li>99</li> <li>100</li> <li>102</li> <li>102</li> <li>102</li> <li>102</li> </ul>                           |

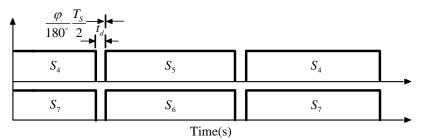

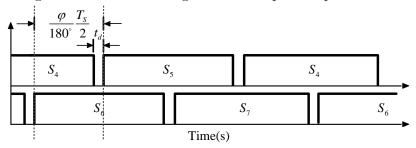

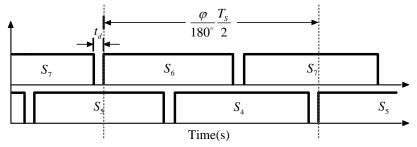

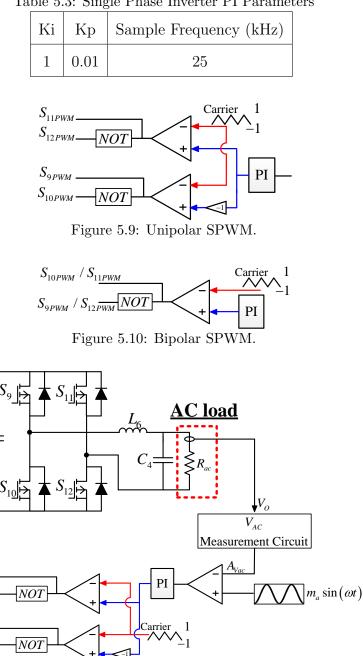

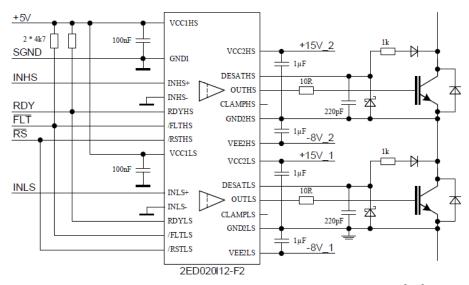

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> </ol> | Average mode current control for Buck converter.Average mode current control for 3 phase interleaved boost converter.saw-tooth carrier PWM generation.triangular carrier PWM generation.PSFB converter using voltage mode control.PSFB PWM generation 50 percent phase shift.PSFB PWM generation 25 percent phase shift.PSFB PWM generation 75 percent phase shift. | <ul> <li>97</li> <li>98</li> <li>99</li> <li>100</li> <li>102</li> <li>102</li> <li>102</li> <li>102</li> <li>102</li> <li>102</li> </ul> |

| 5.12 | Bipolar mode of 2ED020M2-F2 gate driver [89]                           | 105 |

|------|------------------------------------------------------------------------|-----|

| 5.13 | Boost converter phase current measurement circuit                      | 107 |

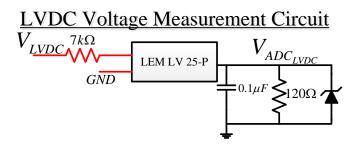

| 5.14 | LVDC voltage measurement circuit                                       | 107 |

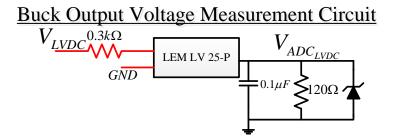

| 5.15 | Buck output voltage measurement circuit.                               | 107 |

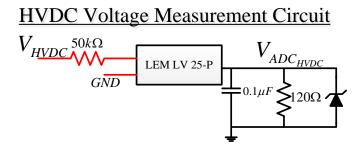

| 5.16 | HVDC link voltage measurement circuit.                                 | 108 |

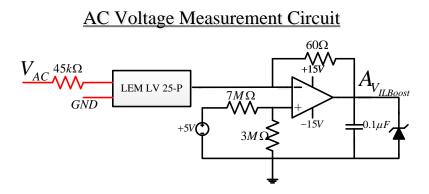

| 5.17 | AC load voltage measurement circuit                                    | 108 |

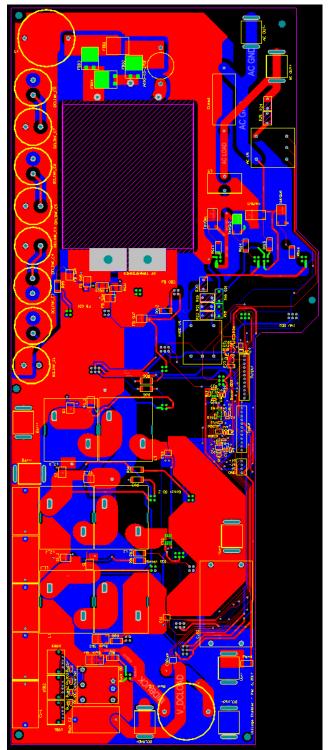

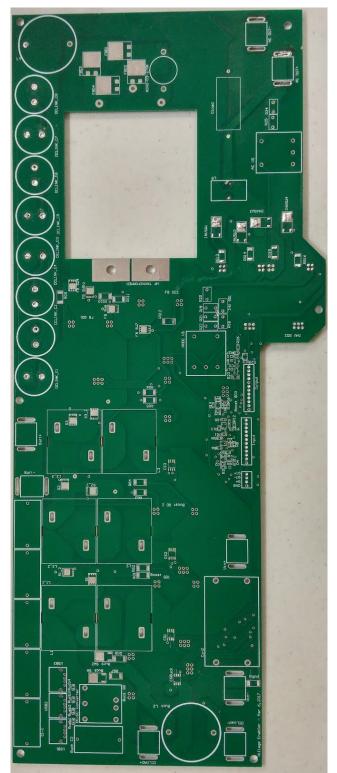

| 5.18 | Altium PCB layout.                                                     | 109 |

| 5.19 | Manufactured PCB                                                       | 110 |

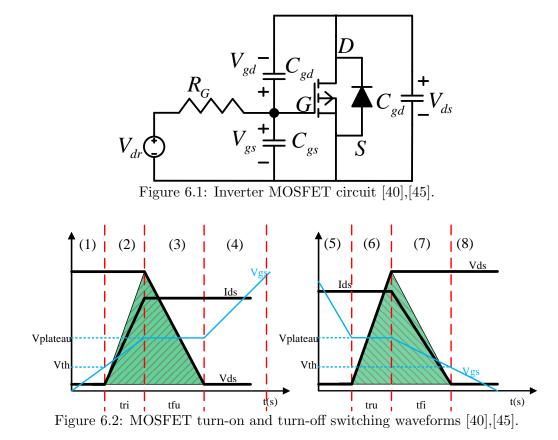

| 6.1  | Inverter MOSFET circuit [40],[45]                                      | 114 |

| 6.2  | MOSFET turn-on and turn-off switching waveforms [40],[45]              | 114 |

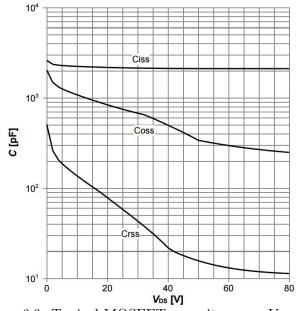

| 6.3  | Typical MOSFET capacitance vs $V_{DS}$ [58]                            | 117 |

| 6.4  | Static characteristics for IPP083N10N5 [58]                            | 119 |

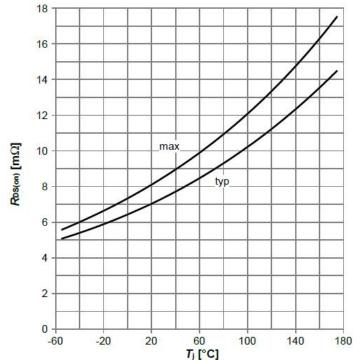

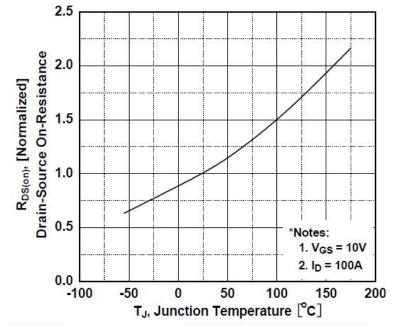

| 6.5  | $R_{DS(on)}$ vs junction temperature for IPP083N10N5 [58]              | 120 |

| 6.6  | Reverse recovery charge for IPP083N10N5 [58]                           | 121 |

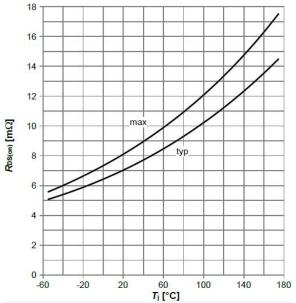

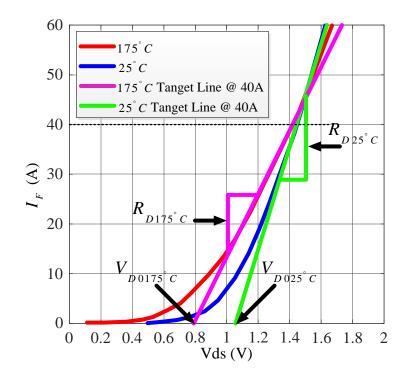

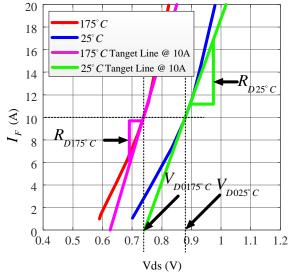

| 6.7  | Forward characteristics of reverse diode of IPP083N10N5 [58]           | 122 |

| 6.8  | $R_{ON}$ vs junction temperature for IPP083N10N5 [58]                  | 123 |

| 6.9  | Forward characteristics of IDW30E65D1 [59]                             | 124 |

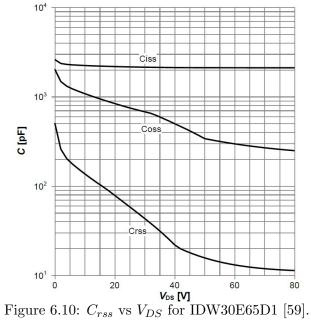

| 6.10 | $C_{rss}$ vs $V_{DS}$ for IDW30E65D1 [59]                              | 125 |

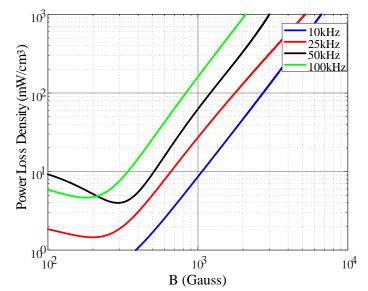

| 6.11 | Power loss density vs flux density for 1140-101K-RC                    | 129 |

| 6.12 | normalized $R_{DS(on)}$ vs junction temperature for FDP045N10A [66].   | 130 |

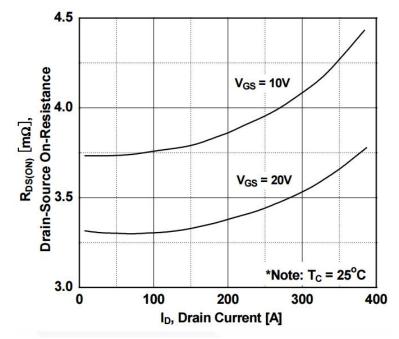

| 6.13 | $R_{DS(on)}$ vs $I_D$ for FDP045N10AF102 [66]                          | 130 |

| 6.14 | Forward characteristics of STP28N65M2 body diode [77]                  | 133 |

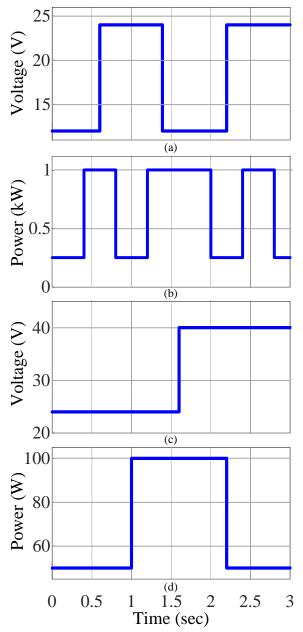

| 6.15 | System simulation control variables (a) buck output voltage (b) output |     |

|      | AC power (c) input boost voltage (d) output buck power                 | 138 |

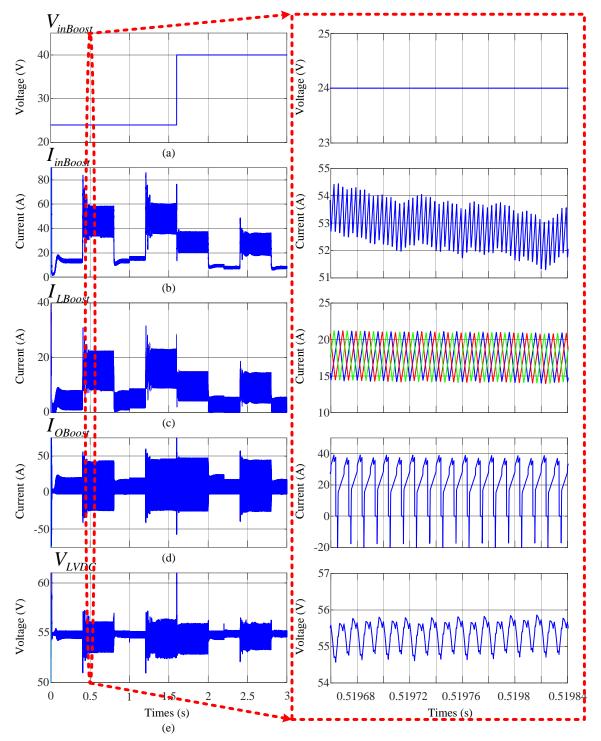

| 6.16 | Boost converter simulation waveforms (a) input voltage (b) input cur-                             |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | rent (d) output current (e) LVDC link voltage                                                     | 139 |

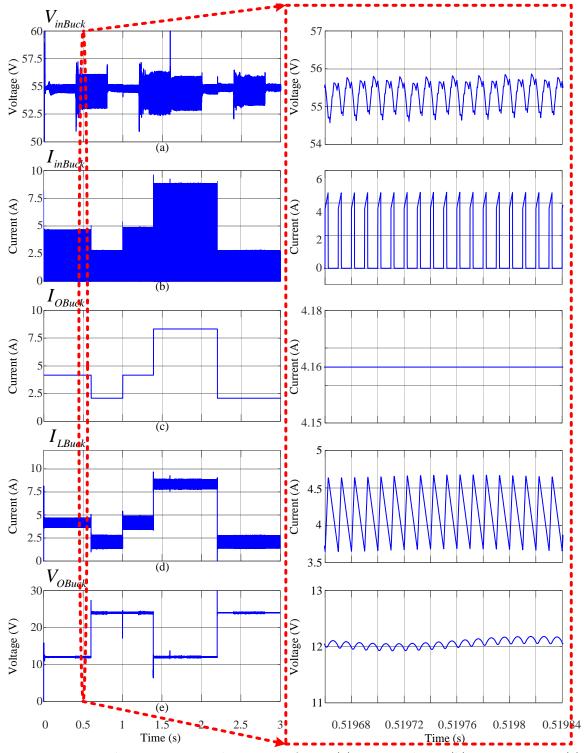

| 6.17 | Buck converter simulation waveforms (a) input voltage (b) input cur-                              |     |

|      | rent (c) output current (d) inductor current (e) LVDC link voltage.                               | 140 |

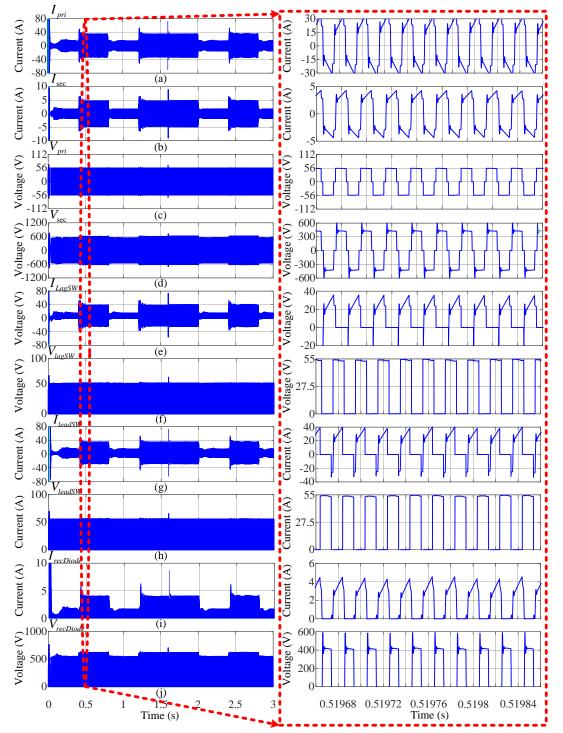

| 6.18 | PSFB converter simulation waveforms (a) primary current (b) sec-                                  |     |

|      | ondary current (c) primary voltage (d) secondary voltage (e) lagging                              |     |

|      | MOSFET current (f) lagging MOSFET voltage (g) leading MOSFET                                      |     |

|      | current (h) leading MOSFET voltage (i) secondary diode current (j)                                |     |

|      | secondary diode voltage.                                                                          | 141 |

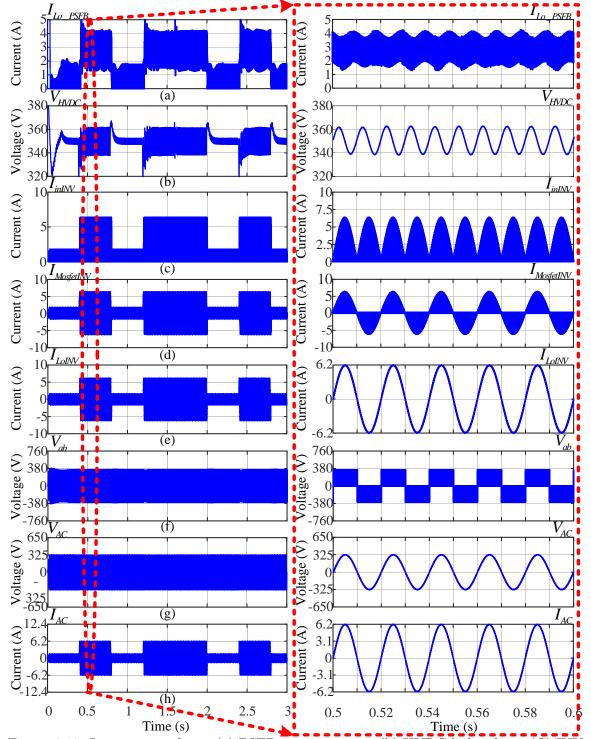

| 6.19 | Inverter waveforms (a) PSFB output current (b) HVDC link voltage                                  |     |

|      | (C) INV input current (d) INV MOSFET current (e) filter inductor                                  |     |

|      | current (f) unfiltered voltage Vab (g) AC voltage (h) AC current. $\ . \ .$                       | 142 |

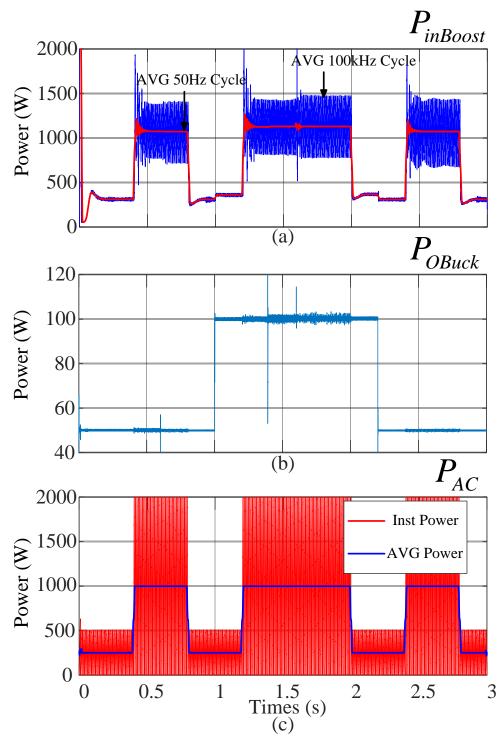

| 6.20 | Input and output power for source and loads within integrated system                              |     |

|      | (a) input boost power (b) buck output power (c) inverter output AC                                |     |

|      | power)                                                                                            | 143 |

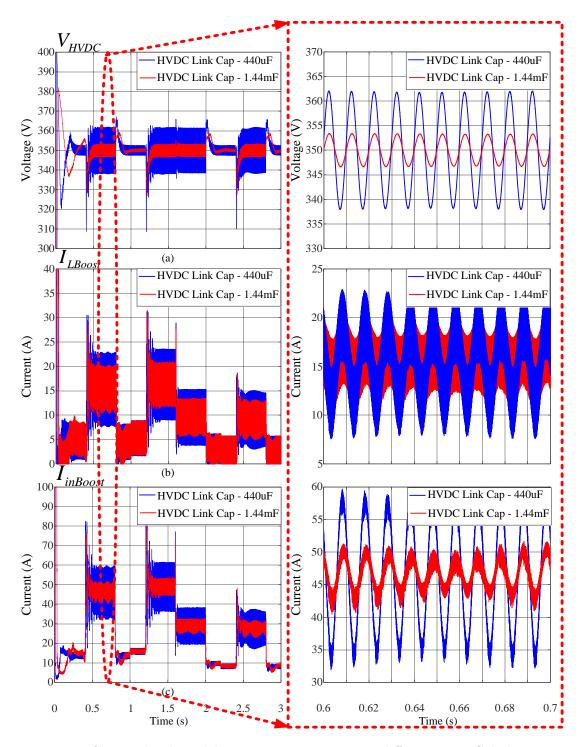

| 6.21 | System level modeling comparison between different HVDC link capac-                               |     |

|      | itor values (a) HVDC bus voltage (b) boost converter phase current                                |     |

|      | (c) boost converter input current. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 144 |

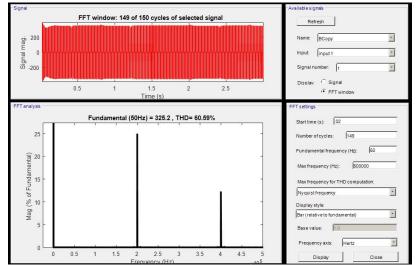

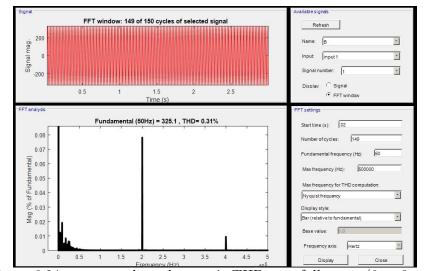

| 6.22 | Single phase inverter output voltage THD                                                          | 146 |

| 6.23 | Non-filtered output voltage harmonic THD over full range (0 to 3 sec).                            | 146 |

| 6.24 | output voltage harmonic THD over full range (0 to 3 sec). $\ldots$ .                              | 146 |

| 6.25 | Boost converter efficiency map over full range for 24V input and 40V $$                           |     |

|      | input                                                                                             | 147 |

| 6.26 | Boost converter efficiency map over 0 to 300W range for 24V and 40V $$                 |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | input                                                                                  | 148 |

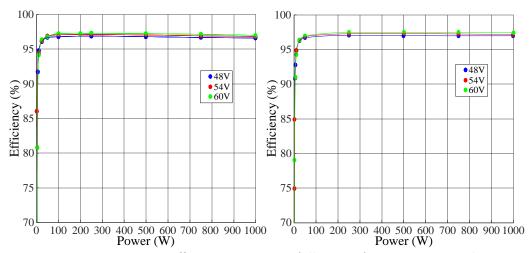

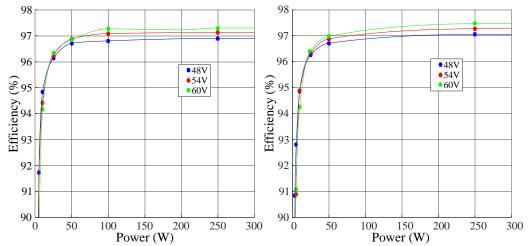

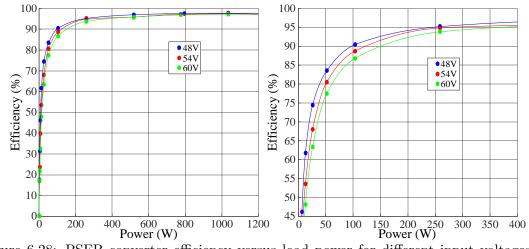

| 6.27 | Buck converter efficiency versus load power over wide load range for                   |     |

|      | different output voltage (a) 12V input (b) 24V input                                   | 149 |

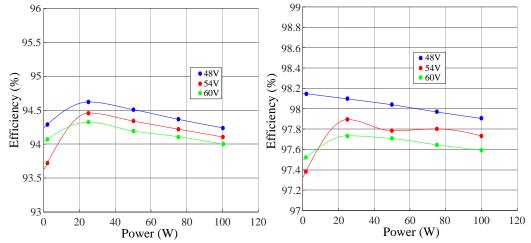

| 6.28 | PSFB converter efficiency versus load power for different input voltages               |     |

|      | (a) complete load range (b) load range from 0 to 400W                                  | 150 |

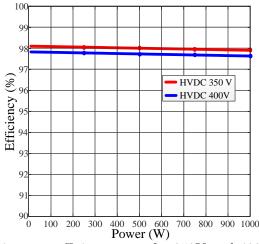

| 6.29 | Simulated inverter efficiency map for $350V$ and $400V$ HVDC input                     |     |

|      | voltage.                                                                               | 150 |

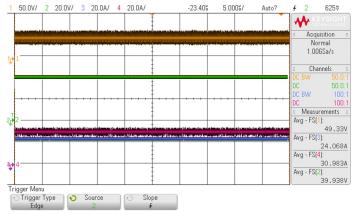

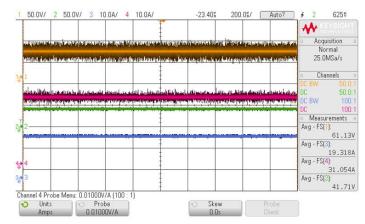

| 7.1  | Boost converter testing 50V out 24V in, Pin 1237.4W, Pout 1179.5W,                     |     |

|      | eff 95.3 percent                                                                       | 153 |

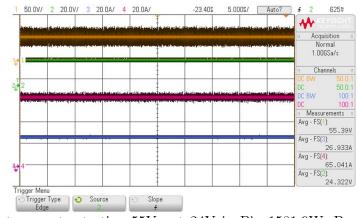

| 7.2  | Boost converter testing 50V out 40V in Pin 1237.4W, Pout 1187.3W,                      |     |

|      | eff 95.95 percent                                                                      | 153 |

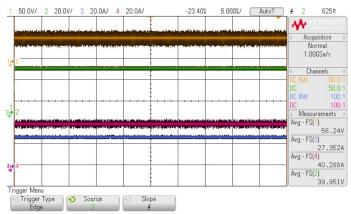

| 7.3  | Boost converter testing 55V out 24V in Pin 1581.9W, Pout 1491.8W,                      |     |

|      | eff 94 percent                                                                         | 154 |

| 7.4  | Boost converter testing 55V out 40V in Pin 1609.55W, Pout 1538.3W,                     |     |

|      | eff 95.57 percent                                                                      | 154 |

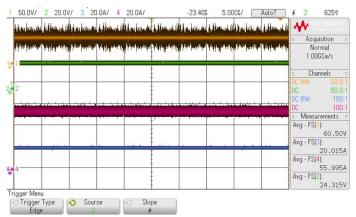

| 7.5  | Boost converter testing $60V$ out $24V$ in Pin 1361.5W, Pout $1210.9W$ ,               |     |

|      | eff 88.97 percent                                                                      | 154 |

| 7.6  | Boost converter testing $60\mathrm{V}$ out $40\mathrm{V}$ in Pin 1295.3W Pout 1180.91W |     |

|      | eff 91.17 percent                                                                      | 155 |

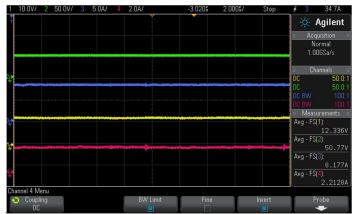

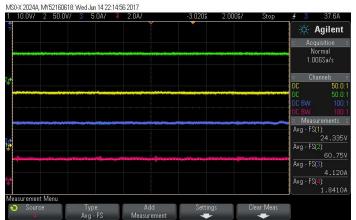

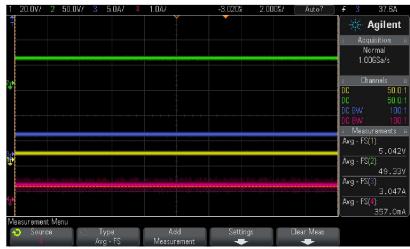

| 7.7  | Buck converter 12V out 50V in Pin 112.34W, Pout 100.9W, eff 89.8 $$                    |     |

|      | percent. input voltage (green), output voltage (yellow), output current                |     |

|      | (blue), input current (red)                                                            | 158 |

| 7.8  | Buck converter 12V out 60V in Pin 109.4W, Pout 98W, eff 89.66 per-                                       |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | cent. input voltage (green), output voltage (yellow), output current                                     |     |

|      | (blue), input current (red)                                                                              | 158 |

| 7.9  | Buck converter 24V out 48V in Pin 108.65W, Pout 99.67W, eff 91.7 $$                                      |     |

|      | percent. input voltage (green), output voltage (yellow), output current                                  |     |

|      | (blue), input current (red)                                                                              | 159 |

| 7.10 | Buck converter 24V out 60V in Pin 111.8W, Pout 100W, eff 89.6 per-                                       |     |

|      | cent. input voltage (green), output voltage (yellow), output current                                     |     |

|      | (blue), input current (red)                                                                              | 159 |

| 7.11 | Cell phone Testing. Pin 17.62W, Pout 15.36W, eff 87.19 percent. Input                                    |     |

|      | voltage (green), output voltage (yellow), output current (blue), input                                   |     |

|      | current (red). $\ldots$ | 161 |

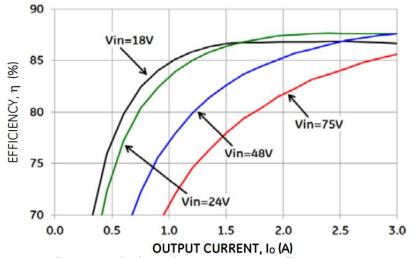

| 7.12 | SHHD003A0A performance charts eff vs output current [97]                                                 | 161 |

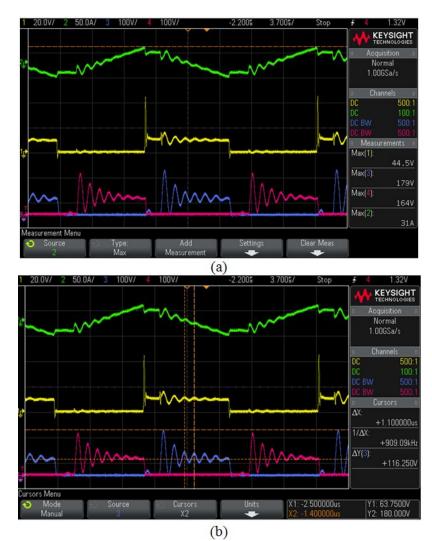

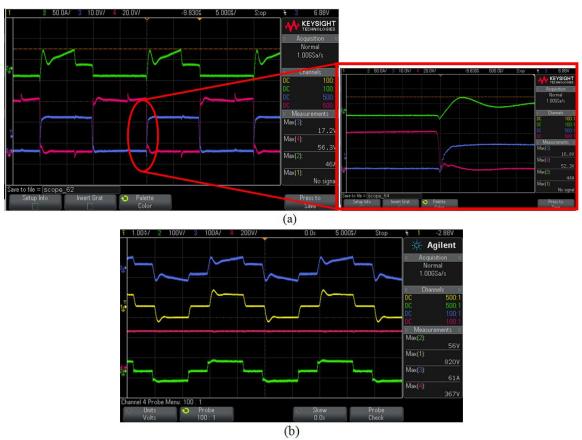

| 7.13 | PSFB converter with 8 turn planer transformer operating at input                                         |     |

|      | voltage of 10 volts and output resistance of 100 ohms. Primary current                                   |     |

|      | (green), primary low side MOSFET (yellow), secondary leg 1 low side                                      |     |

|      | diode (blue), secondary leg 2 low side diode (purple) (a) snap shot                                      |     |

|      | showing voltage and current levels (b) snap shot showing resonance                                       |     |

|      | period                                                                                                   | 163 |

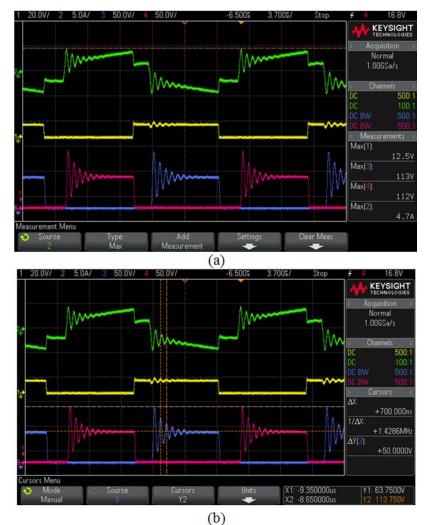

| B converter with 6 turn E core transformer operating at input                                | 7.14 |

|----------------------------------------------------------------------------------------------|------|

| age 10 V and output resistance of 100 ohms. Primary current                                  |      |

| en), primary low side MOSFET (yellow), secondary leg 1 low side                              |      |

| le (blue), secondary leg 2 low side diode (purple) (a) snap shot                             |      |

| ving voltage and current levels (b) snap shot showing resonance                              |      |

| od                                                                                           |      |

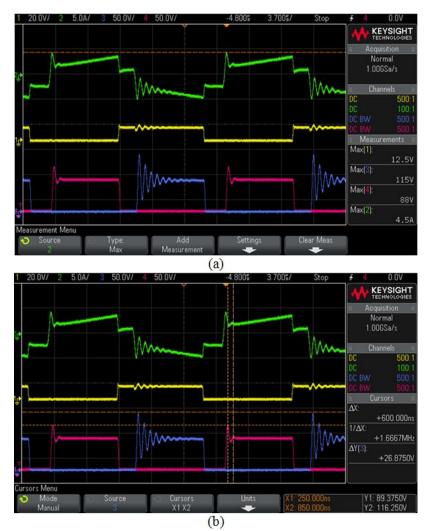

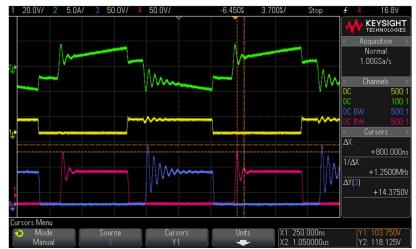

| B Converter. Primary current (green) output voltage (yellow) low                             | 7.15 |

| diode voltage with no snubber(blue) high side diode voltage with                             |      |

| ed snubber across diode (purple) (a) snap shot showing voltage                               |      |

| l (b) snap shot showing resonance period                                                     |      |

| B converter operating at $1.1 \mathrm{kW}$ for input voltage of $45 \mathrm{V}$ . (a) ZVS    | 7.16 |

| agging leg. Switch current (green), Vgs (blue), Vds (red). (b) pri-                          |      |

| y current (blue), secondary voltage (yellow), output voltage (red),                          |      |

| nary voltage (green)                                                                         |      |

| B converter operating at 1.35kW for input voltage of 50V. (a)                                | 7.17 |

| s of lagging leg. Switch current (green), Vgs (blue), Vds (red).                             |      |

| primary current (blue), secondary voltage (yellow), output voltage                           |      |

| ), primary voltage (green)                                                                   |      |

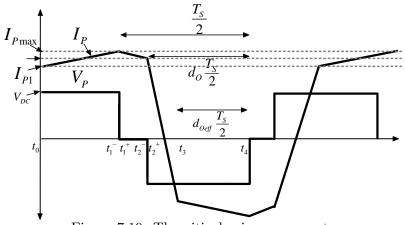

| erimental primary current (green)                                                            | 7.18 |

| oritical primary current                                                                     | 7.19 |

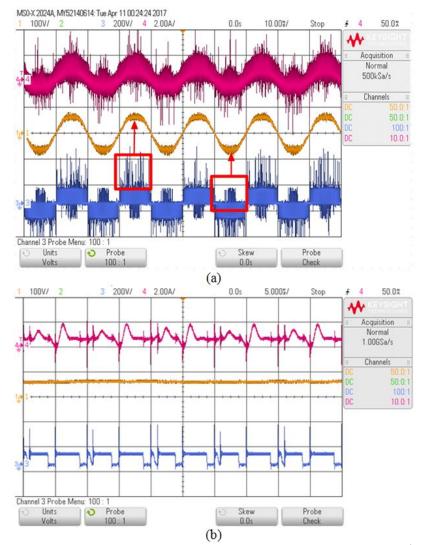

| erter waveforms using integrated PCB. AC load current (red), AC                              | 7.20 |

| voltage (yellow) and unfiltered load voltage $V_{ab}$ (blue) (b) zoomed                      |      |

| ection of (a). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $170$ |      |

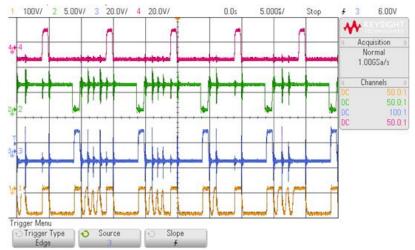

| 7.21 | Gate signal during AC harmonics for each leg. Red and yellow are gate                 |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | signals for leg 1 ( $S_9$ , $S_{10}$ ) while green and blue are gate signal for leg 2 |     |

|      | $(S_{11}, S_{12})$                                                                    | 171 |

| 7.22 | Single phase inverter off-grid inverter using LC filter                               | 171 |

| 7.23 | $10 \rm kW$ single phase grid connected smart home inverter using LCL                 | 172 |

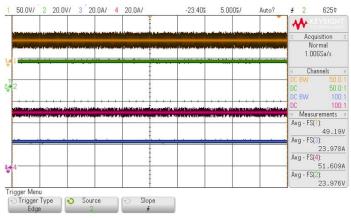

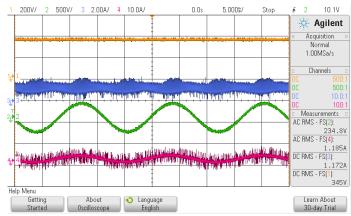

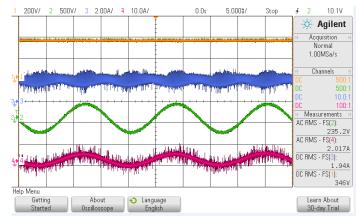

| 7.24 | Single phase inverter experimental testing at 350V HVDC link voltage,                 |     |

|      | 230V AC load voltage and 250W                                                         | 173 |

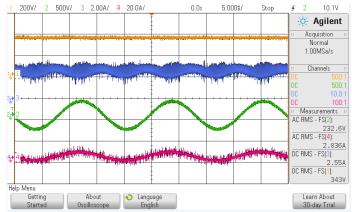

| 7.25 | Single phase inverter experimental testing at 350V HVDC link voltage,                 |     |

|      | 230V AC load voltage and 500W                                                         | 174 |

| 7.26 | Single phase inverter experimental testing at 350V HVDC link voltage,                 |     |

|      | 230V AC load voltage and 750W                                                         | 174 |

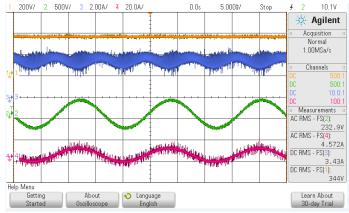

| 7.27 | Single phase inverter experimental testing at 350V HVDC link voltage,                 |     |

|      | 230V AC load voltage and 1kW                                                          | 174 |

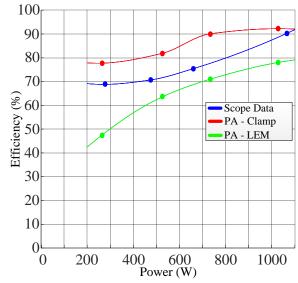

| 7.28 | Comparison in testing methods for single phase inverter                               | 176 |

### Chapter 1

## Introduction

#### 1.1 Background and Motivation

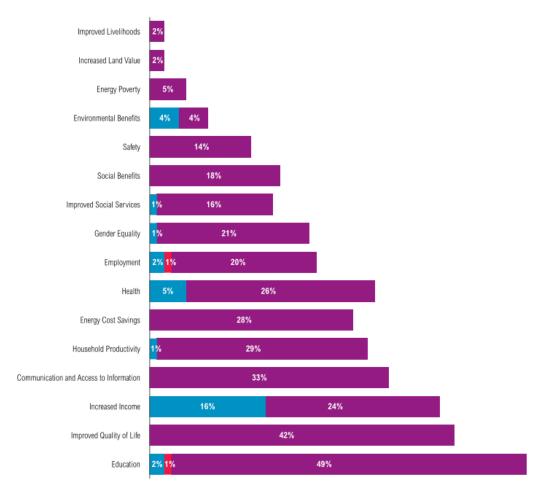

Access to electricity is the main factor limiting the developing world today since it directly influences all aspects of life and living standards [1]. It has been shown that access to electricity allows students the opportunity to have a better education due to longer available hours spent studying at night or in low light conditions [2,3]. It improves health by providing clean water and health services [2,3]. It provides more free time by eliminating the need to gather resources for families since most families use fuels to power their homes [2,3]. This applies even more to women who are typically the ones gathering resources for the family while the men earn the income. Eliminating the time spent gathering resources allows families to have both people earning for the family [2,3]. Also, by improving the reliability of electricity access, businesses can make more electricity- dependent investments [2,3]. In short, all around improved human development is attributed to access to electricity as shown in Fig. 1.1 [2].

No impact

Sometimes has impact

Impact

Figure 1.1: Impacts of Electricity Consumption for Households Reported in Literature [2]

|                         | 2009  |       |                     | 2030  |       |                     |

|-------------------------|-------|-------|---------------------|-------|-------|---------------------|

|                         | Rural | Urban | Share of population | Rural | Urban | Share of population |

| Africa                  | 466   | 121   | 58%                 | 539   | 107   | 42%                 |

| Sub-Saharan Africa      | 465   | 121   | 69%                 | 538   | 107   | 49%                 |

| Developing Asia         | 595   | 81    | 19%                 | 327   | 49    | 9%                  |

| China                   | 8     | 0     | 1%                  | 0     | 0     | 0%                  |

| India                   | 268   | 21    | 25%                 | 145   | 9     | 10%                 |

| Rest of developing Asia | 319   | 60    | 36%                 | 181   | 40    | 16%                 |

| Latin America           | 26    | 4     | 7%                  | 8     | 2     | 2%                  |

| Middle East             | 19    | 2     | 11%                 | 5     | 0     | 2%                  |

| Developing countries    | 1106  | 208   | 25%                 | 879   | 157   | 16%                 |

| Wolrd*                  | 1109  | 208   | 19%                 | 879   | 157   | 12%                 |

Figure 1.2: World population without access to electricity by region (millions) [6].

In Africa alone there are around 600 million people that have no access to electricity with most living in rural locations [4,5]. The world population without access to electricity has been broken down by region in Fig.1.2 [6] and indicates that the number of people without access will decrease over time, while more recent sources estimate that the number of people without access to electricity will continue to increase over the coming years [7,8]. Either way, there will be a significant amount of people who will have no access to electricity so the question becomes, how best can this issue be solved? A renewable option would be the most ideal since it is sustainable and will also help fight climate change. However in reality, the most ideal and desired option is not always the most practical one since cost is usually the driving factor.

Traditionally, rural electrification is powered either by grid connection, distributed energy such as solar, wind or hydro, or through the use of biofuels like wood, oil or diesel with diesel being the most common off-grid option for rural locations [5, 7, 8]. Renewable energy options are gaining in popularity and will continue to do so as time goes on due to the advancement into energy storage technologies, improvements in power electronic converter efficiencies and energy resources like solar and wind. For example, the cost of solar has fallen by 80 percent and could continue to fall another 60 percent by the end of the decade [4,9]. The efficiency of solar is also rising over the past 40 years [10]. 60 percent of the new energy generation is estimated to come from off-grid solutions [8] and there are estimated to be 730 million people that currently rely on biomass for their electricity needs in Africa, as discussed in [4, 5, 7], so the potential output for switching to a renewable alternative, like solar and wind, is vast. It is also important to mention that these locations which are energy deprived have a strong correlation with solar irradiation, meaning that there is a convergence for these locations to move toward a solar option due to the mentioned reasons above. Even though there may be locations in more developed countries which could benefit from an off-grid application, this work is targeting those in developing countries which could benefit the most from electricity access.

Currently, the most common methods to provide rural and off-grid locations with electricity is to either extend the current electricity grid to reach these locations, use oil, wood or other biofuels to run generators, or by implementing distributed energy systems [4, 5, 8, 11]. Extending the grid has a lot of downsides in terms of cost, time and reliability. Rural locations are usually a bit harder to get to and extending the grid to these locations would require new roads, transmission lines, maintenance etc., and even those connected to the grid do not always receive reliable energy due to power outages, and typically the demand of electricity outweighs that supplied by the utility making grid extension a poor choice in some situations [4–12]. Oil and biofuels are the most common option, but again, getting these fuels requires time. Not to mention these options are not sustainable and contribute to global warming. Distributed energy has higher initial costs but it is sustainable, quick to implement, low maintenance, and does not require large transportation costs compared with the other methods [4–13]. These systems also provide reliable electricity by integrating multiple sources together.

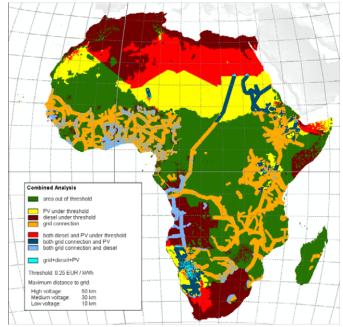

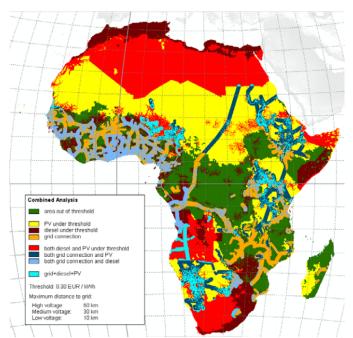

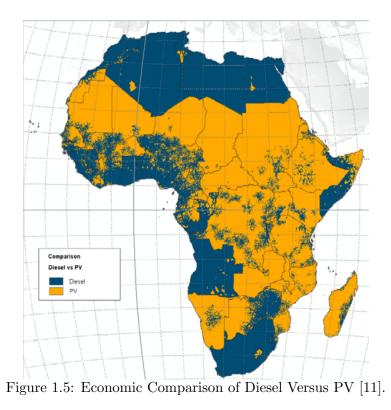

A more in-depth analysis into the cost effectiveness of the available energy options in Africa are discussed in [11]. More specifically, this report comprises a cost comparison between grid extension versus diesel, solar, and other options for locations in Africa. The pricing level and subsidies each country has for each energy option are taken into account during this comparison as discussed in [11]. Fig. 1.3 to Fig. 1.5 show which energy method is most ideal for each location on a cost basis. The colouring indicates the locations where each option is best on a cost basis. Areas in yellow are locations where solar is most ideal, brown shows locations where diesel is most ideal, red shows locations where solar or diesel are best, green indicates locations where solar and diesel are not ideal, orange indicates grid extension being best, and blue shows locations where both grid and either solar or diesel are the most attractive options [11].

Figure 1.3: Geographical distribution of technologies with electricity costs lower than 25 c per kWh and conservative assumption on grid extension [11].

Fig. 1.5 shows the cost comparison for just solar and diesel where solar is in yellow and diesel is in blue. Refer to [11] for a more in-depth explanation, however the point to take from this analysis is that solar has a very large area where it is the most ideal energy source on a cost basis and is a viable alternative to the current energy options in these locations.

Figure 1.4: Geographical distribution of technologies with electricity costs lower than 30c per kWh and conservative assumption on grid extension [11].

Based on the presented information it was decided to design and create an integrated power electronic converter which can provide all the energy needs in these remote locations. This converter will have a DC input source which will provide energy to charge a battery system, multiple cell phone charging ports and it will also power one low voltage (LV) DC and one high voltage (HV) AC load. The DC and AC loading is dependent on the customer, although it was decided to provide 100W of DC electricity at either 12V or 24V and 1000W of AC electricity at 230V, 50 Hz. Note that, the proposed system is not strictly limited to applications in Africa as there are many locations around the world which can benefit from a distributed solar system such as countries in South America, the Middle East, and Asia.

#### 1.2 Thesis Outline

The thesis mainly focuses on the design of each converter within the integrated system, with more detail regarding the inductor design of the boost converter as will be discussed.

Chapter 2 will be a literature review of related off-grid systems and past applications reviewing the type of systems available and the advantages and disadvantages of each.

Chapter 3 will go into the topology breakdown of different energy systems, discussing their advantages and disadvantages. Design concerns for each and a discussion about when certain topologies are more suitable than others for certain requirements or situations. The basic integrated topology will be selected and justified for this application.

Chapter 4 will go into the integrated converter design of each individual converter

within the system. A quick review on the operation of each converter, showing the typical waveforms and necessary equations for the design will be discussed, followed by the design and component selection. An in-depth design process for the inductor within the boost converter will be done. This will cover core and winding design, as well as implementing an optimization technique using the genetic algorithm (GA) in which the inductor is designed around the smallest inductor volume for different winding types. A comparison of these inductor designs will be done followed by the final selection of the inductor to be used. Another comparison between the custom inductor and an off-the-shelf inductor will be done to demonstrate the advantages the custom inductor provides. For the buck converter a simple design method using ripple requirements is used. The phase shifted full bridge (PSFB) converter design implements nest loops to arrive at the converter values. And lastly, a simple inverter design will be discussed involving the input capacitor design and output filter design based on the HVDC link ripple and output voltage harmonic respectively.

Chapter 5 will discuss the implemented control methods for both the simulation analysis, and experimental testing. A brief discussion on the most common and well known control methods implemented within power electronic converters will be discussed, followed by the implemented control method to be used for each converter. The required hardware will also be discussed which will cover the gate driver selection, DSP selection, current and voltage measurement sensors and circuits, and finally the designed PCB layout and manufactured PCB.

Chapter 6 will discuss component and converter modeling, simulation, and loss estimation. Each component within each converter will be modeled and the losses defined and calculated. The losses can be used to determine the efficiency of the converter over varying load power. The system modeling will be done using MAT-LAB/Simulink and will first be simulated over a time range of 3 seconds while the input voltage, output buck voltage, output buck power and output AC power change. This will show the integrated converter being controlled over these applied changes. The efficiency will then be found for each converter over their respective load ranges to determine each converters efficiency map.

Chapter 7 will discuss the experimental testing and simulation comparison for each converter. Each converter will operate at their max powers to both validate the designed converters, and also to compare the experimental modeling to the simulated modeling. It will be shown that there were a few experimental issues with the PSFB converter and single phase inverter that will be discussed in more detail in their respective sections. However, after a few modifications, the tests will be complete at the full load conditions for each. A comparison between the designed inductor using the implemented GA inductor design, and an inductor off-the-shelf will be done. The GA based inductor will be shown to have lower total volume and losses when compared with the boost converter using an off-the-shelf inductor.

Chapter 8 finalizes the thesis with a conclusion on the work presented, and future tasks to be completed.

The main goals/targets of this work include:

- Design, simulate, build, and test a prototype for an off-grid standalone integrated power electronic system for a rural application

- Build and test each converter at its full load conditions and if possible, tests the entire converter operating together

- Create models which can be used to estimate system transients, waveforms and

predict losses

• Have a custom inductor design method which can be applied to future inductor designs. Show that the inductor design provides advantages over the traditional inductors available

### Chapter 2

# Review of Off-Grid System Products and Past Applications

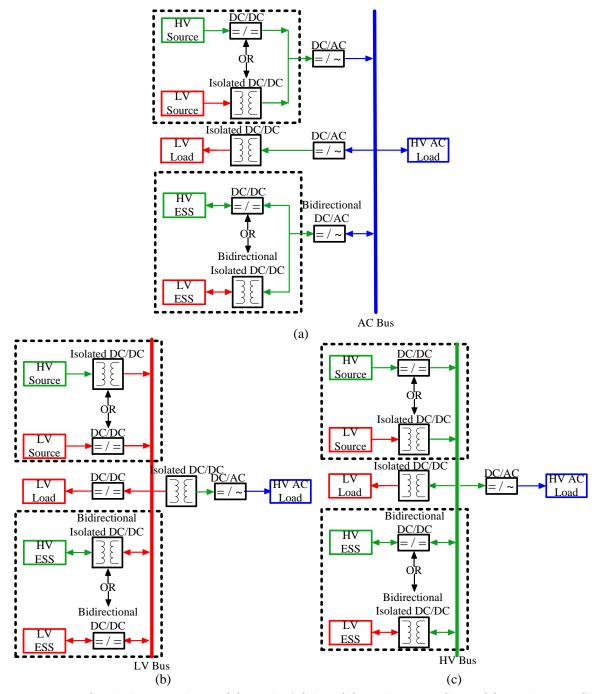

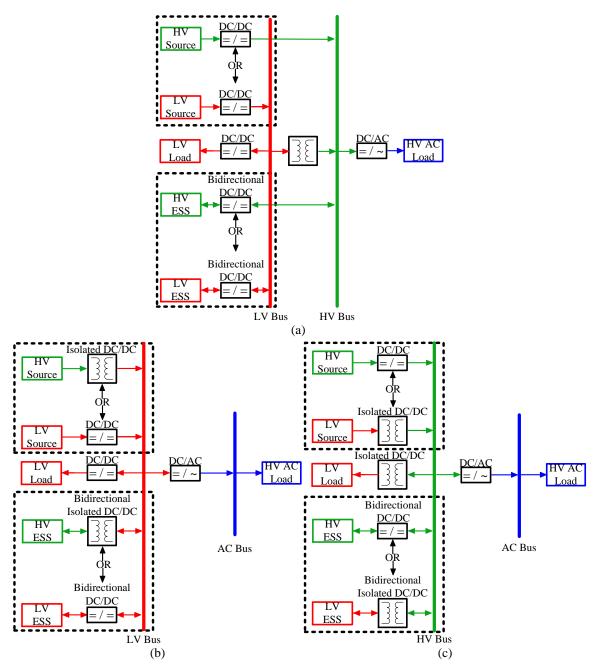

There are many different products and technologies which provided solutions for off-grid distributed energy applications. These mainly fall into either portable or stationary systems or a mixture of the two [13]. Both can further be broken down into DC [14,15], AC [14–16] or a combination of the two known as hybrid systems [14–18]. For AC systems, there is a main AC bus which can be centralized or decentralize. Centralized systems have the main AC bus connected to the grid or load, while decentralized systems have each AC source connected individually to the grid or load. Centralized and decentralized systems can be applied in the same manner for DC systems, however the connection type is typically centralized due to simplicity [19, 20]. Hybrid systems can come in many different topologies either implementing a main DC bus connection, a main AC bus connection, or both an AC and DC bus connection [19,20]. For safety reasons, high voltage (HV) must have galvanic isolation from low voltage (LV), therefore, depending on the application; a variety of topologies can be adopted. The following sections will go into portable and stationary systems and discuss details of each and their respective advantages and disadvantages.

#### 2.1 Portable Applications

Portable systems almost always have a portable battery pack which is used to power either the DC or AC loads and are sometimes combined with solar panels or input ports that are connected with other DC or AC sources to recharge the battery. Some are designed for camping applications which can be carried by the user, while others are for off-grid homes which are heavy and require a trailer to move the system [13]. The off-grid systems can be considered stationary for the most part since they will not be moved in the same way the camping systems are. Therefore, the trailer systems will be considered stationary. A list of portable systems is found in [13] and a few others are shown in Table 2.1. These include EnerPlexs Generator 1200 solar generator, Be Prepared Solar, Wagan Tech Solar e Power Cube, PowerOak hand and home power products, Renogys Lycan PowerBox and Goal Zero Yeti 1250 Solar Generator. The internal circuitry of these products is unknown for the most part; however it appears most of these converters use a 12V DC to 120V AC inverter for either pure sine or modified sine wave output. The input charging capability is low so the charge times are quite long and it appears as if most are meant to run off of the battery pack and not through the input. Meaning the battery first needs to be charged for the system to run the outputs since the input power is not enough to operate all the loads at full power without the battery.

| <ul> <li>EnerPlexs Generatr 1200 solar generator [21]:</li> <li>Input: <ul> <li>4x Solar Panel DC Jack 16-34V, 120W Max</li> <li>Wall Charger DC Jack 19V, 120W Max</li> <li>2x Anderson Jacks 12V, 120W Max</li> </ul> </li> <li>Output: <ul> <li>USB, 12V, Standard AC Wall Outlet</li> <li>3x USB 2.4A/12V-10A, 120W max total</li> <li>12V Anderson- 10A, 120W max total</li> <li>19V- 6.3A, 120W max total</li> <li>AC (3x)-100V AC 60Hz pure-sine wave 1000W Max total continuous (1100 Max over loading)</li> </ul> </li> </ul> | <ul> <li>Wagan Tech Solar e Power Cube 1500 [22]:</li> <li>Solar controller 20A</li> <li>1x 100Ah, 12V, 15A max continuous AG-M/Gel hybrid Battery</li> <li>Input: <ul> <li>2x 100V-240V AC charger 50/60Hz</li> <li>5x 16W solar panels (80W total), 17% eff, 20A max</li> </ul> </li> <li>Output: <ul> <li>2x 5V USB Outlet, 2.1A max</li> <li>2x 115VAC,60Hz 1.5kW continuous 3.6kW peak ac output, modified sine wave, 90% eff</li> <li>2x 12V DC outlet</li> </ul> </li> </ul> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Goal Zero Yeti 1250 Solar Generator [23]:</li> <li>1200Wh, 100Ah, 12V AGM Lead Acid Battery</li> <li>Input Specs: <ul> <li>120V AC Wall Charger (72W)</li> <li>12V Car Charger (30W)</li> <li>8mm Solar 16V-48V, 10A, 160W max</li> <li>Power Pole 16V-48V, 20A, 240W max</li> </ul> </li> <li>Output: <ul> <li>3x 5V, 2.1A USB outlets</li> <li>8mm 12V, 10A, 120W</li> <li>12V, 33A Power Pole Port</li> <li>3x 110V AC, 60Hz, 1200W pure sine wave</li> </ul> </li> </ul>                                                  | <ul> <li>Renogy's Lycan PowerBox [24]:</li> <li>24Ah, 1075Wh, 12V Lead Acid Battery</li> <li>20A Max power point tracking (MPPT) 1200W Pure Sine Wave Inverter</li> <li>Input: <ul> <li>Solar Panel</li> <li>Wall Outlet</li> <li>12V Car Charger</li> </ul> </li> <li>Output <ul> <li>2x 12V DC</li> <li>3x 110V AC</li> <li>4x 2.4A USB</li> </ul> </li> </ul>                                                                                                                    |

#### Table 2.1: Protable Off-Grid Products and Applications

# 2.2 Stationary Applications

As discussed previously, stationary systems provide more power and are typically used for home or village applications, or as charging stations for different loads such as cell phone charging, repurposed automobile batteries or portable battery kits [13, 25] Stationary systems on the smaller side tend to be for home energy applications wherein a single home or a few homes use the same energy system [13, 25] They can also be in trailer systems, storage containers, or carts [13]. Larger systems fall into the micro grid category and can supply small villages or communities with their electricity needs if it is large enough [13, 18, 25]. In most cases these are hybrid systems that implement both AC and DC sources due to reliability since the base load requirement can be large. Typically these systems use AC sources such as diesel generators, wind turbines or hydro, while solar is used as DC supplies with battery storage. Some stationary systems are shown in Table 2.2 below and many others can also be found in [18, 25, 26]. Since this application is targeting small scale DC systems, AC and hybrid architectures will be ignored. Of the systems found in literature which fall into this category, the Sunblazer II and Universal Charge Controller, by IEEE Smart Village, is very similar to the system proposed herein as will be shown in Chapter 3. There is also a bit more documentation discussing the internal circuitry used for the universal charge controller discussed in [27] and shown in Fig. 2.1. The demo board DC2069A was used in this product as a proof of concept to show that the controller works and is able to charge batteries [28]. The demo boards solar input is from 17V to 54V volts and can go up to 200W [28]. This board is used to charge a 12V SLA battery with a max input charge current and output charge current of 10A and 16.6A

## respectively.

| <i>v</i>                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sunblazer II Unit [29]:                                                                                                                                                                                                                                                                                                                 | Smart Village Universal Charge Controller [27]:                                                                                                                                                                                                                              |

| <ul> <li>MPPT solar charge controller</li> <li>Input: <ul> <li>6x 300W solar panels</li> <li>4x 24/48V AGM/GEL batteries</li> <li>1000W AC input charger (Wind/Diesel) backup power</li> </ul> </li> <li>Output: <ul> <li>10-20x 12V, 9-18Ah universal portable battery units</li> <li>1.5 kW AC 230V, 50Hz/60Hz</li> </ul> </li> </ul> | <ul> <li>Input:</li> <li>18V-24V solar panel</li> <li>45V-55V solar panel</li> <li>50V-60V DC microgrid</li> <li>24V Sunblazer-Lite or storage</li> <li>110/220 AC microgrid</li> <li>Output:</li> <li>12V home battery</li> <li>12V appliances (fan, lights etc)</li> </ul> |

| <ul> <li>Leading Edge Power Box [30]:</li> <li>360Ah/24V battery with 24V/(10, 25, 50, or 70 A charger)</li> <li>Input: <ul> <li>2x 140W solar panels</li> <li>300-450W wind power</li> <li>187-265V/16A/45-65Hz AC input</li> </ul> </li> <li>Output: <ul> <li>12V/9A and 24V/ 6A</li> <li>230V/16A AC output</li> </ul> </li> </ul>   | Other Products/Manufacturers:<br>• Tesla PowerWall [31]<br>• SMA products [32]<br>• Schnider electric products [33]<br>• SolarEdge [34]<br>• Enphase Energy [35]<br>• ABB [36]                                                                                               |

### Table 2.2: Stationary Off-Grid Products and Applications

Figure 2.1: Smart village universal charge controller [27].

Figure 2.2: Sunblazer II unit [29].

The Sunblazer II Unit [29] is the other mentioned product by IEEE implemented in village applications. This is a solar charge station that consists of six 300W solar panels, four 24V or 48V batteries (AGM or GEL), solar charge controller using MPPT, ten or twenty charging channels for 12V 9-18Ah universal portable battery units, and the option to have both a 1000W AC input charger and a 1500W AC output load at 230V, 50 Hz or 60Hz as shown in Fig. 2.2. From the comparison discussed between portable and stationary systems, it was decided to design and build a prototype of a stationary energy system using strictly DC sources. The main reason for making this a stationary system is because it has been reported as being more popular than portable applications by people who have used both systems in these remote locations. This is mainly due to the fact that people do not want to carry around a battery pack and would rather have the electricity closer to them [37]. The system will be very similar to the Sunblazer II Unit shown above and more detail will be discussed in the following sections.