Three-Phase Dual Active Bridge Converter: Design Considerations and Planar Transformer Design

## THREE-PHASE DUAL ACTIVE BRIDGE CONVERTER: DESIGN CONSIDERATIONS AND PLANAR TRANSFORMER DESIGN

By

Ying Cui, M.A.Sc., B.Sc.

A Thesis Submitted to the School of Graduate Studies in Partial Fulfillment of the Requirements for the Degree Master of Applied Science

McMaster University © Copyright by Ying Cui, August, 2017 All Rights Reserved Master of Applied Science (2017) (Electrical & Computer Engineering) McMASTER UNIVERSITY Hamilton, Ontario

TITLE:Three-Phase Dual Active Bridge Converter: DesignConsiderations and Planar Transformer Design

| <b>AUTHOR:</b> | Ying Cui                                        |

|----------------|-------------------------------------------------|

|                | M.A.Sc.                                         |

|                | School of Electrical Engineering & Automation   |

|                | (Harbin Institute of Technology, Harbin, China) |

|                |                                                 |

|                |                                                 |

| <b>SUPERVISOR:</b> | Ali Emadi, Professor                    |

|--------------------|-----------------------------------------|

|                    | Ph. D. (Texas A&M University)           |

|                    | IEEE Fellow                             |

|                    | Canada Excellence Research Chair Hybrid |

|                    | Powertrain Program                      |

|                    |                                         |

NUMBER OF PAGES: XX, 115

谨以此献给我的家人

To My Family

### ABSTRACT

This thesis discusses comprehensive design considerations for the three-phase dualactive-bridge (DAB) converter and presents a planar transformer design for the threephase DAB converter used in smart home applications.

An overview of the planar transformer, including magnetic cores, planar windings as well as its advantages and disadvantages are presented first. The review on analysis of transformer losses, leakage inductance and stray capacitance provides a guideline for transformer design.

The operating principle of three-phase DAB converter is presented and the closed form expression of zero-voltage-switching (ZVS) condition, current stress of switching devices and DC link capacitors are obtained. Analytical results are applied in the parameter design of the DAB converter.

A new design method for the three-phase DAB converter parameter selection is proposed. A new parameter fL is defined to simplify the analysis from three dimensions  $(n, f, L_k)$  to two dimensions (n, fL), from which the feasible value of n is determined. Together with the constraint of transformer design, the effective operating area (EOA) of f and  $L_k$  is obtained. The main losses that vary with the selectable parameters are studied and the corresponding converter efficiency is presented at different voltage and power levels. The parameters  $(n, f, L_k)$  are determined based on the comprehensive parameter design considerations of the three-phase DAB converter.

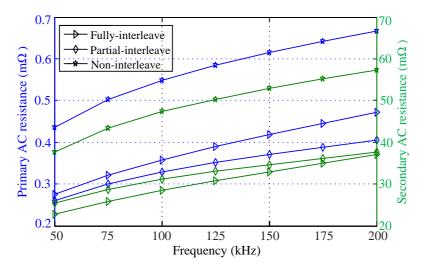

A planar transformer for the three-phase DAB converter is designed based on the mathematical analysis and finite element analysis (FEA). The parameters that determine core selection are derived for the three-phase DAB converter. The winding design is accomplished using the FEA simulations. The impacts of different winding structures on the AC resistance, leakage inductance and stray capacitance are investigated, and the fully-interleaved design is selected for its low resistance and structural simplicity.

The planar transformer prototype is built and tested in a three-phase DAB converter. The experimental waveforms at different voltage levels and power ratings demonstrate the effectiveness of the converter and transformer. The converter ZVS behavior and efficiency performance are measured, which validate the analysis.

### ACKNOWLEDGEMENT

First and foremost, I would like to sincerely thank my supervisor, Dr. Ali Emadi, for his guidance and support of both my life and research work. Over the past two years, his motivation and enthusiasm have inspired me and encouraged me to be more passionate and confident. It is truly an honor to work with him.

I am grateful to all colleagues in the Canada Excellence Research Chair in Hybrid Powertrain Program for their support and help. I would like to thank James Jiang, Fei Peng, Dan Manolescu and Ruoyu Hou for sharing their expertise and valuable information. Special thanks go to Deqiang Wang for helping me with the experiments. Special thanks go to Haoding Li for reading the thesis and for his valuable comments. I want to thank everyone in the lab for the great time we shared together.

To my parents, my sister and brother, words cannot express how grateful I am for your constant encouragement, sacrifices and endless love. Especially, I would like to thank my husband, Hao Ge, for his full support, encouragement and help from the beginning. Thank him for being by my side and inspiring me with insightful ideas. You are my source of strength which is always with me.

This research was undertaken, in part, thanks to funding from the Canada Excellence Research Chairs (CERC) Program. The author also gratefully acknowledges ANSYS for their support with Maxwell in this research.

# **CONTENTS**

| Abstract                                           | V    |

|----------------------------------------------------|------|

| Acknowledgement                                    | vii  |

| Contents                                           | ix   |

| List of Figures                                    | xiii |

| List of Tables                                     | xvii |

| List of Abbreviations                              | xix  |

| Chapter 1 Introduction                             | 1    |

| 1.1. Background                                    | 1    |

| 1.2. Objectives                                    | 6    |

| 1.3. Thesis Outline                                | 7    |

| Chapter 2 Planar Transformers                      | 9    |

| 2.1. Overview of Planar Transformer                | 9    |

| 2.1.1. Magnetic Cores                              | 9    |

| 2.1.2. Planar Windings                             | 11   |

| 2.2. Transformer Losses                            | 14   |

| 2.2.1. Core Loss                                   | 14   |

| 2.2.2. Copper Loss                                 | 14   |

| 2.3. Parasitic effects                             |      |

| 2.3.1. Leakage Inductance                          |      |

| 2.3.2. Stray Capacitance                           | 20   |

| 2.4. Summary                                       | 21   |

| Chapter 3 Three-Phase Dual Active Bridge Converter | 23   |

| 3.1. Basic Configuration                           | 23   |

| 3.2. Operating Scheme                              | 24   |

| 3.3. Zero-voltage-switching Condition              | 26   |

| 3.4. Switch and Capacitor Current Stress                                 | 27     |

|--------------------------------------------------------------------------|--------|

| 3.5. Summary                                                             | 29     |

| Chapter 4 Three-phase Dual Active Bridge Converter Design Considerations | 31     |

| 4.1. Key Influence of Turn Ratio                                         | 31     |

| 4.1.1. Zero-Voltage-Switching Boundary                                   | 31     |

| 4.1.2. RMS Current                                                       | 33     |

| 4.1.3. Ripple Current of DC Link Capacitor                               | 34     |

| 4.2. Effective Operating Area of Frequency and Leakage Inductance        | 36     |

| 4.2.1. Effective Operating Area Limited by Transmission Power            | 36     |

| 4.2.2. Effective Operating Area Limited by Transformer Design            | 36     |

| 4.2.3. Switch and Capacitor Current Analysis                             | 38     |

| 4.2.4. MATLAB/Simulink Verification                                      | 39     |

| 4.3. Loss Analysis                                                       | 44     |

| 4.3.1. Power Loss of Switches                                            | 45     |

| 4.3.2. Transformer Loss                                                  | 48     |

| 4.4. Converter Efficiency                                                | 49     |

| 4.5. Summary                                                             | 54     |

| Chapter 5 Planar Transformer Design for the Three-phase Dual Active B    | Bridge |

| Converter                                                                | 55     |

| 5.1. Design Methodology                                                  | 55     |

| 5.2. Transformer Core Selection                                          | 57     |

| 5.3. Winding design                                                      | 62     |

| 5.3.1. Winding Trace Design                                              | 62     |

| 5.3.2. Winding Arrangements                                              | 64     |

| 5.4. Magnetizing Inductance                                              | 77     |

| 5.5. Core Loss                                                           | 79     |

| 5.6. Summary                                                             | 82     |

| Chapter 6 Experimental Verification                                      | 83     |

| 6.1. Transformer Prototype                                               | 83     |

| 6.2. Transforemr Parameter Measurement             | 84 |

|----------------------------------------------------|----|

| 6.3. Three-phase Dual Active Bridge Converter Test | 86 |

| 6.3.1. Voltage and Current Waveforms               |    |

| 6.3.2. Zero-Voltage-Switching Verification         |    |

| 6.3.3. Efficiency Test                             |    |

| 6.4. Summary                                       |    |

| Chapter 7 Conclusions                              |    |

| Further Work Suggested                             |    |

| Publications                                       |    |

| References                                         |    |

# LIST OF FIGURES

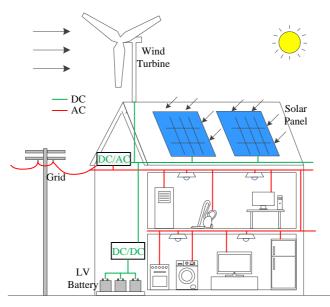

| Fig. 1.1. Example of smart home for residential application.                                                                              | 2  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

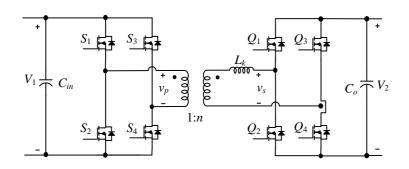

| Fig. 1.2. Configuration of single-phase DAB converter.                                                                                    | 4  |

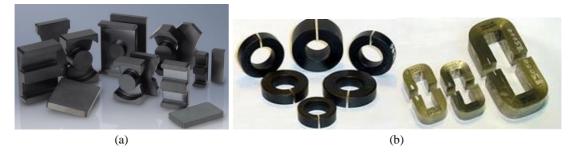

| Fig. 2.1. Core geometry (a) planar E, ER, RM and PQ core<br>(b) toroidal and C core.                                                      | 11 |

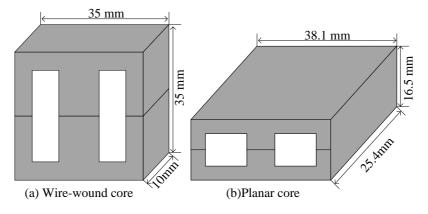

| Fig. 2.2. Comparison of planar and wire-wound structure.                                                                                  | 11 |

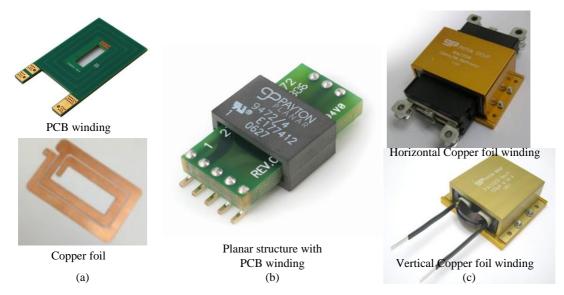

| Fig. 2.3. Different implementation structure of planar windings.                                                                          | 12 |

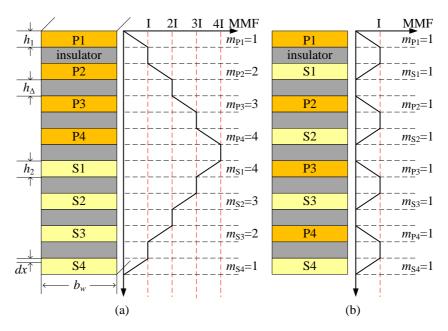

| Fig. 2.4. MMF distribution of<br>(a) non-interleaved winding (b) fully-interleaved winding.                                               | 13 |

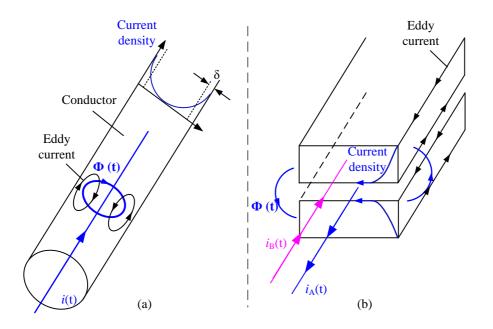

| Fig. 2.5. Eddy current effect (a) skin effect (b) proximity effect.                                                                       | 16 |

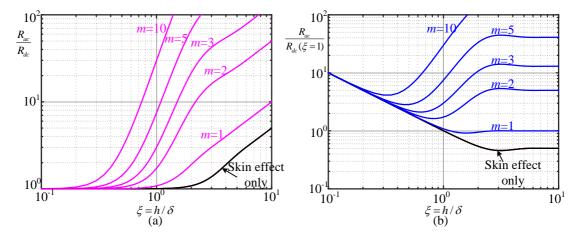

| <ul><li>Fig. 2.6. (a) Ratio of AC to DC resistance</li><li>(b) ratio between AC and DC resistance with thickness of skin depth.</li></ul> | 17 |

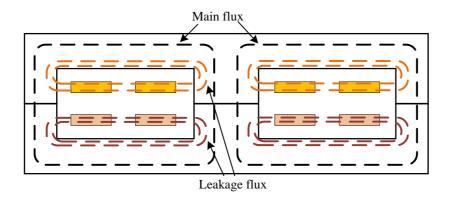

| Fig. 2.7. Main flux and leakage flux paths.                                                                                               | 18 |

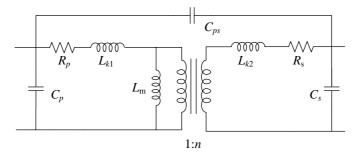

| Fig. 2.8. Equivalent circuit of the planar transformer model.                                                                             | 21 |

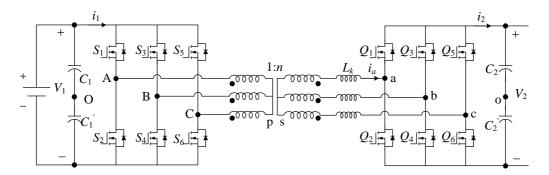

| Fig. 3.1. Basic configuration of three-phase DAB converter.                                                                               | 23 |

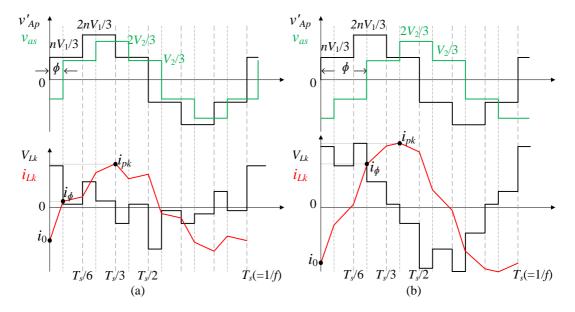

| Fig. 3.2. Operating waveforms of three-phase DAB converter<br>(a) $\phi \le \pi/3$ (b) $\phi > \pi/3$ .                                   | 25 |

| Fig. 3.3. Input current and current through switches.                                                                                     | 28 |

| Fig. 4.1. LV and HV ZVS boundary at different $V_1$ .                                                                                     | 33 |

| Fig. 4.2. Averaged RMS current at different <i>n</i> and <i>fL</i> under full load.                                                       | 34 |

| Fig. 4.3. Worst case LV and HV ripple current at different <i>n</i> and <i>fL</i> .                                                       | 35 |

| Fig. 4.4. EOA limited by transmission power and transformer design at (a) $n = 7$ , (b) $n = 8$ and (c) $n = 9$ .                         | 37 |

| Fig. 4.5. Switches current stress analysis at (a) $n = 7$ , (b) $n = 8$ and (c) $n = 9$ .                                                        | 38 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 4.6. Capacitor ripple current analysis at (a) $n = 7$ , (b) $n = 8$ and (c) $n = 9$ .                                                       | 39 |

| Fig. 4.7. Simulated voltage and current waveforms at (a) $n = 7$ , (b) $n = 8$ and (c) $n = 9$ under 100kHz, 8 $\mu$ H.                          | 41 |

| Fig. 4.8. Simulated voltage and current waveforms at (a) $n = 7$ , (b) $n = 8$ and (c) $n = 9$ under 120kHz, 4 $\mu$ H.                          | 42 |

| Fig. 4.9. Ripple current of DC capacitors on HV side at different $(n, f, L_k)$                                                                  | 44 |

| Fig. 4.10. Conduction and switching loss under different $V_1$ at (a, b, c) $n = 7$ , (d, e, f) $n = 8$ and (g, h, i) $n = 9$ .                  | 47 |

| Fig. 4.11. Transformer losses under nominal operating voltage at (a) $n = 7$ , (b) $n = 8$ and (c) $n = 9$ .                                     | 49 |

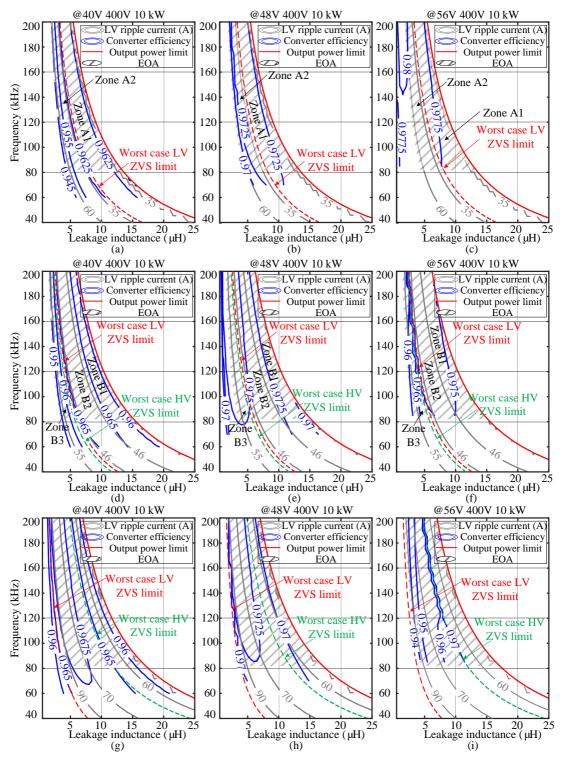

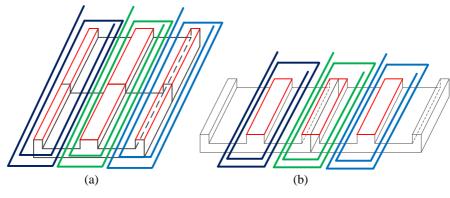

| Fig. 4.12. Converter efficiency under full load at $(a \sim c) n = 7$ , $(d \sim f) n = 8$ and $(g \sim i) n = 9$ .                              | 51 |

| Fig. 4.13. Converter efficiency under half load at $(a \sim c) n = 7$ , $(d \sim f) n = 8$ and $(g \sim i) n = 9$ .                              | 52 |

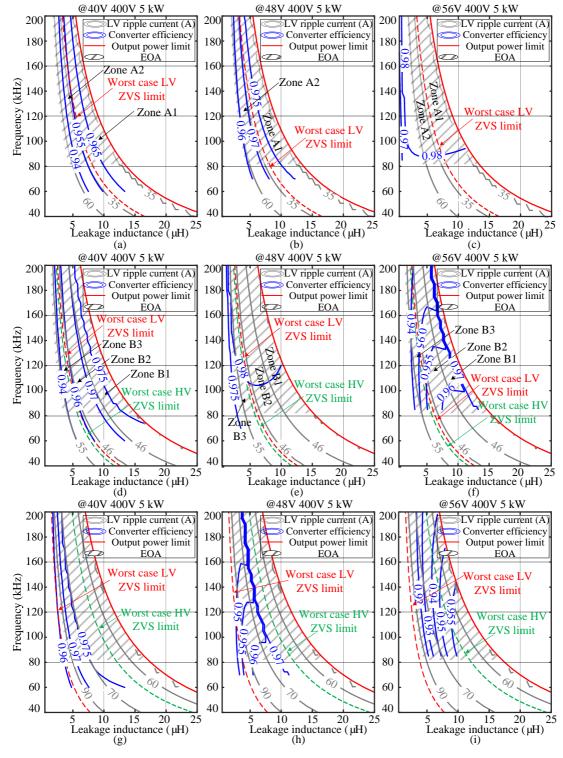

| Fig. 5.1. Design flowchart of planar transformer.                                                                                                | 56 |

| Fig. 5.2. Cores in parallel to extend power capability.                                                                                          | 57 |

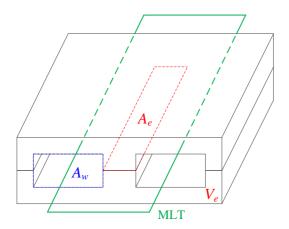

| Fig. 5.3. Dimensions of planar EE core: $A_w$ , $A_e$ , $V_e$ and MLT.                                                                           | 58 |

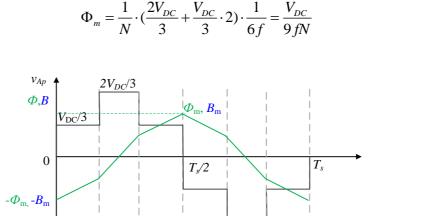

| Fig. 5.4. Voltage, flux and flux density waveform of transformer.                                                                                | 60 |

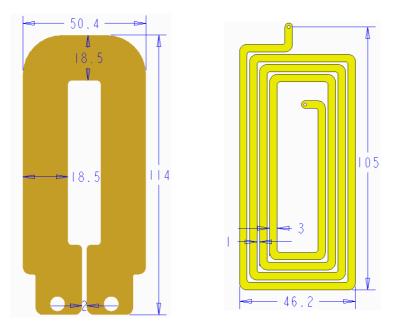

| Fig. 5.5. Trace width and spacing of primary and secondary winding.                                                                              | 64 |

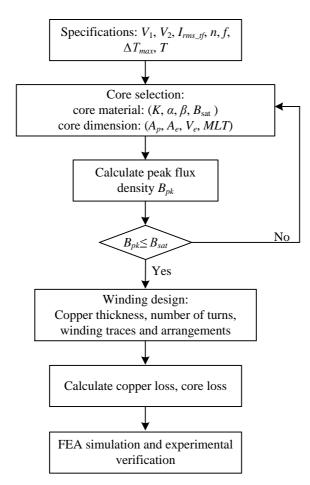

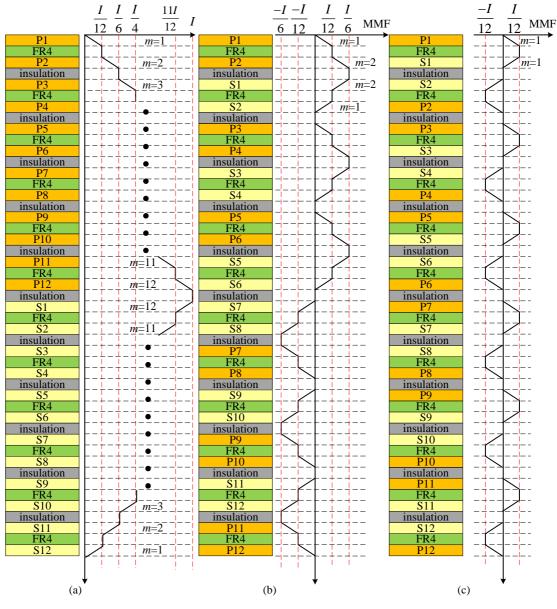

| Fig. 5.6. MMF distribution of (a) non-interleaved,<br>(b) partial-interleaved and (c) fully-interleaved winding.                                 | 65 |

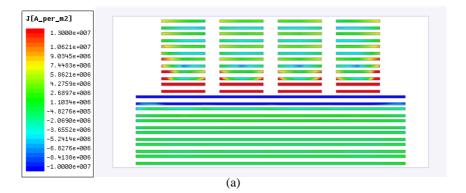

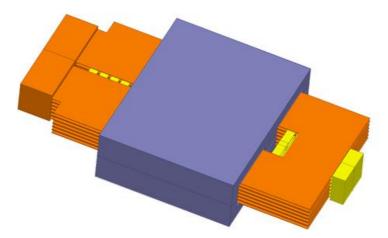

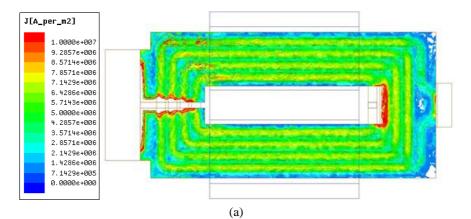

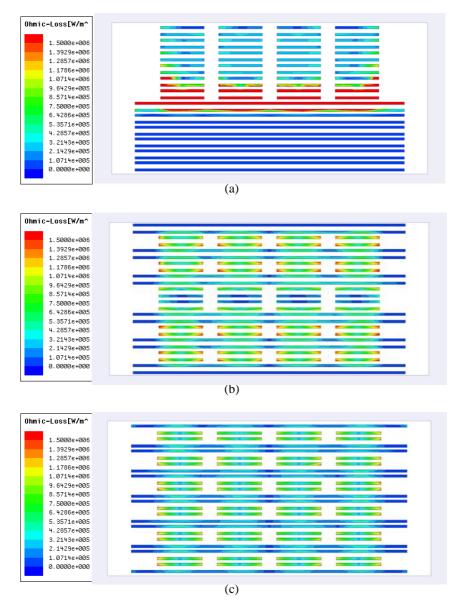

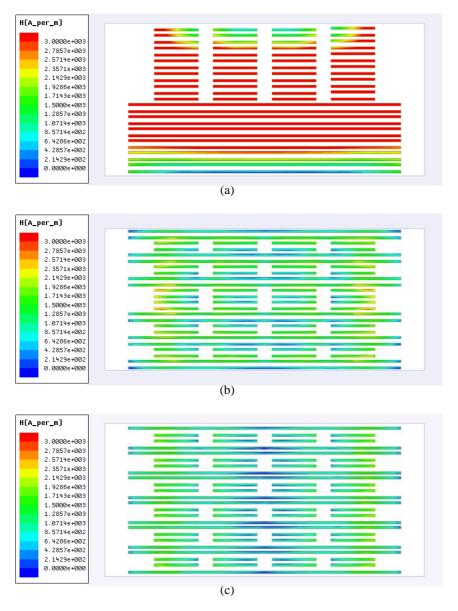

| <ul><li>Fig. 5.7. Current distribution in (a) non-interleaved,</li><li>(b) partial-interleaved and (c) fully-interleaved winding (2D).</li></ul> | 67 |

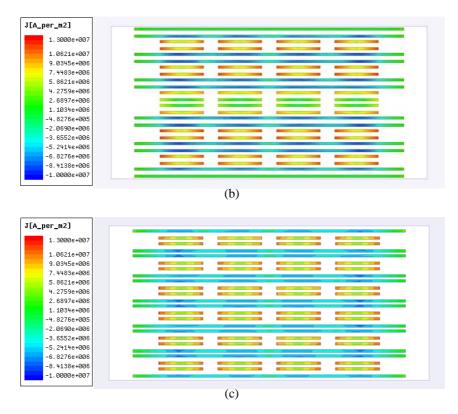

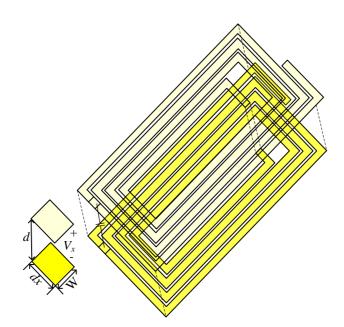

| Fig. 5.8. Maxwell 3D transformer model                                                                                                           | 68 |

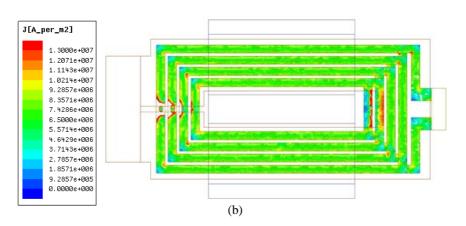

| Fig. 5.9. Current distribution of fully interleaved winding structure in (a) primary winding (b) secondary winding (3D).                         | 68 |

| <ul><li>Fig. 5.10. Ohmic loss distribution of (a) non-interleaved,</li><li>(b) partial-interleaved and (c) fully-interleaved winding.</li></ul> | 69 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 5.11. Simulated AC resistance of three winding structures (2D)                                                                             | 70 |

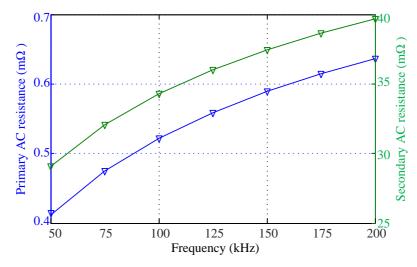

| Fig. 5.12. Simulated AC resistance of fully-interleaved winding (3D).                                                                           | 71 |

| Fig. 5.13. Magnetic field strength distribution of (a) non-interleaved,<br>(b) half-interleaved and (c) fully-interleaved winding               | 72 |

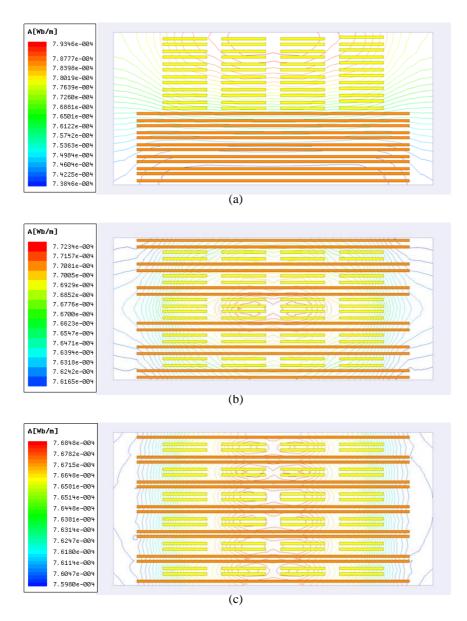

| Fig. 5.14. Flux line distribution of (a) non-interleaved, (b) half-interleaved and (c) fully-interleaved winding.                               | 73 |

| Fig. 5.15. Intra-winding capacitance of two adjacent winding layers in series.                                                                  | 76 |

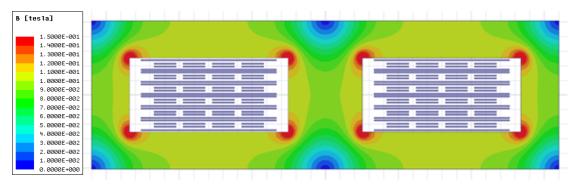

| Fig. 5.16. Flux density distribution of fully-interleaved winding.                                                                              | 78 |

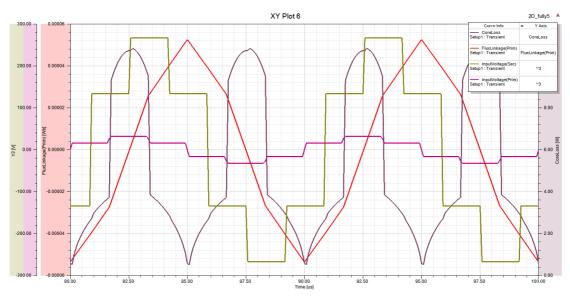

| Fig. 5.17. Voltage, flux linkage and core loss waveforms of the designed transformer.                                                           | 80 |

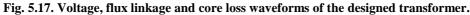

| Fig. 5.18. Core loss density distribution of fully-interleaved winding.                                                                         | 81 |

| Fig. 5.19. Winding stack arrangement of the designed transformer.                                                                               | 81 |

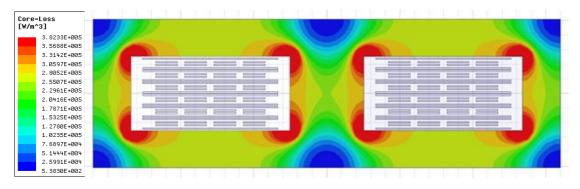

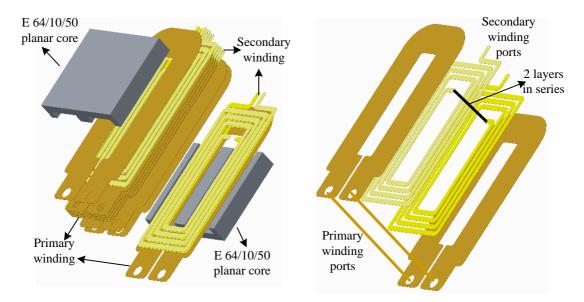

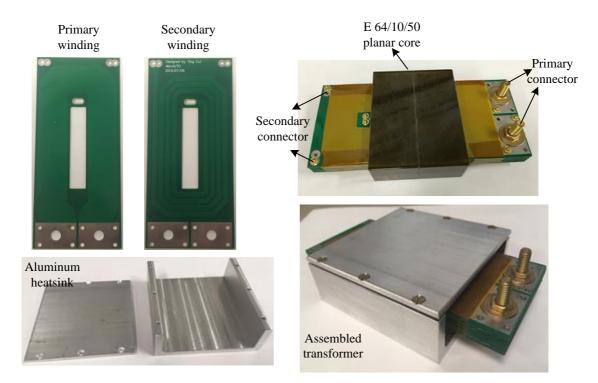

| Fig. 6.1. Photo of designed PCB winding and assembled transformer.                                                                              | 83 |

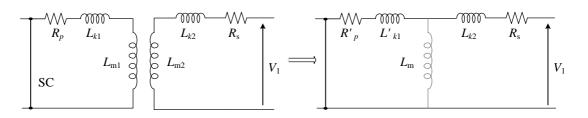

| Fig. 6.2. Equivalent leakage inductance measurement by SC test.                                                                                 | 85 |

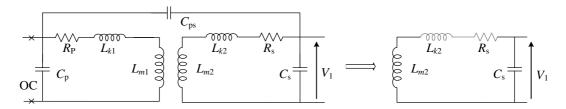

| Fig. 6.3. Magnetizing inductance and intra-winding capacitance measurement by OC test.                                                          | 85 |

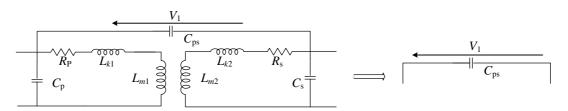

| Fig. 6.4. Inter-winding capacitance measurement.                                                                                                | 85 |

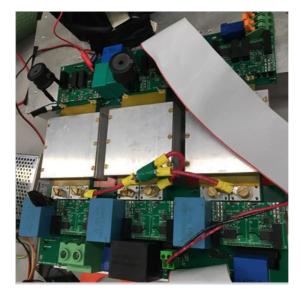

| Fig. 6.5. Picture of the three-phase DAB converter prototype.                                                                                   | 87 |

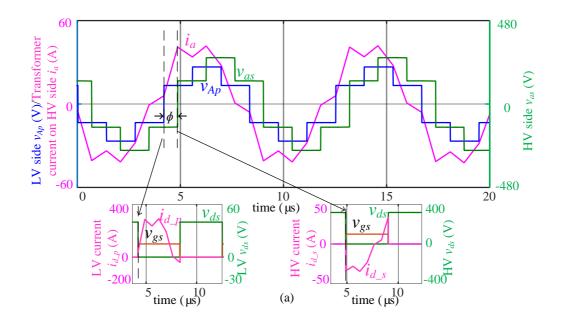

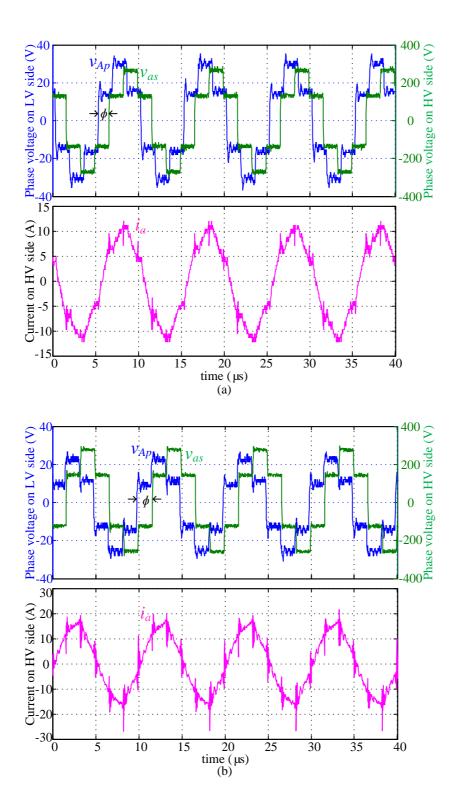

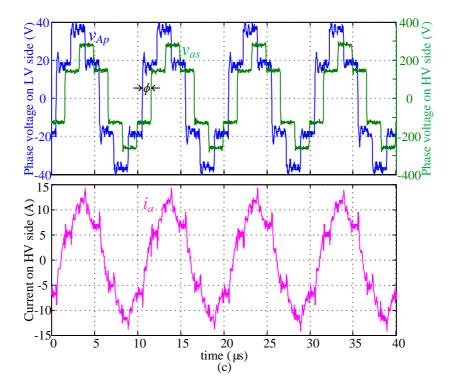

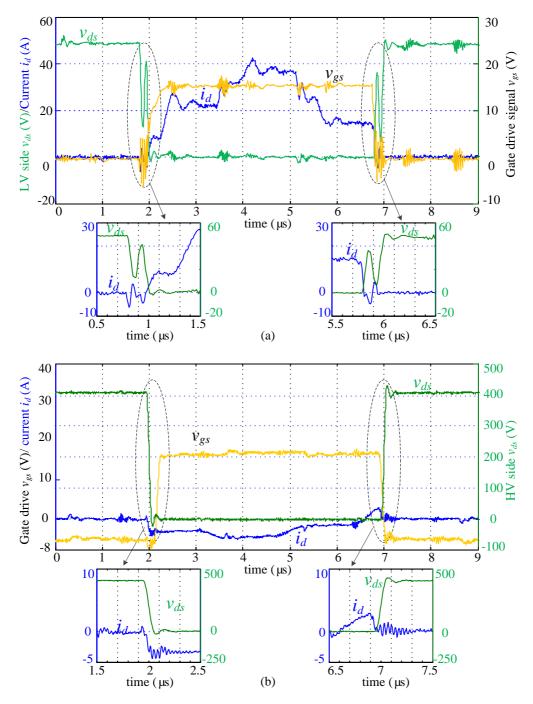

| Fig. 6.6. Voltage and current waveforms of<br>(a) 48/400 V, (b) 40/400 V and (c) 56/400 V operating at 3 kW.                                    | 89 |

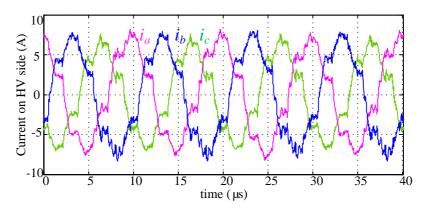

| Fig. 6.7. Current waveforms of three phases operating at 48/400 V 2.4 kW.                                                                       | 89 |

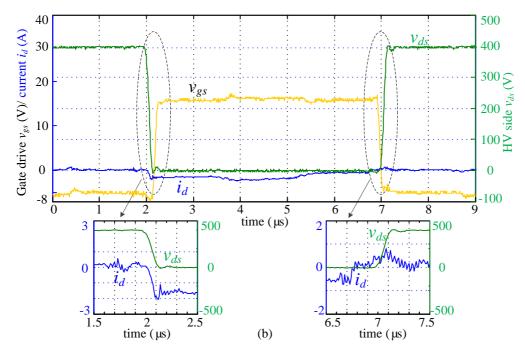

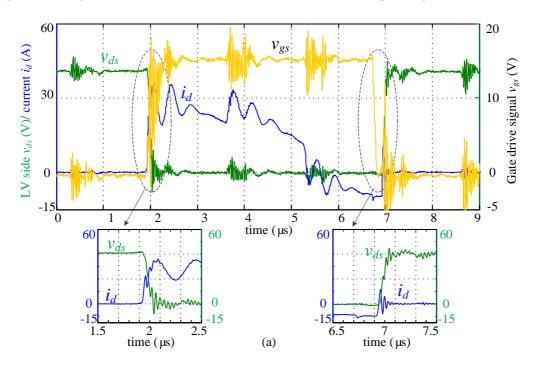

| Fig. 6.8. Voltage and current waveforms of switching behavior on (a) LV and (b) HV side at full load.                                           | 91 |

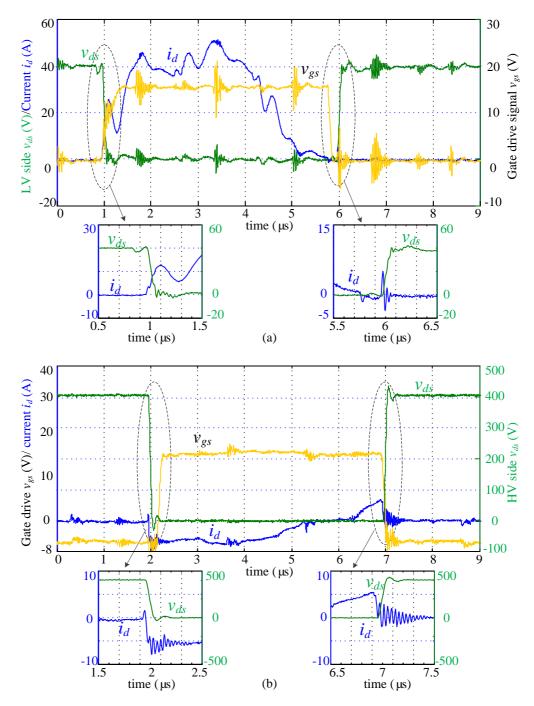

| Fig. 6.9. Voltage and current waveforms on<br>(a) LV and (b) HV side operating at $V_1 = 48V$ , 1.6 kW.                                         | 92 |

| Fig. 6.10. Voltage and current waveforms on<br>(a) LV and (b) HV side operating at $V_1 = 40$ V, 1.6 kW. | 93 |

|----------------------------------------------------------------------------------------------------------|----|

| Fig. 6.11. Voltage and current waveforms on<br>(a) LV and (b) HV side operating at $V_1 = 56V$ , 1.6 kW. | 94 |

| Fig. 6.12. Voltage and current waveforms on<br>(a) LV and (b) HV side operating at $V_1 = 48V$ , 800 W.  | 96 |

| Fig. 6.13. Voltage and current waveforms on<br>(a) LV and (b) HV side operating at $V_1 = 40V$ , 800 W.  | 97 |

| Fig. 6.14. Voltage and current waveforms on<br>(a) LV and (b) HV side operating at $V_1 = 56V$ , 800 W.  | 98 |

| Fig. 6.15. Measured converter efficiency at different input voltage and power level.                     | 99 |

# LIST OF TABLES

| Table 1.1 Specifications of DC/DC converter                                  | 3  |

|------------------------------------------------------------------------------|----|

| Table 2.1 Comparison of magnetic material properties                         | 10 |

| Table 4.1 Current stress of switches under different parameters              | 43 |

| Table 4.2 Capacitor ripple current under different parameters                | 43 |

| Table 5.1 Specifications of the planar transformer                           | 55 |

| Table 5.2 Steinmetz coefficient of N87 and core dimension of EE 58 and EE 64 | 61 |

| Table 5.3 Minimum trace width and clearance between traces                   | 63 |

| Table 5.4 Specifications of primary and secondary winding                    | 63 |

| Table 5.5 Leakage inductance of different winding structure                  | 74 |

| Table 5.6 Inter- and intra-capacitance of different winding structure        | 77 |

| Table 6.1 Transformer parameters                                             | 86 |

# LIST OF ABBREVIATIONS

two dimensional

2D

| 20   | two unitensional                        |  |

|------|-----------------------------------------|--|

| 3D   | three dimensional                       |  |

| AC   | alternate current                       |  |

| СМ   | common mode                             |  |

| DAB  | dual active bridge                      |  |

| DC   | direct current                          |  |

| EMI  | electromagnetic interference            |  |

| EOA  | effective operating area                |  |

| ESR  | equivalent series resistance            |  |

| FEA  | finite element analysis                 |  |

| HV   | high voltage                            |  |

| IGSE | improved generalized Steinmetz equation |  |

| kHz  | kilohertz                               |  |

| LV   | low voltage                             |  |

| MHz  | megahertz                               |  |

| MMF  | magnetomotive force                     |  |

| OC   | open circuit                            |  |

| РСВ  | printed circuit board                   |  |

| PWL  | piecewise linear model                  |  |

| RMS  | root mean square                        |  |

| SC   | short circuit                           |  |

| ZVS  | zero voltage switching                  |  |

|      |                                         |  |

## Chapter 1 INTRODUCTION

#### **1.1. BACKGROUND**

With the advancements in industry technology around the world, the continuously increasing energy consumption is becoming a major concern. Due to the shortage of fossil energy storage and the greenhouse emission, it is of great importance to reduce the energy consumption as well as seek alternative energy sources [1, 2].

In traditional power grid, electric power is delivered to users through long distance transmission line, which results in voltage drop and causes significant power losses. The power quality and reliability are degraded, especially in the rural area. By placing the power source close to the demand, the power loss on transmission line is reduced, which improves the efficiency and power quality in power distribution [3 - 5].

Smart home/grid with renewable energy sources such as solar and/or wind provide a solution to reduce carbon emissions as well as improve the power quality and efficiency. The solar/wind power sources installed in home or community provide power to household. It also has the ability to feed the excess energy back to the grid. By doing so, the power losses in the transmission lines are greatly reduced and the power quality and reliability are enhanced [6 - 8].

As a benefit of renewable energy, sustainable power supply can provide a lot of energy to meet the rapidly increased demand. However, the electric power generated by the renewable energy sources relies greatly on the weather condition, which makes it hard

to predict the power generation at a specific time period [1]. Energy storage systems are needed to absorb the instantaneously generated power, store the energy and provide power to the household when power generation is not enough.

Fig. 1.1 shows a conceptual smart home structure for future residential application [2], where the solar panel and/or wind turbine are placed on the roof. The renewable power generations are connected to the grid through high voltage (HV) DC bus and the corresponding DC/AC converter. To eliminate the impact caused by the intermittent nature of the renewable energy, energy storage devices are applied. In general, the storage devices consist of multiple 6- or 12-V battery cells. The standard voltage level of the battery pack is 48 V [9], which is named as low voltage (LV) battery in this thesis.

Fig. 1.1. Example of smart home for residential application [2].

The interface between HV DC bus (400 V) and the energy storage system desires a DC/DC converter with the ability of bidirectional power transfer. On one hand, this converter should be able to transfer the instantaneous electrical energy generated from

solar/wind to the LV battery pack. On the other hand, it should also allow the power transfer from the LV batteries to the load or back to the grid. In addition, galvanic isolation between HV DC bus and the LV battery pack is required for safety issues.

Considering residential power consumption of an average household, [10] gives the information provided by utility in the Middle Atlantic portion of the United States. For a household with footage area between 2000 ft<sup>2</sup> and 3000 ft<sup>2</sup>, the maximum averaged daily electricity demand is 10.93 kWh. This data deviates with regional difference, seasonal variation, and it also depends if the dwelling is with electric heat or gas heat. In order to meet the average household needs, a 10 kW DC/DC converter is desired. Considering the terminal voltage variation of the LV batteries, the specifications of the target DC/DC converter is given in Table 1.1.

Table 1.1 Specifications of DC/DC converter

| Primary DC voltage (LV side)   | $V_1$ | 48 V (40 V - 56 V) |

|--------------------------------|-------|--------------------|

| Secondary DC voltage (HV side) | $V_2$ | 400 V              |

| Maximum power                  | $P_N$ | 10 kW              |

The bidirectional dual-active-bridge (DAB) converter is a promising candidate for smart home applications because of its bidirectional power flow capability, galvanic isolation and high efficiency [9, 11 - 13]. The configuration of single-phase DAB converter is shown in Fig. 1.2 [14]. Phase shift is applied between the primary and secondary bridges to control the transmitted power in both directions. Due to the ability to realize zero-voltage-switching (ZVS), high efficiency is achieved. This is very important

in applications that use MOSFET, as its turn-on loss is more significant compared to turnoff loss [15]. Contributed by the transformer applied in the DAB converter, galvanic isolation is realized between primary and secondary side.

Fig. 1.2. Configuration of single-phase DAB converter.

However, due to the wide voltage range of the LV battery, the voltage ratio between primary and secondary side will deviate from the transformer turn ratio. In that case, hard switching happens, which leads to significantly lower converter efficiency, especially at light load. Improved modulation strategies [16 - 19] can be applied to improve the converter performance when the voltage mismatch happens. However, the output ripple current is still high, which increases the capacitor volume and decreases power density.

Different from single-phase DAB converter, three-phase DAB converter is composed of two three-phase half bridges and a three-phase transformer. Higher output power capability is achieved compared to single-phase DAB converter with the same current stress of devices. With higher ripple frequency, lower ripple current on the DC side is also achieved. Thus three-phase DAB converter is favored for its lower capacitor volume and higher power density [14, 15]. Details of three-phase DAB converter will be explained in Chapter 3. The main parameters of the DAB converter include transformer turn ratio n, switching frequency f, and leakage inductance  $L_k$ . For a fixed set of parameters, the performance at different operating conditions (corresponding to different LV battery voltage and output power level) are quite different and need to be considered comprehensively in the design stage. Some optimization methods have been proposed for single-phase DAB converter. For example, in [20], the control variables are optimized to achieve highest efficiency for given parameters. The combination of selectable parameters (f,  $L_k$ ) and ( $L_k$ , n) are studied in [21] and [22] respectively to achieve the tradeoff between converter efficiency and its volume. However, no comprehensive study that deals with the impacts of all the selectable parameters (n, f,  $L_k$ ) on three-phase DAB performances, including ZVS range, converter efficiency and capacitor ripple current, are conducted.

In order to provide galvanic isolation, transformers must be incorporated between HV and LV side, as well as step up/down the output voltage to a proper level. However, they take up significant volume in the converter. The planar type transformer is advantageous to achieve a compact package. Due to the utilization of planar magnetic cores and windings as copper foils or printed circuit board (PCB), the converter profile can be reduced considerably. In addition, the manufacture process is also significantly simplified, and consistency of the transformers between unit to unit is also improved [23 - 25].

With the development of semiconductor devices, the switching frequency has been extended to hundreds of kilohertz (kHz) or even megahertz (MHz), which helps reduce

the size of magnetic components significantly. However, the transformer design is a great challenge. At high frequency, extra eddy current losses are introduced in the windings, which is difficult to estimate using traditional analysis. The increased parasitic parameters in planar transformer may also impact the converter performance [23], which should be taken into consideration in the transformer design.

#### **1.2. OBJECTIVES**

For smart home application, the DC/DC converter applied between HV DC bus and LV batteries requires high efficiency and power density. The converter performance is related to its parameters, and this should be considered in the converter design. Planar transformer is beneficial to achieve low profile and improve power density, and the design related issues should be addressed. The main objectives of this thesis are listed as below:

A comprehensive parameter selection for the three-phase DAB converter design is the first research objective. Considering the design of three-phase DAB converter, a comprehensive study of the impacts of all the selectable parameters on the converter performance are needed, including transformer turns ratio n, switching frequency f, and leakage inductance  $L_k$ . The ZVS range, converter efficiency and capacitor ripple current should be investigated under different voltage and power levels.

Planar transformer design for the three-phase DAB converter is the second research objective of this thesis. The impact of non-sinusoidal excitation waveform on magnetic core selection and core loss calculation needs to be considered. In high frequency application, the effect of winding design and arrangement need to be investigated in the aspects of AC resistance, leakage inductance and stray capacitance.

### **1.3. THESIS OUTLINE**

This thesis is organized as follows:

Chapter 2 presents a brief overview of the planar transformer as well as the related issues. The advantages and disadvantages of adopting planar transformer are discussed. Different types of planar core shape and material, as well as planar windings are presented. The eddy current effect due to the high operating frequency and the resulting AC resistance are also overviewed. Finally, the parasitic parameters and their impacts on the transformer performances are discussed.

Chapter 3 explains the basic configuration and operation characteristics of three-phase DAB converter. The operating scheme, waveforms as well as control strategy are discussed. The current stress of switches, ZVS condition and the ripple current through DC capacitors are presented in closed forms.

Chapter 4 presents comprehensive design considerations of three-phase DAB converter. The impact of parameters  $(n, f, L_k)$  on the converter performances, including ZVS operation area, switching device power losses, capacitor ripple current and system efficiency are studied. By taking different operating conditions into consideration, feasible range of the selectable parameters are determined to achieve overall high performance.

Chapter 5 presents the planar transformer design for the three-phase DAB converter. The transformer core is selected based on its power handling capability taking the excitation waveform into consideration. Winding design and arrangement are presented by considering their impacts on eddy current effect and parasitic parameters. The performances of the designed transformer are validated in ANSYS Maxwell 2D and 3D. Chapter 6 presents the implementation of the transformer prototype and the experimental performance of the three-phase DAB converter with the transformer prototype.

Chapter 7 concludes the thesis and presents the possible future work.

## Chapter 2 PLANAR TRANSFORMERS

### 2.1. OVERVIEW OF PLANAR TRANSFORMER

The desire for high power density and high efficiency power converters in industrial applications encourages the development of high frequency switching devices. As the switching frequency increases, the size of passive components, such as capacitors, inductors and transformers, can be significantly reduced. The use of conventional wire-wound transformers is becoming a big obstacle in applications that require low profile. In recent years, planar transformer has become increasingly popular in high frequency applications due to its lower profile, excellent thermal characteristics, good repeatability and easy manufacturing process [23, 26, 27].

### 2.1.1. Magnetic Cores

The key parameters of the core material include the saturation flux density, core loss and effective permeability. Materials with high saturation level and lower core loss are desired to reduce the core size and the temperature rise. High permeability is desired for higher magnetizing inductance and lower reluctance in magnetic path [25, 27].

Silicon steel is widely used in low frequency applications with high saturation (> 1.8 T). To further reduce the core losses, laminated magnetic steel is employed to mitigate the eddy current effect [28].For high frequency application, different magnetic materials are compared in Table 2.1. Ferrite core is widely used due to its high permeability and

resistivity. However, the saturation flux density is relatively low (0.39 T @ 100 °C), which may results in a large core size. The amorphous material features high saturation level and high permeability, which help improve power density. However, it also has the highest loss density compared to other materials [29]. Nanocrystalline forms metallic tape-wounded core, which exhibits high saturation flux density and lower loss density. Thus higher power density and efficiency can be achieved with nanocrystalline core, but the cost is higher [30 - 32].

| Material type                           | Ferrite | Nanocrystalline | Amourphous |

|-----------------------------------------|---------|-----------------|------------|

| Manufacturer                            | N87     | FT-3M           | 2705M      |

|                                         | Epcos   | Hitachi         | Metglas    |

| Saturation flux density $B_{sat}(T)$    | 0.39    | 1.23            | 0.77       |

| Effective permeability $\mu_e$          | 1490    | 15 000          | 290 000    |

| Core loss density (W/kg) (100kHz, 0.2T) | 77      | 41              | 100        |

Table 2.1 Comparison of magnetic material properties

Ferrite material can be sintered into different core shapes, such as planar E, ER, RM and PQ cores. These core shapes feature very low profile, as shown in Fig. 2.1 (a), and they are commonly applied in high frequency power electronics applications. Nanocrystalline and amorphous material are commonly formed as toroidal cores and C cores, as shown in Fig. 2.1(b).

Compared to the wire-wound transformers, the planar cores with same power capability is usually 25% to 50% less in height [23]. A fair comparison of conventional

(EE 35/18/10) and planar core structure (EE 38/8/25) with similar power rating is given in Fig. 2.2. With lower profile, planar core has greater ratio between surface area and the core volume. As more surface area is attached to heatsink or exposed to air, more effective heat conducting and smaller thermal resistance can be achieved [24]. However, along with the low profile and good thermal performance, the large footprint area it occupies is an issue of planar transformer.

Fig. 2.1. Core geometry (a) planar E, ER, RM and PQ core (b) toroidal and C core [33, 34].

Fig. 2.2. Comparison of planar and wire-wound structure.

### 2.1.2. Planar Windings

The windings in planar transformers are usually constructed using PCB based windings and/or copper foils, as shown in Fig. 2.3 (a). Multilayer PCB provides a good solution for highly integrated windings with dielectric substrate. Stamped copper foils are

usually used in high current applications, where insulation film is applied between winding layers. To form parallel or series connection, extra connection between terminations of each layer is also needed, as depicted in Fig. 2.3 (b) and (c) [23, 24].

By applying multilayer PCB or copper foil windings, manufacturing can be simplified since manual or complex automatic wire-wound process are no longer needed. Repeatable and consistent manufacture is much easier to achieve, which is perfectly suitable for modular power converters or multi-phase converters where identical parameters are required. The thickness of flat conductors can be reduced to skin depth, which helps mitigate skin effect and reduce copper losses in high frequency applications [35]. Additionally, the transformer can be modeled in FEA simulation with high fidelity, and its performance can be predicted with high accuracy. Hence the design and validation of planar transformer are also simplified.

Fig. 2.3. Different implementation structure of planar windings [36, 37].

The use of PCB winding or copper foils also provides flexibility to interleave the primary and secondary windings, which reduce the leakage inductance and proximity effect significantly [23, 24, 38]. For example, two different winding arrangements and their magnetomotive force (MMF) distributions along the vertical direction of the windings are illustrated in Fig. 2.4. Taking advantage of the proximity effect, interleaved windings have more evenly distributed current. As a result, lower copper losses and leakage inductance are achieved. The effect of interleaving will be discussed in detail in next section.

Compared to wire-wound windings, the major drawback of planar windings is the lower utilization factor (0.18 to 0.25) [23, 39]. Due to the dielectric spaces required between turns, the number of turns and width of traces are also limited, hence the DC

resistance is increased. Additionally, the large overlap between planar windings results in increased stray capacitance, which is not desired in most applications [38].

#### 2.2. TRANSFORMER LOSSES

#### 2.2.1. Core Loss

There are mainly three methods to determine core losses: hysteresis model, loss separation approach [40, 41] and empirical methods. The first two approaches characterize satisfactory results but require excessive computations to extract the parameters in the models. The Steinmetz equation [42, 43] is the commonly used empirical method to characterize core losses.

$$p_{v} = KB_{m}^{\alpha} f^{\beta} \tag{2.1}$$

where,  $p_v$  is the core loss density. The core loss coefficient *K*,  $\alpha$ ,  $\beta$  can be obtained by curve fitting of the measured core losses provided by manufacturers, and  $\alpha < \beta$ .

#### 2.2.2. Copper Loss

In high frequency applications, the transformer performance is significantly impaired by eddy current effect, including skin effect and proximity effect. Both skin and proximity effect causes non-uniformly current distribution in the cross-section of the conductor, hence decreases the effective cross-section area and increases the resistance of the windings. This leads to dramatically higher copper losses at higher frequency.

When high frequency current flows through a conductor, according to Lenz's law, the alternating flux in the conductor will induce eddy current, which tends to oppose the alternating flux. Therefore, as shown in Fig. 2.5 (a), in the center of the conductor, the eddy current is in opposite direction to the main current i(t); while at the surface of the conductor, the eddy current and main current share the same direction. This results in increased current density near the conductor surface. Based on Maxwell's equation [44], the current distribution within the conductor can be obtained. The current density decreases exponentially along the radius distance to the center of the conductor, and mainly distributed within the skin depth  $\delta$  of the conductor. At a certain frequency, the skin depth is given as

$$\delta = \sqrt{\frac{1}{\pi f \,\mu_0 \sigma}} \tag{2.2}$$

where,  $\mu_0 = 4\pi x 10^{-7}$  H/m is the vacuum permeability,  $\sigma = 5.7 x 10^{7}$  S/m is the copper conductivity.

The proximity effect shows similar characteristics. Take two flat conductors in Fig. 2.5 (b) with opposite current as an example, the flux induced by current  $i_A(t)$  further induces current in the adjacent conductor, which tends to oppose the AC flux. Therefore, current density is increased on the adjacent sides and decreased at the opposite side of the conductors.

AC resistance  $R_{ac}$  is the effective resistance that generate copper losses. Dowell's equation is the most commonly used method in characterizing copper loss. As the planar winding structure features high width to thickness ratio, it can be regarded as infinite foil conductor. Under sinusoidal excitation, the current density distribution within the planar conductor can be solved by general field solutions. Based on Dowell's assumption, the

eddy current effect can be represented by the ratio between AC resistance and DC resistance of a single (*m*th) layer [45 - 47], as shown in (2.3).

$$\frac{R_{ac,m}}{R_{dc,m}} = \frac{\xi}{2} \left[ \frac{\sinh \xi + \sin \xi}{\cosh \xi - \cos \xi} + (2m-1)^2 \cdot \frac{\sinh \xi - \sin \xi}{\cosh \xi + \cos \xi} \right]$$

(2.3)

where  $\xi = h/\delta$ , *h* is the conductor thickness, the DC resistance  $R_{dc} = \rho l/A_s$ ,  $\rho$  is the copper resistivity, *l* is the winding total length,  $A_s$  is the cross-section of the winding. The ratio *m* is related to winding arrangement and it is defined as

$$m = \frac{F(h)}{F(h) - F(0)}$$

(2.4)

where F(h) and F(0) are the MMF at the vertical edges of a layer, which is also annotated in Fig. 2.4. The first term in (2.3) represents the skin effect, and the second term refers to proximity effect. The ratio between AC and DC resistance not only depends on  $\xi$ , but also relates to the ratio *m*, and their relationship can be plotted in Fig. 2.6 (a).

Fig. 2.5. Eddy current effect (a) skin effect (b) proximity effect.

Fig. 2.6. (a) Ratio of AC to DC resistance (b) ratio between AC and DC resistance with thickness of skin depth.

As indicated in Fig. 2.6 (a), the resistance ratio  $R_{ac}/R_{dc}$  increases dramatically with conductor thickness, which makes the selection of conductor thickness a key parameter in winding design. At a large ratio *m*, the proximity effect dominates over skin effect and increases the resistance dramatically. With reduced conductor thickness ( $\xi < 1$ ), the resistance ratio decreases to 1, which suggests a low eddy current effect. The absolute AC resistance is calculated referred to the DC resistance when  $h = \delta$  ( $\xi = 1$ ).

$$\frac{R_{ac}}{R_{dc}(\xi=1)} = \frac{R_{ac}}{R_{dc}} \cdot \frac{1}{\xi}$$

(2.5)

Substituting (2.3) to (2.5), the ratio  $R_{ac}/R_{dc}$  ( $\xi = 1$ ) can be obtained and plotted in Fig. 2.6 (b). From Fig. 2.6 (b), at given frequency and specified winding arrangement (corresponding to different ratio *m*), minimal AC resistance can be achieved by properly choosing conductor thickness [43]. To better estimate AC resistance with finite foil conductor and nonsinusoidal excitation, the correction factor is given in [46, 47]. More accurate AC resistance can be obtained by FEA simulation.

## 2.3. PARASITIC EFFECTS

#### 2.3.1. Leakage Inductance

In a typical transformer, the magnetic flux generated by current in the primary winding is supposed to follow the magnetic circuit and link with the secondary winding, and vice versa [48, 49]. Realistically, although the main flux follows the magnetic path, some flux leaks from the core and returns to the air, the winding layers and insulation layers without linking the secondary winding. This imperfect flux coupling results in leakage inductance. The main flux and leakage flux paths are shown in Fig. 2.7. Almost all of the leakage energy is stored within the window area, and it can be calculated by integrating the energy density within this region.

$$E_{Lk} = \int_{V} \frac{1}{2} B H dV = \frac{1}{2} L_{k} I^{2}$$

(2.6)

where the field intensity  $H = F/b_w = NI/b_w$ , flux density  $B = \mu_0 H$ , NI is the MMF distribution of each layer, and the differential volume  $dV = l_w \cdot b_w \cdot dx$ ,  $l_w$  and  $b_w$  are the core window area length and width, dx is the vertical distance to the reference surface of each layer, as indicated in Fig. 2.4 [49].

Fig. 2.7. Main flux and leakage flux paths.

The leakage inductance is related to the MMF distribution, which varies with different winding arrangements. For a non-interleaved winding structure in Fig. 2.4 (a), the leakage energy stored in all layers (primary, secondary and insulation layers) can be calculated as

$$E_{Lk} = \frac{\mu_0}{2} \sum_{k=0}^{h} H^2 \cdot l_w \cdot b_w \cdot dx$$

(2.7)

where, the field intensity H depends on the ampere-turns (*NI*) linked with the leakage flux path. The field intensity H in the primary winding in Fig. 2.4 can be expressed as (2.8) [48].

$$H = \begin{cases} \frac{(k-1)I}{b_{w}} + \frac{I}{b_{w}} \cdot \frac{x - (k-1)(h_{1} + h_{\Delta})}{h_{1}} & (k-1)(h_{1} + h_{\Delta}) < x \le h_{1} + (k-1)(h_{1} + h_{\Delta}) \\ k \frac{I}{b_{w}} & h_{1} + (k-1)(h_{1} + h_{\Delta}) < x \le k(h_{1} + h_{\Delta}) \end{cases}$$

(2.8)

where the thickness of primary, secondary and insulation layer are  $h_1$ ,  $h_2$  and  $h_{\Delta}$ , and they are indicated in Fig. 2.4. Substituting *H* to (2.7), the total leakage energy can be derived as

$$E_{Lk} = \frac{\mu_0}{2} \cdot l_w \cdot b_w \left[ 4 \int_0^{h_1} \left( \frac{I}{b_w} \cdot \frac{x}{h_1} \right)^2 dx + 4 \int_0^{h_2} \left( \frac{I}{b_w} \cdot \frac{x}{h_2} \right)^2 dx + \frac{\left(I^2 + 4I^2 + 9I^2\right)}{b_w^2} \cdot \left( h_1 + h_2 + 2h_\Delta \right) + \frac{\left(I^2 + 2I^2 + 3I^2\right)}{b_w^2} \cdot \left( h_1 + h_2 \right) + \frac{16I^2}{b_w^2} \cdot h_\Delta \right]$$

(2.9)

Therefore, the closed form of total leakage inductance in Fig. 2.4 (a) can be expressed by [43]

$$L_{k} = \mu_{0} \cdot \frac{l_{w}}{b_{w}} \left[ \frac{64(h_{1} + h_{2})}{3} + 44h_{\Delta} \right]$$

(2.10)

For the fully interleaved winding arrangement in Fig. 2.4 (b), the field intensity H is much lower. By applying similar approach, the leakage inductance can be derived as

$$L_{k} = \mu_{0} \cdot \frac{l_{w}}{b_{w}} \cdot 4 \left[ \frac{(h_{1} + h_{2})}{3} + h_{\Delta} \right]$$

(2.11)

It is obvious that interleaved winding layout has significant advantage in reducing leakage inductance. The layer thickness ( $h_1$ ,  $h_2$  and  $h_{\Delta}$ ) can also be used to adjust the leakage inductance.

#### 2.3.2. Stray Capacitance

In planar transformers, the windings are compactly placed in the core window area with a large overlap between adjacent layers. The small distance between windings results in significant inter-and intra-winding capacitance [50, 51].

The high inter-winding capacitance between primary and secondary windings provides a low impedance path for the high-frequency current, which can cause serious common mode (CM) problems and contribute to electromagnetic interference (EMI) issues. In addition, self-resonance might happen between the leakage inductance and stray capacitance, which results in voltage spike across the switches and deteriorate the converter performance [52 - 54].

A complete equivalent circuit of the planar transformer with parasitic parameters and winding resistance is illustrated in Fig. 2.8.  $R_p$  and  $R_s$  are the resistances of primary and secondary windings,  $L_{k1}$  and  $L_{k2}$  are the leakage inductance on primary and secondary side,  $L_m$  is the magnetizing inductance,  $C_p$  and  $C_s$  are the intra-winding capacitance of primary and secondary windings, and  $C_{ps}$  is the inter-winding capacitance.

Fig. 2.8. Equivalent circuit of the planar transformer model.

In most applications, small stray capacitance is desired. The inter- and intra-winding capacitance can be reduced by decreasing overlapping area and/or increasing distance between two layers. However, this will reduce the window utilization factor and increase winding DC resistance. Different insulation thickness ( $h_{\Delta}$ ) can be applied between layers to tune the capacitance value. In some transformer designs, zero voltage gradient is applied between two paralleled layers, thus these layers can be placed very close to each other without generate any intra-winding capacitance [53]. Additionally, reducing the interleaving level between primary and secondary windings can decrease the inter-winding capacitance.

#### 2.4. SUMMARY

This chapter gives an overview of planar transformer. The advantage and disadvantage of planar transformer are discussed. The most commonly used core material, core geometry and winding structures are presented. Transformer losses and parasitic parameters, including core loss, copper loss, leakage inductance and stray capacitance are discussed.

# Chapter 3 THREE-PHASE DUAL ACTIVE BRIDGE CONVERTER

#### **3.1. BASIC CONFIGURATION**

The basic configuration of a three-phase DAB converter is depicted in Fig. 3.1 [14]. A three-phase high frequency transformer with turn ratio *n* is connected between the AC link of two three-phase active bridges to provide galvanic isolation and enable bidirectional power flow.

In smart home application, the primary side is connected with LV battery pack, and the secondary side is the HV DC link, which is connected to the grid through a DC/AC inverter. Three symmetrical auxillary inductors (corresponding to the leakage inductance  $L_k$ ) are usually connected on the HV side to enable power transfer between the primary and secondary side.

Fig. 3.1. Basic configuration of three-phase DAB converter.

#### **3.2. OPERATING SCHEME**

Phase shift modulation is the commonly used control strategy for DAB converter, and it has good performance at nominal operating condition. However, due to voltage variation of LV batteries, the voltage ratio between primary and secondary side may not match the transformer turn ratio. In that case, hard switching may occur and significantly increase the switching losses. For single-phase DAB converter, advanced modulation strategies [16 - 19, 55, 56] have been proposed to improve the overall efficiency. However, for three-phase DAB converter, due to fixed phase shift (120 °) angle between phases, the advanced modulations are not applicable.

During operation, the switches in one phase leg are driven by complementary signals with 50% duty cycle, and the three half bridges are operated with 120° phase shift. Subtracting the square waveform  $v_{AO}$  or  $v_{ao}$  by the zero-sequence voltage  $v_{pO}$  or  $v_{so}$  in Fig. 3.1, the phase voltage of the transformer is derived. As shown in Fig. 3.2, six-step line-toneutral voltage waveforms are imposed on both side of the transformer, where  $v_{Ap'}$  is referred to the HV side.

A phase shift angle  $\phi$  is applied between primary and secondary voltage, and the voltage difference across  $L_k$  is generated. The waveforms of the other two phases are identical with 120 ° phase delay.

For power transfer from primary to secondary side (P > 0), the relationship between the phase shift and transmitted power is given as (3.1) [22]. For reverse power flow (P < 0), the operating waveforms are symmetrical but the primary side is delayed with respect to secondary side, i.e.,  $\phi < 0$  is applied [57, 58].

Fig. 3.2. Operating waveforms of three-phase DAB converter (a)  $\phi \le \pi/3$  (b)  $\phi > \pi/3$ .

$$P = \begin{cases} \frac{nV_1V_2}{12\pi^2 fL_k} \cdot \phi(4\pi - 3\phi) & 0 \le \phi \le \frac{\pi}{3} \\ \frac{nV_1V_2}{36\pi^2 fL_k} \cdot (18\phi^2 - 18\pi\phi + \pi^2) & \frac{\pi}{3} < \phi \le \frac{2\pi}{3} \end{cases}$$

(3.1)

where, f is the switching frequency, n is the transformer turn ratio,  $V_1$  and  $V_2$  are the DC voltage of primary and secondary side, respectively.

As shown in (3.1), when  $0 < \phi \le \pi/3$ , the output power increases monotonically with phase shift  $\phi$ ; when  $\pi/3 < \phi \le 2\pi/3$ , the output power first increases with  $\phi$  and reaches its maximum at  $\phi = \pi/2$ , and then decreases after  $\phi > \pi/2$ .  $\phi > \pi/2$  is not adopted since it leads to increased reactive power and higher RMS current. Therefore, for a desired transmission power *P*, the phase shift  $\phi$  can be calculated as (3.2).

$$\phi = \begin{cases} \frac{2\pi}{3} (1 - \sqrt{1 - \frac{9fL_kP}{nV_1V_2}}) & 0 \le P \le P_{\max 1} \\ \frac{\pi}{6} (3 - \sqrt{7 - \frac{72fL_kP}{nV_1V_2}}) & P_{\max 1} < P \le P_{\max 2} \end{cases}$$

(3.2)

where,  $P_{\text{max1}}$  (=  $nV_1V_2/12fL_k$ ) is achieved at  $\phi = \pi/3$ , and  $P_{\text{max2}}$  (=  $7nV_1V_2/72fL_k$ ) is achieved at  $\phi = \pi/2$ .

#### 3.3. ZERO-VOLTAGE-SWITCHING CONDITION

The turn-on currents of the switches on the primary and secondary side are indicated in Fig. 3.2 as  $i_0$  and  $i_{\phi}$ . ZVS turn-on can be achieved when the body diode of the switch is conducting before turned on, and thus the voltage across the switch is nearly zero. The sufficient constraints for ZVS turn-on are derived as: negative current  $i_0$  for primary bridges and positive current  $i_{\phi}$  for secondary bridges [58].

$$i_{0} = \begin{cases} \frac{2(V_{2} - nV_{1}) - 3V_{2}\phi / \pi}{18fL_{k}} \leq 0 & 0 \leq P \leq P_{\max 1} \\ \frac{(3V_{2} - 2nV_{1}) - 6V_{2}\phi / \pi}{18fL_{k}} \leq 0 & P_{\max 1} < P \leq P_{\max 2} \\ \frac{2(V_{2} - nV_{1}) + 3nV_{1}\phi / \pi}{18fL_{k}} \geq 0 & 0 \leq P \leq P_{\max 1} \\ \frac{(2V_{2} - 3nV_{1}) + 6nV_{1}\phi / \pi}{18fL_{k}} \geq 0 & P_{\max 1} < P \leq P_{\max 2} \end{cases}$$

(3.3)

## 3.4. SWITCH AND CAPACITOR CURRENT STRESS

The expression of the piecewise current  $i_{Lk}$  is derived from the voltage across the leakage inductance  $v_{Lk}$  [14]. The peak current of switches and transformers in Fig. 3.2 can be derived as

$$i_{pk} = \begin{cases} \begin{cases} \frac{V_2 - nV_1 + 6nV_1\phi/\pi}{18fL_k} & nV_1 \leq V_2 \\ \frac{nV_1 - V_2 + 6V_2\phi/\pi}{18fL_k} & nV_1 > V_2 \end{cases} & 0 \leq \phi \leq \frac{\pi}{3} \\ \begin{cases} \frac{nV_1 + 3V_2\phi/\pi}{18fL_k} & nV_1 > V_2 \\ \frac{V_2 + 3nV_1\phi/\pi}{18fL_k} & nV_1 > V_2 \end{cases} & \frac{\pi}{3} < \phi \leq \frac{2\pi}{3} \end{cases}$$

(3.4)

Similarly, the RMS current flowing through the leakage inductor  $I_{rms\_Lk}$  can be obtained by integrating the current square in one switching period.

$$I_{rms\_Lk} = \begin{cases} \frac{\sqrt{-9nV_1V_2\phi^3 + 18\pi nV_1V_2\phi^2 + 5\pi^3(nV_1 - V_2)^2/3}}{18fL_k\pi^{3/2}} & 0 \le \phi \le \frac{\pi}{3} \\ \frac{\sqrt{nV_1V_2(-18\phi^3 + 27\pi\phi^2 - 3\pi^2\phi) + \pi^3(5n^2V_1^2/3)}}{\sqrt{18fL_k\pi^{3/2}}} & \frac{\pi}{3} < \phi \le \frac{2\pi}{3} \end{cases}$$

(3.5)

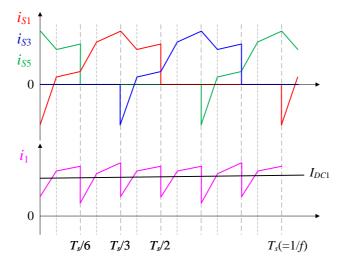

Corresponding to Fig. 3.2 (a), the current flowing through the upper switches  $S_1$ ,  $S_3$  and  $S_5$  on the primary side are depicted in Fig. 3.3. Because the switches conduct half of the switching period, the RMS current through switches  $I_{rms_sw}$  can be calculated by (3.6).

$$I_{rms\_sw} = I_{rms\_Lk} / \sqrt{2}$$

(3.6)

The input current  $i_1$  in Fig. 3.1 is obtained by combining the current of the three upper switches, which is also shown in Fig. 3.3. The output current  $i_2$  can be obtained

similarly by adding the current flowing through the upper switches on the secondary side  $(Q_1, Q_3 \text{ and } Q_5)$ . The RMS value of  $i_1$  and  $i_2$  is expressed by (3.7) [22].

Fig. 3.3. Input current and current through switches.

$$I_{rms1} = \begin{cases} \frac{n}{18 f L_k} \sqrt{\frac{-9V_2 (2nV_1 + 3V_2) \cdot (\phi/\pi)^3}{+9V_2 (nV_1 + 3V_2) \cdot (\phi/\pi)^2 + (nV_1 - V_2)^2/3}} & 0 \le \phi \le \frac{\pi}{3} \\ \frac{n}{18 f L_k} \sqrt{\frac{-36nV_1V_2 \cdot (\phi/\pi)^3 + 27V_2 (2nV_1 - V_2) \cdot (\phi/\pi)^2}{+3V_2 (9V_2 - 8nV_1) \cdot (\phi/\pi) + (n^2V_1^2 + 9nV_1V_2 - 11V_2^2)/3}} & \frac{\pi}{3} < \phi \le \frac{2\pi}{3} \end{cases}$$

$$I_{rms2} = \begin{cases} \frac{1}{18 f L_k} \sqrt{\frac{-9nV_1 (3nV_1 + 2V_2) \cdot (\phi/\pi)^3}{+9nV_1 (3nV_1 + V_2) \cdot (\phi/\pi)^2 + (nV_1 - V_2)^2/3}} & 0 \le \phi \le \frac{\pi}{3} \end{cases}$$

$$0 \le \phi \le \frac{\pi}{3}$$

$$0 \le \phi \le \frac{\pi}{3}$$

$$0 \le \phi \le \frac{\pi}{3}$$

$$\frac{1}{18 f L_k} \sqrt{\frac{-9nV_1 (3nV_1 + V_2) \cdot (\phi/\pi)^3 + 27nV_1 (nV_1 - 2V_2) \cdot (\phi/\pi)^2}{+3nV_1 (9nV_1 - 8V_2) \cdot (\phi/\pi) + (V_2^2 + 9nV_1V_2 - 11n^2V_2^2)/3}} & \frac{\pi}{3} < \phi \le \frac{2\pi}{3} \end{cases}$$

Substituting the RMS value in (3.7) with their DC components,  $I_{DC1} = P/V_1$  (input current) and  $I_{DC2} = P/V_2$  (output current), the RMS value of the ripple current through the DC capacitors C<sub>1</sub> and C<sub>2</sub> can be obtained by (3.8).

$$I_{rms_c1} = \sqrt{I_{rms_1}^2 - I_{DC1}^2}, \ I_{rms_c2} = \sqrt{I_{rms_2}^2 - I_{DC2}^2}$$

(3.8)

# 3.5. SUMMARY

This chapter presents the basic configuration and operating principles of the threephase DAB converter. The sufficient conditions of ZVS turn-on is analyzed and presented. The closed form of the peak and RMS current of both switches and the DC capacitors are also obtained.

# Chapter 4 THREE-PHASE DUAL ACTIVE BRIDGE CONVERTER DESIGN CONSIDERATIONS

#### 4.1. KEY INFLUENCE OF TURN RATIO

The analysis of three-phase DAB converter in (3.1) - (3.8) indicates that the parameters *f* and *L<sub>k</sub>* together influence the characteristics of the converter. To simplify the analysis, a new parameter *fL* is defined here in (4.1). Based on this, the impacts of parameters *n* and *fL* on the ZVS boundary, RMS current and ripple current through DC capacitor are studied respectively.

$$fL = f \cdot L_k / fL_{base} \tag{4.1}$$

where,  $fL_{base} = 7n_{max}V_{1min}V_2/72P_N$ ,  $n_{max} = 10$ ,  $V_{1min} = 40$  V and  $V_2 = 400$  V.

Due to the voltage variation of LV batteries, the performance of the converter under a wide voltage range and different power ratings need to be considered. To reduce computation efforts, 9 different LV side voltages, and 2 different output power levels (full load and half load) are chosen to represent different operating conditions.

$$V_1 = [40, 42, 44, 46, 48, 50, 52, 54, 56]^T V, V_2 = 400 V, P = [5, 10]^T kW$$

#### 4.1.1. Zero-Voltage-Switching Boundary

At full load, ZVS is desired at any voltage level of  $V_1$ . In order to find the worst input voltage that limits the ZVS range, the maximum value of  $i_0$  and minimum value of  $i_{\phi}$  need

to be considered. By substituting (3.2) into (3.3), the derivative of  $i_0$  and  $i_{\phi}$  with respect to  $V_1$  can be obtained.

$$\frac{\partial i_{0}}{\partial V_{1}} = \begin{cases} n \cdot \frac{3 fLP / (nV_{1})^{2} - 2 \sqrt{1 - 9 fLP / nV_{1}V_{2}} / 3}{6 fL \cdot \sqrt{1 - 9 fLP / nV_{1}V_{2}}} < 0 & 0 \le P \le P_{\max 1} \\ n \cdot \frac{12 fLP / (nV_{1})^{2} - 2 \sqrt{7 - 72 fLP / nV_{1}V_{2}} / 3}{6 fL \cdot \sqrt{7 - 72 fLP / nV_{1}V_{2}}} > 0 & P_{\max 1} < P \le P_{\max 2} \\ \frac{\partial i_{\phi}}{\partial V_{1}} = \begin{cases} -\frac{n \cdot (2 - 9 fLP / nV_{1}V_{2})}{18 fL \cdot \sqrt{1 - 9 fLP / nV_{1}V_{2}}} < 0 & 0 \le P \le P_{\max 1} \\ -\frac{n \cdot (7 - 36 fLP / nV_{1}V_{2})}{18 fL \cdot \sqrt{7 - 72 fLP / nV_{1}V_{2}}} < 0 & P_{\max 1} < P \le P_{\max 2} \end{cases} \end{cases}$$

(4.2)

From (4.2), when  $P \leq P_{max1}$ ,  $i_0$  decreases monotonically with  $V_1$ , and the maximum value of  $i_0$  happens at  $V_{1\min}$  (= 40 V);  $i_{\phi}$  decreases with  $V_1$ , and the minimum value of  $i_{\phi}$  happens at  $V_{1max}$  (= 56 V). If the converter operates at  $\pi/3 < \phi \leq \pi/2$ , i.e.,  $P_{max1} < P \leq P_{max2}$ ,  $i_0$  increases with  $V_1$ , and  $i_{0max}$  will happen at  $V_{1max}$ ;  $i_{\phi}$  keeps decreasing with  $V_1$ , and  $i_{\phi\min}$  happens at  $V_{1max}$ .

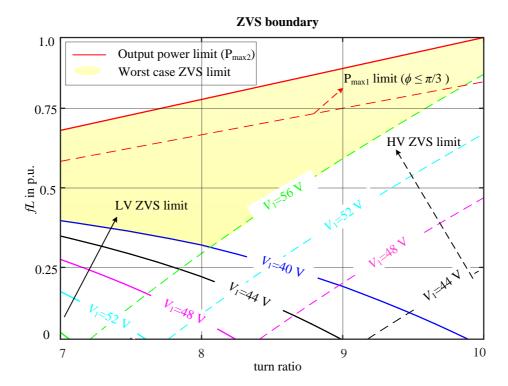

The converter only operates at  $\pi/3 < \phi \le \pi/2$  when  $V_1$  is lower. In most input voltages when  $V_1$  is higher, the converter operates at  $\phi \le \pi/3$ . Thus  $i_{0\text{max}}$  can be considered happening at  $V_{1\text{min}}$ , and  $i_{\phi\text{min}}$  happens at  $V_{1\text{max}}$ . A visualized solution is shown in Fig. 4.1 by solving the ZVS condition at different input voltages at full load.

The feasible range of n and fL which guarantees ZVS at maximum power is highlighted in Fig. 4.1. At higher  $V_1$  and turn ratio n, the LV side ZVS limit (solid line) has a wider range. At lower  $V_1$  and turn ratio n, the HV side ZVS limit (dashed line) features wider range. The applicable value of turn ratio is 7, 8, 9, and n = 8 provides wider range of fL compared to n = 7 and 9.

Fig. 4.1. LV and HV ZVS boundary at different V<sub>1</sub>.

#### 4.1.2. RMS Current

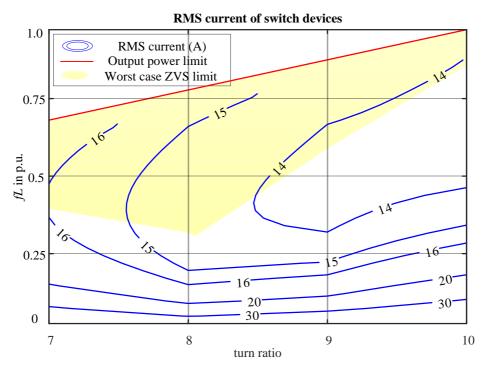

If ZVS is achieved, conduction loss of the switches dominates the total converter losses and the conduction loss is proportional to the square of the RMS current through switches/transformer. Therefore, the characteristics of RMS current versus *n* and *fL* under different voltage level of  $V_1$  are studied. A weighted sum of the RMS current at different input voltages is used to study the variation of conduction loss, where the weight factor  $\alpha_i$ depends on the importance of each operating voltage [59].When equivalent weight factor is applied, the weighted sum of RMS current becomes average RMS current.

$$\overline{I_{rms\_sw}} = \sum_{i} \alpha_{i} I_{rmsi} \quad (\sum_{i} \alpha_{i} = 1)$$

(4.3)

Under different n and fL, the average RMS current of switches is demonstrated in Fig. 4.2. At fixed turn ratio n, as fL increases, the average RMS current first decreases and reaches its minimum; but as fL further approaches its maximum, which is limited by the maximum output power, the RMS current increases again. At fixed fL, the average RMS current is lower at larger turn ratio n.

#### 4.1.3. Ripple Current of DC Link Capacitor

The DC link capacitor smooths the voltage on DC link and absorbs the ripple current. The design of the capacitor is based on the maximum ripple current at all input voltages. From 3.2.3, the closed form of  $I_{rms_c1}$  and  $I_{rms_c2}$  as well as their partial derivative with respect to  $V_1$  is very complex. For given values of *n* and *fL*, the maximum ripple current on both LV and HV side are computed under different input voltage levels. The results are depicted in Fig. 4.3.

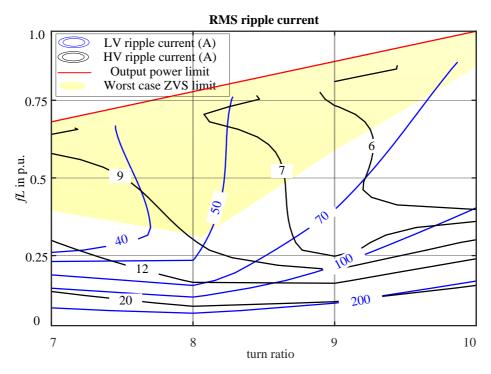

Fig. 4.3. Worst case LV and HV ripple current at different *n* and *fL*.

For a fixed turn ratio *n*, the ripple current on both side decreases as *fL* increases, and reaches its minimum when *fL* approaches its maximum. Within the ZVS area, when n = 7, lower ripple current is achieved on LV side; when n = 9, lower ripple current is achieved on the HV side.

In summary, wider HV side ZVS range and lower LV side capacitor ripple current are achieved at lower turn ratio (n = 7); on the contrary, wider LV side ZVS range and lower HV side ripple current are achieved at higher turn ratio (n = 9). In addition, higher turn ratio n leads to relatively lower RMS current in the switches and transformer, and vice versa.

# 4.2. EFFECTIVE OPERATING AREA OF FREQUENCY AND LEAKAGE INDUCTANCE

At fixed turn ratio n, with the constraints of converter power capability and feasible transformer design, the effective operating area (EOA) defines the feasible range of switching frequency f and leakage inductance  $L_k$ .

#### 4.2.1. Effective Operating Area Limited by Transmission Power

The maximum output power  $P_{\text{max2}}$  has to be higher than the power rating of the converter  $P_N$ . This power requirement should be fulfilled at any input voltage level, thus the upper limit of *fL* is specified by lowest  $V_1$ .

$$f \cdot L_k \le \frac{7 \cdot n \cdot V_{1\min} V_2}{72 P_N} \tag{4.4}$$

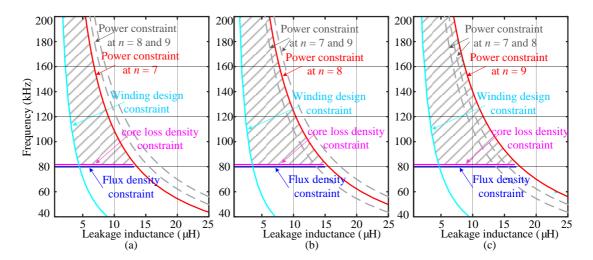

Regarding to different turn ratio, the power constraint are depicted in Fig. 4.4 as red hyperbolic curves. The feasible range of f and  $L_k$  that meets the power requirement is located on the left side of the power constraint curve.

#### 4.2.2. Effective Operating Area Limited by Transformer Design

With the specified magnetic core, the EOA is further constrained by the allowable flux density, the power loss density of the core, and the feasible winding structure design that fits into the core window area. The constraints are given in (4.5) - (4.7).

$$B_m = \frac{V_1}{9fA_e} \le B_{\max} \tag{4.5}$$

$$p_{\nu} = KB_{m}^{\alpha} f^{\beta} \le p_{\nu \max}$$

$$\tag{4.6}$$

$$A_{s} = \frac{I_{rms\_tf}}{J} \le A_{w} \cdot K_{u} / 2 \tag{4.7}$$

where  $A_w$  and  $A_e$  are the core window area and effective area, as shown in Fig. 5.3,  $A_s$  is the cross section of the designed winding. Details of transformer design will be explained in Chapter 5.

Because the leakage inductors are connected to the HV side, LV side voltage waveforms will be applied on flux density and power loss density constraints. The EOA of the converter at different turn ratio are illustrated in Fig. 4.4 as the shaded area. It is observed that the constraints of flux density and core loss density are at the same level for different values of n. The winding design constraint and output power constraint change with the turn ratio.

Fig. 4.4. EOA limited by transmission power and transformer design at (a) n = 7, (b) n = 8 and (c) n = 9.

## 4.2.3. Switch and Capacitor Current Analysis

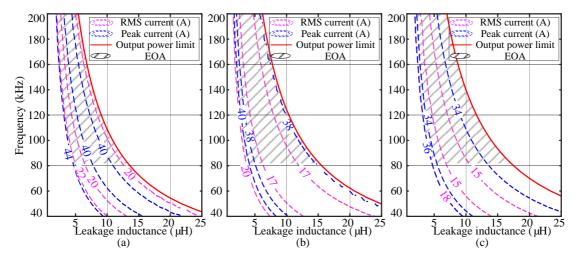

The peak and RMS current of the switches are investigated under 9 different input voltages at full load. The highest current among the 9 input voltages is selected to represent the current stress of the switches, and the results are shown in Fig. 4.5.

Fig. 4.5. Switches current stress analysis at (a) n = 7, (b) n = 8 and (c) n = 9.

Consistent with the analysis in 4.1.2, the peak and RMS current decreases with the increase of the product of f and  $L_k$ , and the minimum value is achieved when f and  $L_k$  are close to the power constraint curve. From Fig. 4.5, it is also observed that for lower turn ratio n, the peak current stress and RMS current is slightly higher.

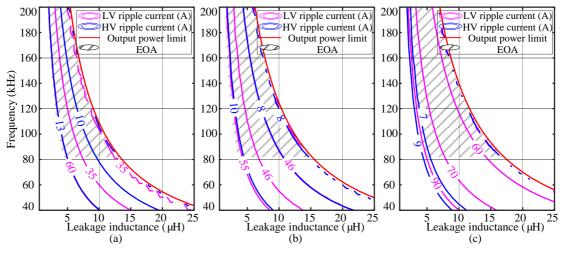

By taking the maximum value of the ripple current among 9 input voltages at full load, the ripple current stress of the DC capacitor at different turn ratio are plotted in Fig. 4.6. Corresponding to Fig. 4.3, the LV and HV ripple current decreases when the product of f and  $L_k$  increases, and reaches their minimum as the value of f and  $L_k$  approaches the power constraint curve. Lower turn ratio leads to higher HV ripple current and lower LV ripple current and vice versa.

Fig. 4.6. Capacitor ripple current analysis at (a) n = 7, (b) n = 8 and (c) n = 9.

#### 4.2.4. MATLAB/Simulink Verification

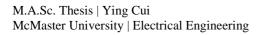

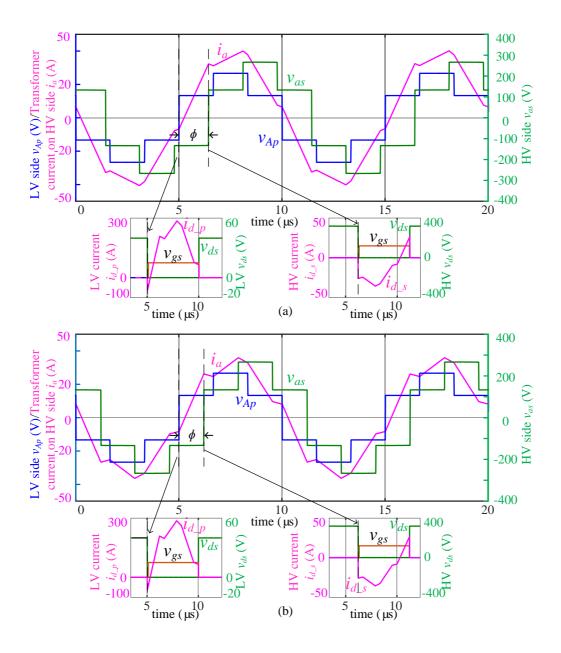

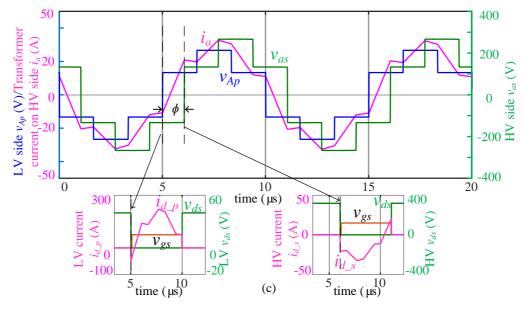

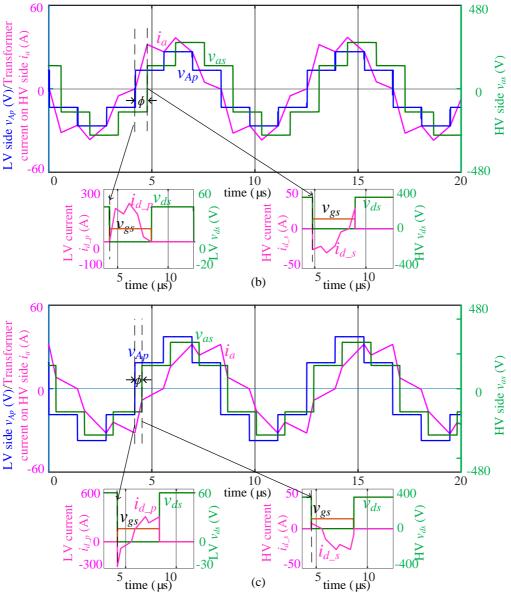

A three-phase DAB converter is built in MATLAB/Simulink to verify the analysis. Three different values of turn ratio n (= 7, 8, 9) and two different combinations of f and  $L_k$  $(f = 100 \text{ kHz}, L_k = 8 \text{ }\mu\text{H} \text{ and } f = 120 \text{ }\text{kHz}, L_k = 4 \text{ }\mu\text{H})$  are selected to compare the impacts of the parameters on the converter performances. For different combinations of  $(n, f, L_k)$ , the simulated voltage and current waveforms at full load are depicted in Fig. 4.7 and Fig. 4.8.

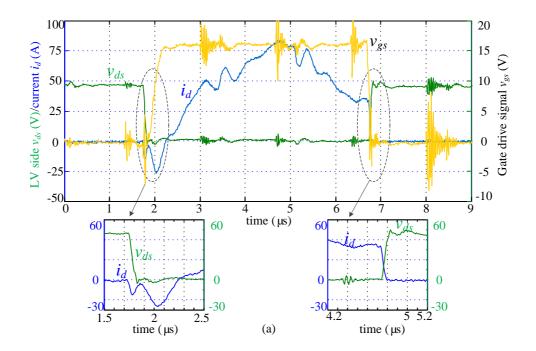

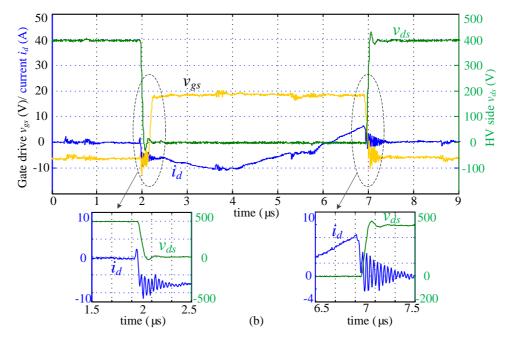

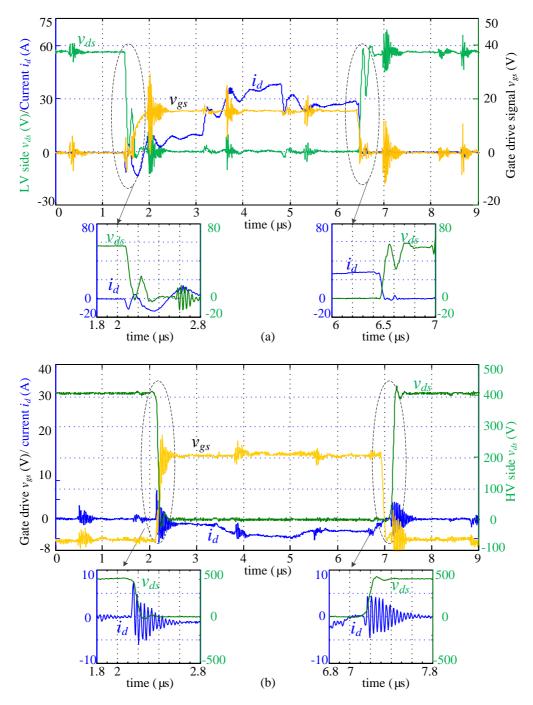

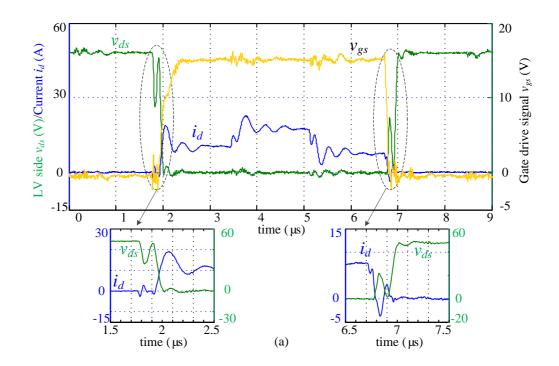

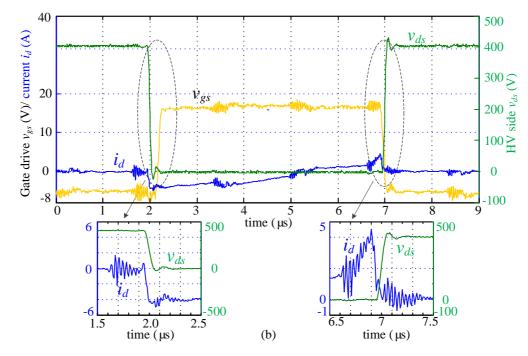

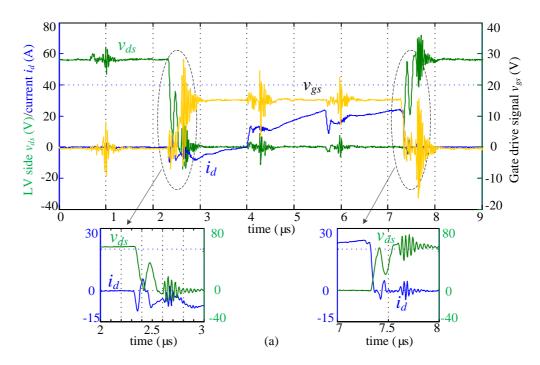

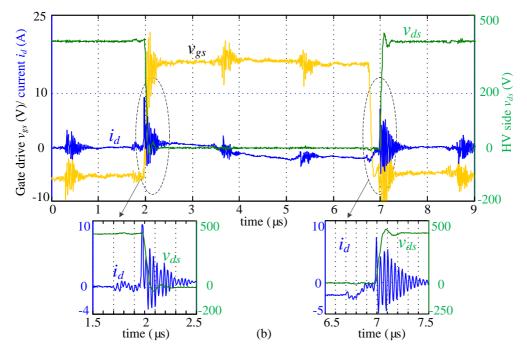

Fig. 4.7 depicts the operating waveforms at  $V_1 = 40$  V with parameters f = 100 kHz and  $L_k = 8$  µH. This parameter combination corresponds to fL = 0.5 p.u. in Fig. 4.1. The ZVS behavior is highlighted in each figure with the gate drive signal  $v_{gs}$ , voltage across the switches  $v_{ds}$  and the current  $i_d$  flowing through it. At the turn-on instant, the negative current flow indicates that ZVS is achieved on both side.

Fig. 4.7. Simulated voltage and current waveforms at (a) n = 7, (b) n = 8 and (c) n = 9 under 100kHz, 8  $\mu$ H.

When the parameters are set as f = 120 kHz and  $L_k = 4 \mu$ H, the operating waveforms are shown in Fig. 4.8, which corresponds to fL = 0.3 p.u. in Fig. 4.1. Consistent with the analysis in 4.1.1, the positive current at the turn-on instant shows ZVS is not achieved on LV side when n = 7 and 8; and when n = 9, ZVS is not realized on HV side.

M.A.Sc. Thesis | Ying Cui McMaster University | Electrical Engineering

Fig. 4.8. Simulated voltage and current waveforms at (a) n = 7, (b) n = 8 and (c) n = 9 under 120kHz, 4  $\mu$ H.

The peak and RMS current of the switches on LV and HV side from MATLAB simulations are summarized in Table 4.1. When f = 100 kHz and  $L_k = 8$  µH, the current stress shows small increase when the turn ratio n decreases. When f = 120 kHz and  $L_k = 4$  µH, significant current increase on the LV side is observed.

|              | Current stress of LV switches (A) |     |               |     | Current stress of HV switches (A) |      |               |      |

|--------------|-----------------------------------|-----|---------------|-----|-----------------------------------|------|---------------|------|

|              | 100 kHz, 8 µH                     |     | 120 kHz, 4 µH |     | 100 kHz, 8 µH                     |      | 120 kHz, 4 µH |      |

|              | Peak                              | RMS | Peak          | RMS | Peak                              | RMS  | Peak          | RMS  |

| <i>n</i> = 7 | 280                               | 135 | 287           | 140 | 39.7                              | 19.3 | 41.4          | 19.9 |

| <i>n</i> = 8 | 289                               | 134 | 374           | 153 | 35.5                              | 16.8 | 46.9          | 19.2 |

| <i>n</i> = 9 | 294                               | 135 | 286           | 163 | 32.5                              | 15   | 31.8          | 18.1 |

Table 4.1 Current stress of switches under different parameters

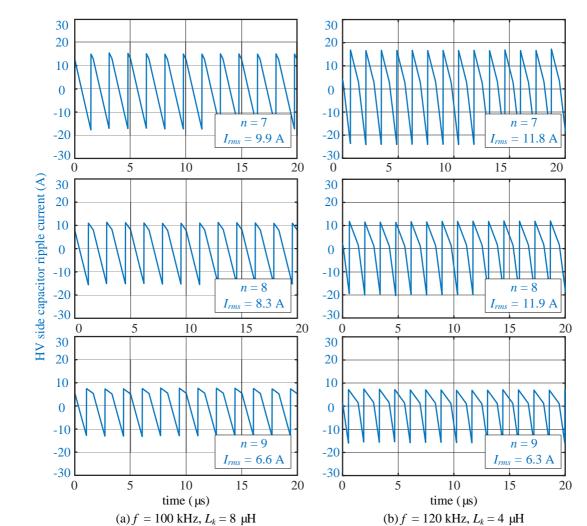

The capacitor ripple currents are also compared under different parameters. The capacitor current waveforms on HV side are shown in Fig. 4.9, corresponding to different parameter combinations. The RMS value of the ripple current on both side are shown in Table 4.2. Consistent with the analysis in 4.2.3, with fixed *f* and  $L_k$ , lower LV ripple current and higher HV ripple current are observed at lower turn ratio, and vice versa. When the parameter *f* = 120 kHz and  $L_k = 4 \mu$ H, higher ripple current is observed on both side compared to the parameter *f* = 100 kHz and  $L_k = 8 \mu$ H.

Table 4.2 Capacitor ripple current under different parameters

|              | LV side ripple cu | urrent (A)    | HV side ripple current (A) |               |  |

|--------------|-------------------|---------------|----------------------------|---------------|--|

|              | 100 kHz, 8 µH     | 120 kHz, 4 µH | 100 kHz, 8 µH              | 120 kHz, 4 µH |  |

| <i>n</i> = 7 | 44                | 47            | 9.9                        | 11.8          |  |

| n = 8        | 51                | 73            | 8.3                        | 11.9          |  |

| <i>n</i> = 9 | 67                | 85            | 6.6                        | 6.3           |  |

M.A.Sc. Thesis | Ying Cui McMaster University | Electrical Engineering

Fig. 4.9. Ripple current of DC capacitors on HV side at different  $(n, f, L_k)$

## 4.3. LOSS ANALYSIS

From the analysis above, trade-offs need to be made between ZVS range and ripple current on LV and HV side for the selection of turn ratio *n*. Higher turn ratio leads to lower HV ripple current and wider LV ZVS range. On the other hand, lower turn ratio results in lower LV ripple current and wider HV ZVS range. In addition, lower RMS current of switches is achieved at higher turn ratio. In this section, further investigation of

power losses and converter efficiency is carried out to determine the turn ratio n and values of f and  $L_k$ .

#### 4.3.1. Power Loss of Switches

#### **Conduction Loss**

Conduction loss in power MOSFET can be calculated using the drain-source on-state resistance  $R_{DS(on)}$  and the current  $i_D$ . By integrating the instantaneous power losses in one switching period, the averaged conduction loss can be obtained by (4.8) [60]. In this case, the conduction loss caused by the anti-paralleled body diode of the MOSFET is assumed to be small enough to be neglected.

$$P_{cond} = \frac{1}{T_{s}} \int_{0}^{T_{s}} \left( R_{DS(on)} \cdot i_{D}^{2}(t) \right) dt = R_{DS(on)} \cdot I_{rms\_sw}^{2}$$

(4.8)

where  $I_{rms_{sw}}$  is obtained from (3.5) and (3.6).

#### Switching Loss

When the switches are not operated under ZVS condition, the switching loss cannot be neglected. The turn-on and turn-off losses in the MOSFET and its body diode can be calculated by linear approximation of the MOSFET switching process [60]. The turn-on energy is the sum of the energy during the current rise time  $t_{ri}$  and voltage fall time  $t_{fu}$ , as well as the energy caused by reverse-recovery of the body diode. Similarly, the turn-off energy is calculated using the voltage rise time  $t_{ru}$  and current fall time  $t_{fi}$ . The turn-off energy loss caused by diode is usually neglected.

$$E_{onM} = E_{onMi} + E_{onMrr} = U_{DS}I_{Don} \cdot \frac{t_{ri} + t_{fu}}{2} + Q_{rr}U_{DS}$$

$$E_{offM} = U_{DS}I_{Doff} \cdot \frac{t_{ru} + t_{fi}}{2}$$

$$E_{onD} \approx E_{onDrr} = \frac{1}{4}Q_{rr}U_{DS}$$

(4.9)

where,  $E_{onM}$  and  $E_{offM}$  are the turn-on and turn-off energy loss of the MOSFET,  $E_{onD}$  is the turn-on energy loss of the body diode, which is mostly the reverse recovery energy  $(E_{onDrr})$ ,  $Q_{rr}$  is the reverse recovery charge of the diode,  $U_{DS}$  is the DC voltage, and  $I_{Don}$  and  $I_{Doff}$  are the turn-on and turn-off current at the switching instant, respectively.

The total switching loss of a MOSFET and its body diode are the product of the switching energies and switching frequency.

$$P_{sw} = (E_{onM} + E_{onD} + E_{offM}) \cdot f \tag{4.10}$$

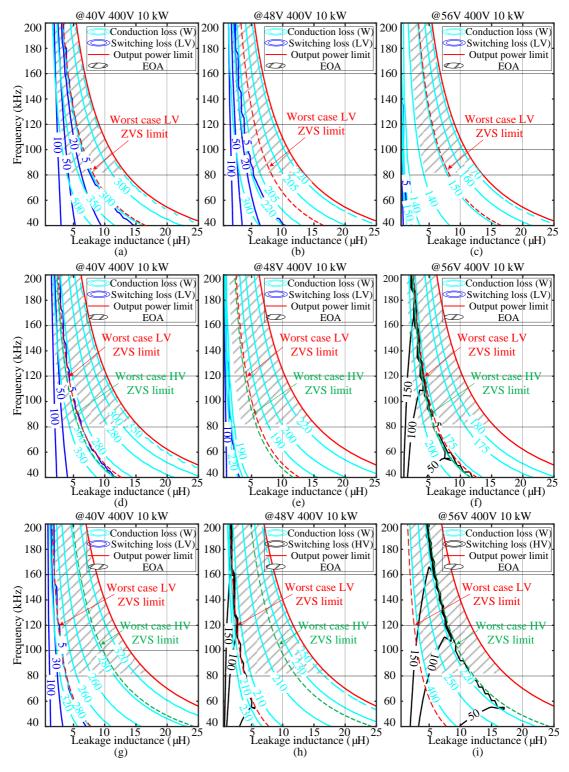

At full load, the losses of the switches are calculated at 3 different voltage level of  $V_1$ : nominal input voltage ( $V_1 = 48$  V), minimum input voltage ( $V_1 = 40$  V) and maximum input voltage ( $V_1 = 56$  V). At different turn ratio n, the conduction and switching losses are calculated and shown in Fig. 4.10. It has to be noted that although the RMS current is lower at n = 9, the conduction loss is not necessarily lower than n = 7 or 8. That's because on LV side, conduction loss is not only proportional to  $I_{rms_sw}^2$ , but also proportional to  $n^2$ .

Fig. 4.10. Conduction and switching loss under different  $V_1$  at (a, b, c) n = 7, (d, e, f) n = 8and (g, h, i) n = 9.

The switching loss of LV and HV side are also depicted at different turn ratio in each figure. When at n = 7, ZVS operation can always be achieved on HV side, and hard switching happens on LV side at lower input voltage ( $V_1 = 40$  V). When n = 9, ZVS operation is guaranteed on LV side within EOA; but switching loss exists on HV side at higher input voltage ( $V_1 = 56$  V). When n = 8, hard switching happens in a small area of EOA, which can be avoided by choosing the value of f and  $L_k$  from the right side of ZVS limit curve. It is interesting to notice that the LV switching loss increases slowly as f and  $L_k$  moves away from the ZVS limit. On the other hand, the HV switching loss in (i) is dramatically higher and comparable with the conduction loss. Due to the significant high switching loss on HV side, it is obviously more important to achieve ZVS on the HV side.

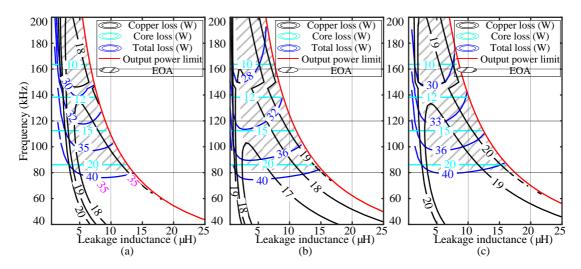

#### 4.3.2. Transformer Loss

The transformer core loss is calculated using the Steinmetz equation in (2.1) [42]. By substituting the flux density equation in (4.5) to Steinmetz equation, core loss density is obtained. The transformer core loss can be calculated by

$$P_{core} = 3 \cdot V_e \cdot p_v = 3 \cdot V_{core} \cdot K \frac{1}{f^{\beta - \alpha}} \left(\frac{V_1}{9A_e}\right)^{\beta}$$

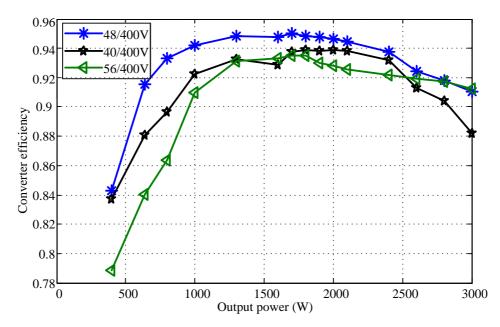

(4.11)