# DESIGN OF INTEGRATED POWER AMPLIFIER CIRCUITS FOR BIOTELEMETRY APPLICATIONS

## DESIGN OF INTEGRATED POWER AMPLIFIER CIRCUITS FOR BIOTELEMETRY APPLICATIONS

By

Munir M. EL-Desouki

Bachelor's of Applied Science King Fahd University of Petroleum and Minerals, June 2002

## A THESIS SUBMITTED TO THE SCHOOL OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER'S OF APPLIED SCIENCE

McMaster University Hamilton, Ontario, Canada

© Copyright by Munir M. El-Desouki, January 2006

MASTER OF APPLIED SCIENCE (2006)McMaster University(Electrical and Computer Engineering)Hamilton, Ontario

| TITLE:           | Design of Integrated Power Amplifier Circuits for     |  |  |

|------------------|-------------------------------------------------------|--|--|

|                  | Biotelemetry Applications                             |  |  |

|                  |                                                       |  |  |

| AUTHOR:          | Munir M. El-Desouki, B.A.Sc. (King Fahd University of |  |  |

|                  | Petroleum and Minerals)                               |  |  |

|                  |                                                       |  |  |

| SUPERVISORS:     | Prof. M. Jamal Deen and Dr. Yaser M. Haddara          |  |  |

|                  |                                                       |  |  |

| NUMBER OF PAGES: | xxv, 139                                              |  |  |

## Abstract

Over the past few decades, wireless communication systems have experienced rapid advances that demand continuous improvements in wireless transceiver architecture, efficiency and power capabilities. Since the most power consuming block in a transceiver is the power amplifier, it is considered one of the most challenging blocks to design, and thus, it has attracted considerable research interests. However, very little work has addressed low-power designs since most previous research work focused on higherpower applications. Short-range transceivers are increasingly gaining interest with the emerging low-power wireless applications that have very strict requirements on the size, weight and power consumption of the system.

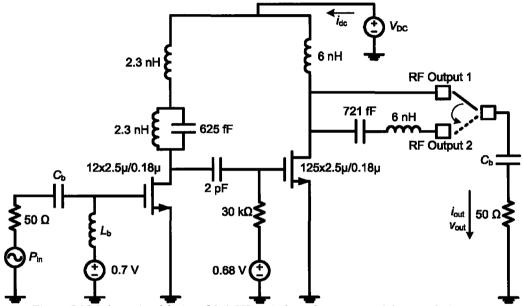

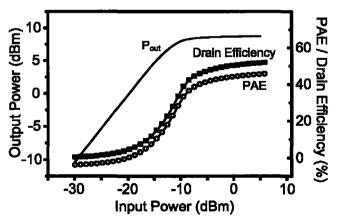

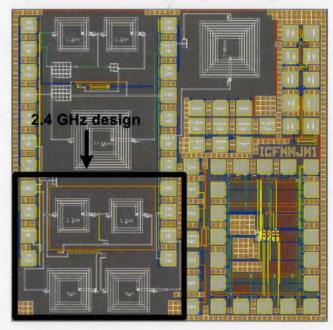

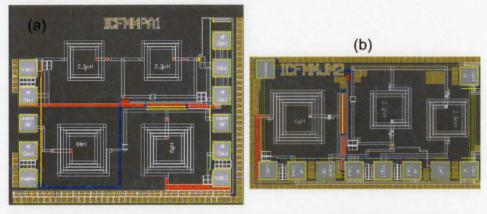

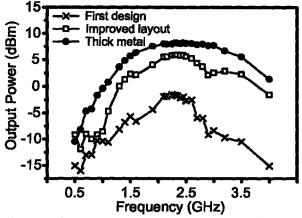

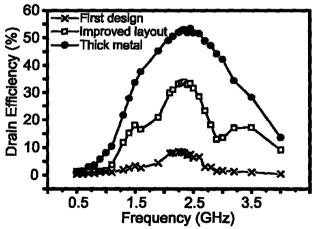

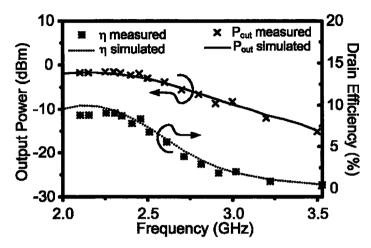

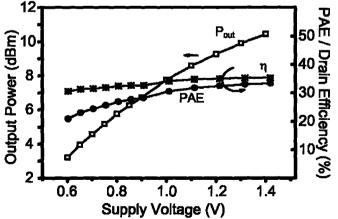

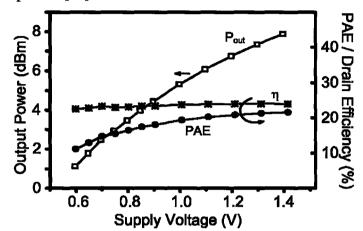

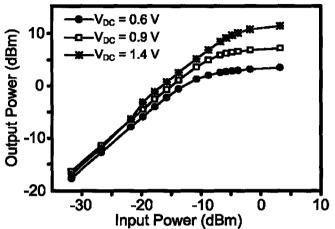

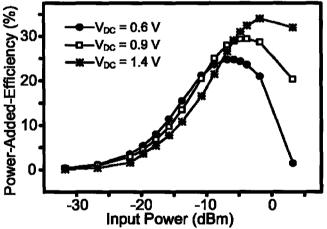

This thesis deals with designing fully-integrated RF power amplifiers with low output power levels as a first step to improving the efficiency of RF transceivers in a 0.18 µm standard CMOS technology. Two switch-mode power amplifiers, one operating at a frequency of 650 MHz and the other at a frequency of 2.4 GHz, are presented in this work using a class-E output stage with a class-F driver stage. The work presented here represents the first use of class-E power amplifiers for low-power applications. The measurement results of the 650 MHz design show a maximum drain efficiency of 15 % and a maximum gain of 11.5 dB. When operated from a 0.65 V supply, the power amplifier delivers an output power of 750  $\mu$ W with a maximum power-added efficiency (PAE) of 10 %. As for the 2.4 GHz design, three layouts were fabricated. The first two designs have a filtered and a non-filtered output to show the effects of using on-chip filtering in low-power designs. Special attention was given to optimize the layout and minimize the parasitic effects. Measurement results show a maximum drain efficiency of 38 % and a maximum gain of 17 dB. When operating from a 1.2 V supply, the power amplifier delivers an output power of 9 mW with a PAE of 33 %. The supply voltage can go down to 0.6 V with an output power of 2 mW and a PAE of 25 %. The improvements in the layout show an increase in drain efficiency from 8 % to 35 %. The third design uses a 2  $\mu$ m thick top-metal layer of low-resistivity, with the same circuit component values as the first two designs. Measurement results show a maximum drain efficiency of 53 % and a maximum gain of 22 dB. When operating from a 1.2 V supply, the power amplifier delivers an output power of 14.5 mW with a PAE of 51 %. The supply voltage can go down to 0.6 V with an output power of 3.5 mW and a PAE of 43 %.

Also, a novel mode-locking power amplifier design is presented in two fullyintegrated, differential superharmonic injection-locked power amplifiers (ILPA) operating at a frequency of 2.4 GHz and at a frequency of 400 MHz. Measurement results of the 2.4 GHz design and the 400 MHz design show that the fabricated power amplifiers have a maximum gain of 31 dB from only one stage that occupies a chip area of only 0.6  $mm^2$  and 0.9  $mm^2$  respectively, with all components fully integrated.

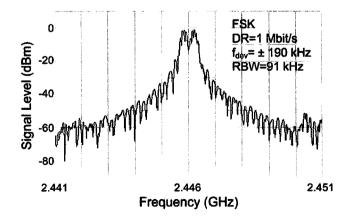

Finally, two fully-integrated, single block baseband direct-modulation transmitters operating at a frequency of 2.4 GHz and at a frequency of 400 MHz are also presented in this work. Measurement results of the 2.4 GHz transmitter show a drain efficiency of 27 %. When operating from a 1.5 V supply, the transmitter delivers an output power of 8 dBm with a low phase noise of -122 dBc/Hz at a 1 MHz offset.

## **Acknowledgements**

I would like to start by expressing my sincere gratitude to the Almighty, where in His name, the most gracious, the most merciful, all good things start. I will next list a number of people who I am thankful to; and I apologize to those I forgot or could not mention.

I would like to express my sincere gratitude to my senior supervisor Prof. M. Jamal Deen, for giving me the opportunity to work on these projects and for his continuous support and guidance throughout my work. It is indeed an honor to have the opportunity to follow into the footsteps of such a great mentor. I have learned, and I continue to learn so much from him and I hope that my future achievements meet and exceed the expectations of being one of his students.

I would also like to express my deep appreciation to my co-supervisor Prof. Yaser M. Haddara for his continuous support and guidance. My personal relationship with Dr. Haddara ranks of a higher importance to me than the academic one. In a country with almost no family, it is very valuable to me to know that I can obtain brotherly advice from him at any time.

Also, I would like to thank Prof. Peter M. Smith and Prof. Mohamed Bakr for taking the time to review my thesis and for being in my committee.

I would next like to thank my team members. I am referring to them as team members because without their support, I would still be stuck at my first design up until today. To mention a number of them, Kareem Shoukri, Sasan Naseh, Rizwan Murji, Nabeel Jafferali, Wai Ngan, Ahmed Fakhr, Ehab El-Badry, Hamed Jafari, Samer Rizk, Tarek Sadek and recently Mohammed Waleed Shinwari, who is also one of my best friends from Saudi Arabia and continues to suffer from my never ending complaints. I would especially like to thank Juan-Carlos Ranuarez who has always supported my work, even after graduating and leaving McMaster University. I would also like to thank Dr. Ognian Marinov for keeping his door always open for advice and support. I would also like to thank other faculty members at McMaster University, such as Dr. Chin-Hung Chen, Dr. Nicola Nicolici, Dr. Steve Hranilovic, Prof. James P. Reilly and Dr. Rafik O. Loutfy. Also, not forgetting the administrative staff at the ECE department, especially Cheryl Gies, Terry Greenlay, Cosmin Coroiu and Helen Jachna.

Next I would like to thank the Canadian Microelectronics Corporation (CMC) for providing me with the means of fabricating my designs. I am also very grateful to my employer, King Abdulaziz City for Science & Technology (KACST) for providing me with this great opportunity by funding my graduate studies. In particular, I would like to thank Dr. Mansour Alghamdi, Dr. Mohammad Alkanhal, Dr. Fayez Alhargan, Soud Albatal and Saad Aldosary. I would especially like to thank Dr. Daham Alani, who had always been like a second father to me. I would also like to thank Nuha Nasser at the Saudi Arabian Cultural Bureau in Canada.

At King Fahd University of Petroleum and Minerals (KFUPM), I would like to thank my mentors Prof. Muhammad Abuelma'atti and Dr. Mohammad Alsunaidi.

I would also like to thank my dearest friends, many of which I was blessed with for more than 16 years, especially Ismail Alani, Fahd Bahadailah, Khalid Al-Najar, Osama Boshnaq, Adel Bedair, Hisham Al-Rowaihi, Mishaal Adib, Teeba Alkhudairi who always makes me feel that I am not the only one with too much to do, Najla Attallah and many others. In Canada, I would like to thank my close friend Jodie Ellenor for always showing me that there is still hope for this world, and my close friend Lyndsey Huvers for ramping up the early stages of my research by keeping me up all night after returning home noisily very late. I would also like to express my sincere gratitude to my friends Zina Alani and Khaldoon Mogharbil for always making me feel that my family is close by.

A group member that I purposely left out, some one who has been involved in all the phases of my work with continuous support, a very dear friend that is more than a sister to me. Thank you Samar Abdelsayed for being the great person that you are.

Finally, I would like to express my deepest acknowledgements to my dear family, Prof. Mahmoud El-Desouki, Dr. Mayadah Al-Homsi, Dr. Majid El-Desouki and Mohannad El-Desouki, who continuously raise my measure of success, by showing me what it really means.

# **Table of Contents**

| ABSTRACT                                          |      |

|---------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                  | V    |

| TABLE OF CONTENTS                                 | vii  |

| LIST OF FIGURES                                   | xi   |

| LIST OF TABLES                                    | xxi  |

| LIST OF SYMBOLS AND ACRONYMS                      | xxii |

| INTRODUCTION                                      | 1    |

| 1.1 Why CMOS?                                     | 3    |

| 1.2 Biomedical Systems                            | 4    |

| 1.3 RF CMOS Transceivers                          | 8    |

| 1.4 Motivation                                    | 10   |

| 1.5 Thesis Organization                           | 13   |

| INTRODUCTION TO CMOS RF POWER AMPLIFIERS          |      |

| 2.1 Simple Power Amplifier                        | 15   |

| 2.2 Important Characteristics of Power Amplifiers | 16   |

| 2.2.1 Power Gain                                  | 16   |

| 2.2.2 Efficiency                                  |      |

| 2.2.3 Linearity                             |    |

|---------------------------------------------|----|

| 2.2.3.1 Gain Compression (AM-AM Conversion) | 19 |

| 2.2.3.2 AM-PM Conversion                    | 19 |

| 2.2.3.3 Inter-Modulation Distortion (IMD)   | 19 |

| 2.3 Design Considerations                   | 20 |

| 2.3.1 Conjugate Match and Load Line Match   | 20 |

| 2.3.2 Effect of the Transistor Knee-Voltage | 21 |

| 2.3.3 Substrate Doping and Leakage          | 22 |

| 2.3.4 Breakdown Voltage                     | 22 |

| 2.3.5 Temperature Considerations            | 23 |

| 2.3.6 On-chip Integration                   | 24 |

| 2.3.7 Amplifier Stability                   | 25 |

| 2.3.8 Ground Inductance                     | 25 |

| 2.3.9 Low Output Power Design               | 26 |

| 2.4 Summary                                 | 28 |

| POWER AMPLIFIER CLASSES OF OPERATION        | 29 |

| 3.1 Current-Mode Power Amplifiers           | 29 |

| 3.1.1 Class-A Power Amplifiers              | 36 |

| 3.1.2. Class-B Power Amplifiers             | 37 |

| 3.1.3. Class-AB Power Amplifiers            | 37 |

| 3.1.4. Class-C Power Amplifiers             | 37 |

| 3.2 Switch-Mode Power Amplifiers            |    |

| 3.2.1 Class-D Power Amplifiers              |    |

| 3.2.2 Class-E Power Amplifiers              |    |

| 3.2.3 Class-F Power Amplifiers4                                                                                                                                                                                                                                                                                                                                                             | 6                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 3.2.4 Class-S Power Amplifiers4                                                                                                                                                                                                                                                                                                                                                             | 7                                    |

| 3.3 Lock-Mode Power Amplifiers4                                                                                                                                                                                                                                                                                                                                                             | 8                                    |

| 3.4 Power Amplifier Figure-of-Merit (FoM)                                                                                                                                                                                                                                                                                                                                                   | 9                                    |

| 3.5 Summary                                                                                                                                                                                                                                                                                                                                                                                 | 9                                    |

| DIRECT-MODULATION TRANSMITTERS5                                                                                                                                                                                                                                                                                                                                                             | 1                                    |

| 4.1 Differential Cross-Coupled Negative-g <sub>m</sub> Voltage-Controlled Oscillator                                                                                                                                                                                                                                                                                                        | 2                                    |

| 4.2 Superharmonic Injection-Locking                                                                                                                                                                                                                                                                                                                                                         | 5                                    |

| 4.3 Transmitter Figure-of-Merit (FoM)                                                                                                                                                                                                                                                                                                                                                       | 5                                    |

| 4.4 Summary                                                                                                                                                                                                                                                                                                                                                                                 | 6                                    |

|                                                                                                                                                                                                                                                                                                                                                                                             | 7                                    |

| SWITCH-MODE POWER AMPLIFIERS – MEASUREMENT RESULTS                                                                                                                                                                                                                                                                                                                                          | '                                    |

| 5.1 First Power Amplifier Design                                                                                                                                                                                                                                                                                                                                                            |                                      |

|                                                                                                                                                                                                                                                                                                                                                                                             | 9                                    |

| 5.1 First Power Amplifier Design                                                                                                                                                                                                                                                                                                                                                            | 9<br>5                               |

| <ul> <li>5.1 First Power Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                         | 9<br>5<br>7                          |

| <ul> <li>5.1 First Power Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                         | 9<br>5<br>7<br>8                     |

| 5.1 First Power Amplifier Design    5      5.1.1 Schematic Simulation Results    6      5.1.2 Layout    6      5.1.3 Refined Circuit Simulation Results    6                                                                                                                                                                                                                                | 9<br>5<br>7<br>8<br>0                |

| 5.1 First Power Amplifier Design       5         5.1.1 Schematic Simulation Results       6         5.1.2 Layout       6         5.1.3 Refined Circuit Simulation Results       6         5.1.4 Measurement Results       7                                                                                                                                                                 | 9<br>5<br>7<br>8<br>0                |

| 5.1 First Power Amplifier Design       5         5.1.1 Schematic Simulation Results       6         5.1.2 Layout       6         5.1.3 Refined Circuit Simulation Results       6         5.1.4 Measurement Results       7         5.2 Second Power Amplifier Design       7                                                                                                               | 9<br>5<br>7<br>8<br>0<br>6           |

| 5.1 First Power Amplifier Design       51         5.1.1 Schematic Simulation Results       61         5.1.2 Layout       61         5.1.3 Refined Circuit Simulation Results       61         5.1.4 Measurement Results       71         5.2 Second Power Amplifier Design       71         5.2.1 Schematic Simulation Results       71         5.2.1 Schematic Simulation Results       71 | 9<br>5<br>7<br>8<br>0<br>6<br>8      |

| 5.1 First Power Amplifier Design       5         5.1.1 Schematic Simulation Results       6         5.1.2 Layout       6         5.1.3 Refined Circuit Simulation Results       6         5.1.4 Measurement Results       7         5.2 Second Power Amplifier Design       7         5.2.1 Schematic Simulation Results       7         5.2.2 Layout       7         5.2.2 Layout       7  | 9<br>5<br>7<br>8<br>0<br>6<br>8<br>9 |

| LOCK-MODE POWER AMPLIFIERS – MEASUREMENT RESULTS92       |

|----------------------------------------------------------|

| 6.1 First Power Amplifier Design                         |

| 6.1.1 Schematic Simulation Results95                     |

| 6.1.2 Layout                                             |

| 6.1.3 Measurement Results                                |

| 6.2 Second Power Amplifier Design                        |

| 6.2.1 Schematic Simulation Results106                    |

| 6.2.2 Layout                                             |

| 6.2.3 Measurement Results                                |

| 6.3 Comparison and Summary112                            |

| DIRECT-MODULATION TRANSMITTERS – MEASUREMENT RESULTS 114 |

| 7.1 First Transmitter Design                             |

| 7.1.1 Schematic Simulation Setup116                      |

| 7.1.2 Measurement Results                                |

| 7.2 Second Transmitter Design                            |

| 7.3 Comparison and Summary124                            |

| CONCLUSIONS AND FUTURE WORK126                           |

| 8.1 Contributions and Summary                            |

| 8.2 Future Work                                          |

| REFERENCES                                               |

# **List of Figures**

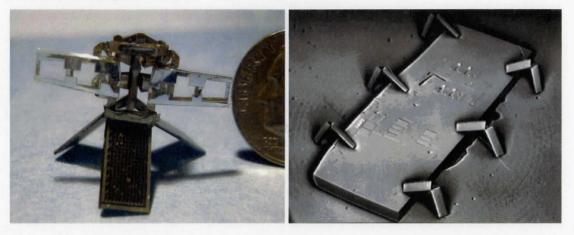

| Figure 1.1: Flying and crawling microrobot models for wireless sensor networks [1]2                      |

|----------------------------------------------------------------------------------------------------------|

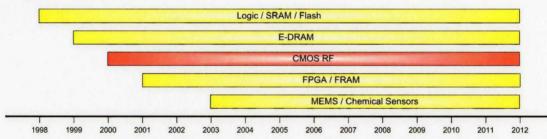

| Figure 1.2: First integration of different technologies as a SoC with standard CMOS, reproduced from [6] |

| Figure 1.3: Application spectrum [6]4                                                                    |

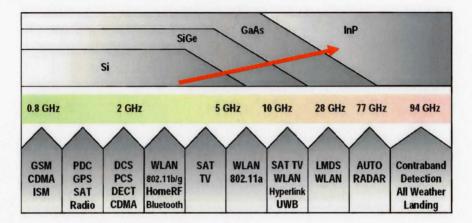

| Figure 1.4: A comparison between emerging technologies and CMOS [6]5                                     |

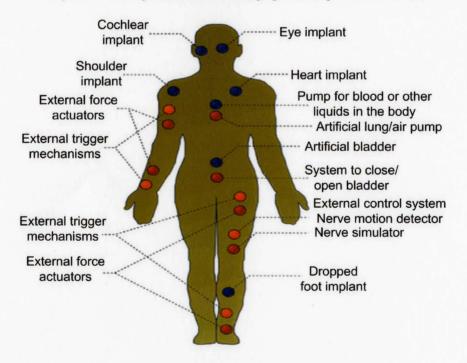

| Figure 1.5: Some applications of implantable electronic systems [14]5                                    |

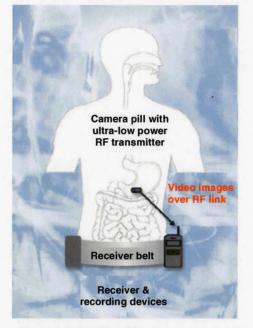

| Figure 1.6: Swallowable camera system [15]8                                                              |

| Figure 1.7: Screen shot of the Norika user interface [16]9                                               |

| Figure 1.8: Block diagram of a typical RF transceiver, reproduced from [17]9                             |

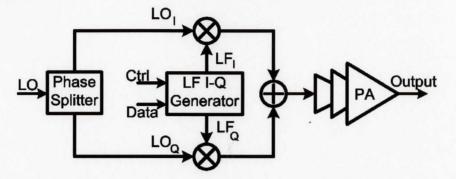

| Figure 1.9: An example of an RF transmitter circuit [18]10                                               |

| Figure 1.10: ITRS projected supply voltage reduction [6]11                                               |

| Figure 1.11: ITRS projected FoM for PAs and VCOs for future technology nodes [6]13                       |

| Figure 2.1 Simple power amplifier16                                                                      |

| Figure 2.2 The basic parameters of a simple power amplifier17                                            |

| Figure 2.3 Simple two-stage power amplifier17                                                            |

| Figure 2.4 The effect of gain compression on the output power19                                          |

| Figure 2.5 Third order IMD components20                                                                  |

| Figure 2.6 Third order intercept points                                                                  |

| Figure 2.7 Optimal load line21                                                                           |

| Figure 2.8 The effects of ground inductance on the performance of a power amplifier,                     |

| reproduced from [3]26                                                                                    |

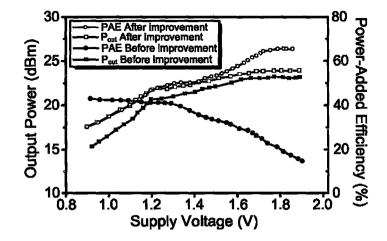

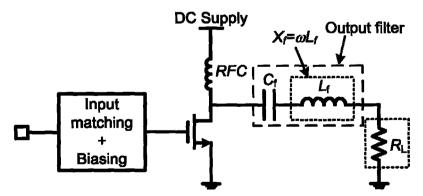

| Figure 2.9 The effect of using a finite RFC on low output power amplifiers27                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.10 The effect of the output filter on low output power amplifiers                                                                                                               |

| Figure 3.1 Basic single-stage current-mode power amplifier                                                                                                                               |

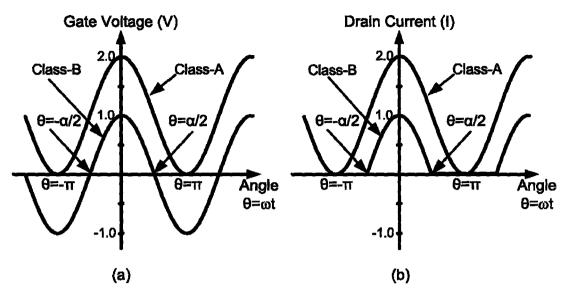

| Figure 3.2 (a) The effect of the gate biasing point on the conduction angle (α). (b) The equivalent drain current                                                                        |

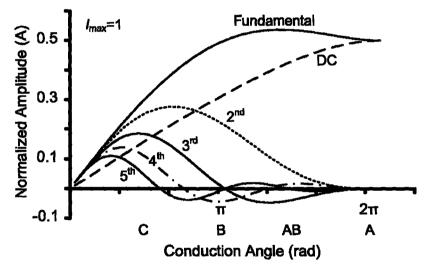

| Figure 3.3 Harmonic components as a function of the conduction angle ( $\alpha$ )                                                                                                        |

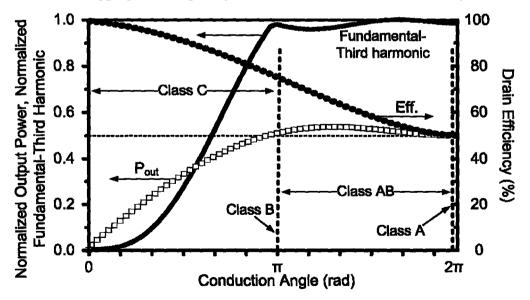

| Figure 3.4 The effect of the conduction angle (α) on the normalized output power, drain efficiency and difference between the fundamental current and the third order harmonic component |

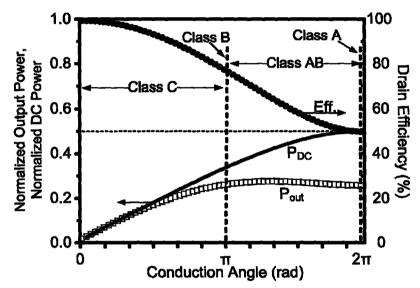

| Figure 3.5 The effect of the conduction angle (α) on the DC power, output power and drain efficiency                                                                                     |

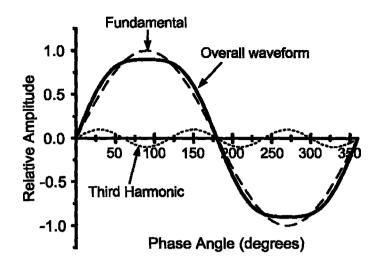

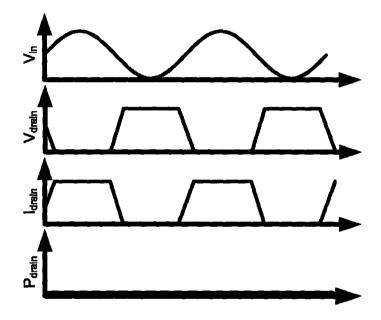

| Figure 3.6 Third order harmonic peaking                                                                                                                                                  |

| Figure 3.7 A method to increase efficiency                                                                                                                                               |

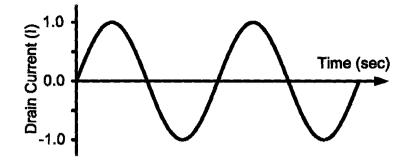

| Figure 3.8 Drain current of a class-A power amplifier                                                                                                                                    |

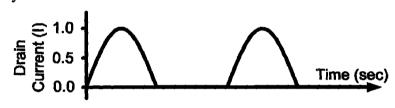

| Figure 3.9 Drain current of a class-B power amplifier                                                                                                                                    |

| Figure 3.10 Basic schematic of a class-D power amplifier                                                                                                                                 |

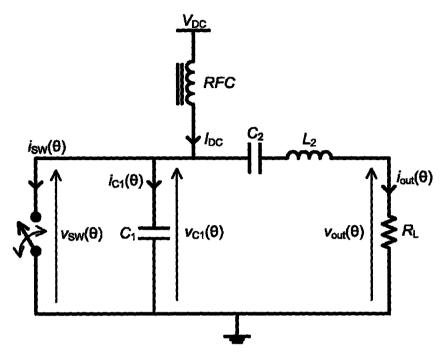

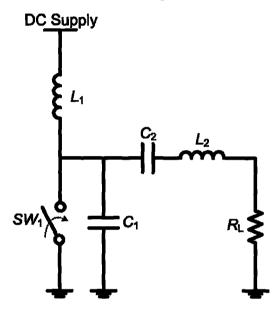

| Figure 3.11 Basic schematic of a class-E power amplifier40                                                                                                                               |

| Figure 3.12 The equivalent circuit of a class-E amplifier41                                                                                                                              |

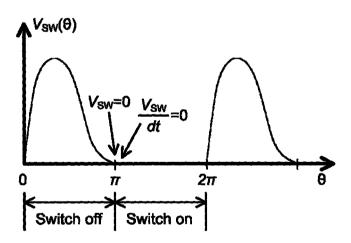

| Figure 3.13 The drain voltage waveform of an ideal class-E amplifier41                                                                                                                   |

| Figure 3.14 The output waveform of a class-E power amplifier42                                                                                                                           |

| Figure 3.15 The effects of adjusting the output network components of a class-E amplifier [30]46                                                                                         |

| Figure 3.16 Basic schematic of a class-F power amplifier                                                                                                                                 |

| Figure 3.17 An example of a class-S power amplifier                                                                                                                                      |

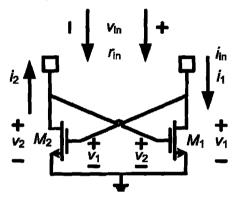

| Figure 3.18 Differential class-E power amplifier with mode-locking, reproduced from [34]                                                                                                 |

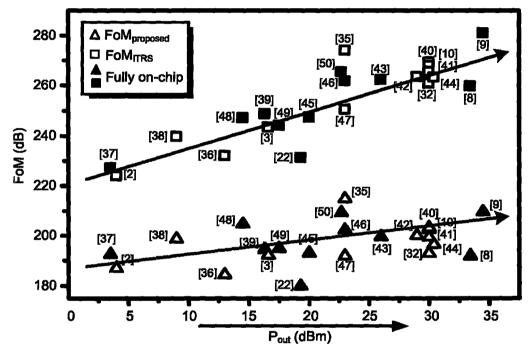

| Figure 3.19 Comparison | between th                            | he proposed | FoM and | the ITRS | FoM for | published |

|------------------------|---------------------------------------|-------------|---------|----------|---------|-----------|

| works [60]             | • • • • • • • • • • • • • • • • • • • |             | ••••••  |          |         | 50        |

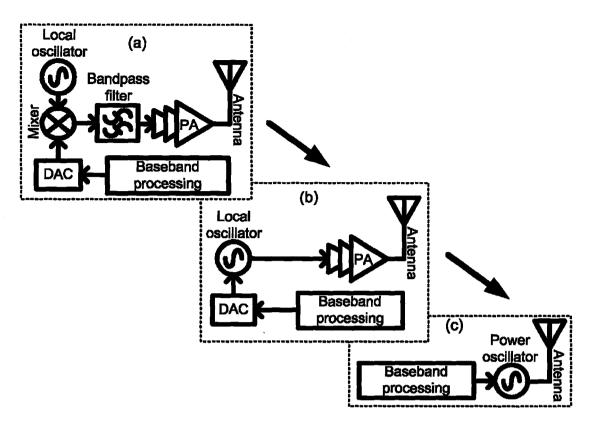

| Figure 4.1 (a) Basic block diagram of a direct-modulation transmitter, (b) simplified      |

|--------------------------------------------------------------------------------------------|

| transmitter, (c) single block transmitter [51]                                             |

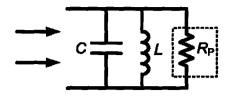

| Figure 4.2 A frequency selective LC-tank showing the parallel output resistance53          |

| Figure 4.3 Negative resistance of a cross coupled NMOS pair53                              |

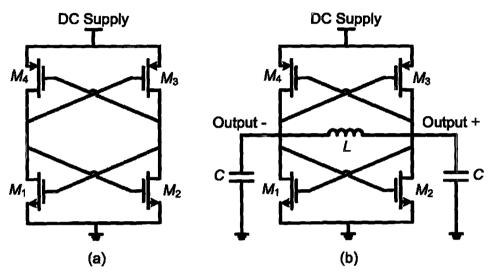

| Figure 4.4 (a) Complementary negative- $g_m$ cross coupled pair, (b) complete oscillator54 |

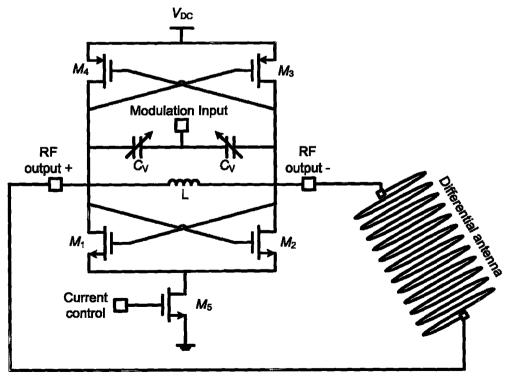

| Figure 4.5 Schematic of a direct-modulation transmitter                                    |

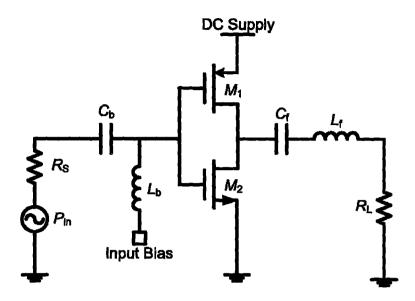

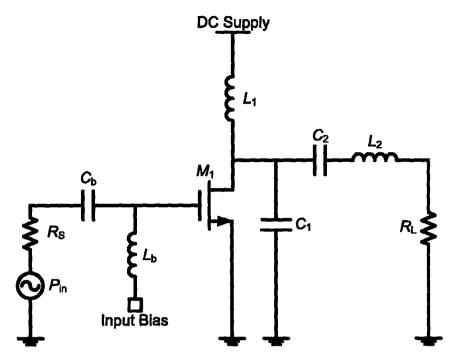

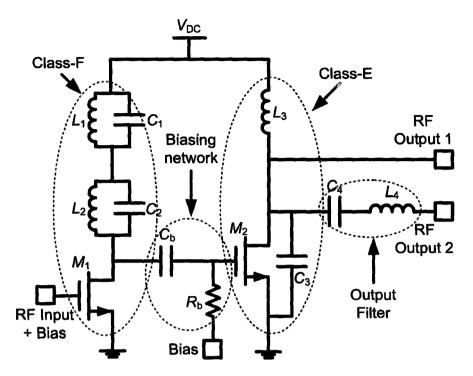

| Figure 5.1 Schematic of the complete two-stage power amplifier                             |

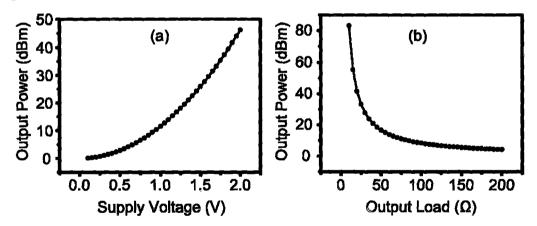

| Figure 5.2 Output power as a function of (a) the supply voltage for a fixed output load of |

| 50 $\Omega$ , (b) the output load for a fixed supply voltage of 1.2 V60                    |

| Figure 5.3 Schematic of a basic class-E power amplifier [56]61                             |

| Figure 5.4 Schematic of designed 900 MHz switch-mode power amplifier [53]64                |

| Figure 5.5 Schematic of 900 MHz switch-mode power amplifier simulation setup65             |

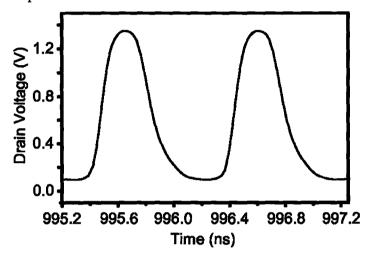

| Figure 5.6 Simulated drain voltage of the class-E power amplifier                          |

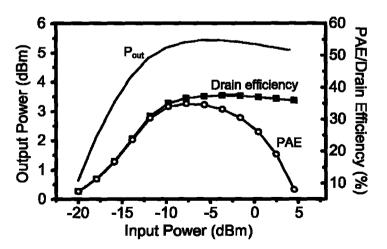

| Figure 5.7 Simulated output power, PAE and drain efficiency as a function of the input     |

| power                                                                                      |

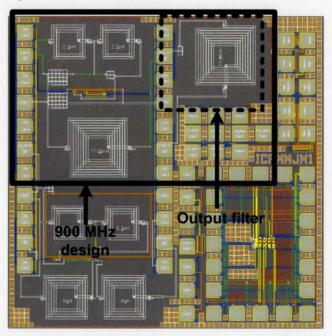

| Figure 5.8 Screen capture of the 900 MHz power amplifier layout                            |

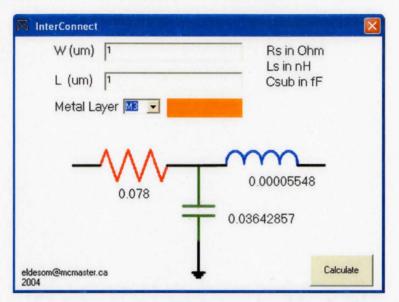

| Figure 5.9 Screen capture of the InterConnect application interface                        |

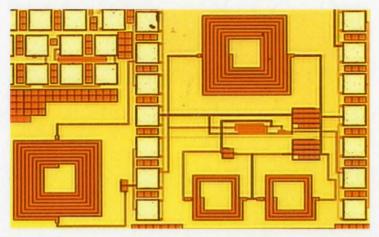

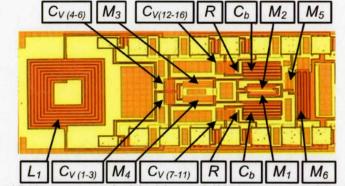

| Figure 5.10 Photomicrograph of the fabricated 900 MHz power amplifier [53]70               |

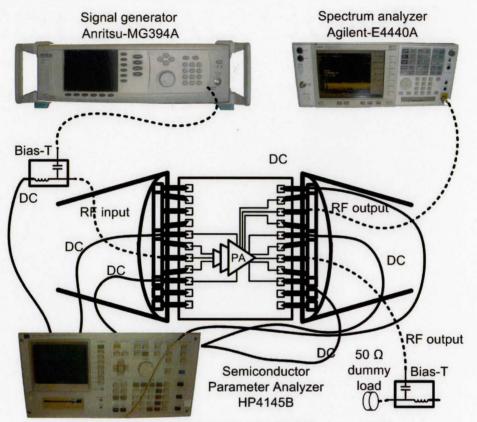

| Figure 5.11 Setup used in measuring the 900 MHz power amplifier71                          |

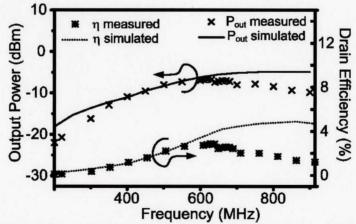

| Figure 5.12 Comparison between the measured and simulated output power and drain           |

| efficiency of the filtered output, as a function of the operating frequency, at a          |

| supply voltage of 0.7 V71                                                                  |

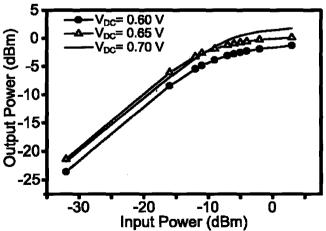

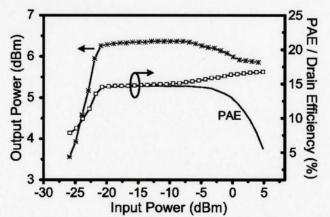

- Figure 5.14 Measured output power of the non-filtered output at an input frequency of 650 MHz, as a function of the input power for various supply voltages [53] 72

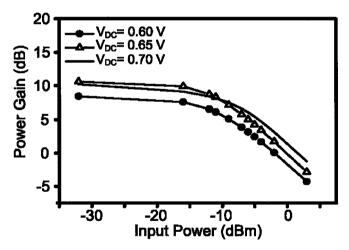

- Figure 5.15 Measured power gain of the non-filtered output at an input frequency of 650 MHz, as a function of the input power for various supply voltages [53]......73

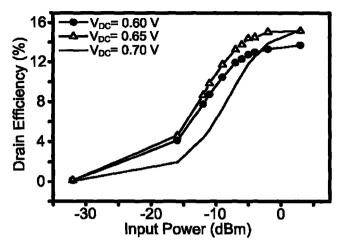

- Figure 5.16 Measured drain efficiency of the non-filtered output at an input frequency of 650 MHz, as a function of the input power for various supply voltages [53] 74

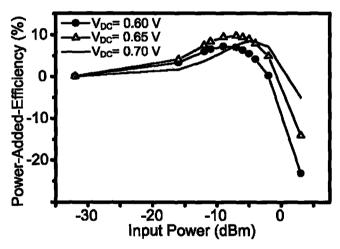

- Figure 5.17 Measured PAE of the non-filtered output at an input frequency of 650 MHz, as a function of the input power for various supply voltages [53]......74

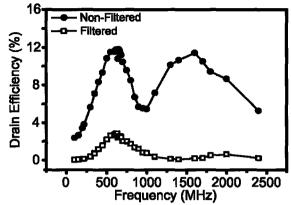

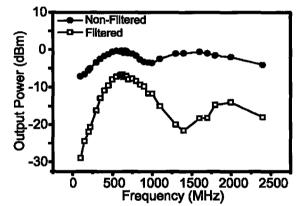

- Figure 5.18 Comparison between the measured drain efficiency of the filtered and the non-filtered outputs as a function of the input frequency, at a supply voltage of 0.7 V [53]......75

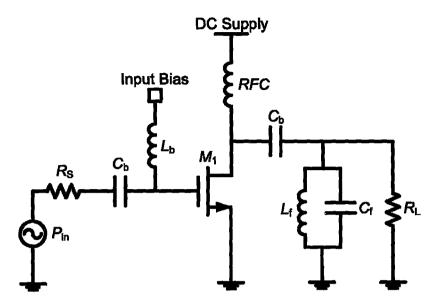

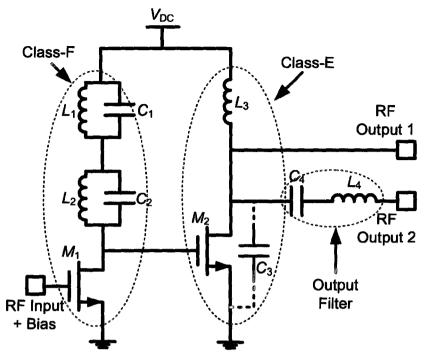

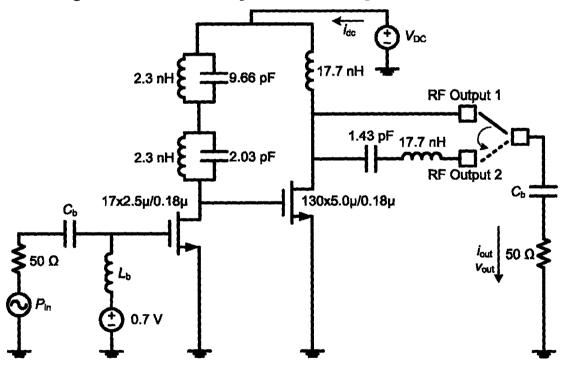

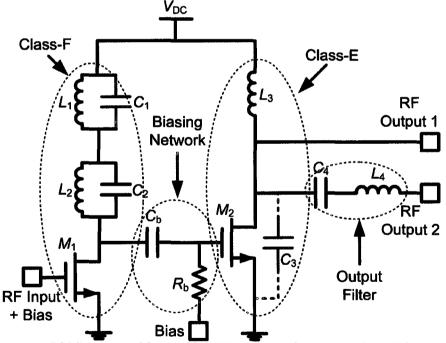

- Figure 5.21 Schematic of designed 2.4 GHz switch-mode power amplifier [54, 55]......76

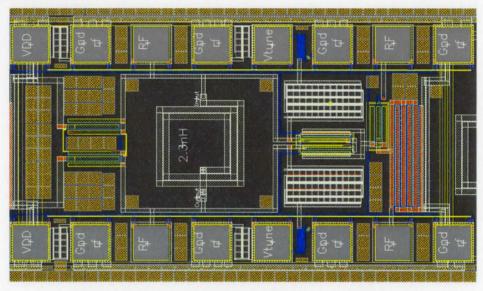

- Figure 5.24 Screen capture of the first 2.4 GHz power amplifier layout ......78

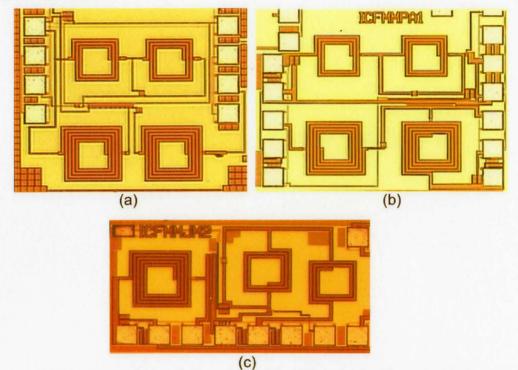

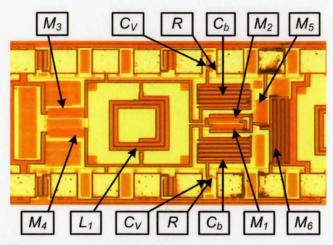

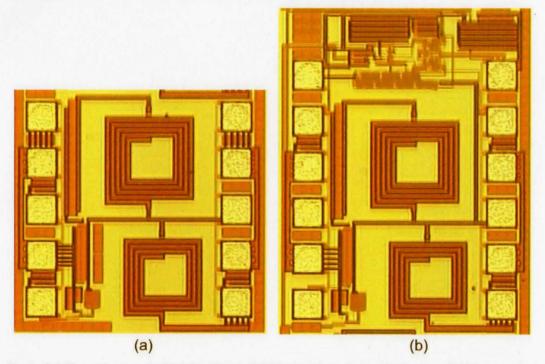

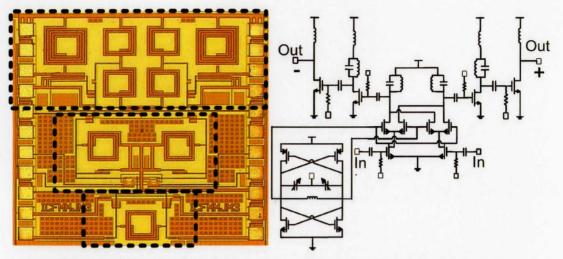

- Figure 5.26 Photomicrograph of (a) the first fabricated 2.4 GHz design, (b) the improved layout and (c) the thick-metal design [54-56]......80

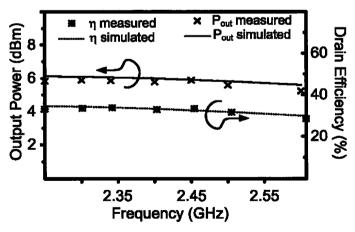

- Figure 5.29 Comparison between the measured and simulated output power and drain efficiency of the filtered output in the first design, as a function of the operating frequency, at a supply voltage of 0.8 V [54]......82

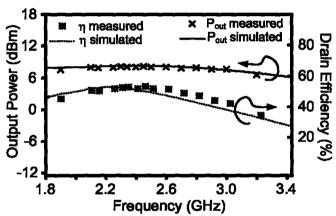

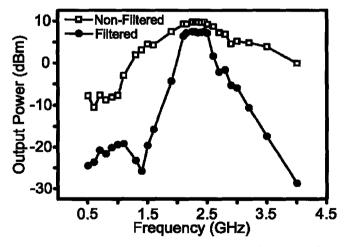

- Figure 5.30 Comparison between the measured and simulated output power and drain efficiency of the non-filtered output in the improved design, as a function of the operating frequency, at a supply voltage of 0.8 V [54] ......82

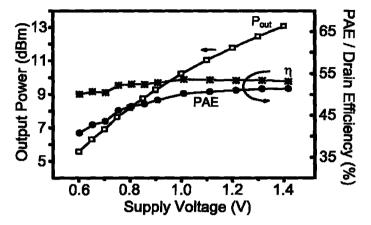

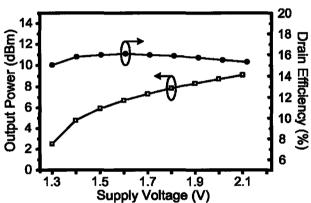

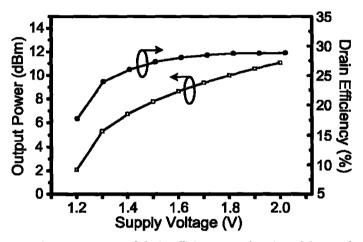

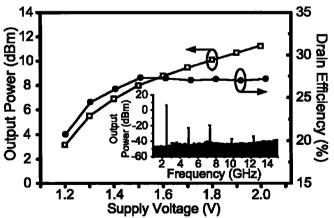

- Figure 5.38 Measured output power, PAE and drain efficiency (η) of the third design at an input frequency of 2.4 GHz, as a function of the supply voltage [56]......87

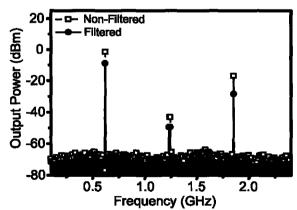

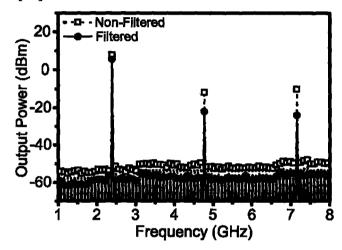

- Figure 5.43 Measured harmonic content of the output signal in the third design, at a supply voltage of 0.8 V and an input frequency of 2.4 GHz [56]......90

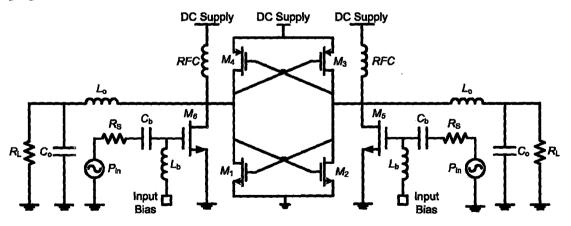

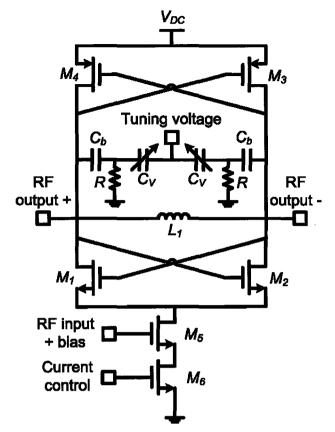

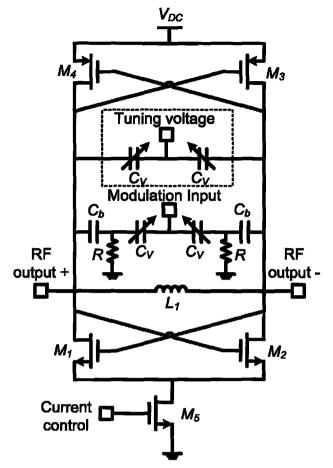

- Figure 6.1 Basic schematic of the lock-mode power amplifier [57]......94

- Figure 6.2 Schematic of designed 400 MHz lock-mode power amplifier simulation setup

- Figure 6.7 Photomicrograph of the fabricated 400 MHz power amplifier [51, 57]......99

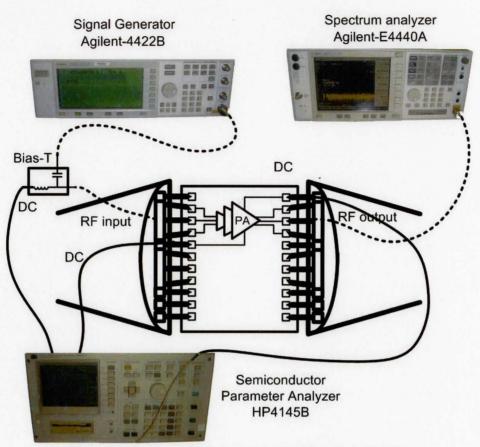

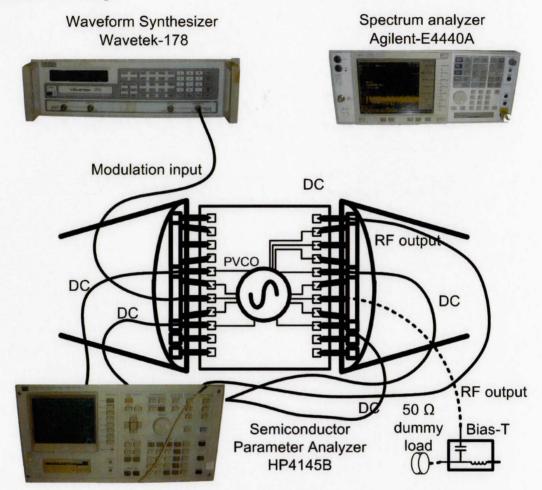

- Figure 6.8 Setup used in measuring the 400 MHz power amplifier......100

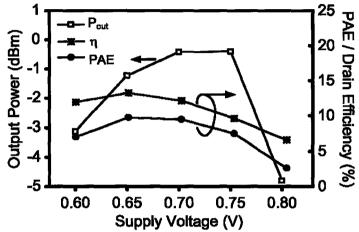

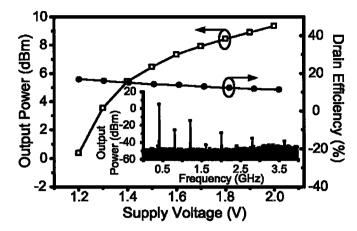

- Figure 6.10 The measured output power and drain efficiency as a function of the supply voltage at an input power of -2 dBm, an incident frequency of 866 MHz and an output frequency of 433 MHz [57]......101

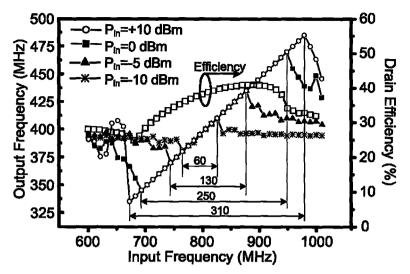

- Figure 6.12 The measured output power and drain efficiency as a function of the input frequency at a supply voltage of 1.5 V and an input power of -2 dBm [57] 102

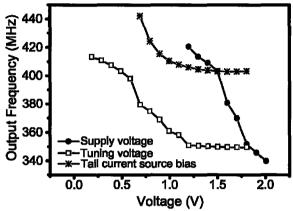

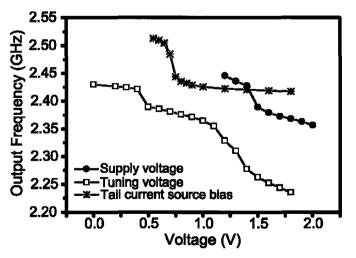

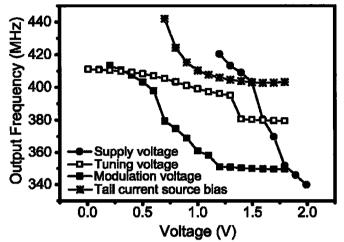

- Figure 6.13 The measured output frequency of the free running amplifier design as a function of the supply voltage, tuning voltage and tail current source bias [57]

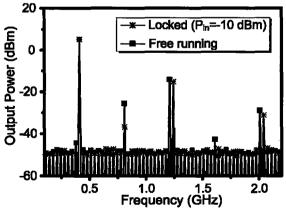

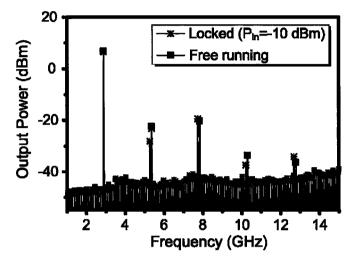

- Figure 6.14 The measured output spectrum taken from a single-ended output after loss compensation, at a supply voltage of 1.5 V for both the free running mode and the locked mode with an input power of -10 dBm [57].....103

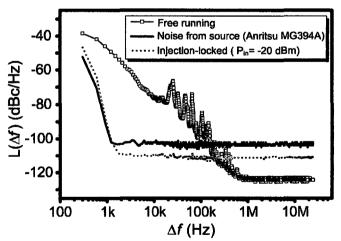

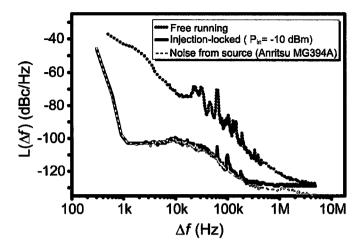

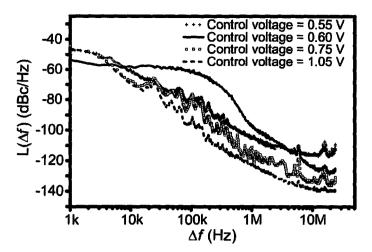

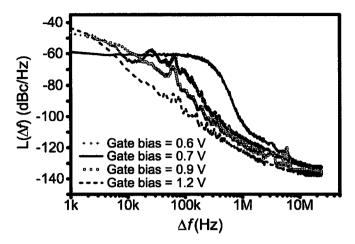

- Figure 6.15 The measured phase noise in free running mode, with a 0.9 V gate bias applied to transistor M<sub>5</sub>, and in locking mode, with an input power of -20 dBm, at a supply voltage of 1.5 V [57] ......104

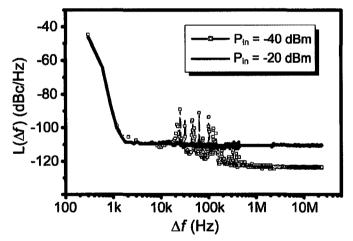

- Figure 6.16 The measured phase noise in the locking-mode, with an input power of -20 dBm and an input power of -40 dBm, at a supply voltage of 1.5 V [57] .....105

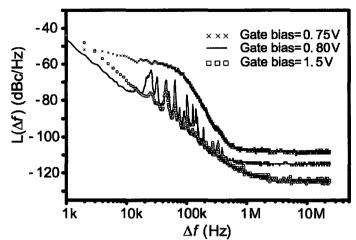

- Figure 6.17 The measured phase noise in free-running mode with no RF input applied, for various gate bias voltages applied to transistor M<sub>5</sub>, at a supply voltage of 1.5 V [57]......106

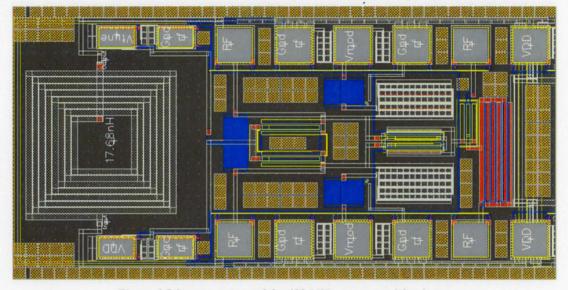

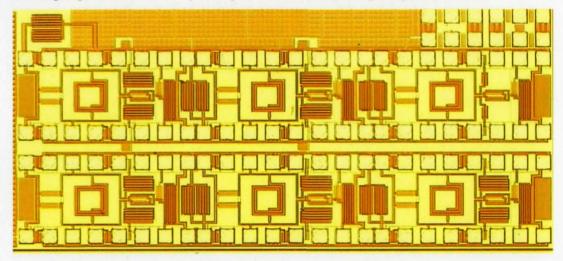

Figure 6.19 Screen capture of the 2.4 GHz power amplifier layout......107

- Figure 6.20 Photomicrograph of the fabricated 2.4 GHz power amplifier [51, 57]......108

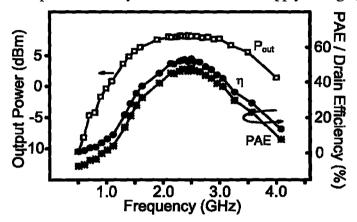

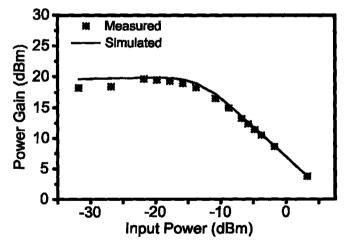

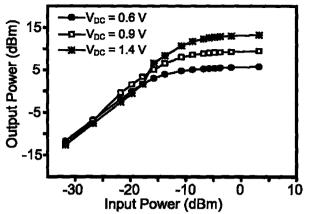

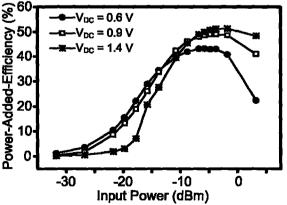

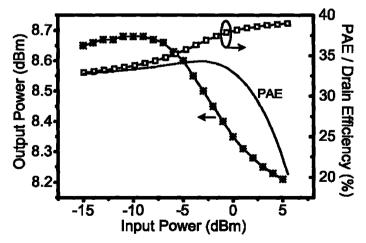

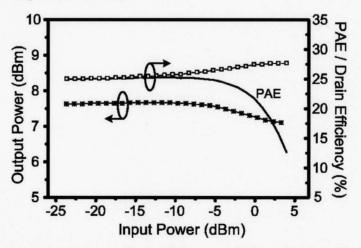

- Figure 6.21 The measured output power, drain efficiency and PAE as a function of the input power at a supply voltage of 1.5 V, an incident frequency of 4.8 GHz and an output frequency of 2.4 GHz [57]......108

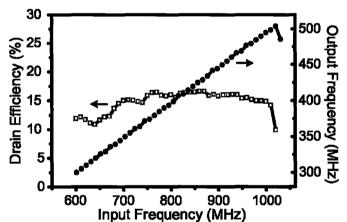

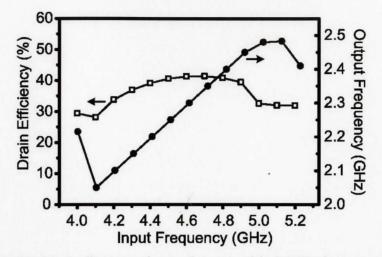

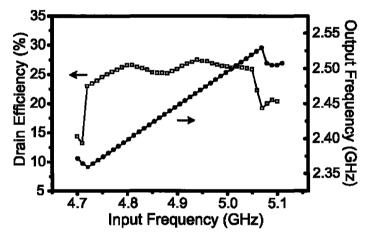

- Figure 6.24 The measured output power and drain efficiency as a function of the input frequency at a supply voltage of 1.5 V and an input power of -2 dBm [57] 110

- Figure 6.25 The measured output frequency of the free-running amplifier as a function of the supply voltage, tuning voltage and tail current source bias [51, 57].....110

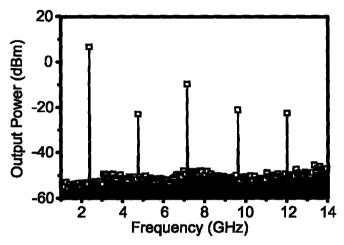

- Figure 6.26 The measured output spectrum taken from a single-ended output after loss compensation, at a supply voltage of 1.5 V for both the free-running mode and the locked-mode with an input power of -10 dBm [57].....111

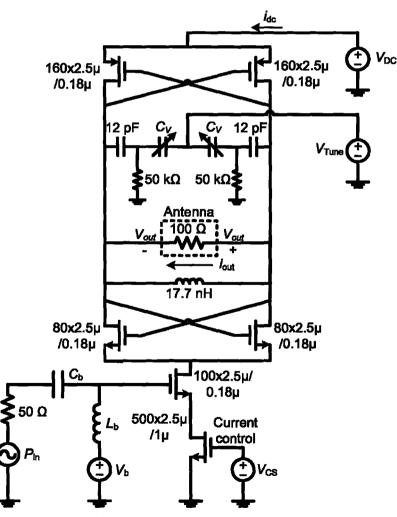

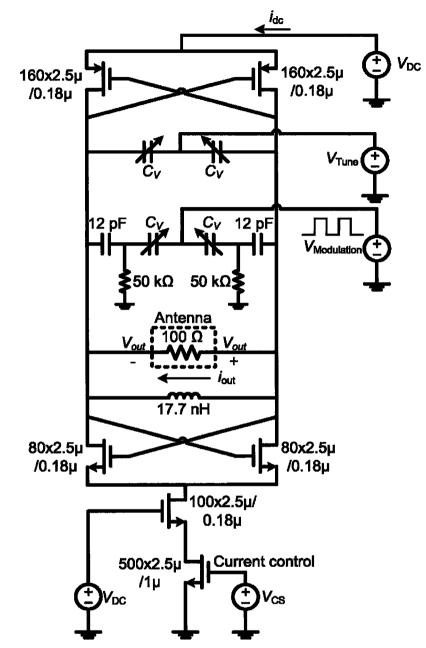

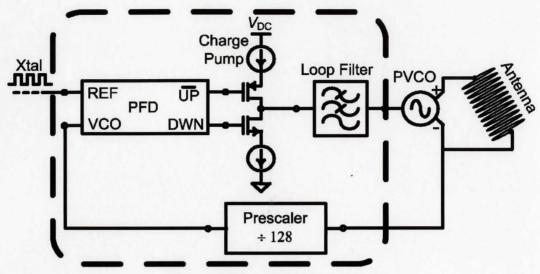

Figure 7.1 Basic schematic of the direct-modulation transmitter ......116

- Figure 7.2 Basic schematic of the direct-modulation transmitter simulation setup ......117

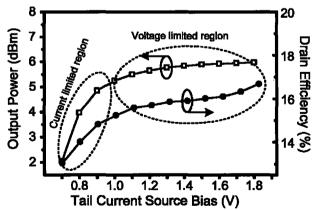

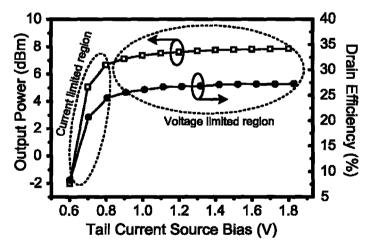

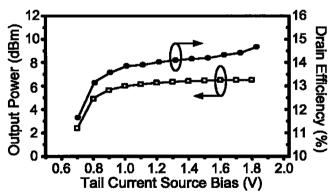

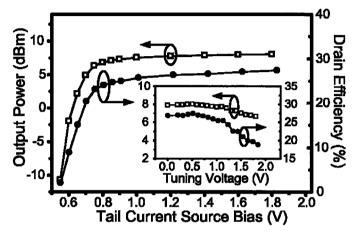

- Figure 7.8 The measured output power and drain efficiency of the 2.4 GHz design as a function of the tail current source bias (transistor M<sub>5</sub> in Figure 7.1) and the tuning voltage applied to the varactors, at a supply voltage of 1.5 V [51]...121

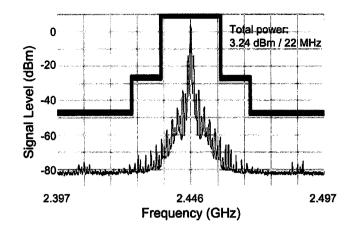

- Figure 7.11 The Measured output spectrum of the 2.4 GHz design, FSK modulated at 1 Mbit/s and ± 190 kHz frequency deviation, at a supply voltage of 1.5 V [51]

- Figure 7.12 Bluetooth data spectrum emission mask [51].....124

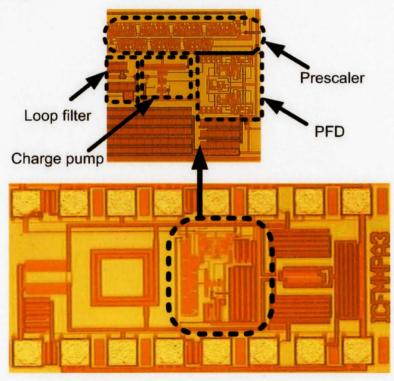

- Figure 8.3Photomicrograph of the designed PLL transmitter......132

- Figure 8.5 Conventional 2.4 GHz transmitter, photomicrograph and circuit schematic.134

# **List of Tables**

| Table 1.1: Performance comparison between the M2A and the Norika pills [16]8        |

|-------------------------------------------------------------------------------------|

| Table 1.2: Power consumption of the building blocks in Figure 1.9 [18]         10   |

| Table 3.1: Summary of the class-E ideal design equations       44                   |

| Table 3.2: Comparison between different power amplifier classes       50            |

| Table 5.1: Performance comparison between the presented power amplifier designs91   |

| Table 6.1: Performance comparison between the presented lock-mode power amplifier   |

| designs113                                                                          |

| Table 7.1: Performance comparison between the presented VCPO designs [51]125        |

| Table 8.1: Performance comparison between state-of-the-art CMOS power amplifier     |

| designs129                                                                          |

| Table 8.2: Performance comparison between state-of-the-art voltage-controlled power |

| oscillators129                                                                      |

# **List of Symbols and Acronyms**

### Symbols

| ω                      | Frequency in radians    |

|------------------------|-------------------------|

| g <sub>m</sub>         | Transconductance        |

| <i>I</i> <sub>DC</sub> | DC current              |

| I <sub>pk</sub>        | Peak current            |

| Iq                     | Quiescent current       |

| $P_{\rm DC}$           | DC power                |

| P <sub>in</sub>        | Input power             |

| Pout                   | Output power            |

| Q                      | Quality factor          |

| $Q_{ m L}$             | Loaded quality factor   |

| R <sub>s</sub>         | Source resistance       |

| $R_{\rm L}$            | Load resistance         |

| Т                      | Temperature             |

| T <sub>r</sub>         | Room temperature        |

| V <sub>DC</sub>        | DC voltage              |

| V <sub>DS</sub>        | Drain to source voltage |

| $V_{\rm gs}$           | Gate to source voltage  |

| $V_{\rm knee}$         | Knee voltage            |

| V <sub>T</sub>         | Threshold voltage       |

| W/L                    | Width over length ratio |

| α                      | Conduction angle        |

| η                      | Drain efficiency        |

| μ                      | Mobility                |

### Acronyms

| AC | Alternating | current |

|----|-------------|---------|

|----|-------------|---------|

| ACPR             | Adjacent channel power ratio                        |

|------------------|-----------------------------------------------------|

| AM               | Amplitude modulation                                |

| CDMA             | Code-division multiple access                       |

| CMOS             | Complementary metal oxide semiconductor             |

| СР               | Compression point                                   |

| DAC              | Digital to analog converter                         |

| DCS              | Defense communications system                       |

| DECT             | Digital enhanced cordless telecommunications        |

| DWN              | Down                                                |

| E-DRAM           | Enhanced dynamic random access memory               |

| EER              | Envelope elimination and restoration                |

| ESD              | Electrostatic discharge                             |

| FoM              | Figure-of-merit                                     |

| FRAM             | Ferroelectric random access memory                  |

| FSK              | Frequency-shift keying                              |

| FPGA             | Field programmable gate-array                       |

| G                | Power gain                                          |

| GaAs             | Gallium arsenide                                    |

| GFSK             | Gaussian frequency-shift keying                     |

| GPS              | Global positioning system                           |

| GSM              | Global system for mobile communications             |

| IIP <sub>3</sub> | Third-order input intercept point                   |

| ILFD             | Injection-locked frequency divider                  |

| ILO              | Injection-locked oscillator                         |

| ILPA             | Injection-locked power amplifier                    |

| IMD              | Inter-modulation distortion                         |

| InP              | Indium phosphide                                    |

| ISM              | Industrial-scientific-medical                       |

| ITRS             | Internacional technology roadmap for semiconductors |

| LAN              | Local area network                                  |

| LMDS             | Local multipoint distribution system                |

|                  |                                                     |

-

| LNA              | Low-noise amplifier                               |  |  |

|------------------|---------------------------------------------------|--|--|

| LO               | Local oscillator                                  |  |  |

| MEMS             | Micro-electro-mechanical systems                  |  |  |

| MICS             | Medical implantable communication systems         |  |  |

| MIM              | Metal-insulator-metal                             |  |  |

| MOSFET           | Metal-oxide semiconductor field effect transistor |  |  |

| NEMS             | Nano-electro-mechanical systems                   |  |  |

| NMOS             | N-type metal-oxide semiconductor                  |  |  |

| OIP <sub>3</sub> | Third-order output intercept point                |  |  |

| OOK              | On-off keying                                     |  |  |

| PA               | Power amplifier                                   |  |  |

| PAE              | Power-added efficiency                            |  |  |

| PCS              | Personal communication services                   |  |  |

| PDC              | Personal digital cellular                         |  |  |

| PFD              | Phase frequency detector                          |  |  |

| PLL              | Phase-locked loop                                 |  |  |

| PM               | Power management                                  |  |  |

| PMOS             | P-type metal-oxide semiconductor                  |  |  |

| PUF              | Power utilization factor                          |  |  |

| PWM              | Pulse-width modulation                            |  |  |

| REF              | Reference                                         |  |  |

| RF               | Radio frequency                                   |  |  |

| RFC              | RFC Radio frequency choke                         |  |  |

| RSFQ             | RSFQ Rapid signal flux quantum                    |  |  |

| SiGe             | Silicon germanium                                 |  |  |

| SiP              | System-in-a-package                               |  |  |

| SoC              | System-on-a-chip                                  |  |  |

| S-parameters     | Scattering parameters                             |  |  |

| SRAM             | Static random access memory                       |  |  |

| TFT              | Thin-film transistors                             |  |  |

| UWB              | Ultra-wide band                                   |  |  |

|                  |                                                   |  |  |

| VCO  | Voltage-controlled oscillator       |

|------|-------------------------------------|

| VCPO | Voltage-controlled power oscillator |

| WBAN | Wireless body area networks         |

| Xtal | Crystal                             |

# **Chapter 1**

### **INTRODUCTION**

The rapid advances in wireless communication systems over the past decades demand continuous improvements in wireless transceiver architecture, efficiency and power capabilities. Since the most power consuming block in a transceiver is the power amplifier, it is considered one of the most challenging blocks and thus, it has attracted a lot of research interests in the recent past. However, very little work has addressed low-power designs since most previous research work focused on higher-power applications such as wireless LAN and Bluetooth. Short-range transceivers are increasingly gaining interest with the emerging low-power wireless applications such as, wireless body area networks (WBAN), wireless sensor networks, smart dusts, biotelemetry and even synthetic insects.

Figure 1.1 shows models of flying and crawling microrobots developed by the University of California [1]. These synthetic insects that could fly or crawl act as smart dust motes (nodes) that can sense and communicate. The crawling microrobot can lift more than 130 times its own weight while consuming only tens of microwatts. The flying microrobot has a wing span of 10-25 mm and consumes less than 10 mW of power provided by solar cells [1]. Such motes are expected to communicate with each other within a wireless sensor network of smart dusts using a transmitted power of 1-3 mW to cover an indoor range of less than 10 meters [2]. Designing power amplifiers for such low transmit power levels is very challenging and not yet thoroughly researched, as compared to high power amplifiers used in traditional transceivers.

Although RF circuits contain fewer devices than digital circuits, RF circuit design is more challenging because second-order effects, non-linearities, noise, mismatch, distortion and parasitic elements must be carefully considered to obtain the required time and amplitude precision [3, 4]. Another reason why RF circuit design is considered more challenging is the lack of automation and synthesis tools, unlike digital circuits, which have well developed tools [4].

Figure 1.1: Flying and crawling microrobot models for wireless sensor networks [1]

For biomedical applications, especially biomedical implantable electronic circuits, RF designers are faced with even more challenges such as electromagnetic radiation exposure safety limits, size and weight of the implantable devices, power supply and power consumption issues and whether the power should be externally supplied through inductive coupling or internally from a battery. Also, due to restrictions on the amount of power transmitted into or out of the human body, there is great need for improving the efficiency of implantable transceivers, even with low-power designs [65].

The choice of technology used depends mainly on the required performance of the targeted market or standard, the level of integration required and most importantly the cost [5]. Traditionally, a mixture of different compound semiconductors was used for designing efficient RF power amplifiers that were connected to the digital circuitry, which is usually implemented in standard CMOS technology, to create a whole systemin-a-package (SiP). However, deep sub-micron CMOS has become a very attractive technology for RF circuit design [7].

### 1.1 Why CMOS?

The main advantages of using current CMOS (180 nm and below) technology in building RF circuits are the high level of integration and cheap cost. Using CMOS in transceiver circuits produces fully integrated system-on-a-chip (SoC) designs at reduced costs, rather than the multiple-die SiP [3, 4, 7]. This furthermore enabled designers to increase system compatibility by developing single chips that could operate at more than one wireless communication standard [1]. Figure1.2 shows the first integration of different technologies as a SoC with a standard CMOS process [6]. Previous designs used compound semiconductors such as SiGe and GaAs instead of standard CMOS for circuits that operate at high-frequencies or transmit high-power levels. However, recent research [8-10] work proved that CMOS designs can fulfill the power requirements of many wireless standards because the maximum operating frequency of MOSFET transistors is continuously increasing with device down-scaling [4]. Future predictions indicate that silicon based technologies will gain even more importance due to their high level of integration [3, 5].

In short-range or biomedical applications, the transmitted power is fairly low and the operating frequency is limited to one of the industrial-scientific-medical (ISM) bands. Usually in biomedical applications, the frequency of the signals transmitted through the human body must be low to minimize the attenuation losses in the body layers and to remain within the safety restrictions [11]. Since both the transmitted power and operating frequency are low, standard CMOS technology becomes a good candidate to be used in biomedical applications. Figure 1.3 shows the application spectrum of some common wireless applications and the corresponding suitable technology. This makes CMOS technology very attractive because its performance is now comparable to traditional compound semiconductors with improved integration compatibility and reduced costs [7]. Figure 1.4 shows a cost, size, speed and switching energy comparison of CMOS technology to some of the emerging technologies such as, molecular devices, quantum cellular automata, rapid signal flux quantum (RSFQ), optical devices, plastic or thin film transistors (TFT), nano-electro-mechanical systems (NEMS), and biologically inspired which represents the human brain for comparison only. More information on these technologies can be found in [6].

Figure 1.3: Application spectrum [6]

Figure 1.4 shows that most of the emerging technologies are superior in a specific range only, which makes them application specific, unlike CMOS that occupies a good area on all axes, which proves that is capable of serving many applications at a reasonable size, cost and speed.

#### **1.2 Biomedical Systems**

Over the past few decades, implantable electronic systems have proven to be very successful in the treatment of many diseases and in improving the quality of care for patients' lives with more advanced and cost-effective condition monitoring [12]. Two-way wireless communication systems can be used to link implanted devices to monitoring systems so that doctors could easily retrieve information about a patient's health and make adjustments on the operation of the implanted devices to ensure optimal treatment [13]. Figure 1.5 shows some of the various locations where electronic systems can be implanted in the human body [14].

Figure 1.4: A comparison between emerging technologies and CMOS [6]

Figure 1.5: Some applications of implantable electronic systems [14]

First generation implantable medical devices used low-frequency inductive links as a means of communication. These systems operated in the hundreds of kilohertz range with data rates lower than 30 kB/sec and over a very short range, which often requires direct contact with the skin. Recent applications that require higher data rates use one of the industrial – scientific - medical (ISM) bands such as the 433 MHz band, the 915 MHz band and the 2.45 GHz band [12]. A 402 - 405 MHz medical implant communications service (MICS) band has been recently allocated specifically for implantable medical devices. The MICS band allows for 10 channels of 300 kHz each and a transmission range of 2 meters with a maximum output power of 25  $\mu$ W [12-14].

The 25  $\mu$ W transmitted power constraint set by the MICS standard applies to the signal outside of the human body, whereas the signal transmitted from the implant should be much higher in order to compensate for losses in the antenna, the matching networks and the body layers. The human body is a partially conductive medium composed of many layers that have different characteristics (dielectric value and conductivity), which is why the human body is not an ideal medium for transmitting RF signals [13]. Other than the fact that the body layers themselves are lossy and these losses increase with frequency, which limits the data rate of the system [11], the different characteristics of each layer cause reflections of the RF signals at the interfaces between the layers [13]. Losses due to the body layers and antenna matching can be more than 40 dB [12], which pose a major challenge for designers.

Biomedical implantable electronic systems can either be powered internally by a battery, or externally using inductive coupling. In both cases there is a scarcity in available power. Also, the impedance of implantable batteries is typically 500  $\Omega$  for a new battery and goes up to 20 k $\Omega$  as the battery is discharged [14]. This sets a limit on the peak current that can be drawn from the battery, which should typically be lower than 10 mA. To reduce the average power in an implanted system, low duty-cycling is used [12], which allows for sending out the data in short bursts keeping the transceiver off for most of the time. Even if the system has a low data rate, the data can be buffered and sent out in groups following a specific duty-cycle. A transceiver should consume less than a few micro-watts in off mode, which should be just enough to "sniff-out" a wakeup signal. The sniffing operation should be immune to noise that could wakeup the system

erroneously. An on-off keyed modulation scheme is a good choice for the wakeup signal since it does not require a local oscillator or receiver synthesizer [12]. Using low duty-cycling could also help reduce the interference with external systems since it reduces the transmission window [15]. Using direct-conversion, which requires less building blocks in the transceiver design, can also help to reduce power consumption in implantable systems. Choosing a constant envelope modulation scheme also reduces power [15] since it allows for the use of non-linear power amplifiers. Constant envelope schemes are also more power efficient since they do not require a high receiver signal-to-noise ratio [14]. A recommended modulation scheme is frequency-shift-keying (FSK) since it provides a good compromise between efficiency, complexity and data rate [12].

In order to reduce the cost of implantable electronic systems, it is recommended to have all components fully-integrated, which also has the benefit of increasing system reliability [12]. Implantable components are more expensive, since they need to pass more tests and qualifications to ensure reliable operation when implanted in the human body. Also, the competition in developing and marketing such components is very low, since most companies fear legal actions in case of device failure [14]. Another challenge faced in designing implantable systems is the placement of the device, since surgeons place the device where it is clinically feasible and convenient for the patient. Therefore, the implanted system should be able to adjust its operation depending on the depth and transmission angles. The antenna should also be capable of automatic tuning to compensate for impedance changes with movement and random placement [12-15].

Figure 1.6 shows how state-of-the-art transceivers can be used to capture images from areas that are not accessible using endoscopes inside the human body [15]. The captured images are wirelessly transmitted to an external receiver to be analyzed by physicians. These devices should be small enough to swallow and flow easily into the small intestine. The power consumption in these devices should be very low in order to last long enough to go through the digestive system, which is typically 6-10 hours.

There are currently two camera pills available in the market, the Norika from RF Systems Labs and the M2A from Given Imaging. Table 1.1 shows a comparison summary between the important aspects of each pill and Figure 1.7 shows a screen capture of the user interface of the Norika pill [16]. Since the Norika pill is not battery

7

powered, there is enough free space to store tissue samples from inside the body and carry medicine that can be sprayed onto infected areas. Temperature measurements and laser therapy are also options that can be added to the Norika pill [16].

Figure 1.6: Swallowable camera system [15]

| Table 1.1: Performance comparison between the M2A and the Norika pills [16] |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

|              | M2A               | Norika             |

|--------------|-------------------|--------------------|

| Dimension    | 11 mm x 26 mm     | 9 mm x 23 mm       |

| Frame rate   | 2 images / second | 30 images / second |

| Power source | Internal battery  | External coupling  |

| Price        | US\$ 450 / each   | US\$ 100 / each    |

### **1.3 RF CMOS Transceivers**

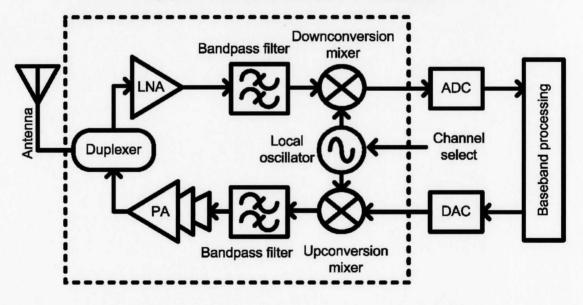

The main blocks of a typical RF transceiver are low-noise amplifiers (LNA), mixers, voltage-controlled-oscillators (VCO), filters, power amplifiers (PA) and power management circuits (PM), which are usually off-chip, transmit/receive switches, and distributed amplifiers. Figure 1.8 shows a simplified block diagram of the basic building blocks in a typical RF wireless transceiver [17]. The total area of an RF transceiver is mainly determined by the number of embedded passive elements [4].

Figure 1.7: Screen shot of the Norika user interface [16]

Figure 1.8: Block diagram of a typical RF transceiver, reproduced from [17]

Since the power amplifier is the most power consuming block of an RF transceiver, the efficiency of the power amplifier governs the overall efficiency of the whole transceiver. Figure 1.9 shows an example of an RF CMOS transmitter circuit; and the corresponding power consumption of each part is shown in Table 1.2 [18]. This example shows the importance of improving the efficiency in RF power amplifier designs

to minimize losses as much as possible and to enhance the overall efficiency of the transceivers.

Figure 1.9: An example of an RF transmitter circuit [18]

| Table 1.2: Power    | consumption | of the | huilding  | blocks in | Figure  | 19  | [18] |

|---------------------|-------------|--------|-----------|-----------|---------|-----|------|

| 1 4010 1.2. 1 01101 | consumption | ofine  | Unitatity | Diocks in | 1 iguic | 1.2 | 101  |

|                 | Power Consumption | Proportion in % |

|-----------------|-------------------|-----------------|

| PA output power | 9.5 mW            | 38              |

| PA losses       | 15 mW             | 60              |

| Other blocks    | 0.5 mW            | 2               |

| Total           | 25 mW             | 100             |

To reduce the building blocks of an RF transceiver and minimize the amount of lossy passive elements; RF transceivers are migrating from heterodyne to homodyne or direct conversion architectures [5].

### **1.4 Motivation**

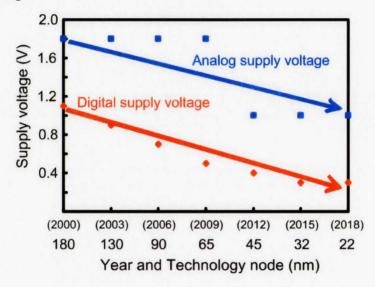

One of the major challenges faced in biotelemetry applications is designing circuits with low-power consumption that operate from very low-supply voltages [65, 66]. However, having a low-supply voltage reduces the linearity of an amplifier and makes the output impedance transformation network more complex due to the need for a smaller load. In biotelemetry applications, a small load value is not required since the power amplifier is not expected to handle high output power levels. The reduction in linearity can also be tolerated in biomedical applications since the utmost concern is efficiency; and the available power from a saturated device is almost double the available power from a linear device [5]. Also, in order to integrate the whole transceiver in a single chip, RF and analog designs should be able to operate from low supply voltages since the supply voltage in digital circuits is continuously decreasing with device down-scaling [66]. This is one of the main reasons why mixed signal development takes longer than digital and memory circuits [4]. Figure 1.10 shows the projected supply voltage reduction for both analog and digital circuits based on the 2003 ITRS roadmap (including 2004 updates) [6]. The continuously decreasing breakdown voltage and maximum voltage limits of CMOS transistors is another motivation for designing power amplifiers that operate from very low-supply voltages.

Figure 1.10: ITRS projected supply voltage reduction [6]

Since low-power power amplifiers (PAs) require larger output loads than highpower PAs, larger DC-feed inductors are required, which have very low quality factors when implemented on-chip. As a result, PAs designed for low-power applications have considerably lower efficiencies than high-power PAs when on-chip components are used. The motivations for improving efficiency in previous work were all driven by high-power applications in order to minimize temperature effects, which are the major concern in base stations, or to extend the operating battery life-time in portable hand held devices. The main drivers for improving efficiency for low-power applications are biomedical implantable electronic systems and wireless sensor networks. The objective of this thesis is to improve the efficiencies of power amplifiers targeted for low-power operation and thus, improve the overall efficiency of the transceiver. Such amplifiers can be suitable for biomedical applications that operate from very low-supply voltages or short-range applications that do not require large output power levels such as wireless sensor networks. Previous research [2, 18] focused on using linear classes for low-power applications since they require a lower input drive, they allow for the use of variable envelope modulation schemes and they have a lower harmonic content in the output signal, which eliminates the need for output filtering.

To obtain maximum efficiency, this work was limited to constant envelope modulation schemes to allow for the use of non-linear, switch-mode power amplifiers. Using a non-linear amplifier has an added advantage of operating from very low-supply voltages since maintaining high linearity is no longer a design goal. A non-linear class-E topology was adopted in this work, which to the authors knowledge, represents the first use of this topology in low-power applications. The major drawback of using such an amplifier is the need for an output filter, that will degrade the efficiency when implemented on-chip. The results of this work show that the degraded efficiency after using an on-chip filter is still higher than the efficiency of a linear class power amplifier. Also, since the circuit is to transmit a signal from inside the human body, the higher order harmonics will be greatly attenuated by the body tissues [11], which would eliminate the need for an on-chip filter.

A novel mode-locking power amplifier is proposed in this work that uses a superharmonic injection-locked VCO as a non-linear power amplifier. This topology can be used as a good alternative for low-power or low-frequency applications, since it minimizes the number of large size, low-Q inductors required in the design, reducing the total area of the circuit, which makes it suitable for minuscule transmitter designs.

Some ideas on improving transmitter efficiency and minimizing the number of building blocks of a transmitter are presented using a high-efficiency cross-coupled differential negative- $g_m$  VCO as a direct baseband modulation transmitter. Some ideas to further improve the efficiency of this transmitter are proposed as part of the future work by using a class-E power VCO instead of the negative- $g_m$  VCO. The main disadvantage of using a VCO as a direct-FM transmitter is the inaccuracy in the oscillation frequency,

12

#### Chapter 1: Introduction

which may vary with temperature or locking to external interference. Using a highefficiency phase-locked-loop (PLL) with an external crystal reference can solve this problem. As part of the proposed future work, a PLL transmitter is also presented as an efficient transmitter for low-power applications. Finally, a basic conventional transmitter design is proposed as part of the future work, to be compared to the direct baseband modulation transmitter presented in this work.

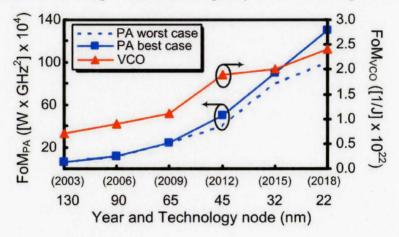

Figure 1.11 shows the projected figure-of-merit (FoM) of power amplifiers and voltage-controlled oscillators for future technologies [6]. The major improvements in the FoM of power amplifiers are mainly due to the improvements in the cut-off frequency of CMOS transistors and the improvement in the quality factor of on-chip inductors.

Figure 1.11: ITRS projected FoM for PAs and VCOs for future technology nodes [6]

#### **1.5 Thesis Organization**

A brief introduction to CMOS RF power amplifiers is presented in chapter 2. This chapter starts by explaining a simple power amplifier, and then some of the important characteristics of power amplifiers are presented, followed by the main practical design considerations related to power amplifiers. Some practical challenges faced when dealing with low-power designs, are also presented.

Chapter 3 explains the different existing power amplifier topologies, which are divided into three main groups, current-mode classes, switch-mode classes and lock-

mode classes. A FoM suitable to compare power amplifiers is also proposed in this chapter.

Chapter 4 explains the concept of using a power oscillator as a transmitter. It starts by explaining the basic differential cross-coupled negative- $g_m$  voltage-controlled oscillator. After that, the concept of superharmonic injection-locking is presented. The chapter ends by presenting a FoM that is proposed to compare power oscillators.

Chapter 5 shows the design, simulations and measurement results of the implemented switch-mode power amplifier circuits. A 900 MHz class-E design is presented here, followed by three 2.4 GHz class-E designs.

In Chapter 6, two novel mode-locking power amplifier designs operating at 400 MHz and 2.4 GHz are presented. The chapter starts with the circuit design, then the simulation results are shown, followed by the layout and finally, the measurement results are shown at the end of the chapter.

Chapter 7 shows the implemented direct-modulation transmitter circuits. Two CMOS cross-coupled negative- $g_m$  voltage controlled oscillators operating at 400 MHz and 2.4 GHz used as single-block direct-modulation transmitters, are presented in this chapter.

Finally, chapter 8 will conclude with a summary of this work and a comparison to previous published works. Future work and areas for improvement will also be given in this chapter.

## **Chapter 2**

# INTRODUCTION TO CMOS RF POWER AMPLIFIERS

The main goal of a power amplifier is to provide adequate power gain to an input signal, to be able to drive a transmission antenna with minimum loss in the amplifier itself. This chapter explains some of the basic information related to power amplifier designs. Section 2.1 shows a simple power amplifier, explaining how it functions. Section 2.2 presents the important characteristics and definitions of power amplifiers. Some of the most important practical design considerations related to power amplifiers are discussed in Section 2.3. Finally, the chapter's summary is presented in Section 2.4.

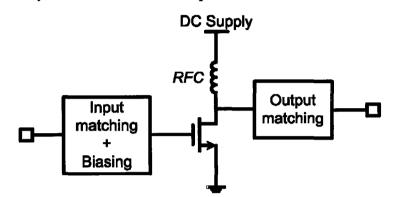

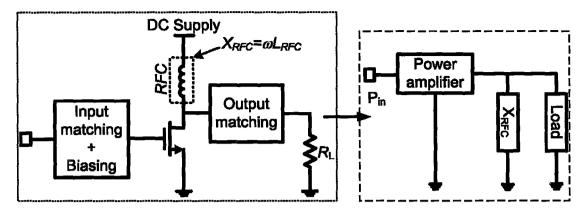

## 2.1 Simple Power Amplifier

A simple power amplifier is illustrated in Figure 2.1. It consists of an input impedance matching network that matches the input impedance of the power amplifier to the source impedance, an amplifying stage that boosts the signal and an output impedance matching network that matches or transforms the output load to the desired output impedance value. The DC biasing is applied at the input and output ports of the amplifying stage. Inductor *RFC* is a large inductor that is usually referred to as the RF-choke. It emulates a DC current source that could sustain negative and positive voltages acting like an AC block to prevent feedback or oscillation through the DC supply.

What makes a power amplifier different from any other amplifier, such as a voltage amplifier (operational amplifier) or current amplifier (operational transconductance amplifier), is the way the input and output impedances are matched. A typical voltage amplifier provides a very high (ideally infinite) input impedance and a very low (ideally zero) output impedance to allow for maximum voltage transfer. On the other hand, a typical current amplifier provides a very low input impedance and a very high output impedance. The input of a power amplifier is matched to satisfy the maximum power transfer theorem, having at best cases a 50 % power transfer from the source to the amplifier's input. The output matching network of a power amplifier is matched differently, as will be shown in Chapter 3.

Figure 2.1 Simple power amplifier

Power amplifiers can be divided into narrowband designs and broadband designs. In most communication systems, narrowband power amplifiers are used since they are usually more efficient [19]. However, some intended narrowband designs may become wideband due to the low quality factors of the passive components used.

## 2.2 Important Characteristics of Power Amplifiers

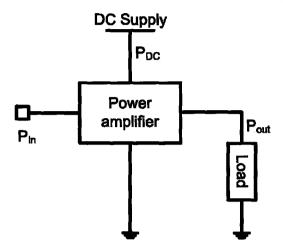

Since the signal transmitted through an antenna is characterized in terms of its power level, most of the definitions and characteristics that are related to power amplifiers deal in terms of power. Figure 2.2 shows the basic parameters of a simple power amplifier and this figure will be used to clarify the basic definitions explained in the following subsections.

## 2.2.1 Power Gain

The power gain of a power amplifier can be defined as the output power delivered to the output load divided by the input power available from the input source or previous stage. Based on Figure 2.2, the power gain can be expressed as:

$$G = \frac{P_{out}}{P_{in}},$$

(2.1)

where G is the power gain,  $P_{out}$  is the output power and  $P_{in}$  is the input power.

Figure 2.2 The basic parameters of a simple power amplifier

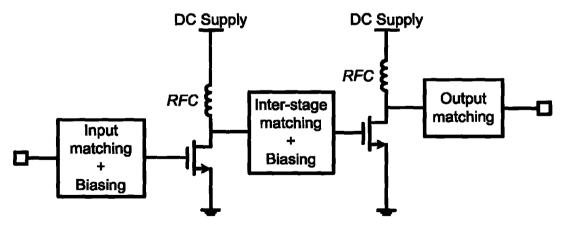

To increase the overall power gain of a power amplifier, which in turn decreases the required input drive, a multistage configuration can be used. Figure 2.3 shows a simple two stage power amplifier. The inter-stage matching network is used to guarantee maximum power transfer between the two stages. In a multistage configuration, care should be taken to avoid stability problems that could arise due to feedback from one stage to the other.

Figure 2.3 Simple two-stage power amplifier

Another important parameter is the power utilization factor (PUF), which is a measure of the output power capability of a power amplifier. It also gives an indication

for the electrical stress that the active device is being exposed to since it is defined as the output power per active device normalized for a 1 V peak drain voltage and a 1 A peak drain current [20].

#### 2.2.2 Efficiency

Power amplifier efficiency can be expressed as drain efficiency ( $\eta$ ) or power-added efficiency (PAE). Based on Figure 2.2, the drain efficiency can be expressed as:

$$\eta = \frac{P_{out}}{P_{DC}},\tag{2.2}$$

where  $\eta$  is the drain efficiency,  $P_{out}$  is the output power and  $P_{DC}$  is the DC power. The PAE however, includes the power gain, since it is defined as the ratio between the output power minus the input power to the DC power. This is a more practical measure of the power amplifier's efficiency since it measures how much power the amplifier adds to the input signal efficiently. Based on Figure 2.2, the PAE can be expressed as:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} = \frac{P_{out}}{P_{DC}} \times \left(1 - \frac{1}{G}\right) = \eta \times \left(1 - \frac{1}{G}\right).$$

(2.3)

It is important to note that the maximum efficiency of the power amplifier is achieved when it is delivering its maximum output power, which is ideally equal to the DC power.

#### 2.2.3 Linearity

This is an important characteristic of power amplifiers since there is a tradeoff between linearity and efficiency. Non-linearities in power amplifiers are due to the non-linearities of the active components used. Spectrally efficient modulation techniques usually produce non-constant envelope signals. When applying these signals to a non-linear power amplifier, the signals will suffer amplitude-modulation (AM) to phase-modulation (PM) conversion and spectral growth, which will lead to adjacent channel interference. Spectral growth is measured by the adjacent channel power ratio (ACPR), which is the ratio of the power in the channel to the power in the adjacent channel [1].

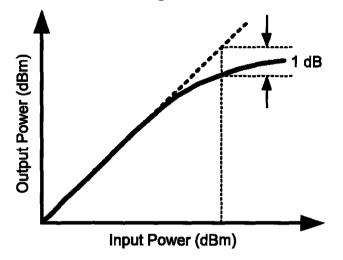

#### 2.2.3.1 Gain Compression (AM-AM Conversion)

Gain compression occurs when the output and input power levels no longer share a linear power relationship. A common measure used to quantify this effect is the 1 dB gain compression point, which defines the point at which the power gain drops by 1 dB below what is expected. This effect is shown in Figure 2.4.

Figure 2.4 The effect of gain compression on the output power

#### 2.2.3.2 AM-PM Conversion

The AM-PM conversion is a result of a phase shift in the power amplifier caused by the amplitude of the signal. This is also a result of the active element's non-linearities such as the drain-source capacitance [19].

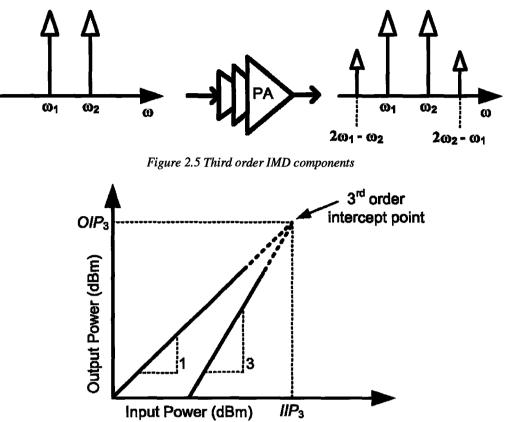

#### 2.2.3.3 Inter-Modulation Distortion (IMD)

Harmonic distortion results in higher frequency components appearing at integer multiples of the output signal's frequency. Inter-modulation distortion is generated by multiple inputs and is also caused by non-linearities of the amplifier and active elements. The IMD products of  $(n+m)^{th}$  order can be give by:

$$n\omega_1 \pm m\omega_2.$$

(2.4)

An example of the third order IMD components is shown in Figure 2.5. An often used measure for the linearity of a system uses the  $IIP_3$  and  $OIP_3$ , which are the  $3^{rd}$  order input and output intercept points respectively. This is a measure of how fast the power of

the  $3^{rd}$  order component reaches the power of the fundamental signal, as shown in Figure 2.6.

Figure 2.6 Third order intercept points

## 2.3 Design Considerations

### 2.3.1 Conjugate Match and Load Line Match

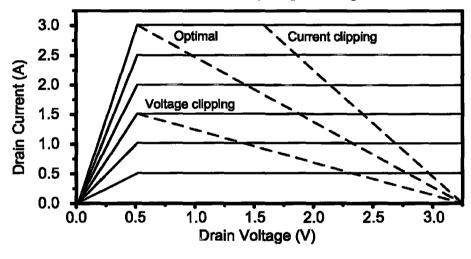

Conjugate matching is done by setting the value of the load impedance equal to the value of the generators impedance in magnitude and opposite in phase. This is done to deliver maximum output power to the load, which is required since the amplifier achieves maximum efficiency when operating at its maximum power. In practice the maximum output power an amplifier can deliver is limited to the maximum power rating of the transistor and the value of the supply voltage or DC headroom available to the transistor. To account for this limitation, a lower output loading resistance ( $R_L$ ) is used, which is

referred to as the load-line match optimal resistance  $(R_{opt})$ . This represents a compromise in extracting maximum power and operating within the specified limits. An output matching network can be used to transform the actual output load value to the desired optimal load value. If  $R_L$  drops below  $R_{opt}$ , then current clipping of the output will occur, whereas if  $R_L$  is too high, voltage clipping will occur, as shown in Figure 2.7 [3]. The value of  $R_{opt}$  can be expressed as:

$$R_{opt} = \frac{V_{\max}}{I_{\max}},$$

(2.5)

where  $V_{\text{max}}$  is the maximum drain voltage and  $I_{\text{max}}$  is the maximum drain current, as shown in Figure 2.7. This improves the output power, however it could cause reflections in the rest of the system that are a fraction of the matching degree between the output load or the antenna and the system. An isolator or balanced amplifier could be used to solve the reverse termination mismatch caused by the power amplifier [3].

Figure 2.7 Optimal load line

#### 2.3.2 Effect of the Transistor Knee-Voltage

The knee-voltage ( $V_{\text{knee}}$ ), which is also known as the pinch-off voltage, is the voltage point that divides the saturation and linear regions of a transistor. It is defined as the point at which the drain current reaches 95 % of  $I_{\text{max}}$ . The optimum load resistance in this case is [3]:

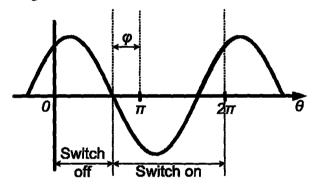

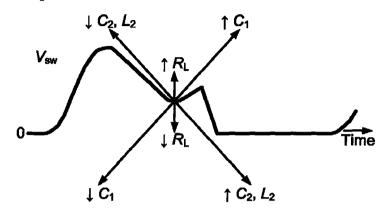

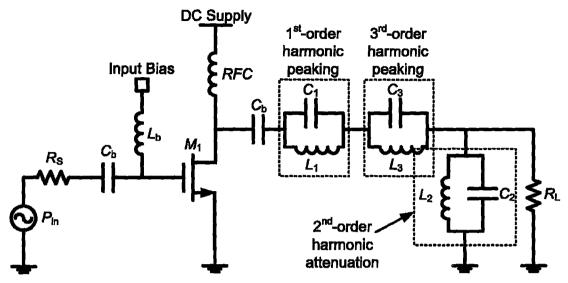

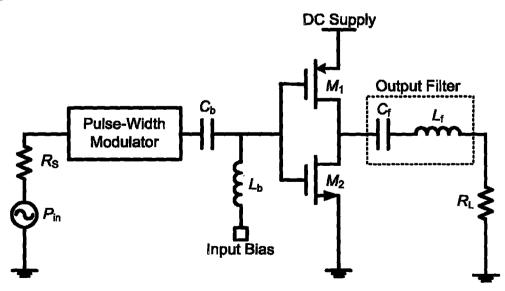

$$R_{opt} = \frac{V_{\max} - V_{knee}}{I_{\max}},\tag{2.6}$$