# CMOS BASED SINGLE PHOTON AVALANCHE DIODE AND TIME-TO-DIGITAL CONVERTER TOWARDS PET IMAGING APPLICATIONS

# CMOS BASED SINGLE PHOTON AVALANCHE DIODE AND TIME-TO-DIGITAL CONVERTER TOWARDS PET IMAGING APPLICATIONS

By

Zeng Cheng B.A.Sc. Xi'an Jiaotong University, 2009 M.A.Sc. Xi'an Jiaotong University, 2012

A Thesis Submitted to the School of Graduate Studies in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> McMaster University Hamilton, Ontario, Canada

© Copyright by Zeng Cheng, September 2016

Doctor of Philosophy (2016) (Electrical and Computer Engineering) McMaster University Hamilton, Ontario

| TITLE:           | CMOS Based Single Photon Avalanche Diode and Time-    |

|------------------|-------------------------------------------------------|

|                  | to-Digital Converter towards PET Imaging Applications |

|                  |                                                       |

| AUTHOR:          | Zeng Cheng,                                           |

|                  | B.A.Sc. Xi'an Jiaotong University, Xi'an, China       |

|                  | M.A.Sc. Xi'an Jiaotong University, Xi'an, China       |

|                  |                                                       |

| SUPERVISOR:      | Prof. M. Jamal Deen                                   |

|                  | Prof. Hao Peng (Co-supervisor)                        |

|                  |                                                       |

| NUMBER OF PAGES: | xvii, 139                                             |

### Abstract

Time-of-flight (ToF) positron emission tomography (PET) is a non-invasive, functional biomedical imaging modality. It can be used to determine the metabolic activity difference between lesion and normal cells, thus, making it possible to detect tumors at their early stages. In such a system, photomultiplier tubes (PMTs) are typically employed as the photon sensors. However, PMTs are of large size, have fragile package, consume large power, require high bias voltage and are costly. To pursue the benefits of ToF PET system, there is a growing need for research on new types of photodetectors and photo-detection systems.

This work focuses on studying and building a compact, low-cost time-of-flight photo-sensing system. To achieve this goal, we choose a standard digital CMOS technology to design and fabricate the photodetectors and associated electronics. A CMOS single photon avalanche diode (SPAD) is selected because of its low-cost, ultrahigh light sensitivity and fast speed. Being implemented in IBM's 130nm CMOS process, the impacts of silicide layer on the overall performances of the SPAD are investigated. By eliminating silicide on the active area of SPAD, a fivefold improvement in both dark noise and photon detection efficiency are demonstrated. Then, a SPAD comprehensive analytical model is proposed and implemented in Verilog-A hardware description language. This model includes all the noise sources and will provide useful guidance in optimizing SPAD and the associated circuits.

A time-to-digital converter (TDC) is proposed and designed in the same 130nm CMOS process. The TDC is capable to digitize time intervals with 7.3ps resolution and covers up to 9ns dynamic range. The proposed TDC achieves state-of-the-art low power consumption. It will be used to extract the time-of-flight information, and to improve the image's single-to-noise ratio (SNR) in a ToF PET imaging system.

Finally, a time-of-flight sensing system prototype is built by integrating the CMOS SPADs and TDC on a printed circuit board. Based on the preliminary measurement results, this system achieves 440ps coincidence timing resolution. Factors of 2.5 and 6.1 improvements in image SNR and effective sensitivity, respectively, are expected with this prototype in ToF PET imaging applications.

### Acknowledgements

Firstly, I would like to express my sincere gratitude and appreciation to my supervisor, Distinguished University Professor Dr. M. Jamal Deen, for his support and guidance over the past four years. It is a great honor and fortune for me to work under the supervision of such an outstanding mentor and scholar. Being always motivational and supportive, he has helped, encouraged and guided me throughout this research work. He is a role model to me, from professional research, to teaching and to personal aspect, and so on. I will never stop learning from him.

I would also like to express my deep appreciation and thanks to my co-supervisor Professor Hao Peng for his help, guidance and encouragement. He guided me into this interdisciplinary research. His door is always open for me for technical supports and insightful discussions. All these helps are greatly appreciated.

My sincerest thanks also go to Professor Nicola Nicolici and Professor Chih-Hung Chen for being members of my supervisory committee. They offer insightful advices and support during my research and take their valuable time to review my thesis.

Next, I would like to the administrative and technical staff of my department at McMaster University: Cheryl Gies, Tyler Ackland and Ron Harwood. Especially, Tyler spent lots of time helping me with the printed circuit boards used in my measurements.

Thanks Canadian Microelectronics Corporation (CMC) for their timely technical support and arranging the fabrication of my test chips.

My thanks also go to my dear colleagues at the Nanoelectronics-Optoelectronics Research Laboratory. Dr. Zhiyun Li, Dr. Darek Palubiak and Dr. Tianyi Guo offered numerous help and suggestion for my work. It is also a great pleasure and memorable experience working together with the other members, Hythm Afifi, Hani Alhemsi, Mrwan Alayed, Yiheng Qin, Si Pan and Sumit Majumder.

Last but not the least, I sincerely thank my parents for their unconditional support and encouragement over all these years, and my dear wife, Xiaoqing Zheng, for her endless love and for always being there for me and putting me first. This thesis is dedicated to them.

## **Table of Contents**

| ABSTRACT                                                                                                                                                | III |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                                                                                                        | IV  |

| TABLE OF CONTENTS                                                                                                                                       | V   |

| LIST OF ABBREVIATIONS                                                                                                                                   | IX  |

| LIST OF FIGURES                                                                                                                                         | XI  |

| CHAPTER 1 INTRODUCTION                                                                                                                                  | 1   |

| 1.1. Application Background                                                                                                                             |     |

| <ul><li>1.1.1. Positron Emission Tomography (PET) Imaging</li><li>1.1.2. Time-of-Flight PET</li><li>1.1.3. Combined Imaging Modality: PET/MRI</li></ul> | 3   |

| 1.2. Brief Review on Existing Technologies                                                                                                              |     |

| 1.2.1. Photodetector Technologies         1.2.2. TDC Technologies                                                                                       |     |

| 1.3. Research Motivations                                                                                                                               |     |

| 1.4. Research Contributions                                                                                                                             |     |

| 1.5. Thesis Organizations                                                                                                                               |     |

| CHAPTER 2 ANALYTICAL MODELING OF SINGLE PHOTON AV                                                                                                       |     |

| DIODE                                                                                                                                                   |     |

| 2.1. Background of SPAD Modeling                                                                                                                        |     |

| 2.2. SPAD Analytical Modeling                                                                                                                           |     |

| 2.2.1. Static Behavior Modeling                                                               |                                                 |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------|

| 2.2.2. Dynamic Behavior Modeling                                                              |                                                 |

| 2.2.3. Statistical Behavior Modeling                                                          |                                                 |

| 2.2.4. Other Considerations of Temperature Dependence                                         |                                                 |

| 2.3. Parameter Extraction                                                                     |                                                 |

| 2.4. Simulation and Experimental Validation                                                   | 39                                              |

| 2.4.1. Simulation Setup                                                                       |                                                 |

| 2.4.2. DCR Results                                                                            |                                                 |

| 2.4.3. After-Pulsing Results                                                                  | 43                                              |

| 2.5. Conclusions                                                                              | 46                                              |

| CHAPTER 3 IMPACT OF SILICIDE LAYER IN CMOS SPAD DESIG                                         | GN 47                                           |

| 3.1. SPAD in CMOS Technology and the Silicide Layer                                           | 47                                              |

|                                                                                               |                                                 |

| 3.2. SPAD Design in 130 nm standard CMOS                                                      | 49                                              |

| <b>3.2. SPAD Design in 130 nm standard CMOS</b>                                               |                                                 |

|                                                                                               | 49                                              |

| 3.2.1. SPAD Structure                                                                         | 49<br>51                                        |

| <ul><li>3.2.1. SPAD Structure</li><li>3.2.2. I-V and Breakdown Voltage Measurements</li></ul> | 49<br>51<br>                                    |

| <ul> <li>3.2.1. SPAD Structure</li></ul>                                                      | 49<br>51<br><b>53</b><br>54                     |

| <ul> <li>3.2.1. SPAD Structure</li></ul>                                                      | 49<br>51<br><b>53</b><br>54<br>56               |

| <ul> <li>3.2.1. SPAD Structure</li></ul>                                                      | 49<br><b>5</b> 1<br><b>53</b><br>54<br>56<br>57 |

| <ul> <li>3.2.1. SPAD Structure</li></ul>                                                      |                                                 |

| <ul> <li>3.2.1. SPAD Structure</li></ul>                                                      |                                                 |

| <ul> <li>3.2.1. SPAD Structure</li></ul>                                                      |                                                 |

| CHAPTER 4 TIME-TO-DIGITAL CONVERTER DESIGN IN CMOS<br>Technology | 68  |

|------------------------------------------------------------------|-----|

| 4.1. CMOS TDC Background                                         |     |

| <b>4.1.</b> CWIOS TDC Dackground                                 |     |

| 4.1.1. TDC in Biomedical Imaging Applications                    | 69  |

| 4.1.2. Performance Metrics of TDC                                | 72  |

| 4.1.3. Existing Digital TDC Architectures                        | 75  |

| 4.2. Operation Principles of the Proposed TDC                    | 80  |

| 4.3. Circuit Implementation                                      | 82  |

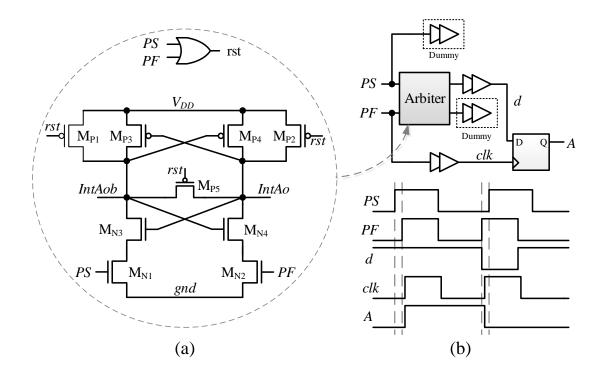

| 4.3.1. Gateable Ring Oscillator                                  | 83  |

| 4.3.2. Arbiter                                                   |     |

| 4.3.3. Single-Transition End-of-Conversion Detection Array       | 87  |

| 4.3.4. Loop Counter                                              | 89  |

| 4.3.5. Enable Generation Block                                   | 90  |

| 4.4. Measurement and Results                                     | 90  |

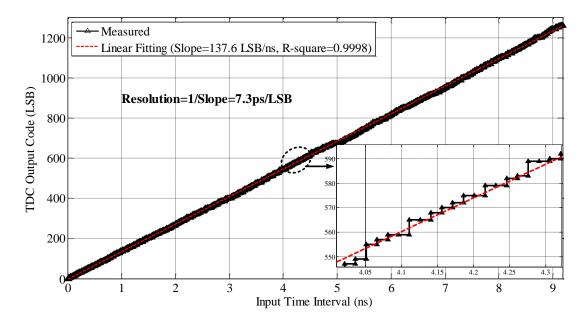

| 4.4.1. Input-Output Characteristic                               | 91  |

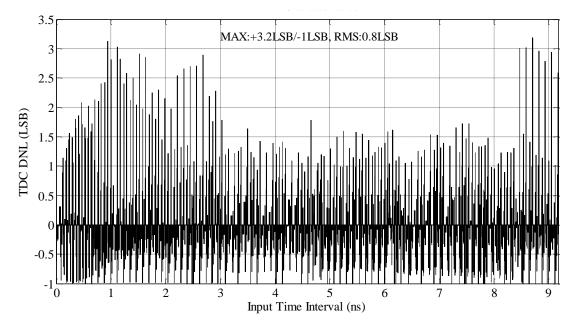

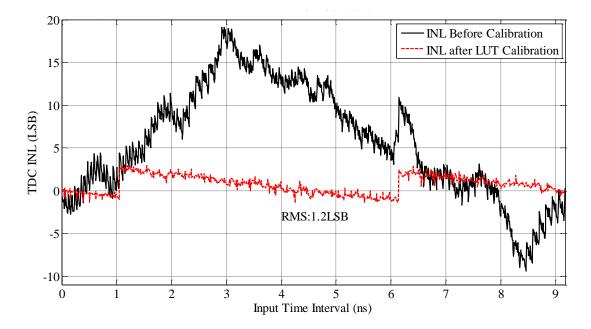

| 4.4.2. Nonlinearities                                            | 92  |

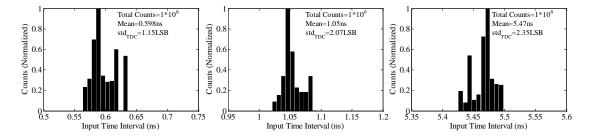

| 4.4.3. Single-shot Precision                                     | 93  |

| 4.5. Conclusions                                                 | 95  |

| CHAPTER 5 PROTOTYPE DEMONSTRATION OF THE SENSING SYS             |     |

| FOR TOF MEASUREMENT                                              | 97  |

| 5.1. System Integration                                          | 97  |

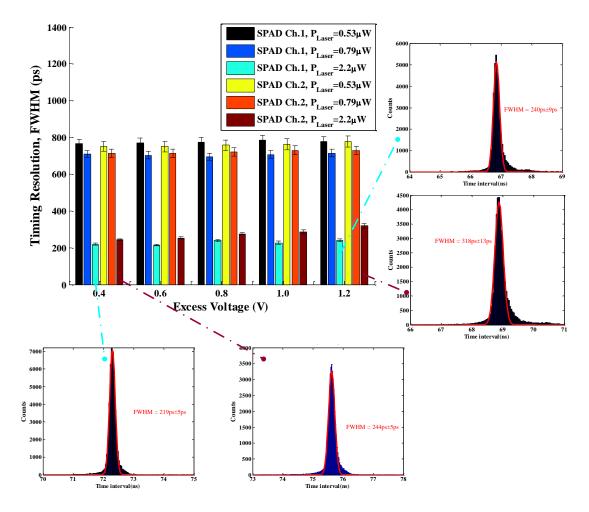

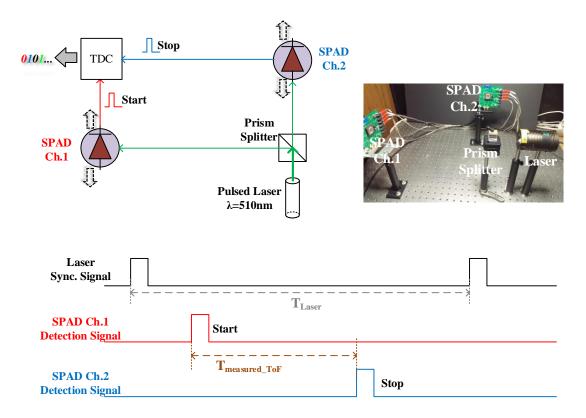

| 5.2. System Characterization                                     | 100 |

| 5.3. Time-of-Flight Measurement                                  | 103 |

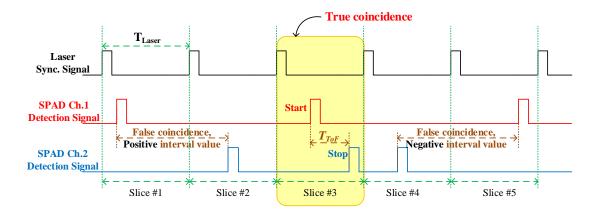

| 5.3.1. Considerations on False Coincidence Events                | 104 |

| 5.3.2. Measurements and Calibrations                             | 106 |

| 5.3.3. Impact of the Timing Resolution on Image Quality          | 108 |

| 5.4. Conclusions                                     | 109 |

|------------------------------------------------------|-----|

| CHAPTER 6 CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE |     |

| WORK                                                 | 111 |

| 6.1. Summary and Discussion                          | 111 |

| 6.2. Recommendations for Future Work                 | 114 |

| References                                           | 119 |

# **List of Abbreviations**

| ADC                                                    | Analog-to-Digital Converter                                                                                                                                                                                             |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADPLL                                                  | All-Digital Phase-Locked-Loop                                                                                                                                                                                           |

| APD                                                    | Avalanche Photodiode                                                                                                                                                                                                    |

| ASIC                                                   | Application Specific Integrated Circuit                                                                                                                                                                                 |

| CIS                                                    | CMOS Imaging Sensor                                                                                                                                                                                                     |

| CMOS                                                   | Complementary Metal-Oxide-Semiconductor                                                                                                                                                                                 |

| CR                                                     | Counting Rate                                                                                                                                                                                                           |

| СТ                                                     | Computed Tomography                                                                                                                                                                                                     |

| DCR                                                    | Dark Count Rate                                                                                                                                                                                                         |

| DFF                                                    | D-Flip-Flop                                                                                                                                                                                                             |

| DLL                                                    | Delay-Locked-Loop                                                                                                                                                                                                       |

| DNL                                                    | Differential Nonlinearity                                                                                                                                                                                               |

| dSiPM                                                  | Digital Silicon Photomultiplier                                                                                                                                                                                         |

| DSM                                                    | Deep Sub-Micron                                                                                                                                                                                                         |

|                                                        |                                                                                                                                                                                                                         |

| DT                                                     | Dead Time                                                                                                                                                                                                               |

| DT<br>FDG                                              | Dead Time<br>Fluorodeoxyglucose                                                                                                                                                                                         |

|                                                        |                                                                                                                                                                                                                         |

| FDG                                                    | Fluorodeoxyglucose                                                                                                                                                                                                      |

| FDG<br>FF                                              | Fluorodeoxyglucose<br>Fill Factor                                                                                                                                                                                       |

| FDG<br>FF<br>FLIM                                      | Fluorodeoxyglucose<br>Fill Factor<br>Fluorescence Lifetime Imaging Microscopy                                                                                                                                           |

| FDG<br>FF<br>FLIM<br>FoV                               | Fluorodeoxyglucose<br>Fill Factor<br>Fluorescence Lifetime Imaging Microscopy<br>Field-of-View                                                                                                                          |

| FDG<br>FF<br>FLIM<br>FoV<br>FPGA                       | Fluorodeoxyglucose<br>Fill Factor<br>Fluorescence Lifetime Imaging Microscopy<br>Field-of-View<br>Field Programmable Gate Array                                                                                         |

| FDG<br>FF<br>FLIM<br>FoV<br>FPGA<br>FWHM               | Fluorodeoxyglucose<br>Fill Factor<br>Fluorescence Lifetime Imaging Microscopy<br>Field-of-View<br>Field Programmable Gate Array<br>Full-Width at Half-Maximum                                                           |

| FDG<br>FF<br>FLIM<br>FoV<br>FPGA<br>FWHM<br>GRO        | Fluorodeoxyglucose<br>Fill Factor<br>Fluorescence Lifetime Imaging Microscopy<br>Field-of-View<br>Field Programmable Gate Array<br>Full-Width at Half-Maximum<br>Gated Ring Oscillator                                  |

| FDG<br>FF<br>FLIM<br>FoV<br>FPGA<br>FWHM<br>GRO<br>HDL | Fluorodeoxyglucose<br>Fill Factor<br>Fluorescence Lifetime Imaging Microscopy<br>Field-of-View<br>Field Programmable Gate Array<br>Full-Width at Half-Maximum<br>Gated Ring Oscillator<br>Hardware Description Language |

| I-V  | Current-Voltage                  |

|------|----------------------------------|

| LoR  | Line-of-Response                 |

| LSB  | Least Significant Bit            |

| LUT  | Look-Up-Table                    |

| MRI  | Magnetic Resonance Imaging       |

| PCB  | Printed Circuit Board            |

| PDE  | Photon Detection Efficiency      |

| PET  | Positron Emission Tomography     |

| PMT  | Photomultiplier Tube             |

| PQPR | Passive Quench, Passive Reset    |

| PVT  | Process, Voltage and Temperature |

| RO   | Ring Oscillator                  |

| SEM  | Scanning Electron Microscope     |

| SiPM | Silicon Photomultiplier          |

| SNR  | Signal-to-Noise Ratio            |

| SPAD | Single Photon Avalanche Diode    |

| SRH  | Shockley-Read-Hall               |

| TDC  | Time-to-Digital Converter        |

| TDL  | Tapped-Delay-Line                |

| TEM  | Transmission Electron Microscope |

| ToF  | Time-of-Flight                   |

| VDL  | Vernier Delay Line               |

# **List of Figures**

| Figure 1-1, Schematic illustration of a PET imaging system. (Reprinted from [1], [2] with permission granted)                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2, Concept diagram of ToF PET comparing with conventional PET 4                                                                                                                                                                                                       |

| Figure 1-3, Illustration of the SNR increase of a ToF PET system over a conventional PET system                                                                                                                                                                                |

| Figure 1-4, Two examples of the fusion images obtained from the combined PET/MRI imaging. (Reproduced from [18], [19] with permission granted. Copyright by the Society of Nuclear Medicine and Molecular Imaging Inc.)                                                        |

| Figure 1-5, Schematic diagram of a typical PMT with a scintillation crystal. (Reprinted from [20] with permission granted.)                                                                                                                                                    |

| Figure 1-6, Depletion region of an APD device                                                                                                                                                                                                                                  |

| Figure 1-7, Principle operation of SPAD. (a) The avalanche breakdown process and (b)<br>The typical current/voltage curve                                                                                                                                                      |

| Figure 1-8, Conceptual illustration of an analog-type TDC. (Reprinted from [75] with permission granted.)                                                                                                                                                                      |

| Figure 1-9, Conceptual illustration of a time stretching TDC. (Reprinted from [75] with permission granted.)                                                                                                                                                                   |

| Figure 1-10, Diagram of a conventional tapped delay line                                                                                                                                                                                                                       |

| Figure 1-11, Diagram of a DLL TDC                                                                                                                                                                                                                                              |

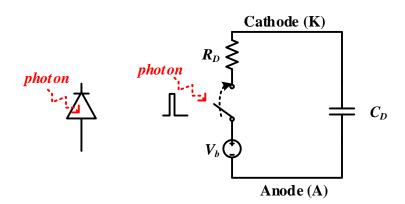

| Figure 2-1, Basic model of a SPAD                                                                                                                                                                                                                                              |

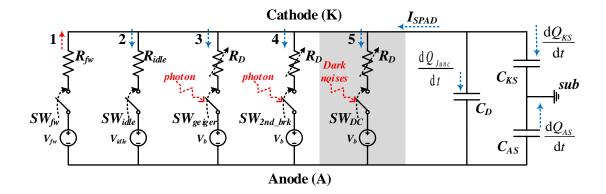

| Figure 2-2, Proposed analytical model of SPAD. The red and blue dashed arrows on each path indicate the current flowing through the SPAD. (Note: the path in shadow is specific for the dark noise due to thermal generation, band-to-band tunneling and after-pulsing noises) |

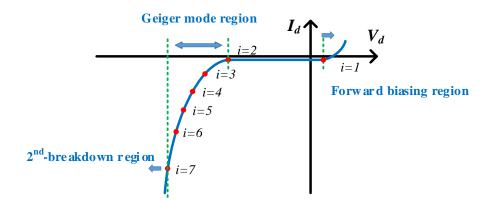

| Figure 2-3, Illustration example of the typical SPAD I-V curve                                                                                                                                                                                                                 |

| Figure 2-4, Verilog-A HDL code for the band-to-band tunneling process                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-5, (a) The inter-avalanche time interval measurement of a free-running SPAD,<br>and (b) Example of the statistical distribution obtained through the measurement<br>at ~30°C with 0.5V excess voltage. The distribution is fitted with four<br>exponentials |

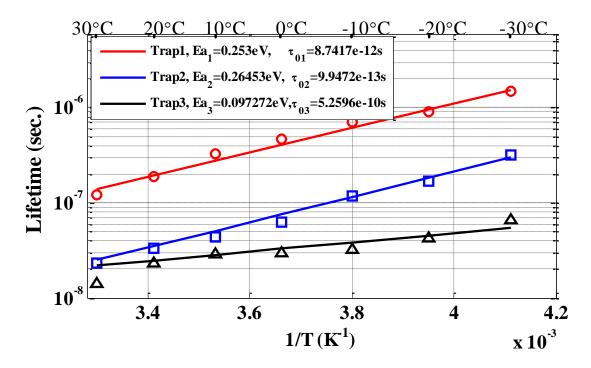

| Figure 2-6, Arrhenius plot of the trap lifetimes to extract their activation energies 38                                                                                                                                                                             |

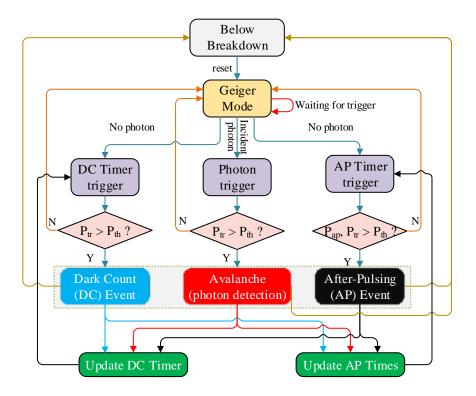

| Figure 2-7, State diagram of the proposed analytical model                                                                                                                                                                                                           |

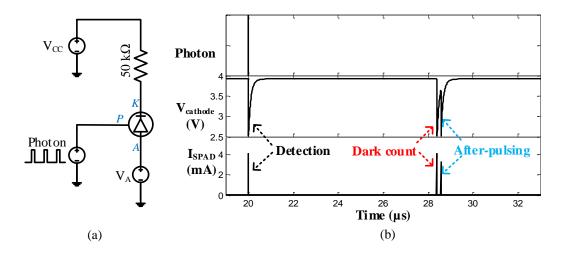

| Figure 2-8, (a) Simulation Setup of the SPAD model, and (b) Example of transient simulation that is executed with 1.5V excess voltage at 40°C. This example shows a detection, a dark count and an after-pulsing events                                              |

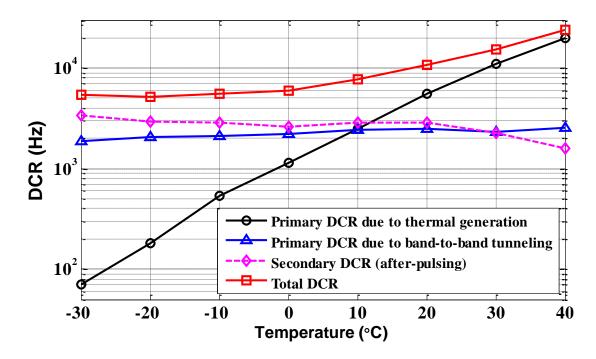

| Figure 2-9, Simulation results of the temperature dependences of both the primary and secondary dark counts ( $V_{ex}=0.5V$ )                                                                                                                                        |

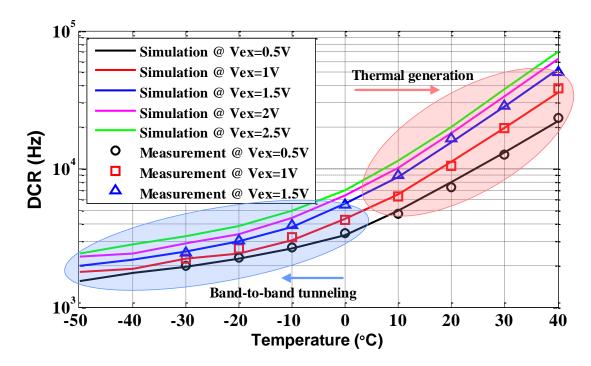

| Figure 2-10, Simulation results of the primary DCR with temperatures at five different excess voltages                                                                                                                                                               |

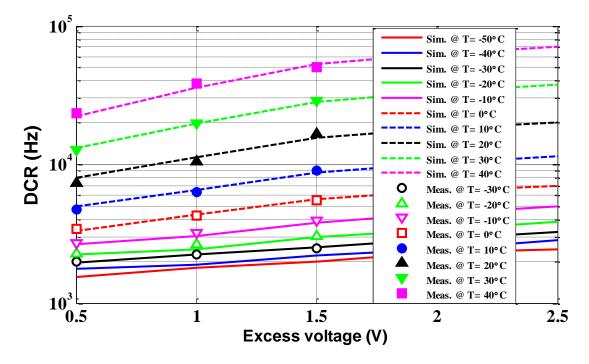

| Figure 2-11, Simulation results of the total primary DCR with excess voltages at ten different temperatures                                                                                                                                                          |

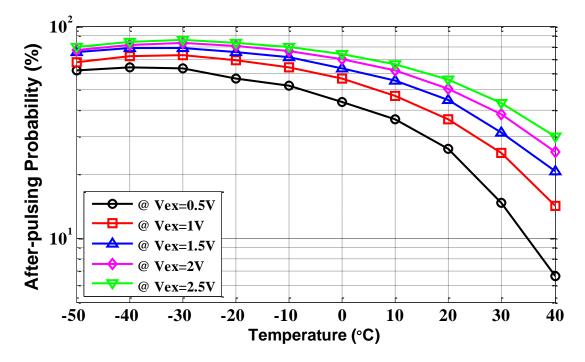

| Figure 2-12, Simulation results of the after-pulsing probability with temperatures at five different excess voltages                                                                                                                                                 |

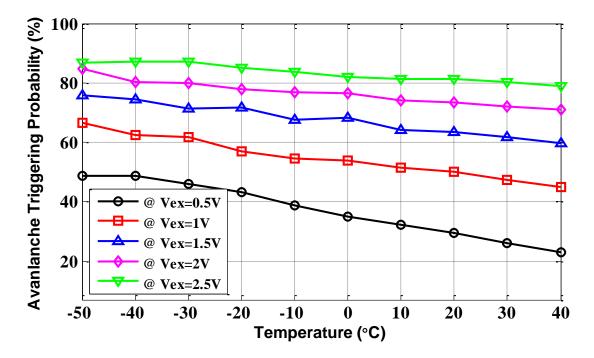

| Figure 2-13, Simulation results of triggering probability with temperatures at five different excess voltages                                                                                                                                                        |

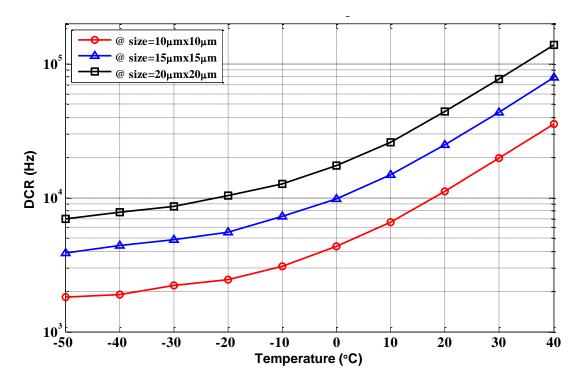

| Figure 2-14, Simulation results of DCR with different SPAD size. The excess voltage is fixed at 1V in this simulation                                                                                                                                                |

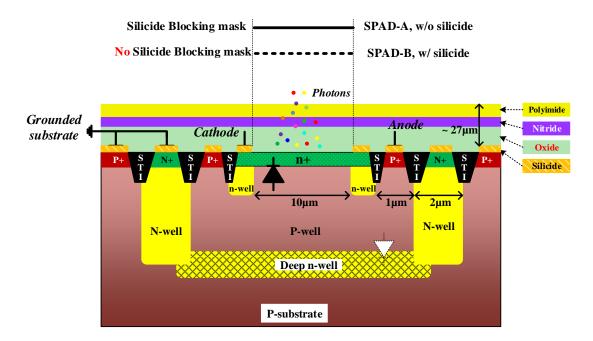

| Figure 3-1, Cross-sectional view of SPADs that are used in this chapter                                                                                                                                                                                              |

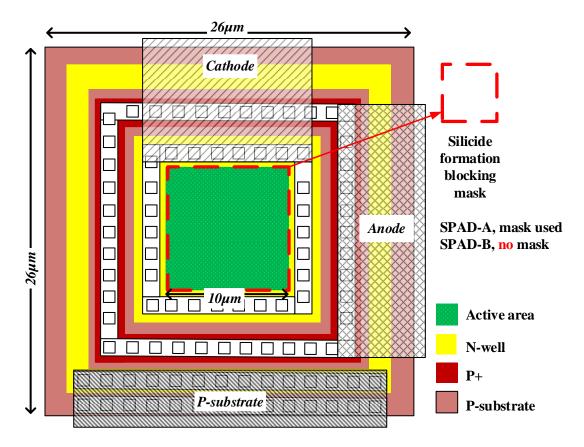

| Figure 3-2, Simplified layout view of SPADs that are used in this chapter 50                                                                                                                                                                                         |

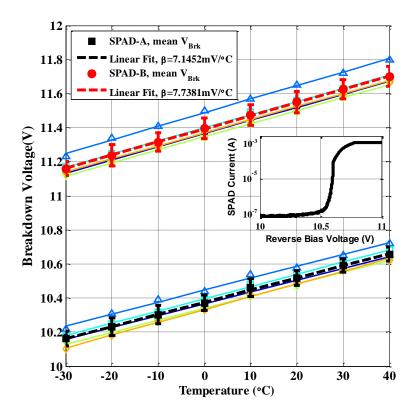

| Figure 3-3, Measured SPAD breakdown voltage as a function of temperature. The inset shows an example of the current versus the reverse bias voltage of a SPAD 52                                                                                                     |

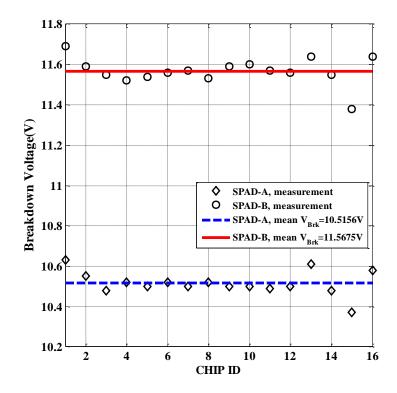

| Figure 3-4, Breakdown voltage of the SPAD chip-to-chip variation from 16 test ch | nips |

|----------------------------------------------------------------------------------|------|

| measured at room temperature (~24°C, ambient conditions)                         | . 53 |

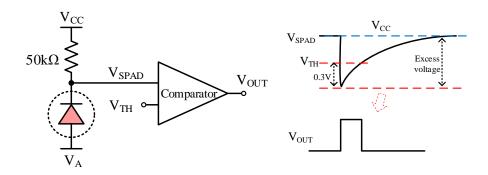

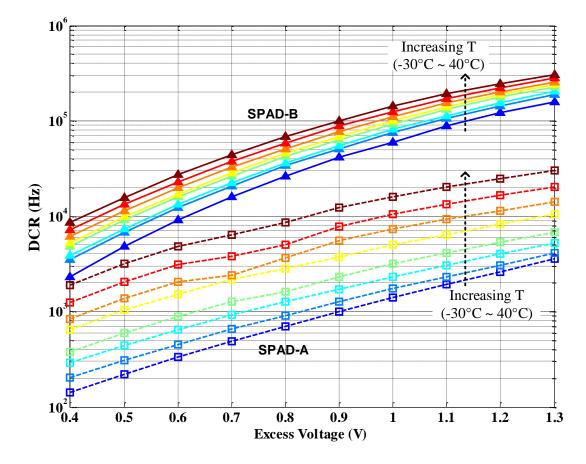

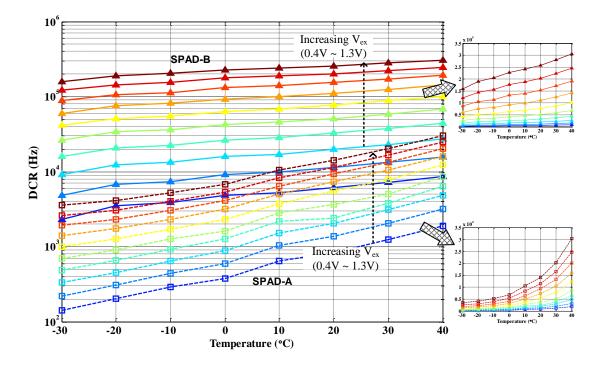

| Figure 3-5, Readout circuit for SPAD characterization                            | . 54 |

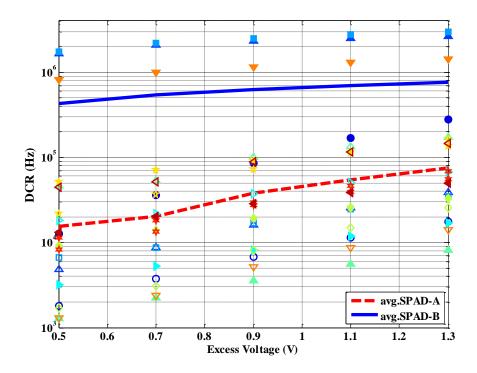

| Figure 3-6, Measured DCR with excess voltages. The temperature changes from -3   | 0°C  |

| to +40°C by 10°C per step                                                        | . 55 |

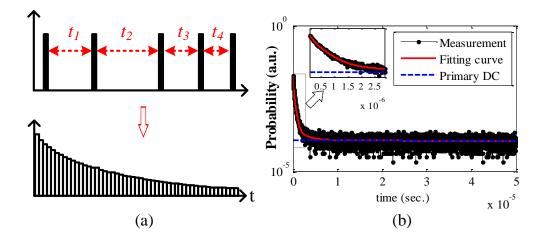

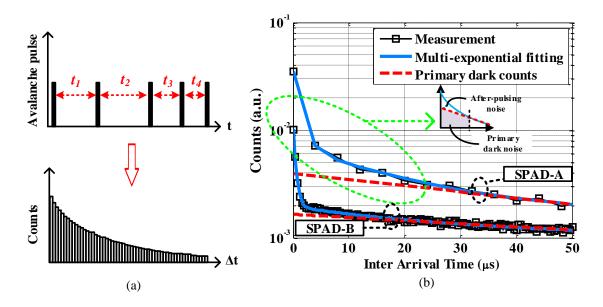

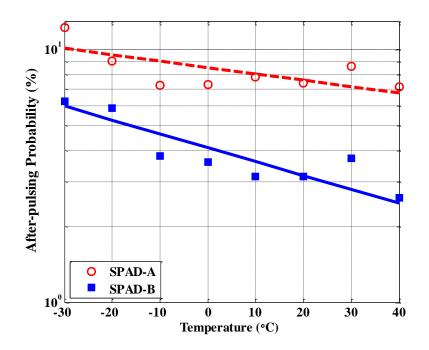

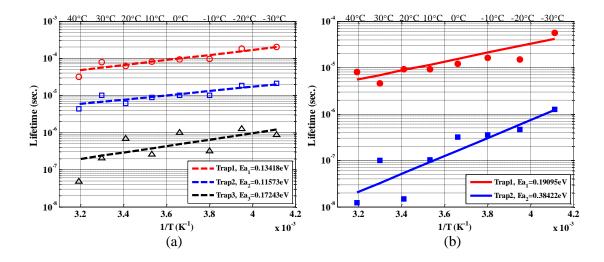

- Figure 3-9, (a) Illustration diagram of the inter-arrival-time (IAT) measurement. (b)

SPAD-A and SPAD-B IAT measurement and fitting examples at -20°C and 0.4V

excess voltage. The measurement data are fitting with four (SPAD-A)/three (SPAD-B) exponentials. For all the data fitting process, R<sup>2</sup> of 0.99 is achieved. The longest tail presents the primary dark noise. The insert shows that the after-pulsing probability is calculated as the area ratio between the dashed region and total area.

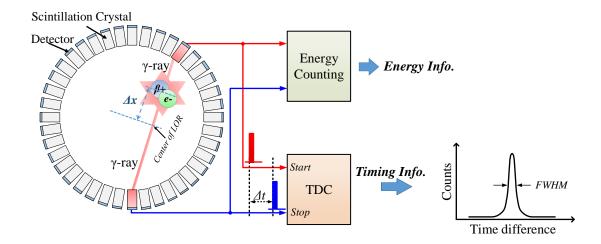

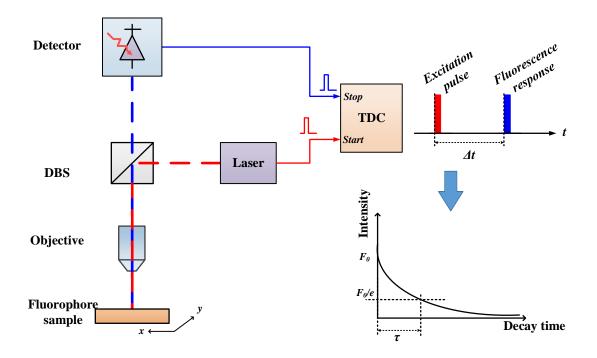

| Figure | 4-1,   | TDC     | utilization | in bio               | omedical       | imaging     | application        | s. (a)  | Conceptual    |

|--------|--------|---------|-------------|----------------------|----------------|-------------|--------------------|---------|---------------|

| di     | agram  | illustr | ating a TI  | DC coll              | ecting th      | e arrival t | ime differe        | nce in  | a ToF PET     |

| sy     | stem.  | Here,   | the timing  | informa              | ation mea      | asured by   | the TDC ( $\Delta$ | t) is u | sed to locate |

| th     | e anni | hilatio | n position  | $(\Delta x = \Delta$ | $t^*c/2)$ with | ith respec  | t to the cer       | ter of  | the line-of-  |

| re     | sponse | e       |             |                      |                |             |                    |         | 70            |

| Figure 4-2, Diagram of a FLIM measurement system. A TDC used in a time-correlated                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| single photon counting set up. The TDC is used to measure the fluorescence decay                                                                                                                                     |

| time with respect to the excitation pulse, which can be extracted from the                                                                                                                                           |

| histogram using exponential fitting71                                                                                                                                                                                |

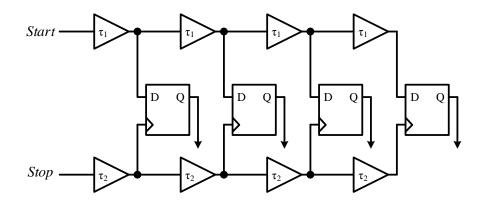

| Figure 4-3, Conceptual diagram of the Vernier-delay-line based TDC75                                                                                                                                                 |

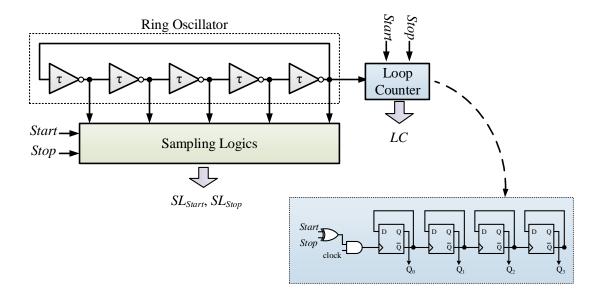

| Figure 4-4, Conceptual diagram of the ring-oscillator based TDC                                                                                                                                                      |

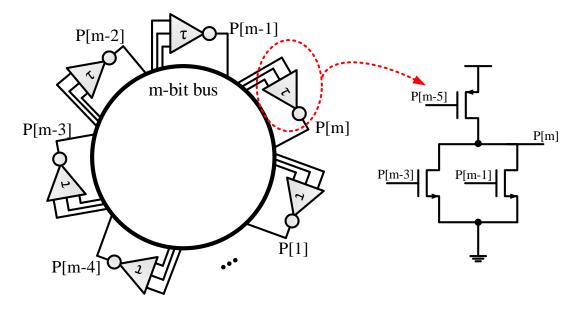

| Figure 4-5, Diagram of multi-path oscillator configuration                                                                                                                                                           |

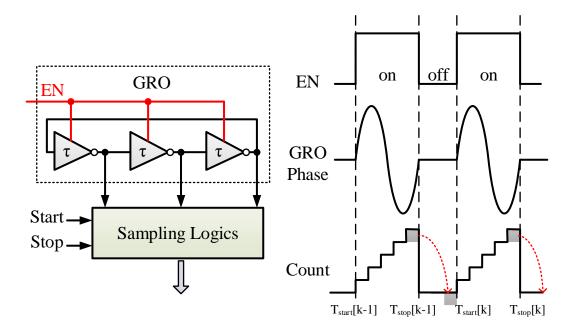

| Figure 4-6, Concept of gated ring oscillator based TDC and its timing waveforms 79                                                                                                                                   |

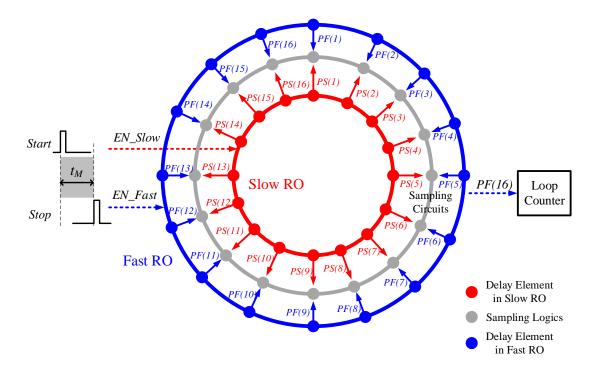

| Figure 4-7, Diagram of the operating principles of the proposed gateable Vernier ring oscillator TDC                                                                                                                 |

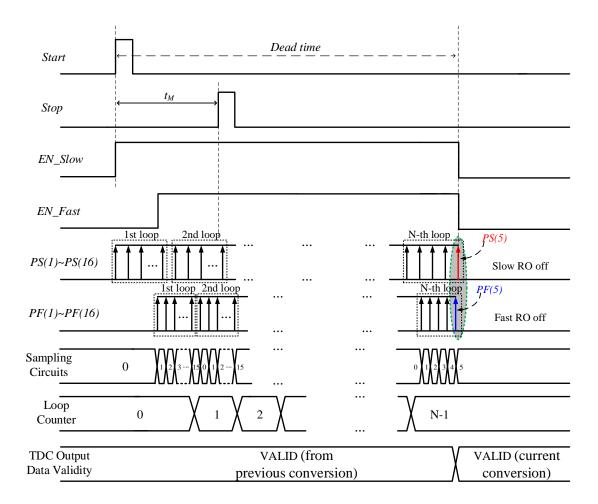

| Figure 4-8, Timing diagram of the proposed gateable Vernier ring oscillator TDC 82                                                                                                                                   |

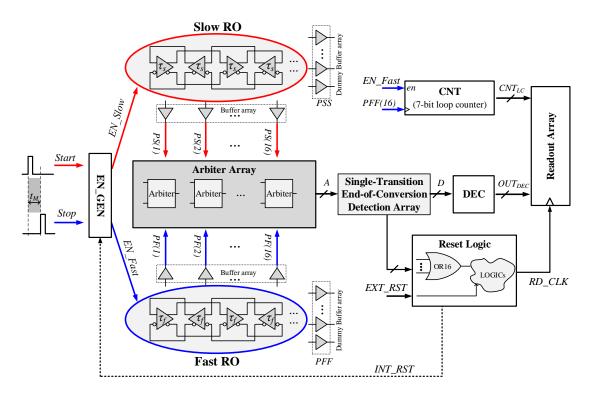

| Figure 4-9, Block diagram of the proposed gateable Vernier ring oscillator TDC 83                                                                                                                                    |

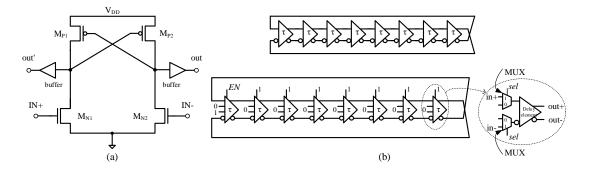

| Figure 4-10, (a) Transistor implementation of the differential delay element; (b)<br>Conventional ring oscillator (top) and gateable ring oscillators with regular<br>connections (bottom)                           |

| Figure 4-11, Twisted-manner arrangement of the RO                                                                                                                                                                    |

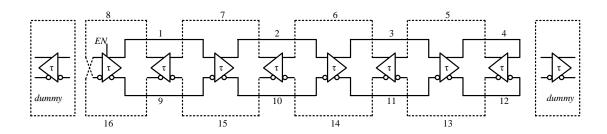

| Figure 4-12, (a) Post-layout extracted capacitive load uniformity of the ROs; and (b)<br>Layout of the RO and its surrounding circuits. Here the fast RO is given as an<br>example. The two ROs have similar layouts |

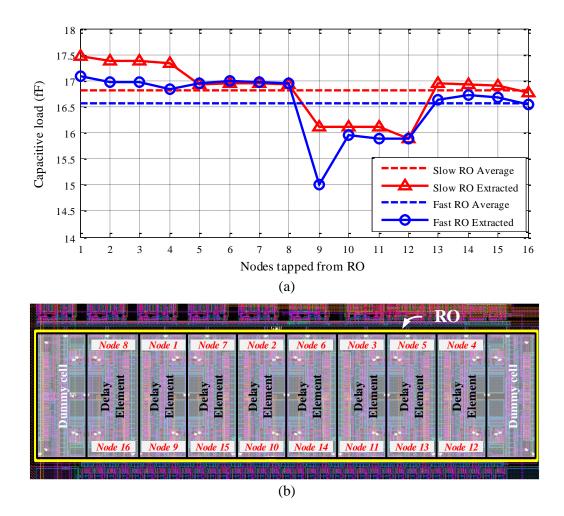

| Figure 4-13, Circuit of (a) The arbiter; and (b) The sampling circuit with its timing diagram                                                                                                                        |

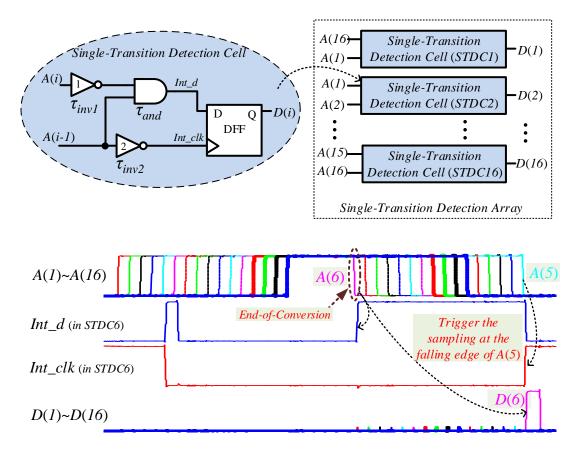

| Figure 4-15, Illustration of the timing diagram of the single-transition end-of-<br>conversion detection array. In the "Sampling Status" row, "N" means there is no<br>sampling and "Y" means there is a sampling operation in the detection array 89 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-16, Circuit and timing diagram of the enable generation block (EN_GEN) 90                                                                                                                                                                    |

| Figure 4-17, (a) Photomicrograph of the test chip (2mm×2mm). The proposed TDC                                                                                                                                                                         |

| occupies $230\mu$ m×150 $\mu$ m area. The major part of the test chip is test structures. (b)                                                                                                                                                         |

| Measurement set up                                                                                                                                                                                                                                    |

| Figure 4-18, Measured input-output characteristic of the TDC                                                                                                                                                                                          |

| Figure 4-19, DNL of the TDC                                                                                                                                                                                                                           |

| Figure 4-20, INL of the TDC before and after the LUT correction                                                                                                                                                                                       |

| Figure 4-21, Three examples of precision measurement histograms at different                                                                                                                                                                          |

| positions in the dynamic range94                                                                                                                                                                                                                      |

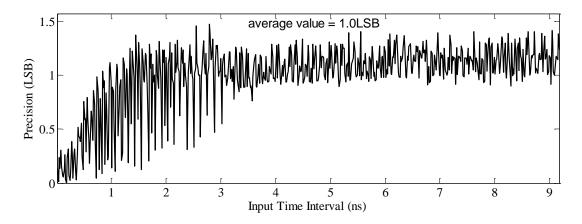

| Figure 4-22, Precision of the TDC over the entire dynamic range                                                                                                                                                                                       |

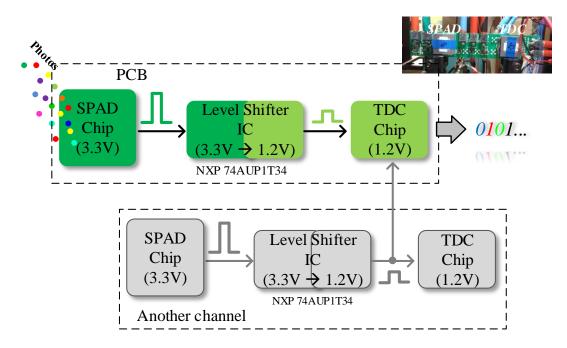

| Figure 5-1, PCB designed to integration the SPAD chip and TDC chip together 98                                                                                                                                                                        |

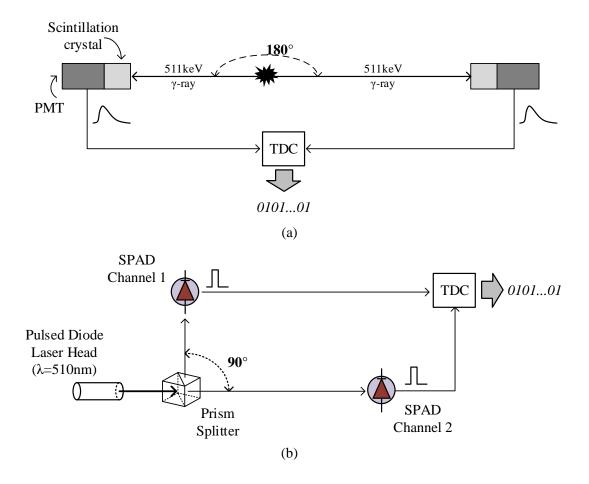

| Figure 5-2, Setup difference between (a) the coincidence detection system in real PET                                                                                                                                                                 |

| imaging application, and (b) the proposed sensing system in this thesis                                                                                                                                                                               |

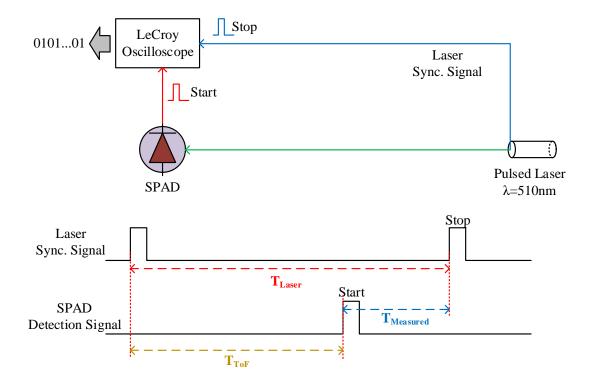

| Figure 5-3, Diagram of the setup used to measure the timing response spectrum of the                                                                                                                                                                  |

| SPAD                                                                                                                                                                                                                                                  |

| Figure 5-4, FWHM of the measured IRF of two SPAD channels with different laser                                                                                                                                                                        |

| powers and excess bias voltages                                                                                                                                                                                                                       |

| Figure 5-5, Time-of-flight measurement set up 103                                                                                                                                                                                                     |

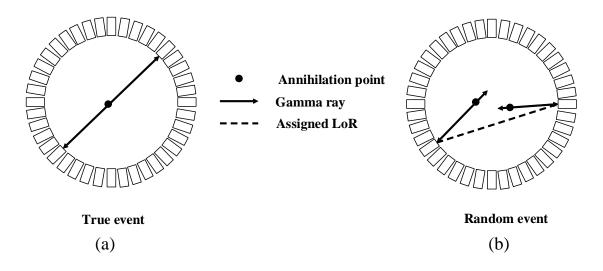

| Figure 5-6, Two different types of coincidence events in PET imaging: (a) True event                                                                                                                                                                  |

| and (b) Random event                                                                                                                                                                                                                                  |

| Figure 5-7, False coincidence issue in the time-of-flight measurement using our                                                                                                                                                                       |

| proposed sensing system 105                                                                                                                                                                                                                           |

## List of Tables

| Table 2-1, Parameters that are used in SPAD analytical model              | . 39 |

|---------------------------------------------------------------------------|------|

| Table 3-1, Performance summary and comparison of the SPADs                | . 66 |

| Table 4-1, Performance summary and comparison with the state-of-the-art T | DC   |

| designs                                                                   | . 95 |

# Chapter 1 INTRODUCTION<sup>\*</sup>

Optical, photonic, and optoelectronics components and systems are intensely studied and deployed in the field of biomedical imaging applications. Examples include Positron Emission Tomography (PET), Raman Spectroscopy, and Fluorescence Lifetime Imaging Microscopy (FLIM). This is mostly because of the non-invasive property of optical sensing and imaging techniques. In these applications, traditional photomultiplier tubes (PMTs) are used as the optical sensors due to their excellent performance in terms of excellent detection efficiency in the visible light range, fast response time and high single-to-noise ratio (SNR). However, they suffer from some important disadvantages such as bulky size, high operating voltage, low integration capability and high cost. Moreover, their performances will be greatly degraded under a high magnetic field. This limits their usage in some medical imaging applications, for example in magnetic resonance imaging (MRI). Thus, a study of optical sensing systems based on detectors not affected by magnetic fields, for example using Complementary Metal-Oxide-Semiconductor (CMOS) technology, is of great importance.

In this chapter, first, we introduce the application background of a PET imaging system. Then, a brief review of commonly used optical sensors and timing circuits will be provided. Next, the research motivation is highlighted, followed by the thesis organization and research contributions from this study.

<sup>\*</sup> Part of this work was published as: Z. Cheng, X. Zheng, M. J. Deen and H. Peng, "Recent developments and design challenges of high-performance ring oscillator CMOS time-to-digital converters," IEEE Transactions on Electron Devices, vol. 63, no. 1, pp 235-251, 2016. Copyright granted by IEEE.

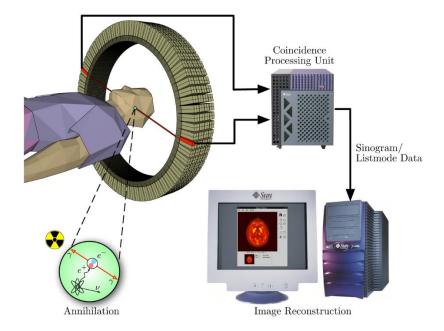

Figure 1-1, Schematic illustration of a PET imaging system. (Reprinted from [1], [2] with permission granted).

#### **1.1. Application Background**

#### 1.1.1. Positron Emission Tomography (PET) Imaging

PET is a non-invasive imaging modality in nuclear medicine. As its name suggests, it is based on the coincidence detection of two 511keV gamma-rays emitted from positron annihilation events from radioactive tracers injected into the patient's body. PET imaging is categorized as functional imaging because of the fact that the reconstructed images can present the patient's physiology.

The schematic illustration of a PET imaging system [1], [2] is presented in Figure 1-1. As the first step in PET scanning, the radioactive tracer is injected into the patient's body. The tracers used in PET are of particular interest since they can be used to form analogs of common biological molecules. For example, <sup>18</sup>F is used to produce <sup>18</sup>F-fluorodeoxyglucose (FDG) which is analogous to glucose and it can be used to indicate levels of cellular metabolism, and <sup>11</sup>C is used in <sup>11</sup>C-L-methionine as it is analogous to the amino acid, which can indicate cancer malignancy based on the amino acid utilization [3]. Since these isotopes feature short half-life times (e.g. <sup>18</sup>F is 110 minutes and <sup>11</sup>C is 20.4 minutes), positrons are generated in form of radioactive decay (i.e. the  $\beta$ + decay). After the positron is emitted it will travel a short distance through the

surrounding tissue before it combines with an electron from surrounding atoms. Then, the mass of these two particles is converted to electromagnetic energy in an annihilation event. Two gamma-rays are then generated in opposite directions with energy of 511keV [4], [5].

To detect these annihilation resulting gamma-rays, PET imaging systems make use of scintillation crystals to convert the high energy photons to low energy photons in visible wavelength range. Then, solid-state photon detectors, such as PMTs, are employed to translate the optical signals to electrical signals. Usually, the scintillation crystals and detectors are coupled together and placed in a ring formation around the patient, as shown in Figure 1-1. The electrical signals will be filtered in a coincidence process unit in order to select true events that are from the same annihilation. Then, the data is used to reconstruct the images for the region under scanning.

Since PET imaging has high sensitivity to the biological and metabolic activity differences at the molecular level, it has become one of the most powerful modalities in nuclear medicine for cancer detection and treatment. PET is currently being used in various fields, including: oncology for cancer diagnosis, staging, and therapy [6]; cardiology in myocardial perfusion and viability studies, and coronary artery disease [7]; and neurology in the study of epilepsy, movement disorders, and Alzheimer's disease [8]. While radiopharmaceutical research will provide new applications for PET, improving the optoelectronic system's capabilities can provide new imaging techniques to increase the effectiveness of PET in current applications and open the door to new ways to apply PET in healthcare.

#### 1.1.2. Time-of-Flight PET

The concept of time-of-flight (ToF) technique has been proposed and demonstrated in early 1980s [9], [10]. The ToF information is the time difference  $\Delta t$  in detection of the two 511keV gamma-rays events. ToF PET takes advantage of this timing information to correlate the detection events to the position  $\Delta x$  of the annihilation point with respect to the center of the field-of-view (FoV) according to the following equation.

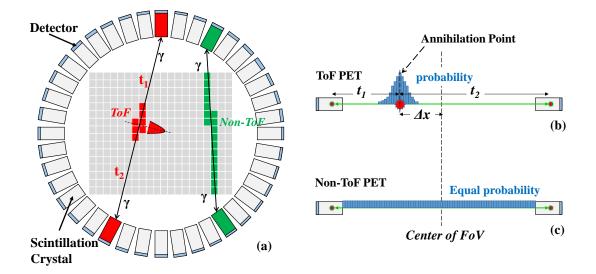

Figure 1-2, Concept diagram of ToF PET comparing with conventional PET.

$$t_1 = \frac{\frac{1}{2}D - \Delta x}{c}, t_2 = \frac{\frac{1}{2}D + \Delta x}{c} \Longrightarrow \Delta x = \frac{\Delta t \times c}{2}, \tag{1-1}$$

where *c* is the speed of light. It is noted that the factor of 2 in equation (1-1) is introduced since the  $\Delta x$  is the distance between the annihilation point and the center of the FoV.

The concept of ToF PET and its differences with the conventional PET are shown in Figure 1-2.

In conventional (non-ToF) PET, each detected photon is tagged with a detector position and a detection time. If the detection time difference between two photons is smaller than a set coincidence window (e.g. traditionally 5-10 ns), these two events are considered physically correlated to the same annihilation event. A line-of-response (LoR) between these two correlated detectors, as presented by the green part in Figure 1-2(a). Thus, in the non-ToF PET, the timing information is only used to filter the time coincidence events. When a LoR is determined, the point that the annihilation occurs can happen anywhere along this LoR. All the voxels along this LoR are assigned the same probability of emission to locate the annihilation position, as shown in Figure 1-2(a) and Figure 1-2(c). This will accumulate the noise contributions from all the voxels and degrade the SNR, which subsequently results in image blurring and degraded image contrast [11]–[14].

However, in the ToF PET, the ToF difference  $\Delta t$  is directly related to the distance  $\Delta x$  by Equation (1-1). In Figure 1-2(a), the time  $t_1$  is proportional to the distance between the annihilation point and the top detector, and the time  $t_2$  is proportional to the distance between the annihilation point and the bottom detector. Because of the advantageous ToF information, only a few voxels on the LoR will be considered for the emission source. Since the measured timing information ( $t_1$  and  $t_2$ ) have jitters, the coincidence timing resolution is limited. This causes a distribution spread in the location probability as shown in Figure 1-2(b), with its most possible position  $\Delta x$  corresponding the measured ToF value.

Even though the ToF concept could not improve the spatial resolution in a PET imaging system [13], it helps reducing the statistical noise in the reconstructed image and enhance the image contrast. The following equation gives the benefit in terms of the gain in SNR,

$$\frac{SNR_{ToF}}{SNR_{Non-ToF}} = \sqrt{\frac{D}{\Delta x}} = \sqrt{\frac{2D}{c \times \Delta t}},$$

(1-2)

where  $SNR_{ToF}$  and  $SNR_{Non-ToF}$  are the SNRs of the reconstructed images from ToF PET imaging and conventional PET imaging, respectively, and *D* is the diameter of the object under scanning [11], [14]–[16].

Another term to represent the advance available from ToF PET is the effective sensitivity increase (G), as presented in the following equation [11], [13],

$$G = \frac{2D}{c \times \Delta t},\tag{1-3}$$

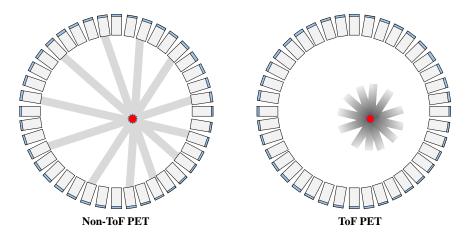

With coincidence timing resolution as fine as hundreds of picoseconds, considerable SNR gain and effective sensitivity increase in the reconstructed images are achievable from ToF PET system. An illustration of the difference between these two PET systems is given in Figure 1-3. This implies better lesion detectability, reduced radioactive dose needed by the patient and/or reduced scan time [12].

Figure 1-3, Illustration of the SNR increase of a ToF PET system over a conventional PET system.

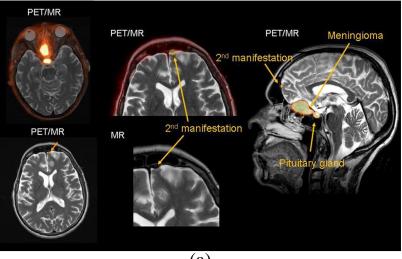

#### 1.1.3. Combined Imaging Modality: PET/MRI

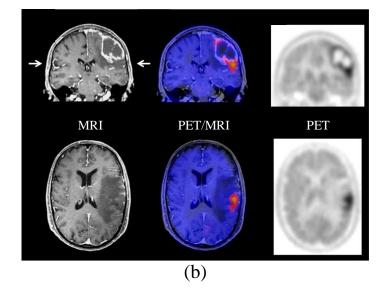

Despite the advantages from the standalone PET scanning, it suffers from image blurring due to patient movement. And the low contrast in PET images increase the difficulty to locate the lesion region precisely. As an important technical evolution in the field of nuclear imaging, PET/MRI multimodality imaging can add anatomic features with high soft-tissue contrast available from MRI to the biological information delivered by PET imaging [17], [18]. Two examples of the images from PET/MRI are given in Figure 1-4 below [18], [19].

Figure 1-4(a) shows the clinical PET/MR images of a 71-year-old woman with frontobasal meningioma in the olfactory region [18]. In addition to the detection of the main tumor, the secondary smaller and previously unknown frontal meningioma was seen on PET scanning. It is not detected by computed tomography (CT) and hardly by MRI. In Figure 1-4(b) [19], the MRI images showed the contrast-enhancing lesion and surrounding edema. PET images showed the tumor's location with better accuracy according to the increase of the isotope intensity. MRI images can help to improve the soft tissue contrast in PET images.

The combination of PET and MRI requires a solution to several technological challenges in terms of the photodetector. First, the photomultipliers used in PET scanner must be replaced by magnetic-field insensitive photon sensors. The strength of magnetic field in the magnet bore in a MRI system is typically between 0.5T and 10T, with 3T for most human MRI scanners. The performance of conventional PMTs used on PET system will be greatly deteriorated under such a high magnetic field strength

(a)

Figure 1-4, Two examples of the fusion images obtained from the combined PET/MRI imaging. (Reproduced from [18], [19] with permission granted. Copyright by the Society of Nuclear Medicine and Molecular Imaging Inc.)

due to their intrinsic analog properties. Second, the size of PET detectors needs to be compact. The detector ring for PET scanner has to be invisible to the MRI and must not interfere with the field gradients or the MR radio frequency [17], [18]. Thus, these requirements motivate the research and development in new types of photodetectors.

#### 1.2. Brief Review on Existing Technologies

We divide the review of existing technologies into two categories. One is for optical detectors including PMTs and other types of silicon-based solid-state detectors. The

Figure 1-5, Schematic diagram of a typical PMT with a scintillation crystal. (Reprinted from [20] with permission granted.)

other is the timing circuitry, i.e. the time digitizer used to extract the ToF timing information.

#### **1.2.1. Photodetector Technologies**

The photodetector that is most commonly used in PET imaging systems is the PMT. PMTs are commonly coupled with scintillators to form the scintillation detectors due to their large area, fast response time, high sensitivity, high gain and low noise. As other types of solid-state photodetectors, the silicon-based photodiodes have attracted intensive research interests over the past decades [5].

#### (a) PMT

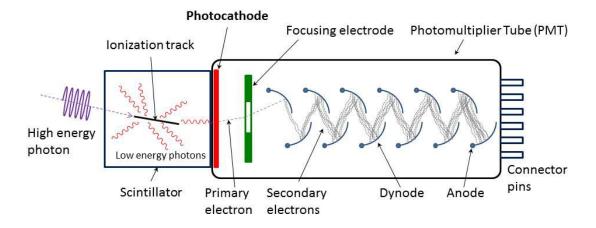

Figure 1-5 presents the typical schematic diagram of a PMT [20], which is coupled with a scintillator to convert the high energy gamma-ray in PET imaging system to low energy visible photons. Basically, a PMT is composed of a photocathode, a series of multiplication stage (i.e. a series of electrodes called *dynodes*) and an anode. All these components are enclosed in a vacuum environment by borosilicate glass.

When scintillation photons strike the photocathode, photoelectrons (i.e. primary electrons in Figure 1-5) will be released by the photoelectric effect given that the incident photon energy is much higher than the work function of the photocathode's material. An important term called quantum efficiency is used to describe the probability of liberating photoelectrons in the PMT's photocathode. It is usually measured as a ratio of the number of generated photoelectrons relative to the number

of incident photons. The PMT's quantum efficiency is wavelength dependent and has a typical value of 20~30% [5].

The photoelectrons are then focused by the focusing electrode and accelerated towards the first dynode. The dynode plates are specifically shaped and arranged in a PMT to maximize the collection of electrons. Since each dynode is held at a higher voltage potential than the previous one, electrons will be accelerated under the electric field. Every time the electrons trike dynodes at high velocities, the plate will emit secondary electrons and they will accelerate towards the next plate. This process is repeated for 10 to 12 times depending on the number of dynodes in a PMT. Usually, a PMT delivers an amplification gain of  $10^6$  [5].

Besides the high gain, PMTs have other attractive properties such as stability, low dark current, linear amplification and low noise. These features make PMT the most used photodetector in a PET imaging system. Recently, several advanced modes of PMTs were developed and are now commercially available. For example, the micro PMT from Hamamatsu features very compact size of 40mm×30mm×12mm, around 5V input voltage and light weight of ~50g [21].

#### (b) Avalanche Photodiode (APD)

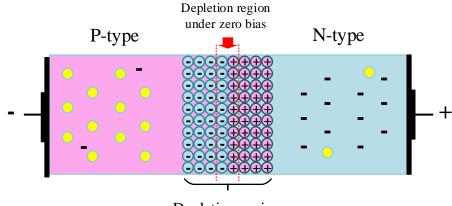

The avalanche photodiode (APD) is essentially a PN junction which works under the reverse-biased condition, as shown in Figure 1-6. A depletion region exists due to the drift of electrons and holes. And it becomes wider in the reverse bias than that in zero bias. When incident photos are absorbed, electron-hole pairs will be generated in the depletion region. These photon generated electron-hole pairs can migrate towards electrodes under the external applied electric field, thus contributing to the so-called photocurrent.

Because the depletion region in APD is very thin, this makes APD response very fast to incident photons, thus, APD can provide better timing performance than PMT. The quantum efficiency of APD is much higher than PMT ( $60\% \sim 80\%$ ) as photoelectrons are not required to escape from the photocathode (which is the case in PMT to overcome the work function of the photocathode material). Besides, silicon-based APDs are easy to miniaturize and can be fabricated in standard semiconductor

Depletion region

Figure 1-6, Depletion region of an APD device.

technologies. It is more robust, less expensive, and requires lower operating voltage when compared with PMT.

However, the internal gain available from APD is usually on the order of  $10^3$ . This is much lower than that of PMT (~ $10^6$ ) and is not sufficient to make it working as a single photon detector in a PET system. Therefore, low noise amplifiers are usually required for APDs [5], [22].

#### (c) Single Photon Avalanche Diode (SPAD)

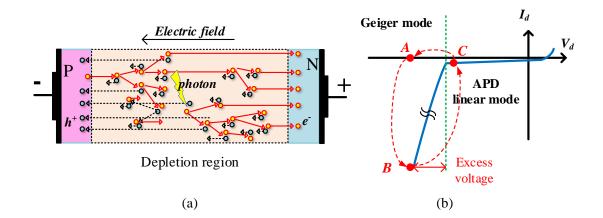

Single photon avalanche diode (SPAD) is an APD being biased in the Geiger mode [5], [22], [23]. This mode refers to the condition that the photodiode is biased above its breakdown voltage.

In Geiger mode, the electric field in the depletion region of the SPAD is sufficiently high that both electrons and holes generated in this region can be multiplied by impact ionization process. As depicted in Figure 1-7(a), first, photon-generated electron-hole pair will be accelerated by the electric field, and then impact ionize to generate more electron-hole pairs. These secondary electron-hole pairs will further ionize more atoms. This multiplication process repeats in the depletion region before the free carriers are collected by electrodes. Thus, a self-sustained avalanche process is resulted in an SPAD.

Figure 1-7(b) shows the typical current/voltage characteristics of a SPAD device. The dashed line presents the breakdown point which also divide the reverse biasing into Geiger mode and APD linear mode. At the beginning, the SPAD is biased beyond

Figure 1-7, Principle operation of SPAD. (a) The avalanche breakdown process and (b) The typical current/voltage curve.

the breakdown voltage and stays in OFF state (A). When a photon strikes its active (depletion) region and introduces initial carriers, avalanche multiplication process will be started. The SPAD is in ON state (B). Other than triggered photons, avalanche could happen due to other sources (as will be discussed in Chapter 2 and Chapter 3), and these are considered as dark noise. Consequently, a macroscopically avalanche current is built up flowing through the device. Usually, the avalanche current follows though a resistor to provide negative feedback. Thus, a large voltage drop across the resistor will bring the SPAD to the point C, where the avalanche cannot be self-sustained. Now, the SPAD is quenched, and it will be recharged back to the point A through the same quenching resistor that is connected to the supply voltage.

Due to the internal avalanche multiplication process in the device, SPAD provides a large gain ( $\sim 10^6$ ) that is comparable with PMTs. It features many attractive properties as a solid-state silicon-based photodetector, such as single photon sensitivity, fast response time, low dead time with different quenching/recharging circuits, low operating voltage, compact size and fully compatible with standard CMOS process. Especially, it can easily scale-up to large SPAD arrays and be integrated with peripheral electronics [24]. As a state-of-the-art example, the work in [25] implemented an 96×240 SPAD array, and integrated timing measurement and real-time energy counting circuits on chip. Being fabricated in a 130nm imaging CMOS process, the design only required 3.3V supply voltage, consumes 300mW power, and worked at 100Msps.

SPAD has several important performance metrics [24], [26]. Below we list several factors that reveal the optical property of a SPAD:

- As mentioned above, the SPAD can be triggered by sources besides light illumination and these false triggering brings dark noises to the SPAD. These sources will be discussed in detail in the following two chapters. Dark count rate (DCR) refers to the avalanche counts per second when a SPAD is falsely triggered by means other than photons. It is a parameter that presents the noise level of a SPAD. Typically, it is greatly affected by the SPAD fabrication technology. It can vary from <100Hz to several MHz. DCR is also highly dependent on both excess bias voltage and temperature.

- Since some associated circuits (e.g. quenching and recharging resistors and transistors) are integrated with the SPAD and due to design rule requirement, only a portion of the surface area of a SPAD can be used to collect photons. Fill-factor (FF) is the ratio of the active area of a SPAD to the total pixel area. A SPAD design with large FF means that more silicon area are dedicated to photon sensing.

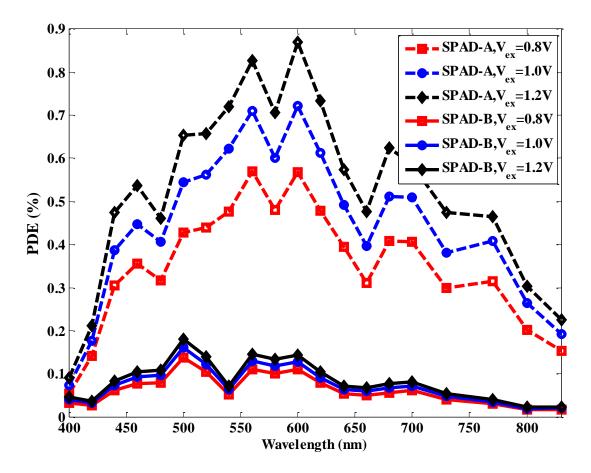

- Photon detection efficiency (PDE) is a measure of the ratio of the number of detected photons to the number of incident photons on the active area of the SPAD. This ratio depends on absorption probability and the triggering efficiency [24]. PDE changes with both excess voltage and wavelength.

- The SPAD timing jitter (or timing precision) is the statistical spread of output pulse of SPAD relative to the actual photon arrival time. This parameter is usually represented as the full-width at half-maximum (FWHM) of the distribution histogram of SPAD response time. CMOS SPAD features good timing performance and timing jitter can be less than 100ps [27].

The past decade has witnessed the development of SPADs with higher detection efficiency, lower dark count level, higher detection rate, and higher fill factor. They can be designed and fabricated in various CMOS processes, from the high performance but high cost custom process [28], [29], to inexpensive mainstream digital CMOS process [30]–[33]. A comprehensive review of SPADs developed in CMOS technology can be found in these references [24], [26].

#### (d) Silicon Photomultiplier (SiPM)

Even though PMT is still the mainstream photodetector used PET imaging system, its drawbacks make researchers start to investigate new types of semiconductor photodetectors. Among all the candidates mentioned earlier, silicon photomultiplier (SiPM) is a novel version of single-photon level photodetector in the photodiode family.

SiPM comprises a high-density matrix of SPADs that are connected in parallel. For example, the C-series SiPM that is commercially available from SensL has an array size varying from  $14.2 \times 14.2 \text{ mm}^2$  to  $57.4 \times 57.4 \text{ mm}^2$ , containing a large number of SPAD microcells from 75920 ( for  $2 \times 2$  pixels) to 687456 (for  $12 \times 12$  pixels) [34]. The output signal of the SiPM thus is proportional to the number of operating SPAD microcells (or summation of outputs from each pixel). SiPM has the high gain characteristic inherited from SPAD microcells (~ $10^6$ ). Thus, it eliminates the needs for external amplification circuits as required with APDs.

The PDE of a SiPM is typically dependent on the quantum efficiency, pixel fillfactor, SPAD microcell's triggering/breakdown probability and its recovery time [12]. The quantum efficiency of silicon is quite high for visible light photons (80-90%) and it heavily depends on wavelength [35]. UV range photons do not penetrate very deep into the material and electron-hole pairs are often lost due to short recombination time of surface defects. Longer wavelength IR photons penetrate deeper into silicon and require deeper depletion layers. The effective photon sensitive area on SiPM can be anywhere from 25% to 80% depending on the implementation of the detector. The breakdown probability is simply the probability that the initial electron-hole pair causes breakdown. This is related to the electric field strength in the SPAD, but can often approach 100% due to its very thin depletion region. The recovery time is the recharging period for a microcell. After firing, it typically takes the microcell about 1 $\mu$ s to recharge its capacitance. The product of these factors gives a PDE in the range of 14% to 51% [36], [37] for SiPM in recent commercial devices.

Due to the arrangement of the SiPM array, optical crosstalk may occur. For every  $10^5$  carriers produced above the band gap of silicon, approximately 3 photons are emitted [35]. These photons may go on to cause avalanche breakdown in neighboring microcells, adding to the overall noise via a stochastic process. This effect can be

reduced by using lower gain, or introducing a physical barrier between microcells, but the cost is reduced gain and/or smaller sensitive area. This crosstalk, combined with the dark counts of individual microcells are the major sources of noise in SiPMs. Due to their much higher gain, however, SiPMs still have an SNR advantage over large area APD detectors.

It should be noted that a SiPM has a relatively higher DCR compared with a PMT. This is because of the thermally generated free carriers in the conduction band and the large number of microcells integrated in one device. Another important feature of SiPM is that it is immune to magnetic fields, which makes it an attractive choice for PET/MRI multimodality imaging as discussed before. All these features of SiPM have led to growing attention to use SiPM as an alternative to the traditional PMTs in low-light detection applications such as PET and FLIM imaging [12], [17], [38]–[40].

An important innovation in the development of SiPM, the digital SiPM (dSiPM), has become a hot research topic in the past few years [25], [30], [31], [41]–[54]. In dSiPM, one-bit analog-to-digital converters (ADCs) are integrated in each SPAD microcell to convert the avalanche pulses to digital signals immediately after the SPADs. The dSiPM allows direct access to each microcell in its pixel, thus the noisy cells (i.e. those cells that show considerably high DCRs) can be disabled. This feature can greatly reduce the median noise performance of the dSiPM. On-chip time-to-digital converters (TDCs) are also implemented to explore the timing information during the photon detection. Currently, dSiPM is commercially available from Philips [53], [55].

#### **1.2.2. TDC Technologies**

TDCs have been intensely used in the past decade due to their excellent timing resolutions and time stamping capabilities. These capabilities are important for various applications such as All-Digital Phase-Locked Loop (ADPLL) [56]–[58], and biomedical imaging including ToF PET [25], [43], [59], FLIM [49], [60] and various ToF ranging applications [61]–[63]. With the digitization function which is analogous to an ADC, a TDC converts time intervals to digital codes with sub-nanoseconds or even sub-picoseconds resolution when implemented in a 90nm CMOS technology [64]. In order to facilitate system integration and reduce cost, on-chip TDC in standard CMOS technology is the preferred choice [65].

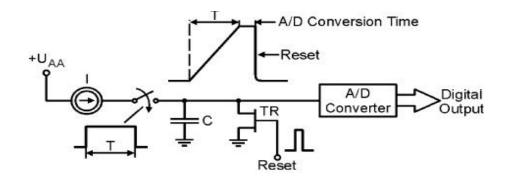

Figure 1-8, Conceptual illustration of an analog-type TDC. (Reprinted from [75] with permission granted.)

TDCs can be divided into two categories according to their operating principles. The analog-type TDCs use time-to-amplitude conversion followed by an ADC. These TDCs achieve good resolution and linearity at the expense of high power dissipation, large size, low scalability with CMOS technology nodes and high noise susceptibility. TDCs based on digital techniques can be further classified as delay-locked-line (DLL) [66], [67], Vernier-delay-line (VDL) [68], and multiple interpolations [69]–[71].

Another variation of the digital types is the ring-oscillator (RO) based TDC [16]. This type of RO-based TDCs is very suitable for array implementation because the ring oscillator used to generate the required multiple-phases for the whole array can be shared on-chip [45], [60], [72], [73]. Also, RO-based TDCs can simultaneously achieve high resolution and wide dynamic range, with small area and low power dissipation. A comprehensive discussion on RO-based TDCs can be found in [15].

Next, a brief discussion and comparison of conventional analog-type TDCs and digital TDCs implemented in both CMOS and field programmable gate array (FPGA) technologies is given. A more detailed review of these TDCs can be found in [74]–[76].

#### (a) Analog-type TDCs

Generally, in an analog-type TDC, a capacitor is discharged by a constant current source during the time interval to be measured. This will produce a voltage change across the capacitor, which is linearly dependent on the discharging time. Then, the voltage change will be converted to digital codes by either a voltage comparator or a conventional ADC. This concept is presented in Figure 1-8 [75].

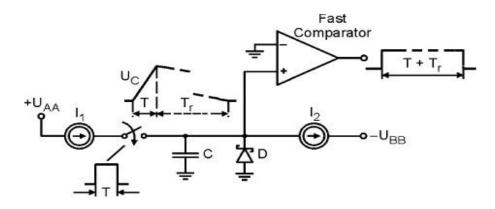

In order to get better resolution, the pulse stretching (or time stretching) method is often employed in analog-type TDCs. Figure 1-9 shows the conceptual diagram of such

Figure 1-9, Conceptual illustration of a time stretching TDC. (Reprinted from [75] with permission granted.)

an example [75]. In such a method, the capacitor *C* is discharged by a current source  $I_1$ . Then, the capacitor is recharged back to the same voltage by another current source  $I_2$ , which is *K* times smaller than  $I_1$ . Thus, a stretching/amplification factor *K* is obtained, and the time resolution can be improved by the same factor [77]–[80]. For example, in [78], using discrete logic circuits, a pulse-stretching factor of about 5000 and a time resolution of 7.8ps were achieved.

To further improve the stretching factor and time resolution of the TDC, the dualslope pulse stretching approach can be used [81], [82]. In this method, a second capacitor is used to take advantage of both the current ratio and the capacitance ratio. First, the node (with an initial voltage of  $V_0$ ) is discharged by the capacitor  $C_1$  with the current source  $I_1$ , during the time interval to be measured. Then, a larger capacitor  $C_2$ (= $MC_1$ ) starts to recharge the node by a smaller current source  $I_2$  (= $I_1/N$ ), until the voltage of the node returns to its initial value. A counter driven by a reference clock records the number of clock cycles during this charging period. In this way, the interpolation factor (= MN) can be very large, yielding an enhanced time resolution of the TDC.

Examples of the dual-slope TDC are now discussed. The TDC implemented in a  $0.8\mu$ m BiCMOS process in [81] achieved 32ps resolution, and 2.5µs dynamic range with a 100MHz reference clock. However, it had the drawback of a large power consumption (350mW) and large temperature drift (±125%, i.e. ±40ps in a 100°C range). Another implementation in [82] achieved 50ps resolution, 250ns dynamic range, and 0.75mW power consumption with a 80MHz reference clock in 0.35µm CMOS

process. Here, the temperature drift was from -15.2% to +13% over a temperature range of -40°C to 80°C. A state-of-the-art analog-type TDC in [83] proposed a triple-slope time stretching scheme and implemented it in a 0.35  $\mu$ m CMOS technology. This TDC had 357ps resolution and 1.46 $\mu$ s dynamic range with a 175MHz reference clock. However, the temperature drift performance was not reported.

Through careful design and layout, the analog-type TDC can have excellent precision and linearity for short measurement ranges. But it suffers from a large temperature drift, hence, a low stability, and a degraded INL for wide dynamic range implementations. Moreover, since the analog-type TDC uses large area consuming capacitors, it is very costly in terms of area, especially for integrated implementations. Also, the dead time of the analog-type TDC will limit its high-speed applications. In addition, the analog nature makes it hard to migrate to advanced CMOS technologies [80]–[83].

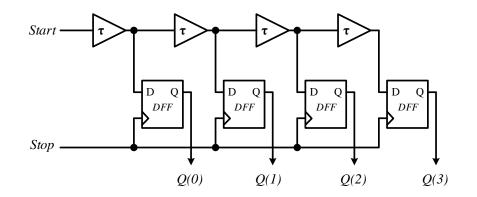

#### (b) Digital CMOS TDCs

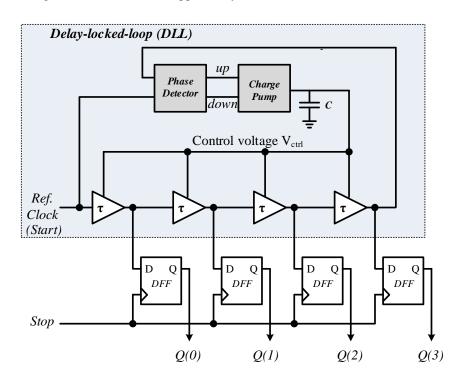

A widely used type of digital TDC is based on the delay lines consisting of several stages of buffers or inverters. As shown in Figure 1-10, the *Start* pulse propagates through the delay line, and its statuses along the delay line will be recorded by flip-flops being triggered upon the arrival of the *Stop* pulse. Then, the time interval between *Start* and *Stop* signals is obtained by decoding the statuses in the flip-flops [84], [85]. This basic tapped delay line architecture offers a relatively straightforward approach to perform the time-to-digital conversion. However, its resolution is typically limited by the propagation delay of an inverter, which is the shortest delay specified in a certain CMOS technology. Also, the delay of a delay unit is subject to process, voltage and temperature (PVT) variations, unless the DLL technique is used [86]–[88]. Using a DLL as in Figure 1-11, the delay of the delay unit is voltage-controllable and is locked to a fraction of a reference clock's period, regardless of ambient or process variations. A phase detector, charge pump and loop filter are used to detect the frequency/phase difference and provide a negative feedback.

The VDL, in which two chains of different delay units are used, is a solution to achieve sub-gate delay in a standard CMOS technology. For example, 5ps resolution was demonstrated with a VDL TDC in a 0.7µm CMOS process [68]. By introducing

Figure 1-10, Diagram of a conventional tapped delay line.

Figure 1-11, Diagram of a DLL TDC.

additional levels of interpolations using both VDL and tapped DLL, the resolution was improved to 1ps with a hierarchical VDL topology implemented in a 90nm CMOS process [89]. VDL-based TDCs can get superior (sub-gate) time resolution, but their dynamic range are usually limited by the total number of delay units, which would increase exponentially in order to cover a large dynamic range. To solve this problem, 2-D VDL-based TDC was proposed [90]. By arranging the delay lines in two orthogonal dimensions, the total length in this 2-D VDL was reduced. This yielded a better efficiency since only a third of the delay lines was required to cover the same

dynamic range as compared to the traditional linear VDL.

Another way to achieve fine time resolution and cover a wide dynamic range is to use the multiple interpolation method. For example, a two-stage coarse-fine TDC could amplify the residue after the coarse conversion and subsequently perform the fine conversion. Implemented in a 90nm CMOS process, the coarse-fine TDC in [58] had 1.25ps resolution, 9 bits range, occupied  $0.6 \text{mm}^2$  area and consumed 3mW power. Because the time residue amplification was used, this TDC suffered from gain uncertainty due to PVT variations. Similar to the cyclic ADC, a 8-bit cyclic time-to-digital conversion was achieved by repetitively using a 1.5-bit time-domain DAC [91]. When implemented in a  $0.13 \mu \text{m}$  CMOS process, this TDC had a resolution of 1.25ps, and a measurement range of 320ps. It occupied  $0.07 \text{mm}^2$  and the power consumption was 4.3mW.

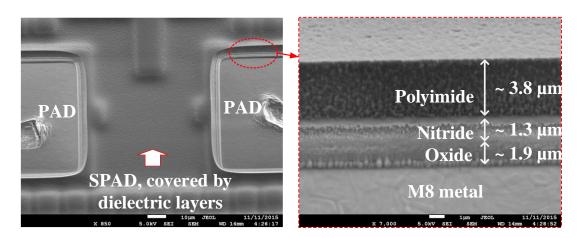

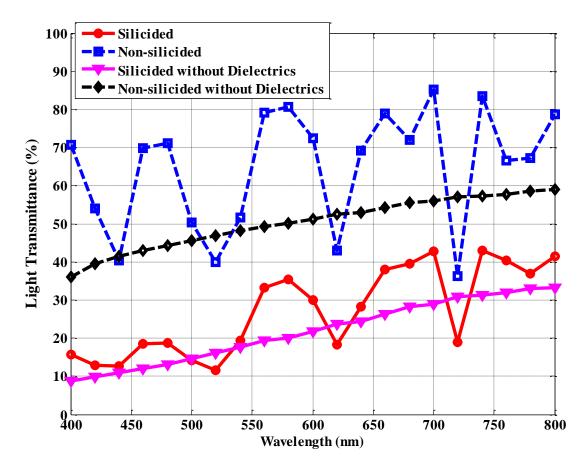

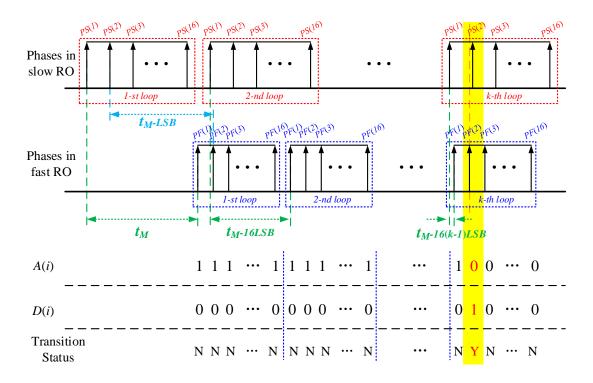

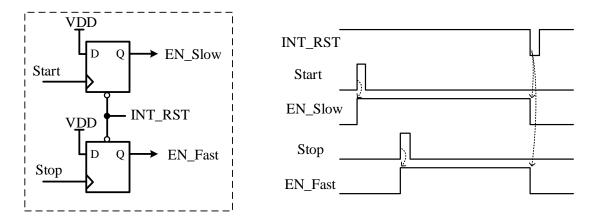

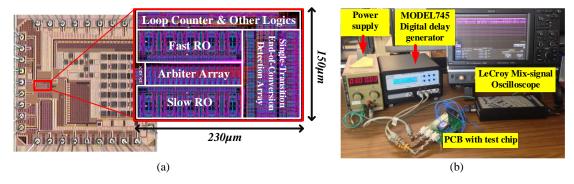

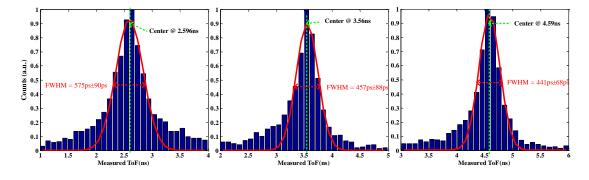

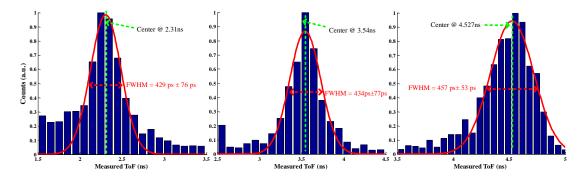

#### (c) **FPGA-based TDCs**