## Proving Implementability of Timing Properties with Tolerances

.

## PROVING IMPLEMENTABILITY OF TIMING PROPERTIES WITH TOLERANCES

By

XIAYONG HU, B.Eng., M.Sc.

A Thesis Submitted to the School of Graduate Studies in Partial Fulfilment of the Requirements for the Degree of Doctor of Philosophy

McMaster University © Copyright by Xiayong Hu, August 2008 DOCTOR OF PHILOSOPHY (2008) (Software Engineering)

### MCMASTER UNIVERSITY Hamilton, Ontario

| TITLE:           | Proving Implementability of Timing Properties with<br>Tolerances                                 |

|------------------|--------------------------------------------------------------------------------------------------|

| AUTHOR:          | Xiayong Hu<br>B.Eng., Shanghai Jiao Tong University, China<br>M.Sc., McMaster University, Canada |

| SUPERVISOR:      | Drs. Mark Lawford and Alan Wassyng                                                               |

| NUMBER OF PAGES: | xvi, 127                                                                                         |

To Jia and Felice

## Abstract

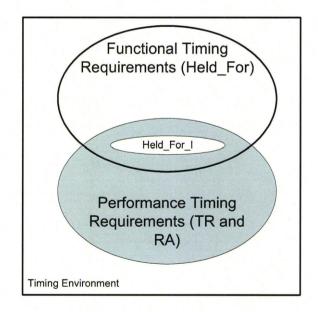

Many safety-critical software applications are hard real-time systems. They have stringent timing requirements that have to be met. We present descriptions of timing behaviors that include precise definitions as well as analysis of how functional timing requirements (FTRs) interact with performance timing requirements (PTRs), and how these concepts can be used by software designers. The definitions explicitly show how to specify timing requirements with tolerances on time durations.

This thesis shows the importance of specifying both FTRs and PTRs, by revealing the fact that their interaction directly determines the final implementability of real-time systems. By studying this interaction under three environmental assumptions, we find that the implementability results of the timing properties are different in each environment, but they are closely related. The results allow us to predict the system's implementability without developing or verifying the actual implementation. This also shows that we can sometimes significantly reduce the sampling frequency on the target platform, and still implement the timing requirement correctly.

We present a component-based approach to formalizing common timing requirements and provide a pre-verified implementation of one of these requirements. The verification is performed using the theorem proving tool PVS. This allows domain experts to specify the tolerance in each individual timing requirement precisely. The pre-verified implementation of a timing requirement is demonstrated by applying the method in two examples. These examples show that both the design and verification effort are reduced significantly using a pre-verified template.

A primary focus of this thesis is on how to include tolerances on tim-

ing durations in the specification, implementation and verification of timing behaviors in hard real-time applications.

## Acknowledgments

First of all, I shall express my sincere gratitude to my supervisors. Dr. Mark Lawford, my supervisor since my master's program, has been guiding me patiently and supporting me to finish this long run. Dr. Alan Wassyng, who became my co-supervisor in 2005, has dedicated a huge amount of his time to help me make progress in my Ph.D. studies.

Second, I must thank my supervisory committee members. Dr. William M. Farmer has provided invaluable comments on my research work ever since my master's thesis work. Dr. Tom Maibaum provided careful review and so many helpful comments.

Third, I must thank my friends for their knowledge, encouragement and help. Yutong He shared a lot of experience in both thesis writing and defense preparation.

Last and certainly not least, I must thank Jia Yu, my parents and my in-laws. They have always supported my studies and encouraged me to complete them. With my family, I have shared every day of this endeavor.

## Contents

| A        | bstra | ct      |                                                      | iv  |

|----------|-------|---------|------------------------------------------------------|-----|

| A        | cknov | wledgn  | nents                                                | vi  |

| Li       | st of | Figure  | es                                                   | xi  |

| Li       | st of | Tables  | 5                                                    | xiv |

| 1        | Intr  | oducti  | on                                                   | 1   |

|          | 1.1   | Motiva  | ation                                                | 2   |

|          | 1.2   | Relate  | d work                                               | 4   |

|          |       | 1.2.1   | Summary                                              | 4   |

|          |       | 1.2.2   | Two Major Challenges                                 | 5   |

|          |       | 1.2.3   | Examples of Requirements Validation                  | 5   |

|          |       | 1.2.4   | Related Work in Implementation Verification          | 7   |

|          | 1.3   | Contri  | butions                                              | 10  |

|          | 1.4   | Thesis  | Outline                                              | 12  |

| <b>2</b> | Pre   | liminaı | ries                                                 | 13  |

|          | 2.1   | PVS F   | Preliminaries                                        | 13  |

|          |       | 2.1.1   | PVS Proofs in Sequent Calculus                       | 14  |

|          |       | 2.1.2   | Unprovable Sequents and Counterexamples              | 15  |

|          |       | 2.1.3   | PVS Support for Tables                               | 16  |

|          |       | 2.1.4   | Overview of the Naming Convention in PVS             | 19  |

|          | 2.2   | Requir  | rements Refinement and SDV Procedure Overview        | 21  |

|          | 2.3   | The P   | VS-RT method                                         | 23  |

|          | 2.4   | Limita  | tions of <i>Held_For</i> operators without tolerance | 25  |

| 3 | Env | rironm  | ental Assumptions and Impact on Implementability              | 29 |

|---|-----|---------|---------------------------------------------------------------|----|

|   | 3.1 | Envire  | onmental Assumptions                                          | 30 |

|   | 3.2 | Funct   | ional and Performance Timing Requirements                     | 31 |

|   | 3.3 | Imple   | mentability of <i>Held_For</i> in a Perfect Clock Environment | 39 |

|   |     | 3.3.1   | Manual Analyses of Implementability Results                   | 41 |

|   |     | 3.3.2   | Latest Results for the Perfect Clock Environment $\ldots$     | 43 |

|   |     | 3.3.3   | PVS Aided Analysis for Case 2                                 | 46 |

|   |     | 3.3.4   | Examples of Feasible Sample Interval Ranges                   | 48 |

|   | 3.4 | Comp    | aring the feasibility results in different environments       | 50 |

|   | 3.5 | Imple   | mentability of <i>Held_For</i> in an Omniscient Environment . | 53 |

|   | 3.6 | Imple   | mentability of <i>Held_For</i> in a No Clock Environment      | 55 |

|   | 3.7 | Summ    | ary                                                           | 57 |

| 4 | For | mal Ve  | erification of Feasibility Results                            | 59 |

|   | 4.1 | Overv   | iew of the PVS Theories                                       | 60 |

|   | 4.2 | PVS 7   | Theory for Sample Type                                        | 61 |

|   |     | 4.2.1   | Time Theory                                                   | 61 |

|   |     | 4.2.2   | SampleInstance Theory                                         | 61 |

|   |     | 4.2.3   | FeasibilityResults Theory                                     | 64 |

|   | 4.3 | Roadr   | nap to Prove the Feasibility Theorems                         | 68 |

|   |     | 4.3.1   | Proving Strategy for Case 1                                   | 68 |

|   |     | 4.3.2   | Proving Strategy for Case 2                                   | 69 |

|   |     | 4.3.3   | Proving Strategy for Case 3                                   | 72 |

|   | 4.4 | Summ    | ary                                                           | 73 |

| 5 | Imp | lemen   | ting <i>Held_For</i> with Tolerance                           | 75 |

|   | 5.1 | Refini  | ng Time                                                       | 76 |

|   |     | 5.1.1   | Timing Model in Physical Domain                               | 76 |

|   |     | 5.1.2   | PVS Theories Based on the Tick Type                           | 77 |

|   |     | 5.1.3   | Difference between Tick and Clock Types                       | 79 |

|   | 5.2 | Held_l  | For operator in Physical and Software Domains                 | 80 |

|   |     | 5.2.1   | Definitions                                                   | 83 |

|   |     | 5.2.2   | Filtered Tick Predicate                                       | 87 |

|   | 5.3 | A mor   | e detailed Implementation Roadmap                             | 89 |

|   | 5.4 | Verific | ation of Held_For_I Based on High Level Requirements .        | 91 |

| 5.5                | Implementation of <i>Held_For</i>                                                                                               | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | 5.5.1 Timer Implementation of Held_For_I $\ldots \ldots \ldots$                                                                 | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                    | 5.5.2 Verification of the Implementation of Held_For_S                                                                          | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                    | 5.5.3 Verification of the Implementation of Held_For $\bot$                                                                     | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.6                | Summary                                                                                                                         | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Exa                | amples                                                                                                                          | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.1                | Example: Sensor Lock System                                                                                                     | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 6.1.1 Overview of the System                                                                                                    | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 6.1.2 Software Requirement Specification (SRS) $\ldots$ $\ldots$                                                                | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 6.1.3 Software Design Description (SDD)                                                                                         | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 6.1.4 Implementation Assumptions                                                                                                | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

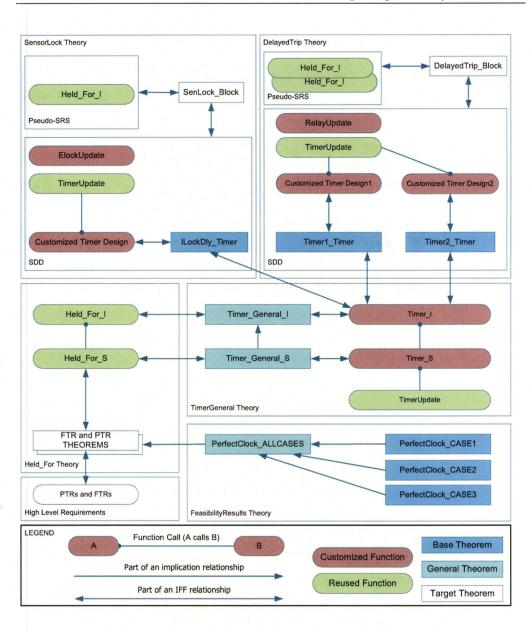

|                    | 6.1.5 Formal Verification of the SenLock System                                                                                 | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2                | Example: Delayed Trip System                                                                                                    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 6.2.1 Software Requirement Specification (SRS) $\ldots$ $\ldots$                                                                | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 6.2.2 PVS Software Design Description (SDD)                                                                                     | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

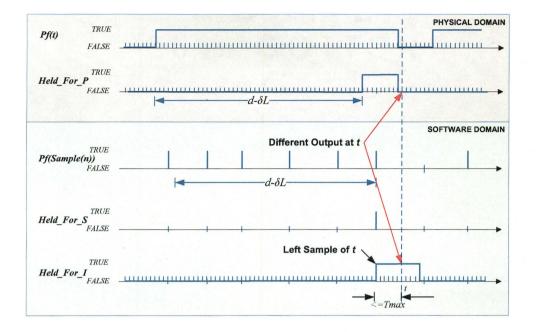

|                    | 6.2.3 Formal Verification of the Delayed Trip Example $\ldots$                                                                  | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.3                | Summary                                                                                                                         | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Sun                | nmary                                                                                                                           | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.1                | Future Work                                                                                                                     | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Tin                | ne Theory                                                                                                                       | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| San                | npleInstance Theory                                                                                                             | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Б                  |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fea                | sibilityResults Theory                                                                                                          | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | sibilityResults Theory<br>ckTick Theory                                                                                         | 132<br>138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Clo                |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Clo<br>San         | ckTick Theory                                                                                                                   | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Clo<br>San<br>Hele | ckTick Theory<br>npleInstanceOnTick Theory                                                                                      | 138<br>140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | <ul> <li>5.6</li> <li>Exa</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>Sum</li> <li>7.1</li> <li>Tim</li> <li>San</li> </ul> | 5.5.1       Timer Implementation of Held_For_J         5.5.2       Verification of the Implementation of Held_For_J         5.5.3       Verification of the Implementation of Held_For_J         5.6       Summary         5.6       Summary         5.6       Summary         6.1       Examples         6.1       Example: Sensor Lock System         6.1.1       Overview of the System         6.1.2       Software Requirement Specification (SRS)         6.1.3       Software Design Description (SDD)         6.1.4       Implementation Assumptions         6.1.5       Formal Verification of the SenLock System         6.2       Example: Delayed Trip System         6.2.1       Software Requirement Specification (SRS)         6.2.2       PVS Software Design Description (SDD)         6.2.3       Formal Verification of the Delayed Trip Example         6.3       Summary         7.1       Future Work         Time Theory         SampleInstance Theory |

### I DelayedTrip Theory

156

# List of Figures

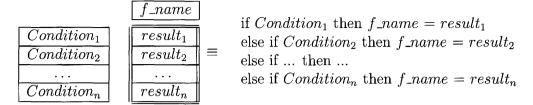

| 2.1  | Horizontal Condition Tables                                                   | 17 |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | A Labeled Complex Horizontal Condition Table                                  | 17 |

| 2.3  | PVS Code of the sample ELOCK Function                                         | 18 |

| 2.4  | PVS Naming Convention Example                                                 | 21 |

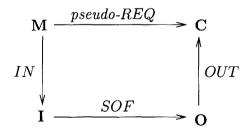

| 2.5  | Revised Commutative Diagram for 4 Variable Model                              | 22 |

| 2.6  | The SRS for the Delayed Trip System Block                                     | 26 |

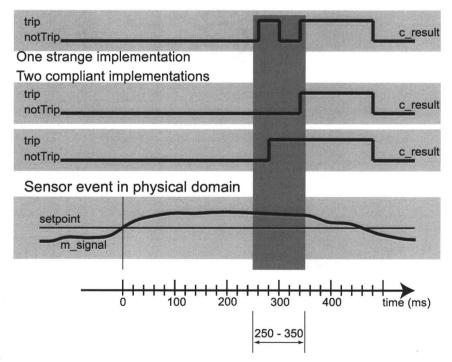

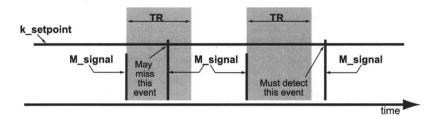

| 3.1  | Two Valid Implementations of a Sustained Timing Requirement                   | 32 |

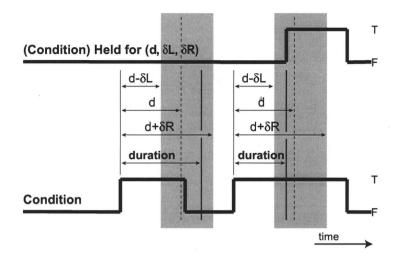

| 3.2  | Held_For Functional Timing Requirement                                        | 34 |

| 3.3  | Formal Definition of "(Condition) Held_For $(d, \delta L, \delta R)$ "        | 35 |

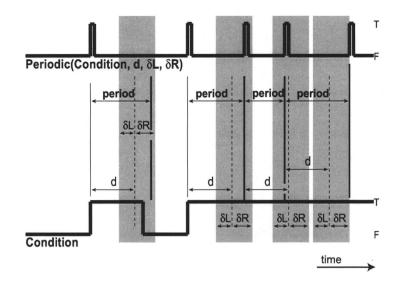

| 3.4  | A Periodic Functional Timing Requirement                                      | 36 |

| 3.5  | Formal Definition of " <i>Periodic</i> (Condition, $d, \delta L, \delta R$ )" | 36 |

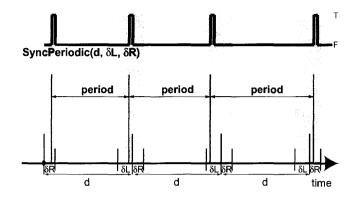

| 3.6  | Synchronized Periodic Functional Timing Requirement                           | 37 |

| 3.7  | Formal Definition of "SyncPeriodic( $d, \delta L, \delta R$ )"                | 37 |

| 3.8  | Timing Resolution for Time Continuous Monitored Variable .                    | 38 |

| 3.9  | Timing Resolution for Time Discrete Monitored Variable                        | 38 |

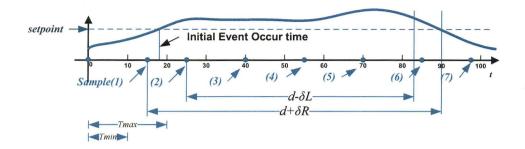

| 3.10 | An Example of Sample Instances                                                | 40 |

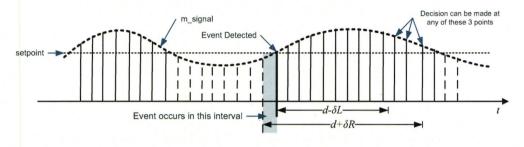

| 3.11 | An Example of Decision Points                                                 | 41 |

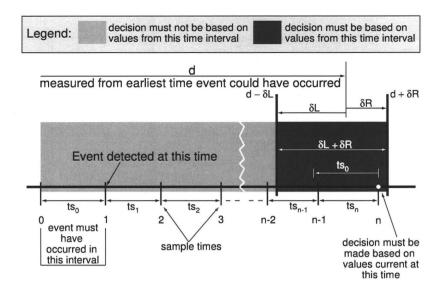

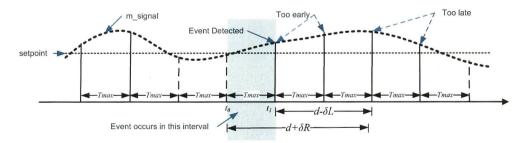

| 3.12 | Sample Intervals Required for Sustained Events                                | 42 |

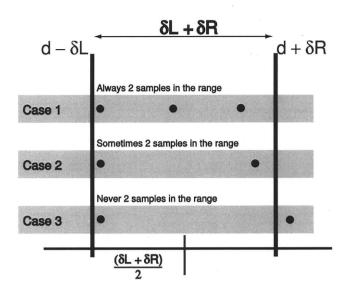

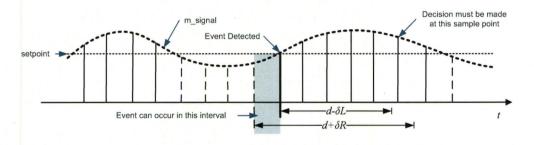

| 3.13 | Sample Points in the Duration Interval                                        | 43 |

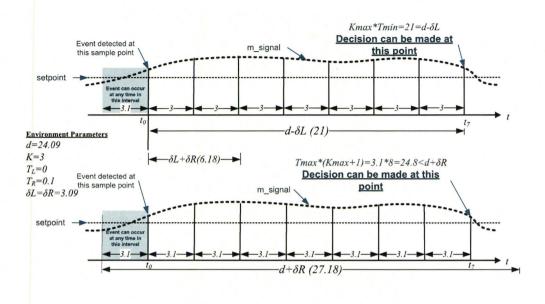

| 3.14 | Case 1 of the Perfect Clock Environment                                       | 44 |

| 3.15 | Case 3 of the Perfect Clock Environment                                       | 45 |

| 3.16 | Case 2 of the Perfect Clock Environment                                       | 46 |

| 3.17 | Case 2 of the Perfect Clock Environment (Boundary Example)                    | 48 |

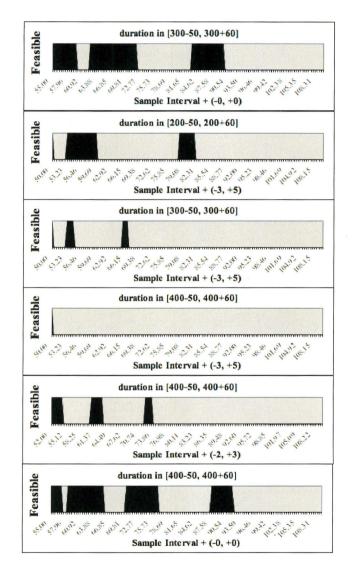

| 3.18 | Feasible Sample Intervals for Various Durations and Tolerances                | 49 |

| 3.19 | Case 2 of the Omniscient Environment                                          | 54 |

| 3.20                                                                                                 | Case 1 of the No Clock Environment                     | 56                                                                               |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------|

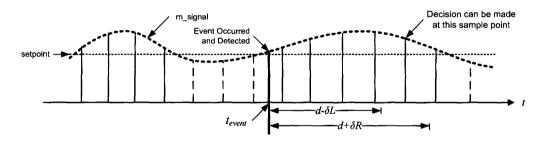

| 4.1                                                                                                  | Overview of PVS Theories and their dependencies        | 60                                                                               |

| 4.2                                                                                                  | Time Theory in PVS                                     | 61                                                                               |

| 4.3                                                                                                  | SampleInstance PVS Theory                              | 62                                                                               |

| 4.4                                                                                                  | PVS Lemmas of Sample Properties                        | 64                                                                               |

| 4.5                                                                                                  | FeasibilityResults PVS Theory                          | 65                                                                               |

| 4.6                                                                                                  | PVS Theorems: Feasibility in Perfect Clock Environment | 66                                                                               |

| 4.7                                                                                                  | PVS Theorems: Feasibility in Omniscient Environment    | 67                                                                               |

| 4.8                                                                                                  | PVS Theorems: Feasibility in No Clock Environment      | 67                                                                               |

| 4.9                                                                                                  | PVS Theorems: Relationship between Feasible Functions  | 68                                                                               |

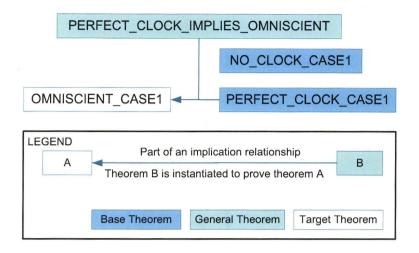

| 4.10                                                                                                 | Proving Strategy for Case 1                            | 69                                                                               |

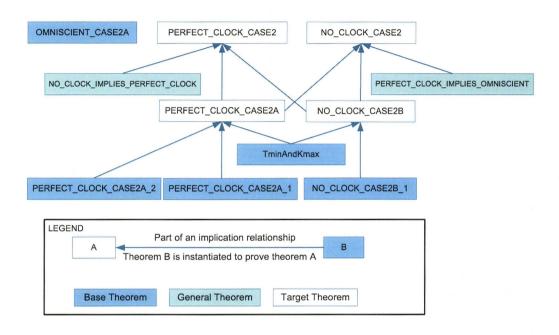

| 4.11                                                                                                 | PerfectClock_CASE2 and NoClock_CASE2 Break Down        | 70                                                                               |

| 4.12                                                                                                 | Proving Strategy for Case 2                            | 71                                                                               |

| 4.13                                                                                                 | PVS Theorem TminAndKmax                                | 71                                                                               |

| 4.14                                                                                                 | PVS Theorems for PerfectClock_CASE2A                   | 72                                                                               |

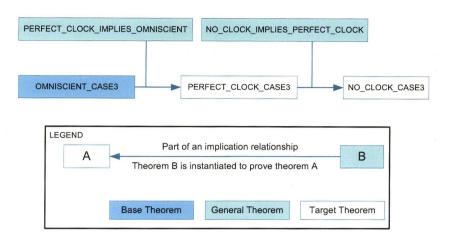

| 4.15                                                                                                 | Proving Strategy for Case 3                            | 73                                                                               |

|                                                                                                      |                                                        |                                                                                  |

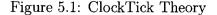

| 5.1                                                                                                  | ClockTick Theory                                       | 78                                                                               |

| $5.1 \\ 5.2$                                                                                         | ClockTick Theory                                       | 78<br>80                                                                         |

|                                                                                                      | •                                                      |                                                                                  |

| 5.2                                                                                                  | SampleInstanceOnTick Theory                            | 80                                                                               |

| $5.2 \\ 5.3$                                                                                         | SampleInstanceOnTick Theory                            | 80<br>81                                                                         |

| $5.2 \\ 5.3 \\ 5.4$                                                                                  | SampleInstanceOnTick Theory                            | 80<br>81<br>81                                                                   |

| 5.2<br>5.3<br>5.4<br>5.5                                                                             | SampleInstanceOnTick Theory                            | 80<br>81<br>81<br>82                                                             |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                      | SampleInstanceOnTick Theory                            | 80<br>81<br>81<br>82<br>84                                                       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                               | SampleInstanceOnTick Theory                            | 80<br>81<br>81<br>82<br>84<br>85                                                 |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                 | SampleInstanceOnTick Theory                            | 80<br>81<br>81<br>82<br>84<br>85<br>85                                           |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                         | SampleInstanceOnTick Theory                            | 80<br>81<br>82<br>84<br>85<br>85<br>85                                           |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                 | SampleInstanceOnTick Theory                            | 80<br>81<br>82<br>84<br>85<br>85<br>85<br>86<br>86                               |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12                         | SampleInstanceOnTick Theory                            | 80<br>81<br>81<br>82<br>84<br>85<br>85<br>86<br>86<br>86<br>87                   |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                 | SampleInstanceOnTick Theory                            | 80<br>81<br>81<br>82<br>84<br>85<br>85<br>85<br>86<br>86<br>86<br>87<br>87       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14         | SampleInstanceOnTick Theory                            | 80<br>81<br>82<br>84<br>85<br>85<br>86<br>86<br>86<br>87<br>87<br>87             |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15 | SampleInstanceOnTick Theory                            | 80<br>81<br>81<br>82<br>84<br>85<br>85<br>86<br>86<br>86<br>87<br>87<br>88<br>89 |

| 5.18 | PVS Theorem Held_For_I_VERIFY_FTR4                                                                                         | 94 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

| 5.19 | PVS Theorem Held_For_L_VERIFY_FTR2                                                                                         | 94 |

| 5.20 | PVS Theorem Held_For_L_VERIFY_FTR3                                                                                         | 95 |

| 5.21 | Timer_S Function                                                                                                           | 97 |

| 5.22 | TimerUpdate Function                                                                                                       | 97 |

| 5.23 | Timer_I Function                                                                                                           | 98 |

| 5.24 | PVS Theorem TimerGeneral_S                                                                                                 | 99 |

| 5.25 | PVS Theorem TimerGeneral_I                                                                                                 | 99 |

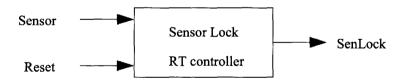

| 6.1  | Block diagram for real-time SenLock controller                                                                             | 02 |

| 6.2  | The upgraded version SRS of SenLock System                                                                                 | 03 |

| 6.3  | PVS Definition of Sensor Lock SRS                                                                                          | 03 |

| 6.4  | PVS Definition of Sensor Lock SDD                                                                                          | 04 |

| 6.5  | PVS Definition of ElockUpdate                                                                                              | 05 |

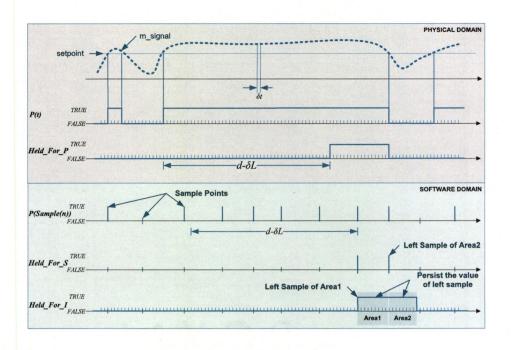

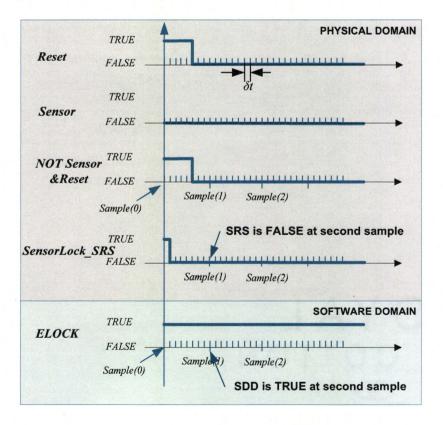

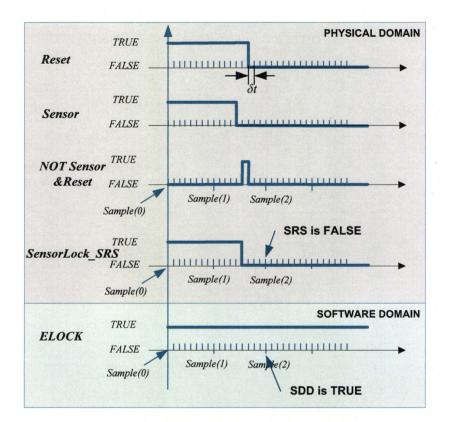

| 6.6  | Example of disagreement on second sample point 1                                                                           | 06 |

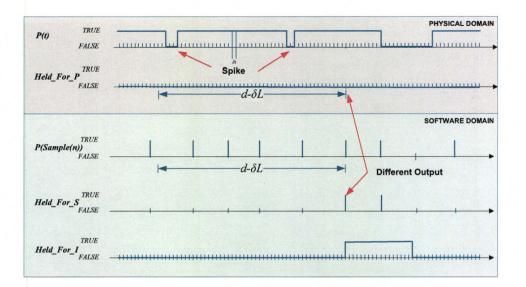

| 6.7  | Spike behavior between consecutive sample points 1                                                                         | 08 |

| 6.8  | SenLock System Proof Obligation                                                                                            | 09 |

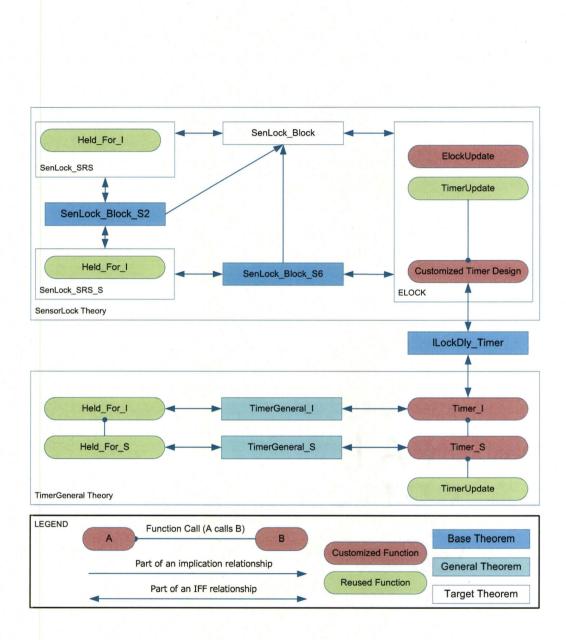

| 6.9  | Theorems and Lemmas of the SensorLock Theory $\hdots$ 1                                                                    | 10 |

| 6.10 | SenLock_SRS_S Function                                                                                                     | 11 |

| 6.11 | PVS Theorem SensorLock_Block_S6                                                                                            | 12 |

| 6.12 | PVS Theorem SensorLock_Block_S2 1                                                                                          | 12 |

| 6.13 | The Upgraded SRS for the Delayed Trip System                                                                               | 13 |

| 6.14 | PVS Pseudo-SRS of Delayed Trip System                                                                                      | 14 |

| 6.15 | RelayUpdate Function $\ldots \ldots 1$ | 15 |

| 6.16 | PVS Code for DTS SDD                                                                                                       | 16 |

| 6.17 | PVS Lemma Timer 1. Timer                                                                                                   | 18 |

# List of Tables

| 2.1 | The Updated SRS for the Delayed Trip System block             | 28  |

|-----|---------------------------------------------------------------|-----|

| 3.1 | Comparison of Implementability Results                        | 51  |

| 4.1 | Comparison of the Proof Work of Case $3 \ldots \ldots \ldots$ | 73  |

| 4.2 | Proof Work of the Feasibility Results                         | 74  |

| 4.3 | Proof Work of General Theorems                                | 74  |

| 6.1 | Verification Effort Comparison of Two Examples                | 120 |

| 7.1 | Summary of Contributions                                      | 123 |

.

## Glossary

- $\mathbb{R}^{\geq 0}$  25 Non-negative real numbers

- $\mathbb{N}$  39 Set of Natural Numbers ({0, 1, 2, ...})

- $\top$  14 Boolean constant *TRUE*

- $\perp~14~$  Boolean constant FALSE

- $\models$  15 Semantic entailment

- $g \circ f$  23 Functional composition

- d 33 Duration of *Held\_For* operator

- $\delta L$  33 (Left) Tolerance of duration d

- $\delta R$  33 (Right) Tolerance of duration d

- $T_{min}$  39 Lower bound of the sample interval

- $T_{max}$  39 Upper bound of the sample interval

$$\begin{array}{ccc} K_{max} & 44 & \left\lfloor \frac{d - \delta L}{T_{min}} \right\rfloor \\ K_{min} & 44 & \left\lfloor \frac{d - \delta L}{T_{max}} \right\rfloor \end{array}$$

- $\delta t$  76 Arbitrarily small time interval between clock ticks

- FTRs 31 Functional Timing Requirements

- PTRs 31 Performance Timing Requirements

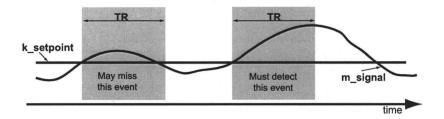

- TR 36 Timing Resolution

- RA 38 Response Allowance

- SDV 21 Systematic Design Verification

- DTS 25 Delayed Trip System

- SRS 22 Software Requirements Specification

- SDD 22 Software Design Description

- Held\_For 2 An operator defined for sustained events

- $Held\_For\_W$  24  $Held\_For$  operator without tolerance defined in [9]

- *Held\_For\_N* 24 *Held\_For* operator *without tolerance* with a "narrower" window

## **PVS Glossary**

- PVS 13 Prototype Verification System

- TCC 18 Type Correctness Conditions

- Held\_For\_S 83 A PVS function defined for sustained events at sample level

- Held\_For\_I 11 A PVS function defined as an intermediate operator between the design and high level requirements of *Held\_For with tolerance*

- Held\_For\_P 83 Held\_For operator which reflects the sustained result in the physical domain.

- Timer\_S 97 A PVS function implements the Held\_For\_S with a timer design

- Timer\_I 98 A PVS function implements the Held\_For\_I with a timer design

- TimerGeneral\_S 99 A PVS theorem pre-verifies Timer\_S implements Held\_For\_S

- TimerGeneral\_I 99 A PVS theorem pre-verifies Timer\_I implements Held\_For\_I

## Chapter 1

## Introduction

"A real-time system is one whose correctness depends not only on values of its outputs, but also on the times at which they are produced" [22]. In order to ensure its correct operation in critical contexts, it is important to rigorously demonstrate that a system's timing requirements are satisfied [7, 25]. In other words, the implementation must not only produce the correct functional outputs but also has to produce them right on time.

Modern real-time systems often have requirements that determine the current outputs based not only on current inputs, but also upon the history of inputs and outputs [15, 34]. An example of such a system is a nuclear reactor shutdown system that has the requirement, "If power and pressure both exceed their maximum allowable limits for 3 seconds, then open the relay for 2 seconds" [14]. Another example is a pacemaker, which is a small device that can be placed under the skin of a patient's chest, to help control abnormal heart rhythm. If a patient's heart does not beat or becomes abnormal for a specified duration, the controller must take action to initiate an electrical pulse to prompt the heart to beat at a normal rate. For both examples above, we can see that real-time systems are often safety-critical. Any failure can cause unrecoverable system failures (i.e., a loss of containment of nuclear material or a pace at the wrong time that might end a patient's life).

Formal methods have been applied in software development in order to provide precise and rigorous specifications, validate the requirements, verify the implementation, etc. However, most formal methods do not scale well (e.g., consider the state-explosion problem in model checking) or they ignore the hard to deal with real-world details (such as timing tolerances) in order to make the resulting mathematical models tractable for analysis and refinement. In this thesis, we present an approach to precisely define complex timing requirements that include tolerances on all time durations to formally verify the feasibility of implementing those requirements, and finally we use this knowledge to build a pre-verified template that implements one of the most common timing requirements that occurs in real world applications.

### 1.1 Motivation

A central focus of this thesis is the specification and implementation of sustained events (later described by the *Held\_For* operator). Sustained events are extremely common in hard real-time systems. The following is a typical example of such an event:

If there has been no ventricle pace initiated for the automatic interval and no sensed event for the spontaneous interval, then pace for  $k_{pace}$  Width.

In this simple requirement, we can find three "held for" events. The first two are the conditions to trigger the pacing: the condition "no ventricle pace initiation" (from the pacemaker) has "held for" the automatic interval and the condition "no sensed event" (from a patient's heart) has "held for" the spontaneous interval. The third one is the pacing control, saying if the above conditions are satisfied, then the pacing must start and be "held for" a sustained duration of  $k_paceWidth$ .

There are other reports of the application of *Held\_For* operators in the real-time systems in the industrial world as well (e.g., the Darlington Nuclear Shutdown System [29]). Therefore, we choose the *Held\_For* operator as the focus of our interest and work. The following overview of the topics highlights the motivation for this thesis.

**Difficulties in formalizing, designing and verifying system timing requirements.** Specifying, implementing and verifying real-time requirements for embedded software systems is a difficult and time-consuming task. If a developer fails to correctly stop, start or reset a timer under conditions that seldom occur, it can result in a design flaw detected late in the development phase, or even worse, a system failure in the field. Hence real-time systems have become an active area of research in the formal methods community. An extensive survey of formal methods for the specification and verification of real-time systems was completed recently by Wang [28] (Section 1.2.1). The survey contains references to well over 200 publications related to the topic. The publications can be categorized by the model of time that they use, either continuous/dense time or discrete time. The overwhelming majority of the referenced publications are dedicated to the specification and validation of real-time requirements within their chosen model of time.

Large gap in requirements and implementation models. Despite a number of comparisons and surveys of real-time formalisms, relatively little work has been done connecting the two types of models when they are used at the levels they best represent: continuous time at the requirements level and discrete time at the implementation level.

Necessary and sufficient conditions for implementation. More researchers are now focusing on using a "platform-independent" layer [8] as a bridge between the abstract high level specification and coding languages like C++. The benefit of using a middle layer is to narrow the large semantic gap between modeling languages and implementation languages. However, the inconsistencies between the design model and realization typically cannot be observed until the final stages. A large amount of work can be saved if we can figure out the necessary and sufficient conditions for implementing the major timing components of the whole system before proceeding to any detailed implementation of the system. For example, the method in [29] shows a way to tell whether further implementation activities are worth it or not as soon as the timing requirements have been specified.

Use pre-verified timing elements. Most real-time systems can be modeled based on basic timing operators at the requirements level, for example "Since P" [25] and *Held\_For* [9, 29]. The serialization, composition and nesting of these fundamental timing elements can be used to model the system requirements in complex real-time systems. A pre-verified timing operator library will benefit real-time system design and verification in the following ways:

1. Developers can pick the timing operator from the library to implement the system and plugin the pre-verified theorem to get the whole system verified on-the-fly.

2. Developers can also provide their own timing operator during the system design, and compare and prove its equivalence to any existing operator or combination of operators in the library, which can speed up the verification of the whole system.

The motivation for this library is that real-time system design and verification is difficult because real-time timing requirements are difficult to implement and verify. We simplify this process by extracting the fundamental timing behaviors of the system, specifying and verifying them using pre-verified timing operators, and thereby saving repetitive work when dealing with systems that fall within the domain for which we have developed a timing operator library.

### 1.2 Related work

#### 1.2.1 Summary

We took an extensive survey [28] of formal methods for the specification and verification of real-time systems as our roadmap to investigate the related work. Although it contains references to over 200 publications, very few of them are found to be related to our research topic. The overwhelming majority of the cited works are dedicated to the specification and validation of real-time requirements. Despite this intensity of research, relatively little work has been done on formally modeling timing tolerances and implementation verification.

#### 1.2.2 Two Major Challenges

There are two major challenges in designing and implementing real-time systems: requirements validation and implementation verification. Requirements validation, also called "design validation" in [4], is to ensure the correctness of the requirements at the earliest stage possible, while implementation verification is to verify the correctness of the implementation against the formal requirements. For most real-time systems, they are equally important since any mistake in the implementation may directly lead to unrecoverable loss.

In the last two decades, many achievements in requirements validation of real-time systems have been reported [28]. Some of the most referenced modeling techniques are timed automata [2], timed Petri Nets [1] and timed process algebras (e.g., [21]). However, they are not related to our research topic as most of them only focus on modeling the real-time system and validating the correctness of the model. Our objective is to formally model and implement real-time systems with timing tolerances, ensuring the correct timing properties in the implementation using design verification. Since the timed automata formalism is one of the most widely researched modeling techniques introduced, we will use it as an example to explain the differences between our design verification focus and the more common requirements validation focus.

#### 1.2.3 Examples of Requirements Validation

#### Timed automata modeling and validation

A model describes selected behavior of a system [28]. Modeling is the first task to convert a design into a formalism accepted by a model checking tool [4]. Timed automata were introduced as a formal notation to model the behavior of real-time systems. They provide a general way to annotate state-transition graphs with timing constraints using finitely many clock variables [2].

Temporal logic (with timing extensions) can be used to specify the real-time properties that the design must satisfy. Branching time temporal logics [3] like Computational Tree Logic can, for example, express whether a formula will eventually be true on at least one path or on all paths. Model checking provides a means for checking whether a model of the design satisfies a given specification. Given the system descriptions as timed automata and the specification temporal logic formulas that describe the properties we want to verify, we can determine whether the models of a given system description satisfies the specification described by Temporal Logic formulas. Some model checking tools can also generate counterexamples, a series of reachable states which do not satisfy the Temporal Logic formula. This helps the verifier to easily identify errors during the validation process. Compared to theorem proving, model checking is almost fully automatic, requiring less user supervision and expertise. However, it is impossible to determine whether the given specification covers all the properties that the system should satisfy [4]. The coverage of the specification formulas usually determines how deeply a design is validated. The specification formulas should be as complete as possible to cover all the important timing properties.

#### Testing implementation for timed automata

There are mainly two approaches to generate the test cases for timed automata, either online or offline. In online (on-the-fly) approaches, the testing environment is responsible for computing the next test primitive and verifying the current output against the specification on-the-fly. In offline approaches, the complete set of test scenarios are computed before execution [12].

The algorithm for online testing with the timed automata model checker UPPAAL described in [12] randomly offers an input, waits for an output until a timeout, or restarts the testing process in each testing cycle. If UPPAAL observes an output or a time delay, it checks whether this is legal according to the state set. Whenever an input is offered or an output/delay is observed, the state set will be updated. Once UPPAAL detects an illegal occurrence or absence of an output during any test cycle, a fail signal is produced and the testing process is ended. Although the state-space-explosion problem experienced by many offline test generation tools is reduced in UPPAAL, because only a limited part of the state-space needs to be stored at any point in time, very large specifications with an extreme amount of non-deterministic behavior may still need significant time to compute the reachable symbolic state set [18]. Plus, the coverage of this approach is random which has an impact on its error detection capability [12]. Sprinintveld *et al.*, presented the first test generation algorithm [27] that yields a finite and complete set of tests for dense real-time systems. In order to limit the infinite problem size, some strong assumptions are made to restrict the problem size. For example, the system is assumed to be *deterministic* and have *isolated outputs* (for each state, if an output is enabled then no other input/output transition can be enabled). Even with these strong assumptions, the algorithm itself is super exponential and cannot be claimed to be of any practical value (according to the authors) [27].

We have the following conclusions from the above discussion: 1. So far, we still lack a formal and effective method to verify the implementation from a timed automata model of a real-time system. 2. Although researchers have done a lot to minimize or even remove the non-determinism in the timed automata, the problem size is still too big to be of practical use. Tremendous work has been done on validating timed automata, but the verification and testing gap between a timed automata model and its implementation is still huge. Our goal is to introduce a formal approach to perform both requirements validation and implementation verification. In this approach, we will consider timing uncertainty (i.e., outputs and given stimuli classified in an interval of time rather than a time instance), which has not been taken into account in timed automata yet [12, 18].

#### 1.2.4 Related Work in Implementation Verification

The overwhelming majority of the cited works in [28] are dedicated to the specification and validation of real-time requirements. Despite this intensity of research, relatively little work has been done on formally modeling timing tolerances.

Recent work has begun to address the issue of the timing tolerances when verifying implementations of requirements modeled as timed automata with Almost ASAP (as soon as possible) semantics [35, 36]. De Wulf et al., consider the case of implementing a continuous-time controller with a discrete-time system, assuming that there is a delay  $\Delta$  associated with the controller's reaction to the environment. Both the controller and the plant are first modeled as timed automata. Their control objective is to ensure that the closed-loop system satisfies a safety property by avoiding bad states. Provided that all control actions can be delayed by up to some fixed  $\Delta > 0$  without violating the safety property, they say that the controller is "implementable". A PSPACE-complete decision procedure to test implementability is described in [35], while [36] provides a semi-decision procedure to compute the maximal reaction delay  $\Delta$  allowable by the implementation that still preserves the correctness of the closed loop system. Further it is shown that the system is implementable by a cyclic executive with loop time upper bound  $\Delta_L$  and a finite precision clock with a resolution of  $\Delta_P$ , provided that  $\Delta > 3\Delta_L + 4\Delta_P$ .

Giotto is described as a domain-specific high-level programming language in [8]. The approach provides an intermediate layer between the mathematical model and the code, called the embedded software model, which is independent of the target execution platform, but closer to programming code than a mathematical model. The code generation task of Giotto is partitioned into two steps, program generation and compilation. During the program generation, a high level mathematical model (e.g., a Simulink model) is transformed into an embedded software model, which is completely independent of any execution platform. Then in the second step, the software model is converted into low level executable code for a target platform. Program generation specifies only the reactivity of the system relative to a physical environment, while compilation ensures the schedulability of the system in a specific execution environment [8]. Therefore the programs in Giotto can be separated into two parts, a timing program which handles the timing concerns (e.g., sampling) and a functionality program which handles the low level implementation. The concept is close to the functional and performance timing requirements that we will introduce in this thesis. The difference is that our approach will predict the impact of their relationship on the implementability of the system in the early stage of the analysis, to avoid unnecessary complex implementation and verification.

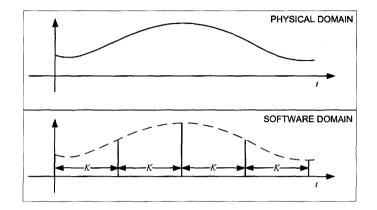

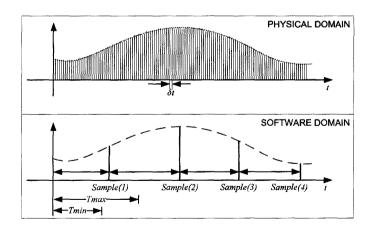

The assumption of zero-time for computational action in the model language is impossible to ensure on the target platform in the implementation language [6]. Thus the predictable design approach introduced in [10]an  $\epsilon$ -hypothesis to fill the gap between the physical domain and the software domain. This  $\epsilon$ -hypothesis requires the model and its realization to have the same observable execution sequence. Also, time deviations between activations of corresponding actions in the model and realization should be less than  $\epsilon$  seconds. In the predictable design approach, the generation tool called Rotalumis takes the model coded with model language POOSL, and automatically generates the executable for the target platform. We note that this hypothesis is very close to what we call "response allowance" (Section 3.2), one of our performance timing requirements, which is measured from the time the event actually occurred in the physical domain until the time the value of the controlled variable is generated and crosses the application boundary into the physical domain. Our research also covers the tolerances in timing requirements when crossing from the physical domain to the software domain, which is not discussed in [6, 10].

The summarized research above is focused on connecting the requirements and implementation. We notice that we can categorize most of the current approaches into two categories: platform-independent and global tolerance. Most research based on the platform-independent idea will plug in another layer between the high level requirements and coding implementation, e.g., "program generation" in the Giotto approach [8] and the POOSL model in [6, 10]. In these approaches, whether or not a system can be implemented on a target platform cannot be known until the final scheduling stage is finished. In the case of the generation of an unimplementable result, the designer has to improve the hardware performance or relax the timing requirements, both of which are problematic.

The approaches with global tolerances (e.g., reaction delay parameter  $\Delta$  in [36] and  $\epsilon$ -hypothesis in [10]) all define a global constraint as the constant upper bound of the delay during implementation. The benefit of a single global tolerance is clear. It is easy to analyze and greatly simplifies the problem. However, in most industrial applications, different tolerances are required for different timing requirements. A global tolerance on all timing durations does not make much sense at the requirements level. In addition, at the implementation level, timing tolerances in sampling intervals (jitter) may be caused in many ways. Unless the executive is a very simple loop, it is likely that different timing functions will exhibit different jitter. Again, a global tolerance seems to be both a simplification and too restrictive. The results we have so far (see Chapter 5) allow one to consider things like jitter associated with such a fast requirement being implemented by repeated calls within a cyclic executive. Our approach, to replace a very conservative global tolerance by including tolerances in each individual timing requirement, may significantly reduce unnecessary load on the target platform. This is illustrated by the Delayed Trip example in Chapter 6.

### **1.3 Contributions**

The main contributions of this thesis include: