# A VIDEO GRAPHICS TERMINAL

# A VERSATILE, HIGH SPEED, RASTER SCAN

VIDEO GRAPHICS TERMINAL

By

PETER DOUGLAS MACDONALD, B.Sc.

# A Project

Submitted to the School of Graduate Studies in Partial Fulfilment of the Requirements

for the Degree

Master of Science

McMaster University April 1979 MASTER OF SCIENCE (1979) (Computation) McMASTER UNIVERSITY Hamilton, Ontario Canada

TITLE: A Versatile, High Speed, Raster Scan Video Graphics Terminal

AUTHOR: Peter Douglas Macdonald, B.Sc. (Queen's University)

SUPERVISORS: Mr. G. J. Hicks Professor K. A. Redish

NUMBER OF PAGES: viii, 112

#### ABSTRACT

The design of a flexible, high speed, raster scan graphics terminal is presented. The design is presented in general architectural terms rather than from a detailed circuitry point of view.

Control is divided between the 'main' microprocessor, an Intel 8086, and a subservient graphics controller which consists of a microprogrammable, bit-sliced, AM2903/2910 special purpose microprocessor. The high speed graphics controller is microprogrammed to accept basic line and circle generating commands. The configuration is felt to represent an efficient balance between simplicity and speed.

#### ACKNOWLEDGEMENTS

I wish to express my appreciation to my supervisors, Mr. G. Hicks and Professor K. Redish for their guidance and assistance during the preparation of this project. I would also like to acknowledge the very great contribution made by Mr. G. Hicks to the design proposed in this report. My special thanks to Mr. G. Hicks and Professor K. Redish for the patience and cooperation which they extended to me.

# TABLE OF CONTENTS

| CHAPTER 1:   | INTRODUCTION                                  | 1   |

|--------------|-----------------------------------------------|-----|

| I. 1<br>I. 2 | Cathode Ray Tubes<br>Controlling CRT Displays | 1 2 |

| I. 3         | Design Proposal                               | 5   |

| CHAPTER 2:   | BASIC DESIGN                                  | 8   |

| II. 1        | Five Concurrent Processes                     | 10  |

| II. 1.1      | Dialogue Process                              | 11  |

| II. 1.2      | Text Definition Process                       | 12  |

| II. 1.3      | Graphics Definition Process                   | 13  |

| II. 1.4      | Text Display Process                          | 14  |

| II. 1.5      | Graphics Display Process                      | 16  |

| II. 2        | Fully Interlaced Display                      | 17  |

| II. 3        | Hardcopy Dump                                 | 18  |

| II. 4        | Process Coupling                              | 18  |

| II. 5        | Modularity                                    | 22  |

| CHAPTER 3:   | THE GRAPHICS CONTROLLER                       | 24  |

| III. 1       | Microprogramming                              | 25  |

| III. 2       | Basic Architecture                            | 28  |

| III. 3       | Microinstruction Fields                       | 32  |

| III. 3.1     | Sequence Controller                           | 33  |

| III. 3.2     | ALU                                           | 39  |

| III. 3.3     | Data Bus Interface                            | 44  |

| III. 3.4     | Bit Map Interface                             | 47  |

| CHAPTER 4:   | THE GRAPHICS CONTROLLER FIRMWARE              | 52  |

| IV. 1        | Definition Variables                          | 53  |

| IV. 2        | Definition Instructions                       | 56  |

| IV. 3        | Drawing Instructions                          | 57  |

| IV. 4        | Algorithms                                    | 62  |

| IV. 4.1      | Line Generator                                | 65  |

|              | Circle Generator                              | 70  |

|              |                                      |          |          | rage     |

|--------------|--------------------------------------|----------|----------|----------|

| CHAPTER 5:   | PERFORMANCE                          |          |          | 78       |

| V. 1<br>V. 2 | Line Generation<br>Circle Generation |          |          | 79<br>81 |

| CHAPTER 6:   | CONCLUDING REMARKS                   |          |          | 83       |

| REFERENCES   |                                      |          |          | 85       |

| APPENDIX A:  | Line and Circle Ger                  | verators | (IFTRAN) | 87       |

| APPENDIX B:  | Sample Microprogram                  | n        |          | 109      |

# LIST OF FIGURES

Page

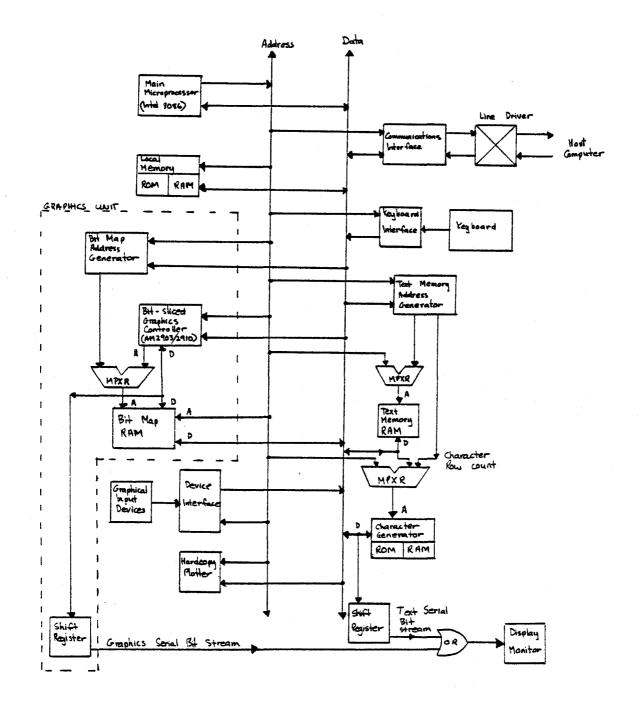

| Figure | 2.1: | The Video Graphics Terminal         | 9  |

|--------|------|-------------------------------------|----|

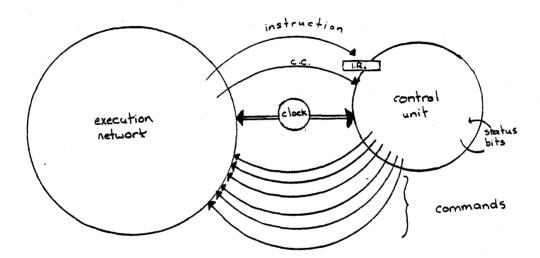

| Figure | 3.1: | The CPU of a Computer               | 26 |

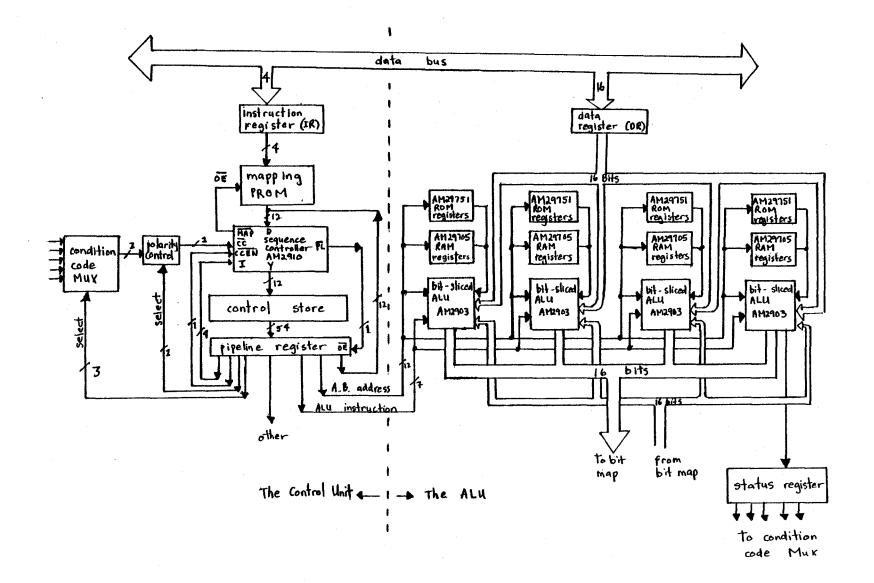

| Figure | 3.2: | The Graphics Controller             | 29 |

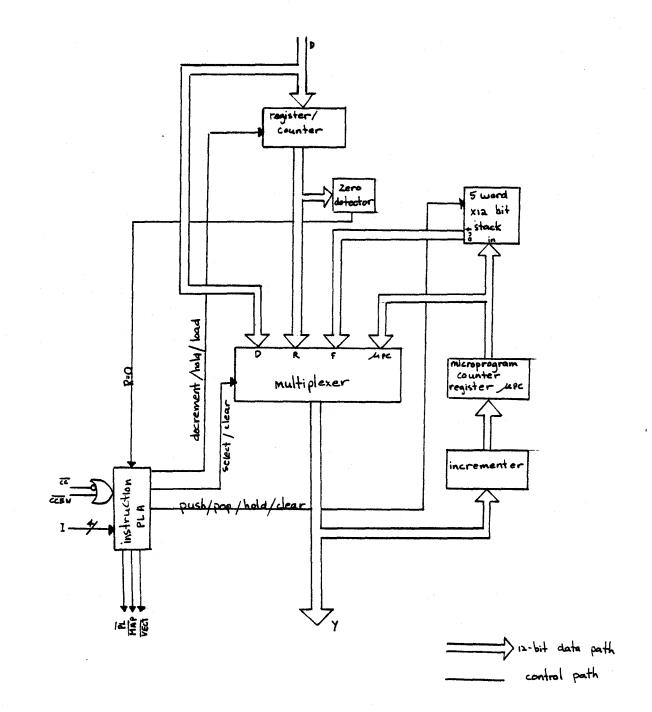

| Figure | 3.3: | The AM 2910 Microprogram Controller | 34 |

| Figure | 3.4: | The ALU                             | 40 |

| Figure | 3.5: | The Data Bus Interface              | 45 |

| Figure | 3.6: | The Bit Map Interface               | 48 |

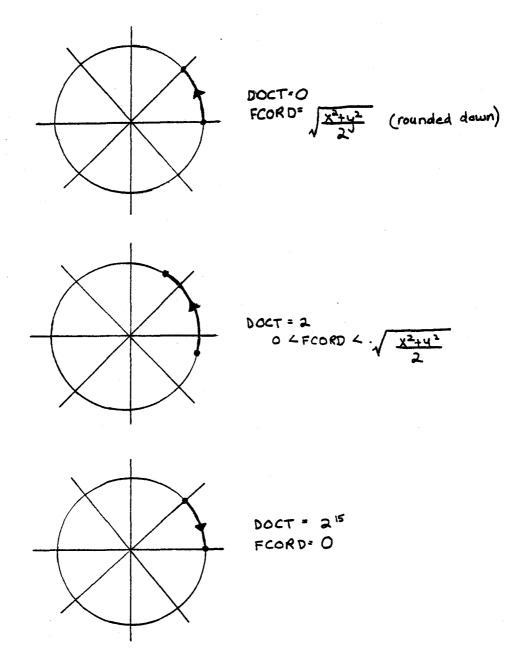

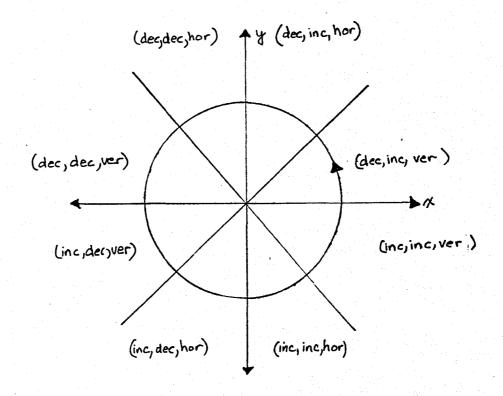

| Figure | 4.1: | The Division of a Circle            | 61 |

| Figure | 4.2: | Specification of Arc Endpoint       | 63 |

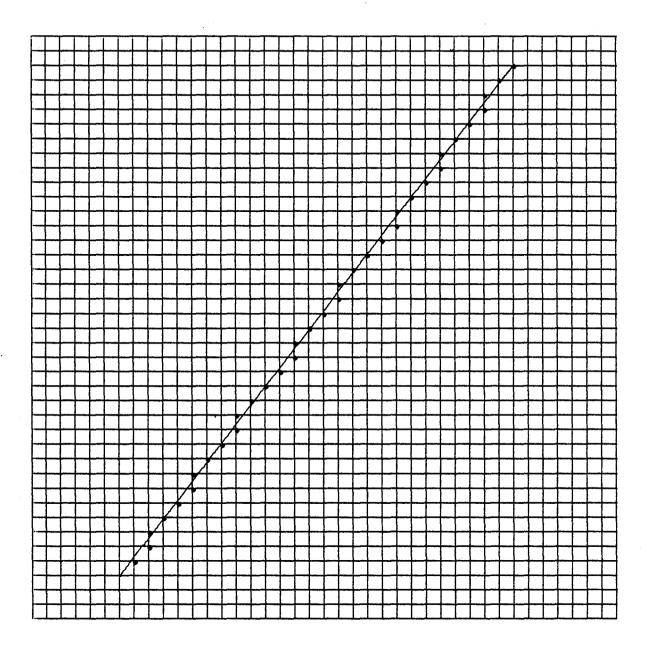

| Figure | 4.3: | Example of Line Generation          | 69 |

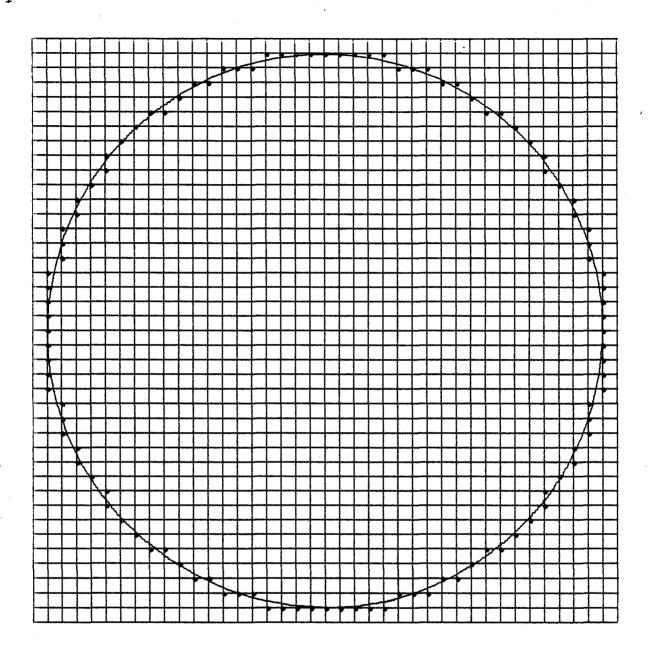

| Figure | 4.4: | Example of Circle Generation        | 74 |

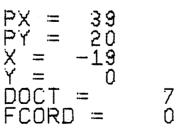

| Figure | 4.5: | Actual Motion Variables             | 76 |

### LIST OF TABLES

| Table 2.1: | Typical Video Graphics Terminal Specifications | 20 |

|------------|------------------------------------------------|----|

| Table 3.1: | The AM 2910 Instruction Set                    | 35 |

| Table 3.2: | Control Sequencer Fields                       | 37 |

| Table 3.3: | Further Microinstruction Fields                | 43 |

| Table 3.4: | Data Bus Interface Fields                      | 46 |

| Table 3.5: | Bit Map Interface Fields                       | 49 |

#### CHAPTER 1

#### INTRODUCTION

Computers speak a language of bits, bytes, and registers. Man is more fluent with sketches, words, graphs, tables and digits. Each member of this unlikely pair, man and computer, can be indispensable to the solving of a problem at hand. Man is needed for his creative intuition and judgement. The computer is unmatched in its raw speed, its ability to remember large quantities of data, and in its willingness to perform simple repetitive tasks. In situations which require talents from both of the above categories, the interactive video graphics terminal provides a natural man-computer interface. Its usefulness is as an interpreter in the dialogue between man and machine. The development of this role has led to a wide range of computer graphics applications in fields ranging from engineering design to mathematical analysis to business data processing.

#### I. 1 Cathode Ray Tubes

At the heart of modern interactive graphics terminals, is the cathode ray tube (CRT). A CRT is large pear shaped tube which has been pumped free of air and closed off. At the narrow neck end of the tube there is an electron gun from which a continuous beam of electrons may be caused to emanate. At the other end of a tube there is a phosphorus display screen onto which the electron beam is focused. As electrons hit the screen and for a time afterwards, the phosphor glows and a spot of light is seen. The colour of this light depends on the type of phosphor used. The electron beam is focused onto any point on the screen through the application of the proper 'horizontal deflection' and 'vertical deflection' analogue input signals. A third input signal controls the intensity of the beam and thus, indirectly, the intensity of the resulting screen dot. The range of this control includes the situation where the electron gun is turned off and there is no electron beam.

Interactive graphics terminals exchange information with a user on the one hand, and a 'host' computer on the other. Much of the information which is received from the user is passed on to the host computer. Information received from the host computer is translated, by the graphics terminal, into corresponding CRT beam control input signals. These signals, in turn, cause a visual image to be generated on the face of the CRT screen. In this way, the user and host computer communicate indirectly via the visual display.

Since phosphor glows for only a short time after the termination of an electron bombardment, CRT images are transient and need to be regenerated regularly in order to obtain a steady and coherent picture. The so called refresh rate is usually 30-60 Hz, depending on the type of phosphor used. Refresh rates which are too low cause an annoying 'flicker' whereby the display is noticeably discontinuous in time.

### I. 2 Controlling CRT Displays

Two distinctive methods for generating and manipulating CRT displays have evolved. There are, accordingly, two general types of interactive graphics terminals, the directed beam terminals and the raster scan terminals. With directed beam terminals, digital display data is converted into analogue waveforms which are used to drive the

horizontal deflection and vertical deflection inputs of the CRT. As a result, the electron beam is directed, under program control, about the display screen. By controlling when the electron beam is on and when it is off, continuous or discontinuous outlines of display images are traced onto the screen. The approach yields good line quality.

With directed beam refresh terminals, the flicker problem ultimately results in an upper limit to the amount of information which can be displayed. The display must be simple enough that it can be completely generated in the time between two successive screen refreshes. High speed, but expensive, vector generators can be used to raise the image complexity limit.

Alternatively, some directed beam terminals use storage tubes which, unlike conventional CRT's, do not require that the image be refreshed. While this strategy eliminates flicker problems, storage tubes are expensive, inherently less bright, and wear out much more quickly than refresh CRT's. A further disadvantage is that the entire screen must be erased in order to delete any part of the picture.

With raster scan terminals, the screen is treated as a rectangular mesh of defineable dot positions. For example, a screen may be characterized by a matrix of 500 x 600 discrete positions. A graphics display is composed of the complete set of defineable dots, each of which is either bright or dark according to the specifications of a bit map. This bit map is maintained in an internal memory and is such that each bit in the map corresponds to a single screen position. During each screen refresh, the contents of the bit map are mapped onto the screen. Since the bit map is commonly maintained in random access read/write memory, the image can be selectively modified by simply

changing the contents of the bit map.

The words 'raster scan' refer to the manner in which the information contained in the bit map is mapped onto the display screen. The term, raster, refers to the complete set of horizontal lines defined by the discrete screen positions. Each raster line consists of a separate row of screen dots. At the start of each screen refresh, a new scan of the raster is begun. Starting with the electron beam focused on the top leftmost screen position, the beam is automatically made to scan through each raster line, in turn, from left to right. Upon reaching the end of each line, the leftmost dot of the next line down is selected as the starting position for the next horizontal scan. Upon reaching the bottom line, the beam is once again directed to the top raster line in preparation for the next screen refresh.

As the raster is scanned, the corresponding bits in the bit map are accessed, in sequence, and used as ON/OFF input signals for the electron gun. During the course of a complete raster scan, each bit in the bit map is accessed exactly once and used momentarily as the electron gun ON/OFF input signal. For each bit, this occurs at the precise moment that the electron gun is focused at the bit's corresponding screen position. In this manner, the information contained in the bit map is transformed into the graphics display.

For a time, the directed beam storage-tube terminals represented the only choice in relatively low cost graphics terminals. Memory prices rendered raster scan graphics impractical. With the advent of high density, inexpensive semiconductor memories, however, raster scan graphics terminals have become an economically attractive, alternative, low-cost terminal. The more expensive refresh directed beam terminals remain uniquely useful in situations which require high speed and good line quality.

## I. 3 Design Proposal

This report presents the design of a raster scan graphics terminal. In this design, commercially available LSI chips and, in particular, microprocessors are used to control the terminal. The graphics processing is distributed amongst two microprocessors which execute in parallel. A microprocessor can be thought of as a programmable logic device which can be made to synthesize any sequence of individual logic devices. In effect, it corresponds to the CPU of a digital computer. The term, microprocessor, usually refers to a single chip CPU although it can be extended to include 'bit-sliced' CPU's which consist of several LSI chips.

The control program of a microprocessor is stored in a separate memory. It is this program which gives the microprocessor its distinct personality. Since the control program is usually stored in Read Only Memory (ROM), it is thought of as being more 'firm' than regular software. Hence, it is commonly referred to as the control firmware.

The advantages of microprocessor-based design are several. Rather than design special purpose and, in comparison, inflexible hardware, many terminal control functions are easily programmed. The resulting firmware can be of a very general nature. Sophisticated, host independent capabilities can be programmed into the terminal without any accompanying increase in hardware complexity. Furthermore, future additions to the firmware are fairly readily accommodated. As more 'intelligence'

is built into the terminal, the burden on both the user and the host computer is reduced. Finally, the reduction in the number of discrete integrated circuits, results in low cost, low maintenance and high reliability.

A price for these benefits is paid for in processing speed. Hardwired logic can be made to operate faster than programmed logic. This compromise in speed provides the principle motivation for incorporating two microprocessors into the design. By distributing the graphics processing among two microprocessors rather than one, the terminal performance is significantly enhanced. The objective is the design of a capable raster scan graphics terminal which is able to keep pace with modern host-terminal transmission rates. These rates may be as high as 9600 baud (960 characters per second). This means that the terminal must be able to process incoming characters at the average rate of one character every millisecond.

In the proposed design, control is divided between the 'main' microprocessor, an Intel 8086, and a subservient graphics controller which consists of a bit-sliced AM 2903/2910 special purpose microprocessor. The main microprocessor supervises the hardware interfaces with the user, host computer, display hardware and graphics controller. It sends graphic commands to the high speed graphics controller whenever the contents of the bit map are to be altered. The configuration is felt to represent an efficient balance between simplicity and speed.

The graphics controller has been referred to as a 'bit-sliced' microprocessor. The precise meaning of this terminology shall be made clear in chapter 3. For the moment, it suffices to mention two prominent

aspects of the bit-sliced technology. Firstly, the bit-sliced approach enables the design of a highly specialized CPU specifically equipped for the task at hand. Secondly, bit-sliced microprocessors are microprogrammable. Microprogramming can be thought of as a level of programmable control below that provided by machine language. It is, in effect, the programming of the control unit of a CPU. It is inherently more complicated than regular machine language programming although, as a reward, the efficient use of microprogramming techniques can lead to further increases in speed.

In this report, the design is presented in general architectural terms rather than from a detailed circuitry point of view. A discussion of overall terminal design is followed by a more detailed look at the microprogrammable graphics controller. Finally, algorithms which provide basic graphics capabilities are developed.

### CHAPTER 2

#### BASIC DESIGN

The hardware architecture of the video graphics terminal is shown in figure 2.1. Control firmware stored in the local memory is referred to as the operating system. It is executed by the main microprocessor (Intel 8086). Programmable control also resides in a separate control store contained in the bit-sliced graphics controller. The two programmable processors are able to execute in parallel. They provide for the basic flexibility of this design.

At any one time, the video display is entirely defined by the digital information contained in both the text memory and graphics bit map. The two separate memories are characteristic of the dual graphic and text roles of which the terminal is capable. The bit map defines the graphic image as described earlier. The text memory enables the terminal to act as a conventional alphanumeric terminal as well. The contents of the text memory are mapped onto the screen as characters. This is accomplished through the use of a character generator. Each alphanumeric character can be thought of as consisting of a rectangular matrix of dots. Each matrix is identical in size, depending only on character height and width. These matrix patterns are stored in the character generator and are accessed simply by providing the appropriate addresses.

In a typical application, the user's dialogue with the host computer is stored in the text memory while the graphic commands are

Fig. 2.1: The Video Graphics Terminal

sent to the graphics controller where they are transformed into graphics output to be stored in the bit map. The two independent text and graphics memories allow maximum user flexibility. Via the keyboard, the user may request that the contents of both memories be displayed simultaneously.Alternatively, either of the text or graphics displays may be viewed singly. At any moment, the user's dialogue with the host may be recalled to the screen for viewing or temporarily dismissed while the graphical display is studied.

#### II. 1 Five Concurrent Processes

The normal terminal operation can be understood in terms of five concurrent processes. The dialogue process enables communication between user, terminal and host computer to take place. The text definition and graphics definition processes are responsible for depositing information into the text memory and bit map respectively. The text display and graphics display processes are concerned with mapping this information onto the CRT display screen at the proper refresh rate.

Each of the five processes involves the operating system in some manner. The graphics and text display processes are interrupt driven. Each time a new frame needs to be displayed, the operating system is interrupted and the display process serviced. This is accomplished by sending the appropriate starting values to the graphics and text address generators. Both display processes then proceed under automatic hardware control. The operating system is free to resume its own processing. There are, however, important limitations to this freedom which will be discussed later. The 'background' or interrupt-enabled processing, consists of either the text definition or graphics definition process.

The dialogue process is also interrupt driven. The host computer communications interface issues data transmit and receive interrupts to the operating system. The dialogue process services these interrupts. The keyboard and other slow input devices which interface with the user, are conveniently polled at frame interrupt time, and therefore, do not require separate interrupts. It should be noted that part of the graphics display process is under control of the bit-sliced graphics controller and is independent of the operating system. Each of the five concurrent processes will now be described in detail. For these descriptions, the reader should refer to figure 2.1.

### II. 1.1 Dialogue Process

The dialogue process resides in the operating system. It receives input in the form of ASCII characters from the user via the keyboard. If a received character does not correspond to a local command, it is passed onto the host computer where it is interpreted by mainframe software. The host computer replies in accordance with its interpretation by returning more encoded ASCII characters. These characters are received and stored in a character receive buffer in local memory which acts as an interface between the dialogue and definition processes. This arrangement can be used to afford the user either direct or indirect control over the display. Local commands can cause ASCII characters to be placed directly in the character receive buffer without their having come from the host computer.

Further dialogue with the user is provided by means of graphical input devices. Devices like the joystick, tracker ball, and mouse may be interfaced with the terminal (NEW). The 'steering' control of these

devices results in corresponding digital x and y coordinate values. Each input device is polled at the 60Hz frame interrupt rate. Every time a new effective x, y screen position is read, a request is issued to the graphical display process to change the position of the small cross or graphics cursor on the screen. Visual feedback enables the user to position the graphics cursor at any addressable point on the screen. Proper use of this feature greatly enhances the interaction between terminal and user. Among other functions, the user is able to specify lines through the use of endpoint positioning.

Notice the use made by the dialogue process of the 60Hz frame interrupt rate. The regularity of this interrupt makes it an effective real time clock. As such, it is frequently very useful in controlling the several 'rates' which are maintained by the operating system. The text cursor 'wink', automatic key repeat, keyboard polling, and text scrolling, are among some of the functions which require a real time clock.

### II. 1.2 Text Definition Process

While the dialogue process is filling up the character receive buffer, the text definition and graphics definition processes are busy emptying it. Control of the text definition process also resides in the operating system. The characters which are passed to it are written in ASCII form into the text memory. At any one time, several screenfuls of alphanumeric text are stored in the text memory. Paging, scrolling and text cursor motion are accomplished by changing the first word address of the text display. General text editing capabilities may also be provided.

There are occasions where it is useful to write nonstandard text characters onto the screen. Although the standard ASCII character bit patterns are stored in ROM and can't be altered, the character generator also includes some RAM memory. This provision enables nonstandard character sets to be downloaded from the host computer.

#### II. 1.3 Graphics Definition Process

The graphics definition process is organized somewhat differently from the text definition process. Although some graphics processing is done by the operating system, most is delegated to the high speed graphics controller. This is necessary in order to handle situations where graphic commands are coming from the host computer at a very high rate. Whereas ASCII characters passed to the text definition process cause only a few text memory accesses, a character received by the graphics definition process may result in the drawing of a vector which requires hundreds of bit map accesses.

Any graphic image may be thought of as being composed of a set of vectors between specified points. From this perspective, a minimal requirement of the graphics controller is the ability to 'draw' vectors which are arbitrarily positioned on the screen. The graphics controller reads in the vector command sent by the operating system and then proceeds to modify the bit map accordingly. Single points are drawn by specifying zero length vectors. The graphics controller must also be able to 'erase' vectors. This is simply a matter of placing zeros in the bit map instead of ones. A complement mode is useful whereby bits in the map are 'flipped' rather than set or erased. This feature requires that the graphics controller be able to read as well as write to the bit map. In many instances, it is desirable to include alphanumeric text as an integral part of the graphic display. For example, labels to diagrams must remain fixed with respect to the display. Regular text from the text memory is scrolled past the graphic display in the conventional manner of alphanumeric terminals. It is clear that the character bit patterns must be written directly into the display bit map. A convenient arrangement involves translating the bit patterns into graphical commands capable of being accepted by the graphics controller. This is accomplished by the operating system which reads the bit patterns from the character generator, translates them into a series of vector instructions, and sends these to the graphics controller. The operating system can also perform effective scale, rotating and slanting operations on the characters.

Up until now, the discussion has focused on the depositing of the proper display information into the text and graphics memories. Now, attention is shifted to getting information out of storage and onto the screen. Once every 1/60 sec,two processes are activated, whereby, the contents of both storage memories are simultaneously mapped onto the CRT screen.

#### II. 1.4 Text Display Process

The text display process will be described first. At the beginning of each screen refresh, the operating system sends the first word address of the text display to the text address generator. In hardware terms, the address generator simply consists of a few counting registers and some control logic. It provides the contiguous sequences of text memory addresses which correspond to the rows of text. As an example, consider ASCII characters represented in the character generator as 16 by 8 dot matrices. Each matrix row is stored as a separate byte. The 8 bit ASCII character codes stored in the text memory are used as addresses to the corresponding character patterns. In order to fully specify a row within a character pattern, a four bit quantity must also be provided. Together, the four bit character row count and ASCII character code constitute a presentable character generator address.

Imagine that the CRT screen is wide enough to accommodate exactly 80 characters in a row of text. At screen refresh time, the character row count is set to zero just as the electron beam is about to begin a horizontal trajectory along the top raster line of the terminal screen. The first word address of the text display is interpreted as the address of the text memory byte which corresponds to the leftmost character of the top text row to be displayed.

As the electron beam sweeps across the screen, the first raster line is displayed by generating a sequence of 80 contiguous text memory addresses. This sequence begins with the first word address. The result is a sequence of 80 ASCII character codes being presented, in combination with the zero valued character row count, as addresses to the character generator. The outputs of the character generator are just the topmost rows of the specified 80 characters matrix bit patterns. These bytes are loaded in sequence into the shift register and clocked out at video rate as a serialized bit stream to the electron gun.

Upon reaching the end of its horizontal trajectory, the electron

beam is shut off and swung quickly back (horizontal flyback) into position for the display of the next raster line. The next raster line is displayed by incrementing the character row count by one and generating the exact same sequence of text memory addresses. This process is continued until all 16 raster lines of the first row of text have been displayed. At this time, the row count is reset to zero and the first word address is incremented by 80. It now corresponds to the first character of the next row of text. When a complete screenful of text has been displayed, the electron beam is repositioned (vertical flyback) so as to be ready for the next complete raster.

### II. 1.5 Graphics Display Process

The graphics display process is organized in a similar way. At the beginning of a screen refresh, the first word address is sent to the graphics address generator. The graphics bit map is row-ordered so that the raster-scan motion of the electron beam corresponds to traversing through contiguous words in the bit map. As a result, the graphics display process consists simply of the production, by the graphics address generator, of contiguous memory addresses. The bit map is read at appropriate intervals and the output is clocked at video rate to form a second serial bit stream to the electron gun.

The two resultant bit streams from the text and graphics display processes are subject to the same timing constraint. Both streams must be such that they can be OR"ed together to form a single digital signal representative of both the text and graphics displays. As well, depending on the display mode, either of the bit streams may be

inhibited. In this way, the display can be made to consist entirely of text or entirely of graphics. Alternatively, text and graphics may appear together on the screen.

#### II. 2 Fully Interlaced Display

Until now, we have assumed that during each screen refresh, all the raster lines are displayed. For television compatibility (HOL), a fully interlaced display may be implemented instead. This requires that during any screen refresh, only half the raster lines are displayed. Consider raster lines to be numbered from the top to the bottom of the screen. A fully interlaced display is one which is characterized by alternate display frames of only the evenly numbered lines and only the oddly numbered lines.

The implementation of a fully interlaced display has implications for both the text and graphics display processes. For example, the character row count in the text process is incremented by two during each horizontal flyback instead of by one as before. During the vertical flyback it is initialized according to the next frame type as either zero or one. Perhaps the most significant implications, however, has to do with the graphics display process. The simplest way to accommodate a fully interlaced display is to split the bit map into two. One contains the information for the even raster frames and the other, the information for the odd raster frames. The organization of both bit maps is still row-ordered. Depending on whether an even or odd frame is to be displayed next, the starting graphics display address is the first word address of either the even or odd bit maps.

#### II. 3 Hardcopy Dump

A sixth process may be discerned from the operation of the graphics terminal. It is different from the others in that it is only infrequently activated at the user's command. This process has to do with providing the user with a hardcopy of the graphic image. The simplest way to provide this capability is to enable the operating system to read the bit map directly. The dual port bit map memory shown in figure one affords this access. When a graphics hardcopy is desired, the bit map is read by the operating system and sent to the hardcopy plotter.

Until recently, a problem with this approach has been the relatively small address space of available microprocessors. Typically, they could address up to only 64 K bytes. The bit map alone may easily require 40 K 8 bit bytes. This would leave minimal space for the operating system and separate text memory. Use of the recently introduced Intel 8086 is one method of eliminating this problem (MOR). It has an addressing capability of 1 M byte.

### II. 4 Process Coupling

Earlier, passing comment was made on limitations to the independence of the display and definition processes. This point is now addressed. The six processes which have been discussed, are coupled with one another by virtue of their shared resources. The integrity of their operation must be carefully guarded by properly ensuring mutual exclusion (HAN). A single resource must not be assigned to more than one process at the same time.

The text definition and text display processes both share access to the text memory and character generator. Conflict resolution logic is required to prevent memory from being simultaneously accessed. A simple solution is to inhibit the main microprocessor from bus access except during horizontal and vertical flybacks. With the Intel 8086, external bus access is stopped by driving the 'hold' pin high. Simple analysis reveals that this restriction on operating system processing does not prevent the terminal from operating effectively.

For example, consider the terminal specifications which are presented in table 2.1. A host-terminal transmission rate of 9600 baud requires that the terminal be able to process one character every millisecond. In the processing of a single character by the operating system, the dialogue process receives it. The text definition process writes it into text memory or interprets it as a text command of some sort. Alternatively, if passed to the graphics definition process, it is 'interpreted', and as a result, information is usually sent to the graphics controller. This processing must last, on average, no longer than one millisecond.

One millisecond corresponds to the time required to display approximately 15 raster lines. With the operating system processing restricted to horizontal and vertical flybacks, the actual operating system processing time is only 225 usec. This corresponds to approximately 625 Intel 8086 instructions which should be more than enough to accomplish the processing required.

# TABLE 2.1

# TYPICAL VIDEO GRAPHICS TERMINAL SPECIFICATIONS

| Resolution                | 480  | x   | 650 | dots |      |

|---------------------------|------|-----|-----|------|------|

| Frame Interrupts          |      | 60  | Hz  |      |      |

| Fully Interlaced Display  |      |     |     |      |      |

| Horizontal Electron       | Beam | Sca | n   | 53   | usec |

| Horizontal Flyback        |      |     |     | 15   | usec |

| Vertical Flyback          |      |     |     | 280  | usec |

| Average Execution Time of |      |     |     |      |      |

| Intel 8086 Instruc        | tion |     |     | •36  | usec |

Objective 9600 Baud (960 char/sec) Host-terminal transmission rate or approximately 1 character every msec A necessary provision is, of course, that the graphics controller is fast enough. New information can only be sent to the graphics controller if it is ready to accept it. The performance of the graphics controller will be discussed after the bit-sliced design has been looked at in detail. It suffices to say at this point, that a basic rationale for the graphics controller is its parallel operation with the text and graphic display processes as well as with the operating system. Unlike the operating system, it continues to operate during the horizontal raster line time.

To realize this parallelism, special contention logic is required to administer the sharing of another resource, namely, the graphics bit map. A flag protocol is used to resolve conflicts between the graphics controller and graphics display process. The graphics display process raises a hardware flag whenever it requires access to the bit map. After the access, the flag is lowered until the need arises again. The graphics controller must consult this flag before every bit map access. If it is raised, it simply waits for it to be lowered before proceeding. The flag is raised by the display process some time in advance of the actual access. This provides the graphics controller with the time to finish any access of its own, which was begun before the flag was raised.

A third process interested in accessing the bit map is the graphics hardcopy display process. When a hardcopy plot is being made, the graphics definition and graphics display processes are suspended. The operating system does this by disabling the visual display and secondly, by refusing to send any further commands to the graphics

controller. Eventually, the graphics controller, after having finished with its last received command, rests in an idle loop. It sets a hardware idle flag in order to communicate this idle condition to the operating system. The operating system then initiates the bit map dump. Since both display processes are disabled, it proceeds without competition.

It should be pointed out that the graphics hardcopy display process corresponds to one of only two situations where the operating system accesses the bit map directly. In both cases the protocol is to disable the visual display and the graphic definition processes. If this were not the case, further hardware logic would be required to resolve conflicts between the graphics controller and operating system. The other instance where the bit map is accessed by the operating system, is during the clearing of the graphic display. The operating system does this by loading zeros directly into the bit map.

Further process coupling involves the dialogue and both definition processes. They all share the use of the character receive buffer. Since the dialogue process is interrupt driven, the contention logic is simple. It consists in momentarily disabling interrupts at appropriate places in the definition processes.

### II.5 Modularity

As mentioned earlier, the terminal has dual text and graphics roles. It is possible to split the hardware design along these lines. The dotted lines in figure 2.1 outline the various units which provide the terminal with graphics capabilities. These may be incorporated into a single functional unit. Essentially, the final product becomes

two. A conventional alphanumeric terminal which, when interfaced properly with the separate graphics unit, becomes a full fledged graphics terminal.

This flexibility is characteristic of the modular design approach. With this approach, a design is broken into relatively independent functional units or modules. The overall design problem is then reduced to the proper interfacing of these modular units. The details of each module's design are then faced separately. In the light of this design concept, it is now appropriate to focus attention on the graphics controller. It is this module which comprises the heart of the graphics unit. We have discussed its purpose within the context of the overall design. Now, it is time to look inside the black box.

#### CHAPTER 3

### THE GRAPHICS CONTROLLER

The graphics controller is designed as a bipolar microprogrammable bit-sliced microprocessor. Compared with single-chip MOS microprocessors, the bit-sliced bipolar approach represents a fundamentally different philosophical direction. The current limitations, associated with bipolar technologies, on chip complexity, pin numbers, and chip size, dictate that the CPU be implemented on a multichip basis. This is realized by splitting the CPU and implementing the control and processing units on separate chips. The processing section or arithmetic logic unit (ALU) is itself dispersed over several chips. The manner of this dispersion is understood by imagining a single ALU which is vertically sliced into identical 'bit-slices'. These slices operate in parallel and may be cascaded to any width which is a multiple of the basic slice. The basic slice is usually only two or four bits wide. Although inherently less reliable, the use of more chips is justified with the increased performance and flexibility.

Hardware flexibility arises from the fact that the designer essentially builds his own customized CPU. The chips can be configured to provide a wide variety of digital system architectures. Unconventional word lengths can be provided by simply stacking the desired number of bit-sliced ALU chips together. As well, there is the programming flexibility which is inherent in the use of a microprogrammable control unit. The designer may define the system's

instruction set by a program (microprogram) stored in ROM. The microinstructions which constitute the microprogram, provide for a very low level control over the hardware resources. As such, they can be used to implement a very efficient graphical instruction set.

For our purposes, advantage is taken of this flexibility in order to design a special purpose processor. The processor instruction set is an atypical set designed for the express purpose of manipulating the bit map. Many of these instructions are relatively high level and correspond to hundreds of microinstructions. The graphics instructions are not fetched from a central memory in the manner of a conventional CPU but are received from the main microprocessor. In order to see how the graphics controller is realized, it is necessary to first introduce some fundamental concepts in microprogramming.

## III. 1 Microprogramming

The central processing unit of a computer can be logically divided into a control unit and an execution network as shown in figure 3.1. The current instruction is contained in the instruction register (IR). In general, it requires several clock cycles to execute, depending on the particular instruction. The control unit decodes the instruction and as a result, emits control signals or commands to the execution network. A new set of commands is issued at every clock cycle. More precisely, at each cycle, the control unit sends a set of 'boolean' signals which defines the behaviour of the components of the execution network for the duration of that cycle. This boolean command vector can be regarded as a word, the command word.

Fig. 3.1: The central processing unit of a computer can be logically divided into a control unit and an execution network (BOU).

Conditional instructions require information concerning the current status of the execution network. Such information is generally called the condition code (CC). It may, for example, consist of the value of a carry, the sign of the last result, or of an overflow status. This information is maintained by the execution network and made available to the control unit at appropriate moments.

After the current instruction has been executed, the control unit issues a sequence of command words which cause the next instruction to be placed in the instruction register. This sequence of command words corresponds to what is referred to as the fetch cycle. It is followed by an execute cycle whereby the instruction is executed. This alternate sequence of fetch and execute cycles continues for as long as the CPU is in operation. It should be stressed that each fetch and execute cycle consists of several clock cycles.

In the course of executing an instruction, the control unit is solely responsible for presenting the correct sequence of command words to the execution network. Consequently, the control unit must maintain a number of internal 'status bits' so as to keep track of the state of its own processing. The form of these status bits depends on the particular design of the control unit itself. At each clock cycle, the control unit must therefore perform two operations. It must generate a command word and update its internal status bits.

Traditionally, there have been two approaches to the realization of a suitable control unit. One method consists of using random hardwired logic to generate each control word at every clock cycle. The second method is the microprogrammed solution. Command words are stored

in a memory called the control store. At each clock cycle, a new command word is available from memory and sent to the execution network. The internal status bits now correspond to the specification of the next command word to be used.

A single word contained in the control store is called a microinstruction. It consists not only of the command word, but, as well, of the second set of boolean commands which are used to update the internal designation of the next microinstruction. Whereas, at each clock cycle, the command word is sent to the execution network, the next microinstruction command vector is sent to the next - microinstruction - logic of the control unit itself.

Just as regular computer instructions can be combined to form a program, so a logically coherent sequence of microinstructions is called a microprogram. The terms, instruction, fetch and execute, are now prefixed with 'macro' to distinguish them from the micro-fetch and micro-execute cycles associated with the execution of each microinstruction. The execution of each macroinstruction normally corresponds to the execution of a single associated microprogram.

Each microinstruction is logically divided into component fields. Each field corresponds to a functionally independent set of boolean commands. It can consist of varying numbers of bits. For example, the carry control, ALU function control, and next microinstruction address control, may be three separate microinstruction fields.

## III. 2 Basic Architecture

Figure 3.2 shows the basic design of the graphics controller. The figure is divided into the control unit and the ALU. The ALU

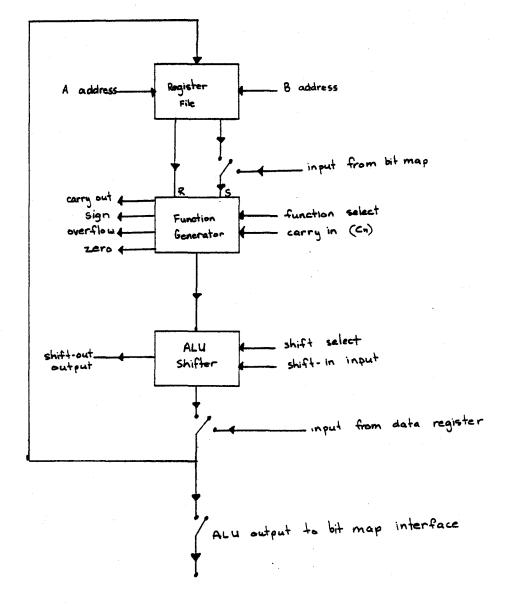

Fig. 3.2 : The Graphics Controller

consists of four 4 bit wide ALU chips (AM2903's) cascaded together to form a 16 bit processor. The AM2903 contains 16 internal working registers. This working space is increased through the addition of extra RAM (AM29705) and PROM (AM29751) bit-sliced register files. The final ALU contains 32 RAM and 16 PROM registers.

At each clock cycle, a new microinstruction is latched from the control store into what is called a 'pipeline register'. The contents of this register provide control inputs to the sequence controller (AM2910), the ALU, the bit map interface, and the data bus interface. In terms of the previous discussion, the latter three components constitute the execution network. The sequence controller is the next microinstruction - logic of the control unit.

The execution network maintains arithmetic status information in the status register. This information, together with other various hardware I/O flags, constitutes the information from which the condition code is selected. It is available to the control unit through the condition code multiplexor.

The macroinstructions sent from the main microprocessor, include both an operation code (opcode), and several 16 bit words of data. The opcode is deposited in the instruction register while the data are sent to the data register. The mapping prom maps the contents of the instruction register into a starting microprogram address. During each macro-fetch cycle, this starting address is accepted by the sequence controller as the next microinstruction address. The instruction data are then read, under microprogram control, into the internal

register file. A 'handshaking' I/O protocol ensures that the opcode and data are received properly.

The pipeline register enables a time-saving technique known as 'pipelining'. With this technique, the next microinstruction is fetched at the same time that the current microinstruction is executed. By definition, the pipeline register always contains the microinstruction which is currently being executed. The contents of this register must remain fixed for the entire clock cycle. They define the current state of the execution network. While the contents of the pipeline register remain fixed, the next microinstruction can be fetched from the control store without affecting the integrity of the currently executing microinstruction.

This parallelism is one way of maximising the clocking frequency. In effect, there are two parallel processing paths. The first path involves the fetching of the next microinstruction. Boolean commands are sent from the control store to the sequence controller. These commands, in combination with the condition code input, cause the address of the next microinstruction to be presented to the control store. The corresponding memory word is fetched and set-up at the inputs to the pipeline register. This must all be accomplished during one clock cycle.

The second processing path is through the execution network. Control signals sent to the ALU cause arithmetical or logical operations to be performed on operands which are brought into the ALU from the data bus, bit map or the internal registers. After the results have stabilized, the contents of the status register are updated. The clocking period of the control unit and execution network must be at

least as long as the duration of the longest of the two parallel processing paths. Typically, for the AM2900 LSI series, the clock period is in the neighbourhood of 130 nsec.

Pipelining has a further implication. The status register is updated at the end of an execution network process path. However, its contents are required as input to the condition code multiplexor early in the fetching of the next microinstruction. This means that the condition code available to the control unit always corresponds to a previous state of the execution network. As a consequence, a microprogram branch, which is conditional on the results of the current microinstruction, cannot be specified until the next microinstruction.

### III. 3 <u>Microinstruction Fields</u>

The graphics controller microinstruction contains four types of fields. These fields are concerned with the sequence controller, the ALU, the data bus interface, and the bit map interface, respectively. In the following discussion, each of these components will be discussed in more detail. As the discussion proceeds, the associated control fields will be defined. The result of this discussion is the specification of the complete set of microinstructions available for firmware control of the graphics controller.

For further details regarding the AMD (Advanced Micro Devices, Inc.) devices which are presented in the following discussion, the reader is referred to the appropriate technical specifications issued by AMD (AMD), (MIC).

## III. 3.1 Sequence Controller

Figure 3.3 shows the block diagram of the AM2910 sequence controller. It operates according to signals received at the I input pins. During the execution of each microinstruction, the sequence controller presents the address of the next microinstruction to the control store. This address comes from one of four sources. The usual source is the microprogram counter register (UPC). In the graphics controller configuration, this register always contains an address one greater than the previous address. This provides for sequential access to the control store.

A second address source is the external input (D). For our purposes, this address ultimately comes from either the mapping prom output or from a part of the pipeline register. The sequence controller selects one of these two input sources by issuing either a mapping prom enable signal ( $\overline{\text{MAP}}$ ) or a pipeline enable signal ( $\overline{\text{PL}}$ ). If these output signals control tri-state output enables, for both input sources, then the D input pins can be driven directly, by both sources, without further contention logic. Note that the mapping prom and pipeline register must never both be enabled at the same time.

Input from the mapping prom signals the start of a new macroexecute cycle. It designates the start of the microprogram which executes the associated graphical instruction. Address input from the pipeline, on the other hand, affords a convenient branching capability. In this case, the microinstruction itself, contains the next microinstruction address.

Fig. 3.3: The AM 2910 Microprogram Controller

,

| HEX   |          |                       | REG/<br>CNTR  | CCEN = LC | FAIL<br>DW and CC = HIGH | CCEN = HI | PASS<br>GH or CC = LOW | REG/   |        |

|-------|----------|-----------------------|---------------|-----------|--------------------------|-----------|------------------------|--------|--------|

| 13-10 | MNEMONIC | NAME                  | CON-<br>TENTS | Y         | STACK                    | Y         | STACK                  | CNTR   | ENABLE |

| 0     | JZ       | JUMP ZERO             | ×             | 0         | CLEAR                    | 0         | CLEAR                  | HOLD   | PL     |

| 1     | CJS      | COND JSB PL           | X             | PC        | HOLD                     | D         | PUSH                   | HOLD   | PL     |

| 2     | JMAP     | JUMP MAP              | X             | D         | HOLD                     | D         | HOLD                   | HOLD   | MAP    |

| 3     | CJP      | COND JUMP PL          | x             | PC        | HOLD                     | D         | HOLD                   | HOLD   | PL     |

| 4     | PUSH     | PUSH/COND LD CNTR     | X             | PC        | PUSH                     | PC        | PUSH                   | Note 1 | PL     |

| 5     | JSRP     | COND JSB R/PL         | X             | R         | PUSH                     | D         | PUSH                   | HOLD   | PL     |

| 6     | CJV      | COND JUMP VECTOR      | x             | PC        | HOLD                     | D         | HOLD                   | HOLD   | VECT   |

| 7     | JRP      | COND JUMP R/PL        | X             | R         | HOLD                     | D         | HOLD                   | HOLD   | PL     |

| 8     | RFCT     |                       | ≠0            | F         | HOLD                     | F         | HOLD                   | DEC    | PL.    |

| 0     | RFCI -   | REPEAT LOOP, CNTR ≠ 0 | <b>⇒</b> 0    | PC        | РОР                      | PC        | POP                    | HOLD   | PL.    |

| 9     | RPCT     |                       | ≠0            | D         | HOLD                     | D         | HOLD                   | DEC    | PL     |

| Э     | nrci     | REPEAT PL, CNTR ≠ 0   | = 0           | PC        | HOLD                     | PC        | HOLD                   | HOLD   | PL     |

| A     | CRTN     | COND RTN              | X             | PC        | HOLD                     | F         | POP                    | HOLD   | PL     |

| В     | CJPP     | COND JUMP PL & POP    | x             | PC        | HOLD                     | D         | POP                    | HOLD   | PL     |

| С     | LDCT     | LD CNTR & CONTINUE    | ×             | PC        | HOLD                     | PC        | HOLD                   | LOAD   | PL     |

| D     | LOOP     | TEST END LOOP         | x             | F         | HOLD                     | PC        | POP                    | HOLD   | PL     |

| E     | CONT     | CONTINUE              | x             | PC        | HOLD                     | PC        | HOLD                   | HOLD   | PL     |

| F     | тwв      | THREE-WAY BRANCH      | ≠0            | F         | HOLD                     | PC        | POP                    | DEC    | PL     |

| F     |          | INCE-WAT BRANCH       | = 0           | D         | POP                      | PC        | POP                    | HOLD   | PL     |

Note 1: If  $\overrightarrow{CCEN}$  = LOW and  $\overrightarrow{CC}$  = HIGH, hold; else load. X = Don't Care

TABLE 3.1: AM2910 INSTRUCTION SET

ω

A third address source is the register/counter (R). It is preloaded via the D input from the pipeline register. The five deep last-in first-out stack (F) is the fourth source. The stack provides for microsubroutine return linkages and looping capabilities. Microsubroutines may be nested up to five levels deep.

The register/counter R can also be made to act as a loop counter. It can be loaded from the D input and decremented each time through a loop. When its contents become equal to zero, the loop terminates. The arrangement is such that if it is preloaded with a number N and subsequently used as a loop termination counter, the loop will be executed N+1 times.

Table 3.1 presents the AM2910 instruction set. Many of these instructions are conditional. The input signal  $\overline{CC}$  is used as the test criterion. A low signal corresponds to a pass. Further flexibility is provided by the  $\overline{CCEN}$  input, which enables the conditional testing. When this signal is high,  $\overline{CC}$  is ignored and the sequence controller operates as though the result of the condition test were a pass. The vector address enable signal (VECT) allows a third external source to drive the D input. This capability is not utilized in the graphics controller design. As a result, the CJV instruction in table 3.1 is never used.

The microinstruction fields which control the operation of the AM2910 are shown in table 3.2 and are described below. AM2910 Instruction - Controls operation of AM2910. Mnemonics correspond to those of table 3.1.

## TABLE 3.2

# CONTROL SEQUENCER FIELDS

| AM 2910<br>Instruction<br><u>4 Bits</u> | Condition<br>Code Enable<br>1 Bit | Force Test<br>Polarity<br>1 Bit | Conditio<br>Code<br>3 Bits | nc              | Pipeline<br>Data<br>12 Bits |

|-----------------------------------------|-----------------------------------|---------------------------------|----------------------------|-----------------|-----------------------------|

| JZ                                      | CD                                | NEG                             | С                          | Carry out       |                             |

| CJS                                     | UCD                               | POS                             | OVR                        | Overflow        |                             |

| JMAP                                    |                                   |                                 | Z                          | Zero            | 12 Bit                      |

| CJP                                     |                                   |                                 | S                          | Sign            | Data                        |

| PUSH                                    |                                   |                                 | SO                         | Shift Out       | Item                        |

| JSRP                                    |                                   |                                 | IRF                        | IR Full         | -<br>                       |

| CJV                                     |                                   |                                 | DRF                        | DR Full         |                             |

| JRP                                     |                                   |                                 | MPF                        | Bit Map<br>Free |                             |

| RFCT                                    |                                   |                                 |                            |                 |                             |

| RPCT                                    |                                   |                                 |                            |                 |                             |

| CRTN                                    |                                   |                                 |                            | •               |                             |

| CJPP                                    |                                   |                                 |                            |                 |                             |

| LDCT                                    |                                   |                                 |                            |                 |                             |

| LOOP                                    |                                   |                                 |                            |                 |                             |

| CONT                                    |                                   | CD                              |                            | + f a a 1       |                             |

| TWB                                     |                                   | UCD<br>NEG<br>POS               |                            |                 |                             |

Force Test Polarity - Provides the polarity select signal in figure 3.2. The input to the polarity control is either flipped (NEG) or passed to the AM2910 CC input unchanged (POS.).

Condition Code - Selects the condition code input from one of the eight condition code multiplexor inputs. The selected signal is subsequently passed to the polarity control.

Pipeline Data

The 12 bit pipeline data field which, if enabled, provides an external D input to the AM2910.

With the condition code multiplexor and polarity control shown in figure 3.2, the operation of the AM2910 can be made conditional on the status of the execution network. For example, a nonzero result in the ALU may lead to a branch in the microprogram. This would correspond to the following microinstruction field values.

| AM2910 Instruction | Condition Code | Force Test | Condition | Pipeline          |

|--------------------|----------------|------------|-----------|-------------------|

|                    | Enable         | Polarity   | Code      | Data              |

| CJP                | CD             | NEG        | Z         | Branch<br>Address |

The meaning of the various possible condition code inputs will be explained more fully as the discussion of the execution network proceeds.

## III. 3.2 ALU

The ALU is fashioned from four AM2903 LSI chips. A principle reason for using these chips rather than the less expensive AM2901 chips, is that the internal register file of the AM2903 is easily expanded to virtually any required size. The AM2903 includes the necessary 'hooks' needed to accomplish this. On the other hand, the full range of capabilities available with the AM2903 has not been used in this design. In particular, the AM2903 has built-in floating point logic, which is not required for our purposes.

Figure 3.4 illustrates the functional capabilities of the proposed ALU. The diagram does not correspond to a specific component chip, but represents, instead, the complete ALU assembly. This assembly consists of the bit-sliced AM2903's, AM29751's and AM29705's as well as extra shift control logic. Specific chip assembly details may be found in the AMD literature (AMD).

The extra shift control logic specifies whether a shift operation is cyclic or linear. In any case, the actual shift operation is performed by the AM2903's. The control logic merely controls where the shift-in and shift-out bits come from and go to respectively. For example, in a cyclic shift, the shift-in bit is made equal to the shift-out bit, whereas, in a linear shift, the shift-in bit is driven from the external shift-in input as shown below.

Shift Register Shift-Out Output Cyclic Right Shift Shift-In Input Shift Register Shift-Out Output Right Shift (linear)

The operation of the arithmetic logic unit proceeds as follows. At the beginning of a microinstruction, the A and B addresses are presented to the ALU. As a result, two operands are sent to the function generator. Alternatively the B operand may come from the bit map. Next, an operation, as selected by the function select input, is performed. During the course of this operation, the carry out, sign, overflow and zero status flags are generated. The result is sent to the shifter, where, in like manner, the shifter operates on its input and as well, creates the shift-out output. After the result is stable, it may be written into the register file at the location specified by the B address or it may be sent to the bit map interface. Finally, the status register may be updated with the newly generated status flags. The microprogrammer has the option of inhibiting this update.

It is also possible for input to be accepted directly from the data register (fig. 3.2). In this case, the shifter output is ignored and the contents of the data register is written to the register file instead. Any operation to be performed on the data must wait until the next microinstruction. This situation is in contrast to input from the bit map, which, being presented directly to the function generator, can be read and operated on in the same microinstruction.

In the ALU's operation, the B address has a dual role. It is an operand address in the early part of the microinstruction cycle, and a result destination address in the latter. This constitutes what is known as a two address architecture. A three address architecture, whereby, separate destination and operand addresses are specified, is

also possible with AM2903 chips. However, if implemented, a three address configuration would involve more complex timing logic.

The preceding discussion enables further microinstruction fields to be defined. These are presented in table 3.3. Several of the ALU functions are expressed in terms of Cn, an input which is provided by the carry in field. For the shift control field, the only difference between a 'NOP' and a 'NS' command, is that a NOP does not cause the final result to be written into the register file. All other shift control instructions cause a final write operation. The NOP instruction is useful when the firmware designer wishes to idle the ALU without overwriting any of the data in the register file.

The enable status load field offers the firmware designer direct control over the updating of the status register. This feature can lead to a reduction in the number of microinstructions needed to accomplish a conditional operation. For example, consider the case of a microprogram 'jump' which is performed only if the value of a specific variable is zero. If the status register were automatically loaded at the end of every microinstruction, the variable in question would have to pass through the function generator during the clock cycle which immediately preceeds the execution of the conditional jump. In many instances, an extra microinstruction would be required for this purpose alone. If, on the other hand, the variable had been defined several microinstructions back, and the status load disabled ever since, then, the further microinstruction would not be required.

Notice that the input/output fields are classified as belonging to either the data bus or bit map interfaces. The interface

|             |                  | A      | LU Fields         |                   |                   |                          | Data Bus<br>Interface     | Bit Map<br>Interface     |                      |

|-------------|------------------|--------|-------------------|-------------------|-------------------|--------------------------|---------------------------|--------------------------|----------------------|

| Function    | Carry<br>In (Cn) | Shift  | Shift-In<br>Input | A<br>Addr.<br>(R) | B<br>Addr.<br>(S) | Enable<br>Status<br>Load | Data Reg.<br>Input Enable | Bit Map To<br>ALU Enable | ALU<br>Output Enable |

| 4 bits      | l bit            | 3 bits | 1 bit             | 6 bits            | 6 bits            | l bit                    | l bit                     | l bit                    | 1 bit                |

| HIGH        | 0                | CRS    | 0                 |                   |                   | E                        | E                         | E                        | E                    |

| S-R-1+Cn    | Ĩ                | RS     | 1                 |                   |                   | DIS                      | DIS                       | DIS                      | DIS                  |

| R-S-1+Cn    |                  | NOP    |                   |                   |                   |                          |                           |                          |                      |

| R+S+Cn      |                  | NS     |                   |                   |                   |                          |                           |                          |                      |

| S+Cn        |                  | CLS    |                   |                   |                   |                          |                           |                          |                      |

| S+Cn        |                  | LS     |                   |                   |                   |                          |                           |                          |                      |

| R+Cn        |                  |        |                   |                   |                   |                          |                           |                          |                      |

| R+Cn        |                  |        |                   |                   |                   |                          |                           |                          |                      |

| LOW         |                  |        |                   |                   |                   |                          |                           |                          |                      |

| <b>R</b> ∧S |                  |        |                   |                   |                   |                          |                           |                          |                      |

| R₩S         |                  |        |                   |                   |                   |                          | c right shift             |                          |                      |

| R₩S         |                  |        |                   |                   | RS<br>NOP         | : right<br>: no op       |                           |                          |                      |

| RAS         |                  |        |                   |                   | NS                | : no sh                  | ift                       |                          |                      |

| RVS         |                  |        |                   |                   | LS                | : cycli<br>: left :      | c left shift<br>shift     |                          |                      |

| RAS         |                  |        |                   |                   | Ε                 | : enable                 | е                         |                          |                      |

| R∨S         |                  |        |                   |                   | DIS               | : disab                  | le                        |                          |                      |

# TABLE 3.3 : Further microinstruction fields

fields are used rather infrequently in comparison to those of the ALU and sequence controller. Excepting microinstructions which perform I/Ooperations, the contents of these fields do not vary from one microinstruction to the next.

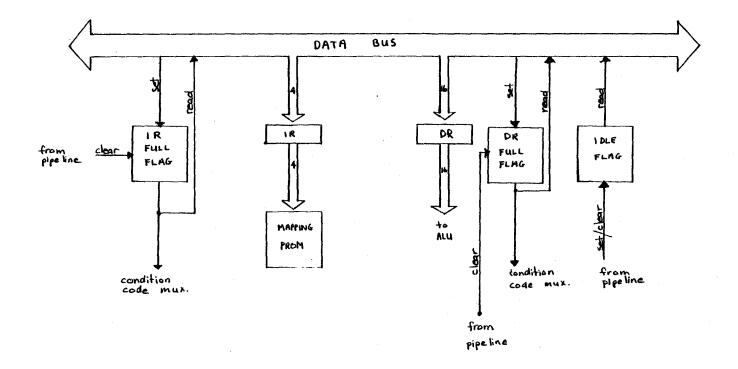

#### III. 3.3 Data Bus Interface

Figure 3.5 shows the data bus interface in more detail. The IR full and DR full, flags are used to establish a 'handshaking' input/output protocol. Using this protocol, the transfer of data from the main microprocessor to the graphics controller, proceeds under program control. For example, consider for the moment, the data path to IR. Before the main microprocessor can deposit a graphics instruction into the IR, it must wait for the graphics controller to clear the IR full flag. This flag is cleared immediately after each new macroinstruction is 'accepted' by the graphics controller. A macroinstruction is accepted by selecting the mapping from output as the next microinstruction address. Similarly, before the graphics controller can accept a new graphics instruction, it must wait for the main microprocessor to set the IR full flag. This flag is set immediately after each new macroinstruction is loaded, by the main microprocessor, into the IR. This protocol protects the integrity of the data transfer. In like manner, the DR full flag is used to regulate the transfer of data to the graphics controller via the data register.

It is clear that in order to establish the I/O protocol properly, provision must be made for microinstructions which are conditional to the value of either of the two I/O flags. Accordingly, both flags are used as inputs to the condition code multiplexor. The

Fig. 3.5 : The Data Bus Interface

£5

# TABLE 3.4

## DATA BUS INTERFACE MICROINSTRUCTION FIELDS

| IR<br>Full Flag | DR<br>Full Flag | Idle<br>Flag | Data Register<br>Input Enable |

|-----------------|-----------------|--------------|-------------------------------|

| 1 Bit           | l Bit           | 1 Bit        | 1 Bit                         |

| CLR             | CLR             | IDLE         | E                             |

| NCL             | NCL             | BSY          | DIS                           |

CLR = Clear IR Full Flag NCL = No Clear E = Enable DIS = Disable BSY = Busy

set conditions correspond to the 'DRF' and 'IRF' condition code field values shown in table 3.2

Another feature of figure 3.5 is the idle flag. This flag is set by the graphics controller whenever it is in an idle state, waiting for further graphics instructions. During this state, the bit map is not accessed by the graphics controller. As discussed in the preceding chapter, the main microprocessor must first test the idle flag before addressing the bit map directly.

The complete set of data bus interface microinstruction fields are shown in table 3.4. Except for I/O operations, these fields have the following fixed values.

| IR Full | DR Full | Idle | Data Register |

|---------|---------|------|---------------|

| Flag    | Flag    | Flag | Input Enable  |

| ,       |         |      |               |

| NCL     | NCL     | BSY  | DIS           |

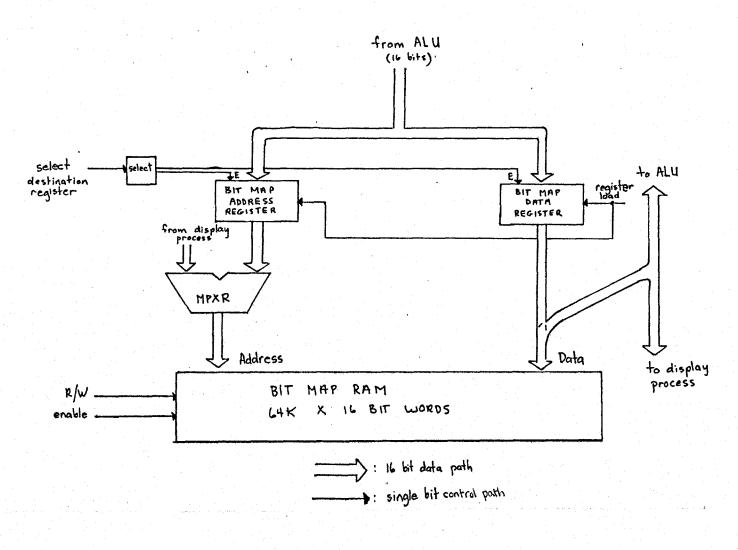

III. 3.4 Bit Map Interface

The final microinstruction fields to be defined are those of the bit map interface. Figure 3.6 shows the bit map interface in more detail. Note that  $2^{20}$  bits may be stored in the 64K by 16 bit word RAM. This is large enough to support a screen resolution of 1024 by 1024 dots. The bit map interface fields are shown in table 3.5 and are defined below.

ALU Output Enable - The enable signal causes data to be sent from the ALU to the bit map interface.

Enable R<sup>e</sup>gister Load - The enable signal causes output from the ALU to be latched into one of the two destination registers. This destination is specified by the field which is defined next.

Fig. 3.6 : The Bit Map Interface

## TABLE 3.5

## BIT MAP INTERFACE MICROINSTRUCTION FIELDS

| ALU<br>Output Enabl | Enable<br>e Register Load | Bit Map<br>Address/Data | RAM<br>Enable | RAM<br>Read/Write | Bit Map to<br>ALU Enable |

|---------------------|---------------------------|-------------------------|---------------|-------------------|--------------------------|

| l Bit               | l Bit                     | 1 Bit                   | 1 Bit         | l Bit             | l Bit                    |

| E                   | E                         | ADD                     | E             | R                 | E                        |

| DIS                 | DIS                       | DAT                     | DIS           | W                 | DIS                      |

D = Disable

E = Enable

ADD = Address register

DAT = Data register

R = Read

W = Write

Bit Map address or data - This field specifies the destination of

output from the ALU as being either the bit map data register or the bit map address register. When the graphics controller performs bit map read/write operations, these registers drive the corresponding address and data lines of the bit map RAM. It is important to note that these registers are local to the graphics controller. The graphics display process uses its own separate address and data registers.

- RAM Enable - Enables or disables the RAM read/write operations.

- RAM Read/Write - Specifies whether a read or a write operation is to be performed by the bit map RAM. Note that depending upon the particular read/ write access times of the RAM chosen for the bit map, read/write operations may require several microinstruction cycles to complete. In this case, RAM enable and read/write signals must be held fixed over several microinstructions.

- The enable signal causes bit map output available at the RAM data lines to be accepted as input to the ALU.

Bit Map to ALU Enable

Except for I/O operations, the bit map interface fields have the following default values.

| ALU           | Enable        | Bit Map      | RAM RAM   |   | Bit Map to |

|---------------|---------------|--------------|-----------|---|------------|

| Output Enable | Register Load | Address/Data | Enable Re |   | ALU Enable |

| X             | DIS           | X            | DIS       | x | DIS        |

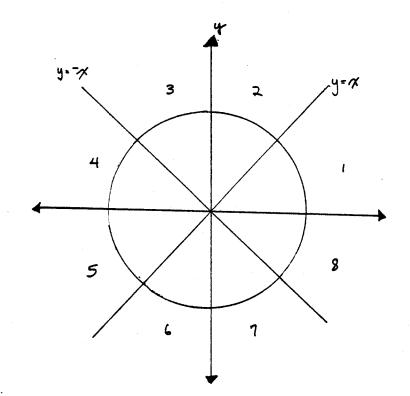

where X = don't care