# NEW ALGORITHMS AND ARCHITECTURES FOR POST-SILICON VALIDATION

# NEW ALGORITHMS AND ARCHITECTURES FOR POST-SILICON VALIDATION

BY HO FAI KO, B.Eng. & Mgt., M.A.Sc. APRIL 2009

# A THESIS SUBMITTED TO THE SCHOOL OF GRADUATE STUDIES IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE DOCTOR OF PHILOSOPHY

McMaster University

© Copyright 2009 by Ho Fai Ko

All Rights Reserved

#### DOCTOR OF PHILOSOPHY (2009) (Electrical and Computer Engineering)

McMaster University Hamilton, Ontario, Canada

TITLE:

New Algorithms and Architectures for Post-Silicon Vali-

dation

AUTHOR:

Ho Fai Ko, B.Eng. & Mgt., M.A.Sc. (Electrical and

Computer Engineering, McMaster University, Canada)

SUPERVISOR:

Dr. Nicola Nicolici

NUMBER OF PAGES: xvii, 170

### Abstract

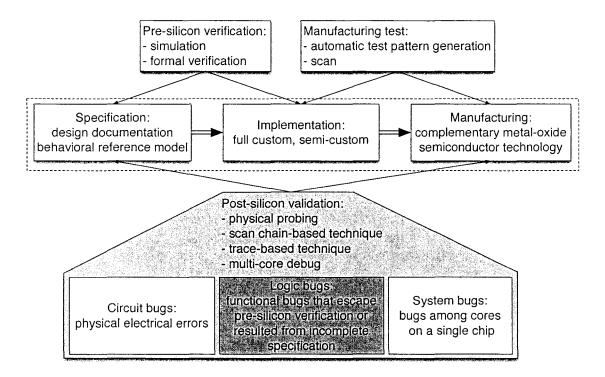

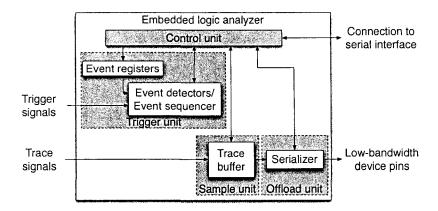

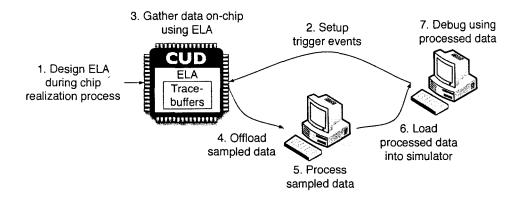

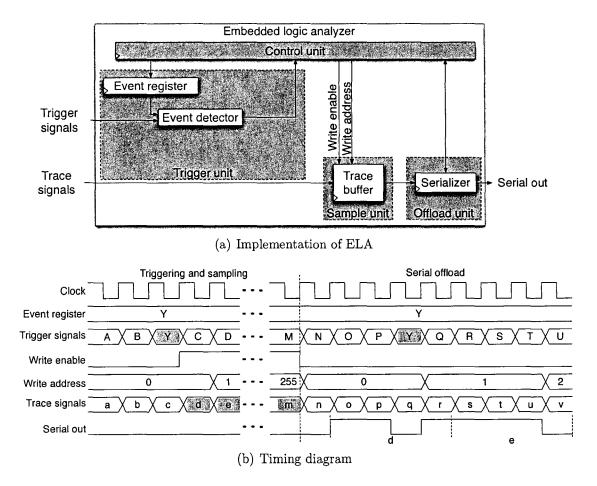

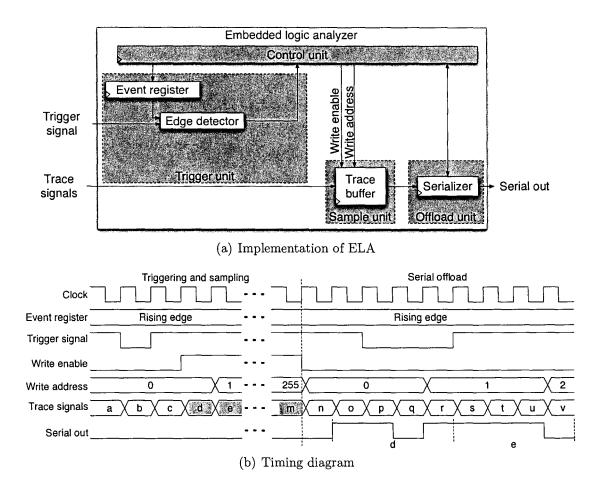

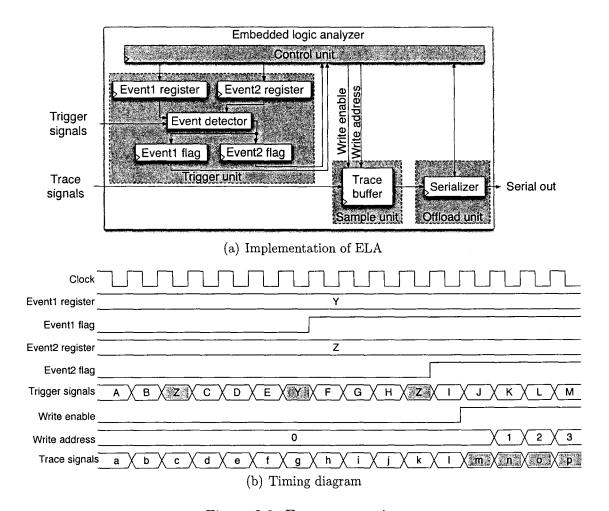

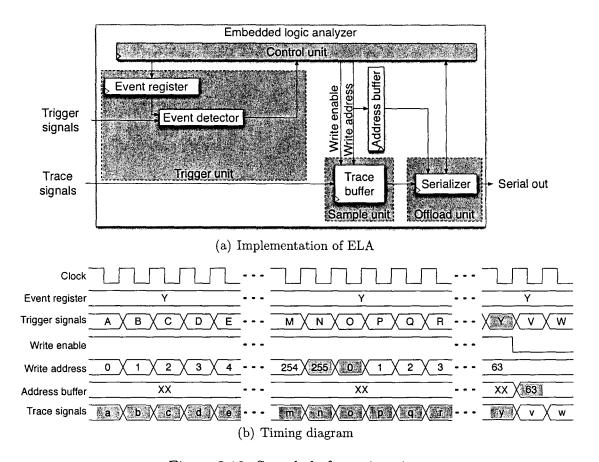

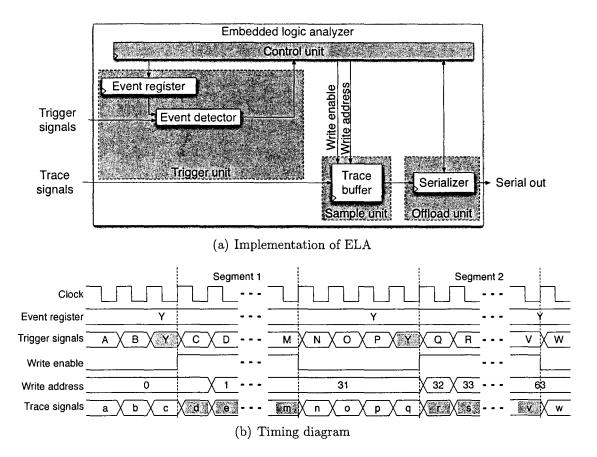

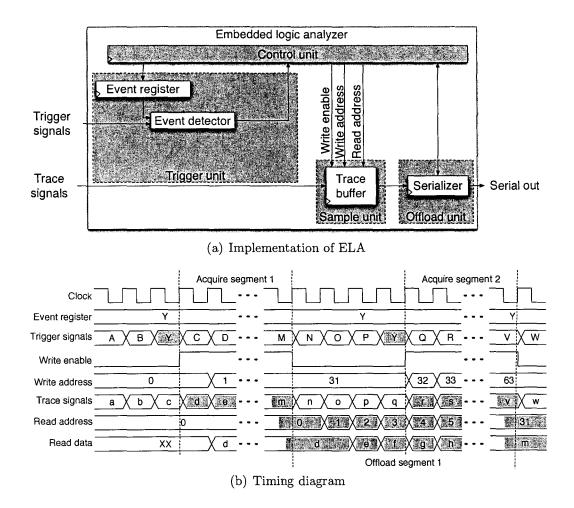

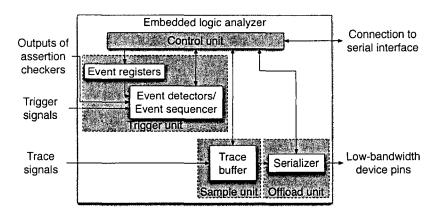

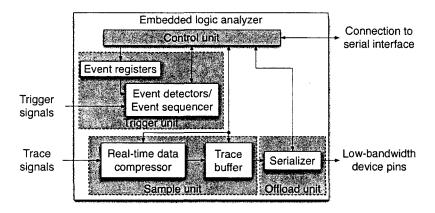

To identify design errors that escape pre-silicon verification, post-silicon validation is becoming an important step in the implementation flow of digital integrated circuits. While many debug problems are tackled on testers, there are hard-to-find design errors that are activated only in-system. A key challenge during in-system debugging is to acquire data from internal circuit's nodes in real-time. In this thesis, we propose several techniques to address this problem, ranging from resource-efficient and programmable trigger units to automated selection of trace signals to a distributed architecture for embedded logic analysis.

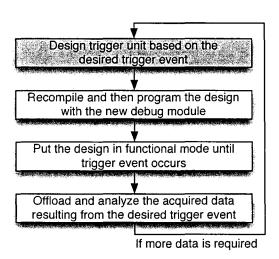

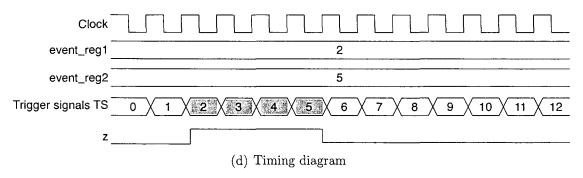

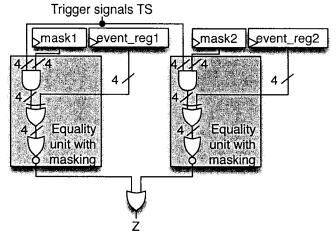

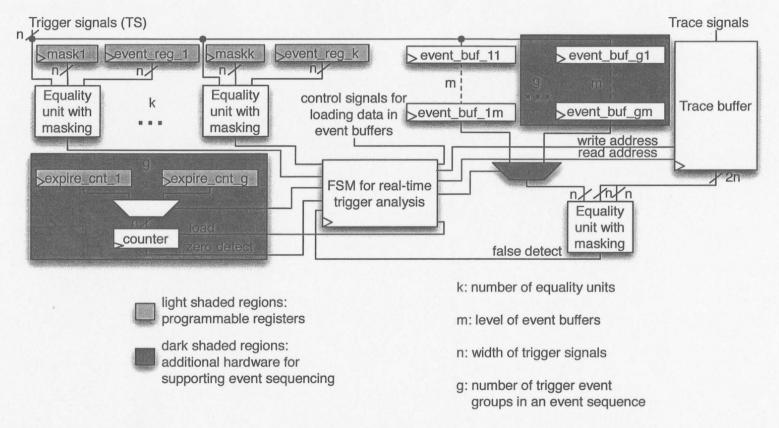

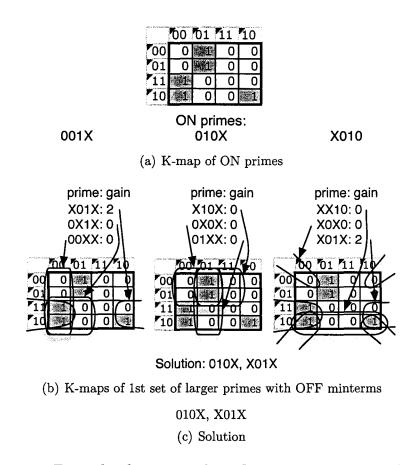

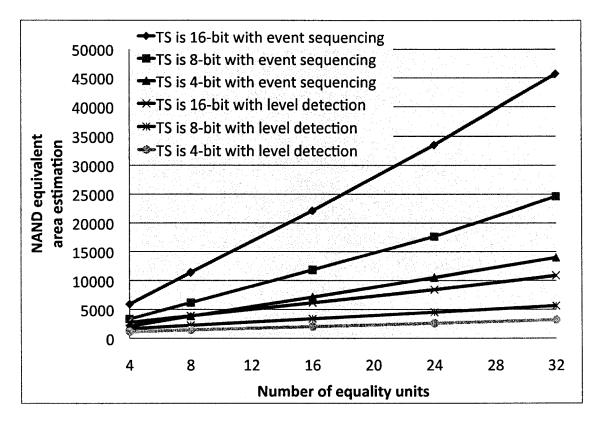

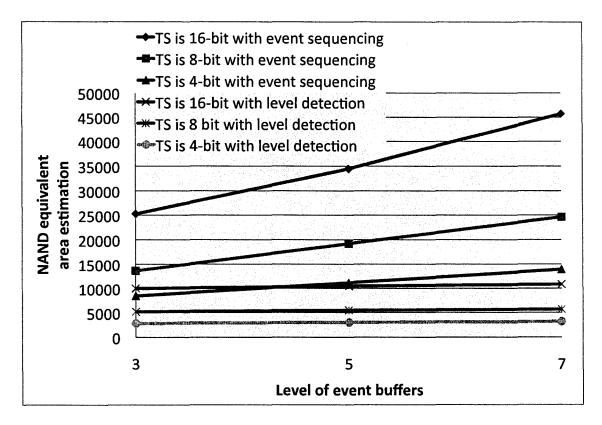

Deciding when to acquire data on-chip is done using trigger units. Because there is an inherent tradeoff between the size of the trigger units and the types of events that can be programmed into them, we first explore a resource-efficient and programmable trigger unit implementation. We show how the on-chip buffers used for data acquisition can be leveraged to store information regarding the logic functions that are programmed at runtime as the trigger events. This reduces the requirement in terms of logic resources for the trigger unit, while enlarging the set of programmable trigger events supported by these resources. We also propose a new algorithm to automatically map trigger events onto the proposed trigger unit.

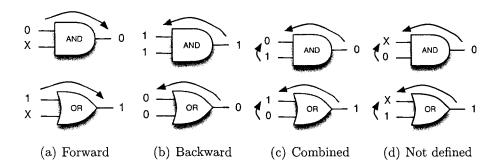

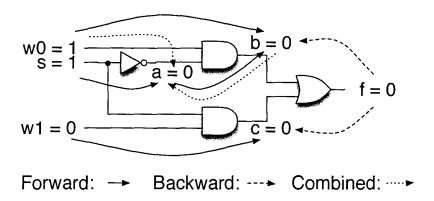

Next we shift the focus from the trigger units to the sample units available onchip. Once the real-time debug experiment has been completed, the amount of data available to the user is limited by the capacity of the on-chip trace buffers. For logic bugs, where the circuit implementation matches the physical prototype, we show how the structural information from the circuit netlist can be leveraged to expand the amount of data made available off-line to the user. To ensure that data expansion can scale as the amount of debug data that is acquired increases, we propose a fast algorithm that leverages the bitwise parallelism of logic operations available in the instruction set of microprocessors. In a follow-up chapter, we also discuss how trace signals can be automatically selected in order to improve the amount of data that can be restored off-line. To achieve this objective, we propose two new metrics and two new algorithms for automatically identifying the circuit nodes which, if traced, will aid data expansion for the neighboring nodes in the circuit.

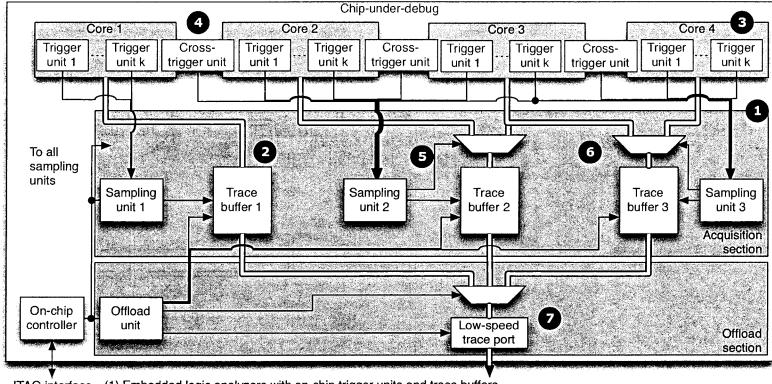

The last contribution of this thesis is concerned with managing multiple trace buffers in complex designs with many logic blocks. We propose a new distributed embedded logic analysis architecture that can dynamically allocate the trace buffers at runtime based on the needs for debug data acquisition coming from multiple logic blocks. We also leverage the real-time offload capability through high-speed trace ports in order to extend the duration of a debug experiment. It is shown how with little investment in on-chip debug logic resources, the length of debug experiments can be expanded for multi-core designs without increasing the number of on-chip trace buffers.

# Acknowledgments

Over the course of my doctoral studies, I always thought I was the person who had the influence over the people around me. However, what I did not realize was that, in fact, the people around me had also influenced the way my personality was developed over the past five years.

I would like to first give my gratitude to my parents, my brother Chris, and my sister Eska. Their generous patience had provided me the best shelter whenever I lost confidence in myself. Although it has been a long time since the five of us sat together as a family, each of us knows that we are always connected in our hearts, and we support each other in every way.

Secondly, I would like to express my deepest thanks to my supervisor Dr. Nicola Nicolici. His constant battering gave me the opportunity to learn so much from him both technically, and personally. Although I had doubted myself, he had always stood by me and believed in me to give me the success I have today.

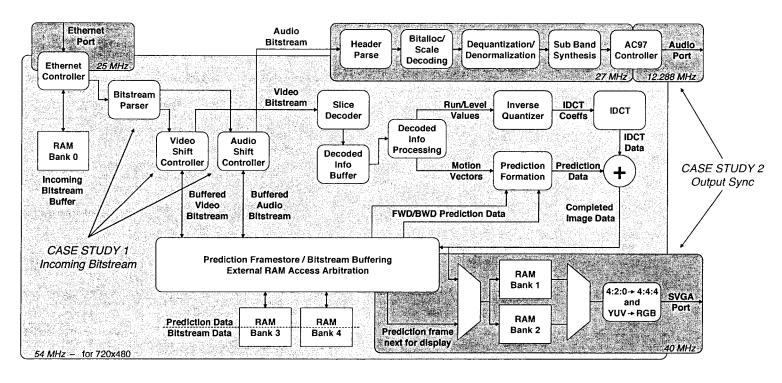

My special thanks also go to not only my colleague, but one of my best friends Adam Kinsman and his family. Their comforting home, delicious meals prepared by Pamela and cheerful laughs from Eric and Robyn provided me the energy whenever I felt like I was running out of battery. I would also like to acknowledge Adam for his effort on developing the MPEG decoder, which was used in the experiments for the work of this thesis.

Drs. Sirouspour and Haddara have been constructive during the supervisory committee meetings and I acknowledge them for their continuous support. My colleagues in the Computer-Aided Design and Test (CADT) Research Group: Johnny Xu, Baihong Fang, David Lemstra, David Leung, Ehab Anis, Kaveh Elizeh, Zaha Lak, Mark

Jobes, Jason Thong and Phil Kinsman have assisted me in so many ways. I would like to thank them for their great company when disasters strike. I would also like to express my gratitude to the graduate students, faculty, administrative and technical members in Department of Electrical and Computer Engineering at McMaster University for their assistance during my study and research.

I would also like to thank all my friends. Their continuous yelling, arguments, opinions and support had pushed me from behind to give me the extra lift I needed.

And last, but the most important person I would like to thank, is Nana. She had given me the happiest days of my life that gave me strength to continue on my studies without me realizing it. She had also taught me what it is like to feel truly appreciated for who I am, but not what I do. I hope that in the future, I can make her feel the same way whenever she is with me.

## List of Abbreviations

ASIC Application Specific Integrated Circuit,

ATE Automatic Test Equipment,

ATPG Automatic Test Pattern Generation,

CAD Computer-Aided Design,

CMOS Complementary Metal-Oxide Semiconductor,

CUD Circuit under Debug,

CUT Circuit under Test,

DA Debug Agent,

DFD Design for Debug,

DFT Design for Testability,

DP Debug Probe,

ELA Embedded Logic Analyzer,

FF Flip-Flop,

FIFO First-In First-Out,

FPGA Field Programmable Gate Array,

FSM Finite State Machine,

HDL Hardware Description Language,

IP Intellectual Property,

K-map Karnaugh Map,

MISR Multiple Input Signature Register,

NOC Network-on-Chip,

OCI On-Chip Instrumentation,

OVL Open Verification Library,

PSL Property Specification Language,

PTE Programmable Trigger Engine,

QBF Quantified Boolean Formulation,

RTL Register Transfer Level,

SFF Scanned Flip-Flop,

SOC System-on-a-Chip,

TDI Test Data In,

TDO Test Data Out,

VLSI Very Large Scale Integration,

# Contents

| A  | ostra                       | ict    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 111 |  |  |

|----|-----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| A  | ckno                        | wledgr | ments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | v   |  |  |

| Li | st of                       | Abbro  | eviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | vii |  |  |

| 1  | Intr                        | oduct  | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   |  |  |

|    | 1.1                         | VLSI   | design flow $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1   |  |  |

|    | 1.2                         | Pre-si | licon verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4   |  |  |

|    | 1.3                         | Manu   | facturing test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5   |  |  |

|    | 1.4                         | Post-s | silicon validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7   |  |  |

|    |                             | 1.4.1  | Circuit bugs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S   |  |  |

|    |                             | 1.4.2  | Logic bugs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Ö   |  |  |

|    |                             | 1.4.3  | System bugs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10  |  |  |

|    |                             | 1.4.4  | Terminology definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10  |  |  |

|    |                             | 1.4.5  | Non-deterministic and deterministic replay experiments $% \left( 1\right) =\left( 1\right) \left( 1\right)$ | 12  |  |  |

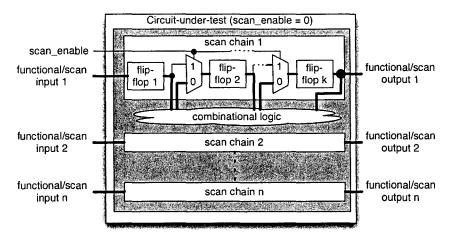

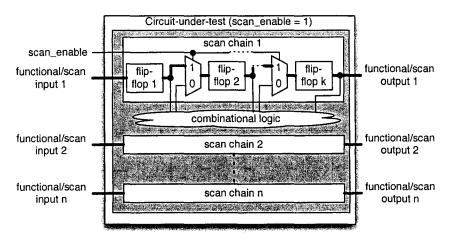

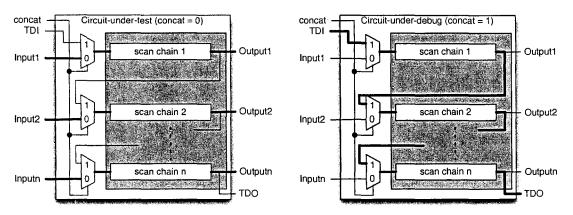

|    |                             | 1.4.6  | Scan chain-based technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12  |  |  |

|    |                             | 1.4.7  | Trace-based technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13  |  |  |