## ON-CHIP DEBUG ARCHITECTURES FOR IMPROVING OBSERVABILITY DURING POST-SILICON VALIDATION

# BY EHAB ALFONS ANIS DAOUD, B.Sc., M.Sc. SEPTEMBER 2008

# A THESIS SUBMITTED TO THE SCHOOL OF GRADUATE STUDIES IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE DOCTOR OF PHILOSOPHY

McMaster University

© Copyright 2008 by Ehab Alfons Anis Daoud

All Rights Reserved

DOCTOR OF PHILOSOPHY (2008)

(Electrical and Computer Engineering)

McMaster University Hamilton, Ontario, Canada

TITLE: On-Chip Debug Architectures for Improving Observabil-

ity during Post-Silicon Validation

AUTHOR: Ehab Alfons Anis Daoud, B.Sc., M.Sc. (Electronics and

Communications Engineering, Cairo University, Egypt)

SUPERVISOR: Dr. Nicola Nicolici

NUMBER OF PAGES: xiv, 139

## Abstract

Post-silicon validation has become an essential step in the design flow of system-onchip devices for the purpose of identifying and fixing design errors that have escaped pre-silicon verification. To address the limited observability of the circuits during post-silicon validation, embedded logic analysis techniques are employed in order to probe the internal circuit nodes at-speed and in real-time. In this dissertation, we propose novel on-chip debug architectures and the associated debug methods, which improve observability during at-speed post-silicon validation.

First, we propose a novel embedded debug architecture that enables real-time lossless data compression in order to extend the observation window of a debug experiment. The proposed architecture is particularly suitable for in-field debugging on application boards that have sources of non-deterministic behavior, such as asynchronous interfaces. To quantify the performance gain from using lossless compression in embedded logic analysis, we present a new compression ratio metric that captures the trade-off between the area overhead and the increase in the observation window.

Second, we propose a novel architecture based on lossy compression. This architecture enables a new debug method where the designer can iteratively zoom only in the intervals that contain erroneous samples. Thus, it is tailored for the identification of the hard-to-detect functional bugs that occur intermittently over a long execution time. When compared to increasing the size of the trace buffer, the proposed architecture has a small impact on silicon area, while significantly reducing the number of debug sessions. The new debug method is applicable to both automatic test equipment-based debugging, as well as in-field debugging on application boards, so long as the debug experiment can be reproduced synchronously.

Third, we address the problem of the presence of blocking bugs in one erroneous module that inhibit the search for bugs in other parts of the chip that process data received from the erroneous module. We propose a novel embedded debug architecture for bypassing blocking bugs. This architecture enables a hierarchical event detection mechanism to provide correct stimuli from an embedded trace buffer, in order to replace the erroneous samples caused by the blocking bugs.

It is anticipated that the main contributions presented in this dissertation will help further the adoption of embedded logic analyzers, as the main alternative to scan chains for gathering data during post-silicon validation in real-time debug environments.

## Acknowledgments

I would like to thank God for giving me the strength, peace, and guidance to complete this work. I believe that all things work together for good to those who love God and all things are possible through God who strengthens me.

I am greatly indebted to my supervisor, Nicola Nicolici, for his research guidance and generous support. I greatly appreciate his enthusiasm, encouragement for high standard applied research, and his depth of knowledge in many research areas that helped me to complete this work. I am very grateful to him for enriching my knowledge with stimulating and fruitful discussions. It was an honour for me to conduct this research under his supervision.

I am grateful to all my colleagues in the computer-aided design and test research group at McMaster University, Qiang Xu, Henry Ko, Adam Kinsman, David Leung, Kaveh Elizeh, Roomi Sahi, Mark Jobes, Zahra Lak and Jason Thong, for their support, stimulating discussions during our group meetings, and for providing a lively working environment. Special thanks to my friends, Amir Gourgy, Michael Botros, Sameh Saad, and all of my friends at Saint Mina Church for their love and support.

I would like to thank the faculty, administrative and technical members in Department of Electrical and Computer Engineering at McMaster University for their assistance during my study and research. Many thanks to Cheryl Gies, Helen Jachna, Terry Greenlay and Cosmin Coroiu for their endless help in many matters.

Finally, I would like to express my sincere gratitude to all my family members for their love and continuous support. Words cannot express my love and great appreciation to my father Alfons, my mother Hoda, my brother Alfred, my sister Eman, my sister-in-law Vivianne, my brother-in-law Emad, my nice Alexandra and my nephew Antoine.

## List of Abbreviations

ABV Assertion-Based Verification

ASIC Application Specific Integrated Circuit

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generation

BIST Built-In Self-Test

CAM Content Addressable Memory

CMOS Complementary Metal Oxide Silicon

CUD Circuit under Debug

CUT Circuit under Test

DFD Design for Debug

DFT Design for Testability

FF Flip-Flop

FIFO First-In First-Out

FPGA Field Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

I/O Input/Output

IC Integrated Circuit

LFSR Linear Feedback Shift Register

LFU Least Frequently Used

LRU Least Recently Used

MISR Multiple Input Signature Register

MTF Move-to-Front

NoC Network-on-Chip PI Primary Input

PO Primary Output

PSL Property Specification Language

RAM Random Access Memory RTL Register Transfer Level

SA Signature Analyzer

SFF Scanned Flip-Flop

SoC System-on-Chip

TPG Test Pattern Generator

VLSI Very Large Scale Integration

WDLZW Word-based Dynamic Lempel-Ziv

## Contents

| A  | bstract               |        |                                            | iii |  |

|----|-----------------------|--------|--------------------------------------------|-----|--|

| A  | ckno                  | wledgr | ments                                      | ī   |  |

| Li | List of Abbreviations |        |                                            | vi  |  |

| 1  | Intr                  | oduct  | ion                                        | 1   |  |

|    | 1.1                   | Design | n Flow of VLSI Circuits                    | 2   |  |

|    |                       | 1.1.1  | Pre-Silicon Verification                   | 4   |  |

|    |                       | 1.1.2  | Manufacturing Test                         | Į.  |  |

|    |                       | 1.1.3  | Post-Silicon Validation                    | 8   |  |

|    | 1.2                   | Disser | tation Motivation                          | 10  |  |

|    | 1.3                   | Disser | rtation Organization and Contributions     | 11  |  |

| 2  | Bac                   | kgrou  | nd and Related Work                        | 13  |  |

|    | 2.1                   | Overv  | iew of Post-silicon Validation             | 13  |  |

|    |                       | 2.1.1  | Debug Environments                         | 14  |  |

|    |                       | 2.1.2  | Post-silicon Validation Techniques         | 15  |  |

|    | 2.2                   | Scan-l | based Observability                        | 15  |  |

|    |                       | 2.2.1  | Scan-based DFT Methodology                 | 16  |  |

|    |                       | 2.2.2  | Scan-based Debug Methodology               | 17  |  |

|    | 2.3                   | Embe   | dded Logic Analysis                        | 23  |  |

|    |                       | 2.3.1  | Basic Principle of Embedded Logic Analysis | 23  |  |

|    |                       | 2.3.2  | Embedded Debug Module Architecture         | 25  |  |

|   |     | 2.3.3   | Embedded Logic Analysis Related Work                  | 27 |

|---|-----|---------|-------------------------------------------------------|----|

|   | 2.4 | Recent  | Advancements in DFD Techniques                        | 29 |

|   |     | 2.4.1   | Assertion-based Debug                                 | 30 |

|   |     | 2.4.2   | Transaction-level Debug                               | 33 |

|   |     | 2.4.3   | Compression in Embedded Logic Analysis                | 34 |

|   | 2.5 | Conclu  | ding Remarks                                          | 38 |

| 3 | Eml | bedded  | Debug Architecture for Lossless Compression           | 40 |

|   | 3.1 | Prelim  | inaries and Summary of Contributions                  | 41 |

|   | 3.2 | Embed   | lded Logic Analysis Framework                         | 42 |

|   |     | 3.2.1   | Lossless Compression Requirements                     | 43 |

|   |     | 3.2.2   | The Proposed Compression Ratio Metric                 | 44 |

|   |     | 3.2.3   | Performance Analysis of Compression Algorithms        | 44 |

|   | 3.3 | The Pr  | roposed Debug Architecture                            | 46 |

|   |     | 3.3.1   | Overview of Embedded Debug Module                     | 46 |

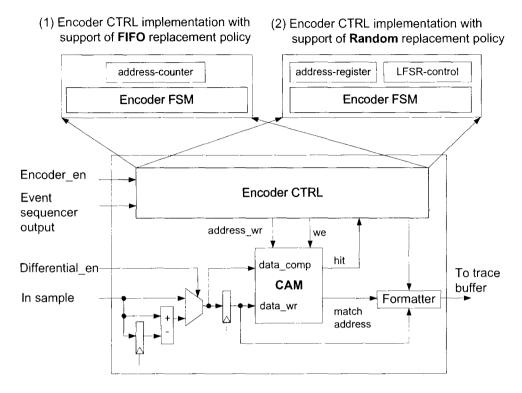

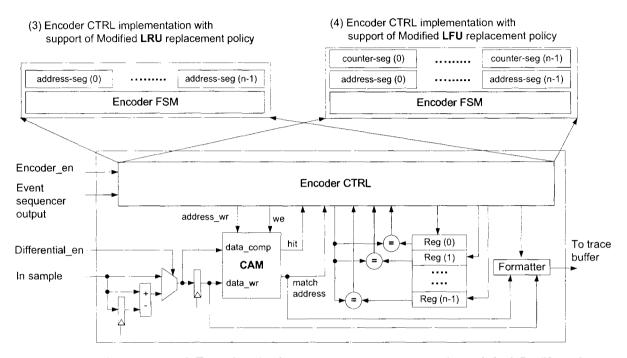

|   |     | 3.3.2   | The Proposed Encoder Architecture                     | 47 |

|   | 3.4 | Diction | nary-based Compression Algorithms                     | 56 |

|   |     | 3.4.1   | BSTW Dictionary-based Compression Algorithm           | 57 |

|   |     | 3.4.2   | MBSTW Dictionary-based Compression Algorithm          | 59 |

|   |     | 3.4.3   | WDLZW Dictionary-based Compression Algorithm          | 60 |

|   | 3.5 | Experi  | mental Results                                        | 62 |

|   |     | 3.5.1   | Area of the Proposed Encoder Architecture             | 62 |

|   |     | 3.5.2   | MP3 Decoder Experiments                               | 65 |

|   | 3.6 | Summa   | ary                                                   | 73 |

| 4 | On  | Extend  | ling the Observation Window through Lossy Compression | 75 |

|   | 4.1 | Prelim  | inaries and Summary of Contributions                  | 76 |

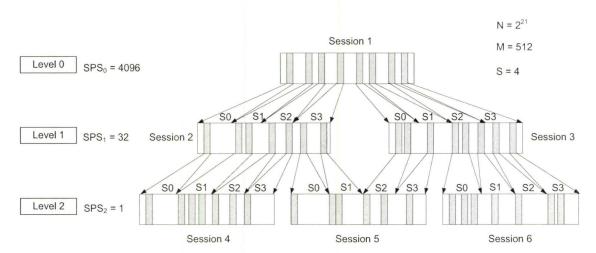

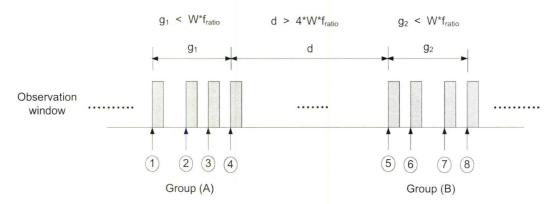

|   | 4.2 | Propos  | sed Iterative Silicon Debug Framework                 | 77 |

|   | 4.3 | Debug   | Architecture for Lossy Compression                    | 80 |

|   |     | 4.3.1   | The Embedded Debug Module                             | 80 |

|   |     | 4.3.2   | Features to Extend the Observation Window             | 82 |

|   | 4.4 | The Pr  | roposed Scheduling Algorithms                         | 87 |

|                       |                            | 4.4.1  | Algorithm for Scheduling Debug Sessions          | 87  |  |

|-----------------------|----------------------------|--------|--------------------------------------------------|-----|--|

|                       |                            | 4.4.2  | Variable Segments Sizes at the Last Debug Level  | 89  |  |

|                       |                            | 4.4.3  | Spatial Compression                              | 90  |  |

|                       |                            | 4.4.4  | Combining Streaming and Compression              | 90  |  |

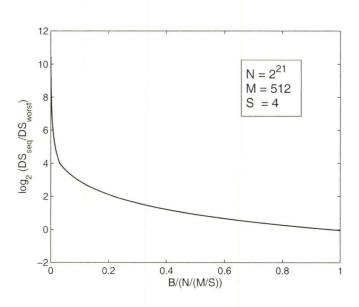

|                       | 4.5                        | Sensit | ivity Analysis                                   | 92  |  |

|                       | 4.6                        | Exper  | imental Results                                  | 94  |  |

|                       |                            | 4.6.1  | Area of the Proposed Debug Module                | 94  |  |

|                       |                            | 4.6.2  | MP3 Decoder Experiments                          | 96  |  |

|                       |                            | 4.6.3  | Random Data Experiments                          | 98  |  |

|                       | 4.7                        | Summ   | ary                                              | 99  |  |

| 5                     | Em                         | bedded | d Debug Architecture for Bypassing Blocking Bugs | 100 |  |

|                       | 5.1                        | Prelin | ninaries and Summary of Contributions            | 101 |  |

|                       | 5.2                        | Metho  | odology for Bypassing Blocking Bugs              | 103 |  |

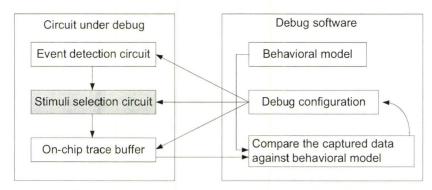

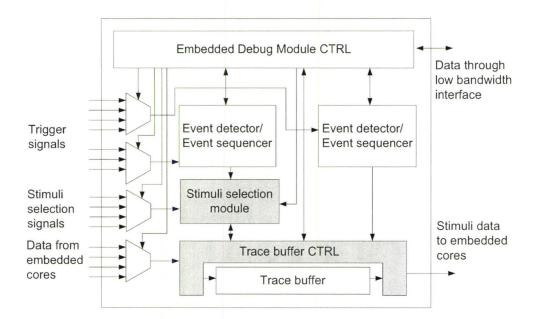

|                       | 5.3                        | Propo  | sed Embedded Debug Module                        | 106 |  |

|                       |                            | 5.3.1  | Overview of the Embedded Debug Module            | 106 |  |

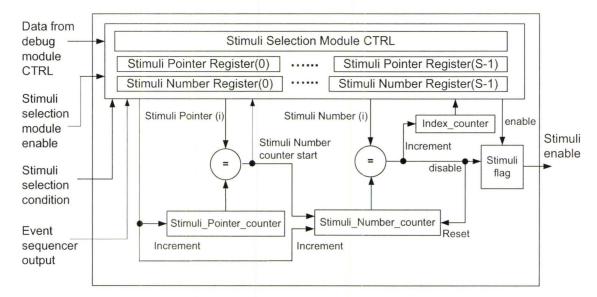

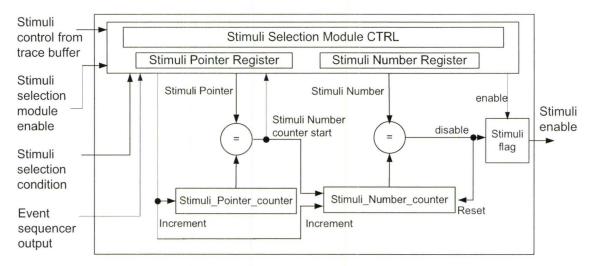

|                       |                            | 5.3.2  | Stimuli Selection Module                         | 107 |  |

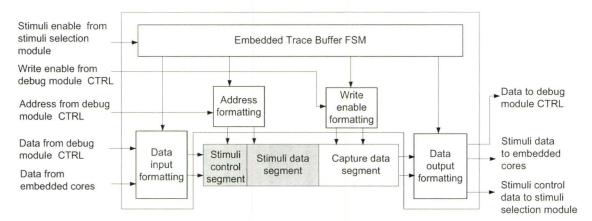

|                       |                            | 5.3.3  | Embedded Trace Buffer Control                    | 110 |  |

|                       | 5.4                        | Exper  | imental Results                                  | 112 |  |

|                       |                            | 5.4.1  | Area of the Proposed Debug Module                | 112 |  |

|                       |                            | 5.4.2  | MP3 Decoder Experiments                          | 113 |  |

|                       | 5.5                        | Summ   | ary                                              | 119 |  |

| 6                     | Conclusion and Future Work |        |                                                  |     |  |

|                       | 6.1                        | Summ   | ary of Dissertation Contributions                | 121 |  |

|                       | 6.2                        | Future | e Research Directions                            | 122 |  |

| $\mathbf{B}^{\sharp}$ | ibliog                     | ranhv  |                                                  | 124 |  |

## List of Tables

| 3.1 | Terminology for the Proposed Encoder Architecture                                                                                                              | 49  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Area of The Proposed Encoder Architecture in NAND2 Equivalents .                                                                                               | 63  |

| 3.3 | Average Compression Ratios of Encoding MP3 Data ( $12 \times 2^{20}$ samples)                                                                                  |     |

|     | at Stereo Decoder Output using BSTW Algorithm, M=16k Bytes                                                                                                     | 67  |

| 3.4 | Average Compression Ratios of Encoding MP3 Data ( $12 \times 2^{20}$ samples)                                                                                  |     |

|     | at Stereo Decoder Output using MBSTW and WDLZW Algorithms,                                                                                                     |     |

|     | M=16k Bytes                                                                                                                                                    | 68  |

| 3.5 | Average Compression Ratios of Encoding MP3 Data ( $12 \times 2^{20}$ samples)                                                                                  |     |

|     | at MDCT Input using BSTW Algorithm, M=16k Bytes                                                                                                                | 69  |

| 3.6 | Average Compression Ratios of Encoding MP3 Data ( $12 \times 2^{20}$ samples)                                                                                  |     |

|     | at MDCT Input using MBSTW and WDLZW Algorithms, M=16k Bytes                                                                                                    | 70  |

| 4.1 | Terminology for the Proposed Embedded Debug Module                                                                                                             | 82  |

| 4.2 | Terminology for the Proposed Debug Method                                                                                                                      | 85  |

| 4.3 | Area of The Embedded Debug Module Architecture in NAND2 Equiv-                                                                                                 |     |

|     | alents                                                                                                                                                         | 95  |

| 4.4 | Reduction in Debug Execution Time $(T_{seq}/T_{prop})$ for the MP3 Data                                                                                        |     |

|     | with $N = 2^{21}$ , $M = 512$ , $S = 4$ , $Ch = 2 \dots \dots$ | 97  |

| 4.5 | Reduction in Debug Execution Time $(T_{seq}/T_{prop})$ versus Error Per-                                                                                       |     |

|     | centage of Random Data for Different Burst Lengths with $N=2^{27}$ ,                                                                                           |     |

|     | $M = 2048, S = 4 \dots \dots$                                  | 99  |

| 5.1 | Area of The Proposed Debug Module in NAND2 Equivalents                                                                                                         | 112 |

## List of Figures

| 1.1  | Design Flow and Verification Techniques of VLSI Circuits        | 3  |

|------|-----------------------------------------------------------------|----|

| 1.2  | Basic Principle of VLSI Circuits Testing                        | 5  |

| 1.3  | Basic Principle of BIST                                         | 6  |

| 1.4  | Deterministic BIST with Multiple Scan Chains Architecture       | 7  |

| 2.1  | A Single Scan Chain Architecture                                | 16 |

| 2.2  | Example of Breakpoint Debug Module                              | 19 |

| 2.3  | Scan-based Debug Architecture [93]                              | 21 |

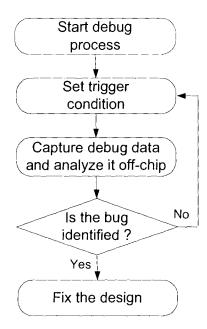

| 2.4  | Debug Flow during Post-silicon Validation                       | 22 |

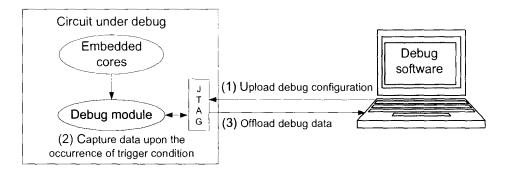

| 2.5  | Debug Framework of Embedded Logic Analysis                      | 24 |

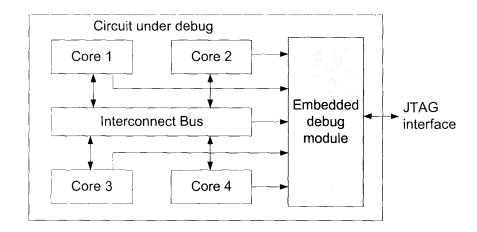

| 2.6  | Circuit under Debug with Centralized Debug Module               | 24 |

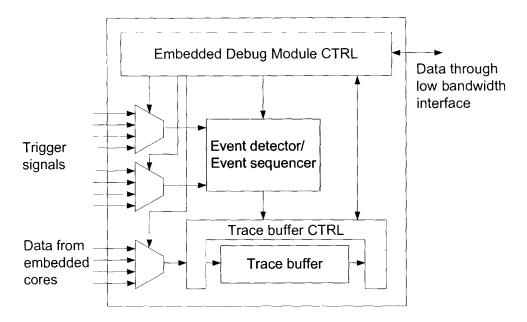

| 2.7  | Embedded Debug Module Architecture                              | 25 |

| 2.8  | Triggering Conditions Flow with Segmented Trace Buffer          | 26 |

| 2.9  | Multi-core Debug Architecture with Centralized Trace Buffer     | 27 |

| 2.10 | Multi-core Debug Architecture with Multiple Trace Buffers       | 28 |

| 2.11 | Basic Principle of Assertion-based Debug                        | 31 |

| 2.12 | Illustrative Example of Assertion                               | 32 |

| 2.13 | Transaction-Based Communication-Centric Debug [42]              | 33 |

| 2.14 | Compression Phases of Real-time Address Trace Compressor $[60]$ | 35 |

| 2.15 | Illustrative Example of State Restoration [67]                  | 38 |

| 3.1  | Embedded Logic Analysis Framework Based on Lossless Compression | 43 |

| 3.2  | The Proposed Embedded Debug Module                              | 47 |

| 3.3 | The Proposed Encoder Architecture with support of FIFO and Ran-            |     |

|-----|----------------------------------------------------------------------------|-----|

|     | dom Replacement Policies                                                   | 48  |

| 3.4 | The Proposed Encoder Architecture with support of Modified LRU             |     |

|     | and Modified LFU Replacement Policies                                      | 51  |

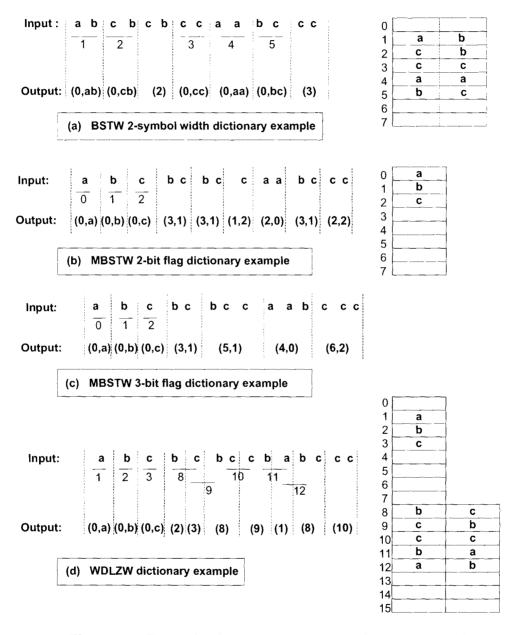

| 3.5 | Illustrative Examples for Dictionary-based Compression Algorithms .        | 58  |

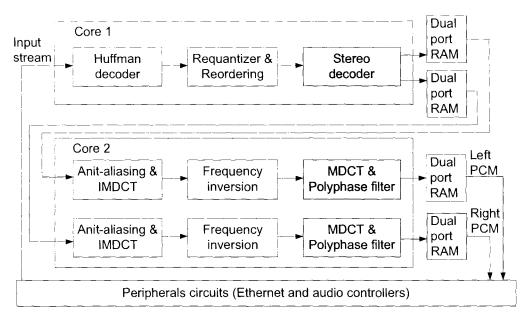

| 3.6 | MP3 Decoder Architecture                                                   | 65  |

| 4.1 | The Iterative Flow of the Silicon Debug Process Based on Compression       |     |

|     | and Cyclic Debugging                                                       | 78  |

| 4.2 | The Proposed Embedded Debug Module Architecture                            | 81  |

| 4.3 | An Iterative Debug Example for the Proposed Iterative Debug Flow           |     |

|     | using Lossy Compression                                                    | 84  |

| 4.4 | Reduction in Debug Sessions versus Failing Intervals                       | 93  |

| 5.1 | Debug Scenarios with and without Bypassing Blocking Bugs Feature           | 102 |

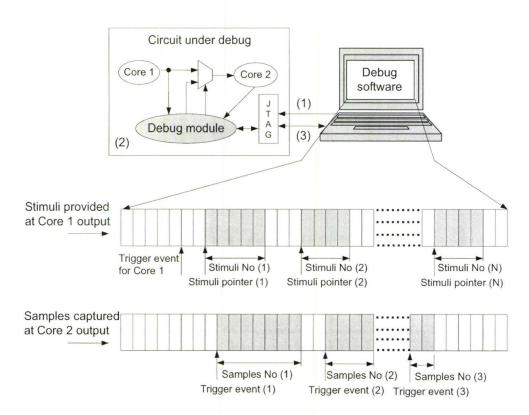

| 5.2 | Bypassing Blocking Bugs Framework                                          | 104 |

| 5.3 | The Proposed Embedded Debug Module                                         | 106 |

| 5.4 | Example of On-chip Stimuli Pointers                                        | 108 |

| 5.5 | Stimuli Selection Module With S Stimuli Control Registers                  | 109 |

| 5.6 | Stimuli Selection Module With Stimuli Control Stored in the Trace          |     |

|     | Buffer                                                                     | 110 |

| 5.7 | Embedded Trace Buffer CTRL                                                 | 111 |

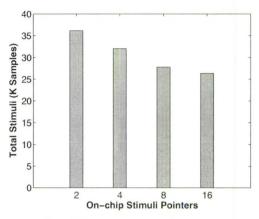

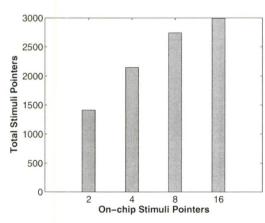

| 5.8 | The Effect of the On-chip Stimuli Pointers on the Total Number of          |     |

|     | Stimuli and on the Total Number of Stimuli Pointers that are used          |     |

|     | during debug the entire Observation Window (Song = $462.38$ k Sam-         |     |

|     | ples, Sample = 2-byte word) $\dots$                                        | 114 |

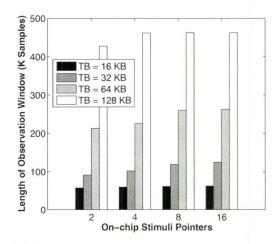

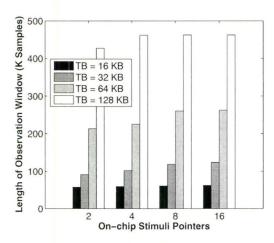

| 5.9 | The Length of the Observation Window (k Samples) versus the On-            |     |

|     | chip Stimuli Pointers for different Sizes of Trace Buffers (k Bytes); Half |     |

|     | of each Trace Buffer Size is used for Capturing Debug Data (Song =         |     |

|     | 462.38 k Samples)                                                          | 115 |

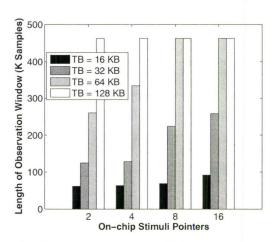

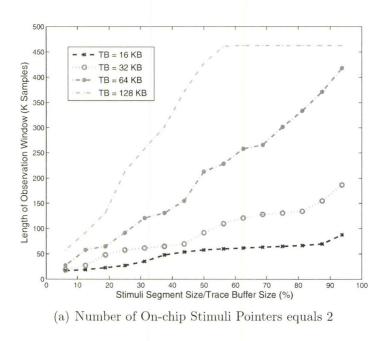

| 5.10 | The Length of the Observation Window (k Samples) versus Stimuli        |     |

|------|------------------------------------------------------------------------|-----|

|      | Segment Size Ratio without using Stimuli Data Streaming, and the       |     |

|      | Number of On-chip Stimuli Pointers equals 2 and 4, respectively (Song  |     |

|      | = 462.38 k Samples)                                                    | 117 |

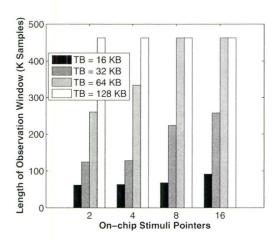

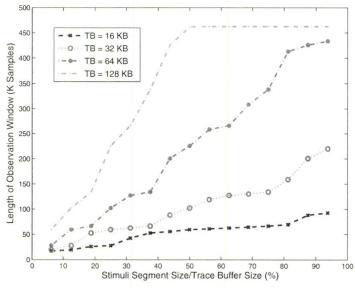

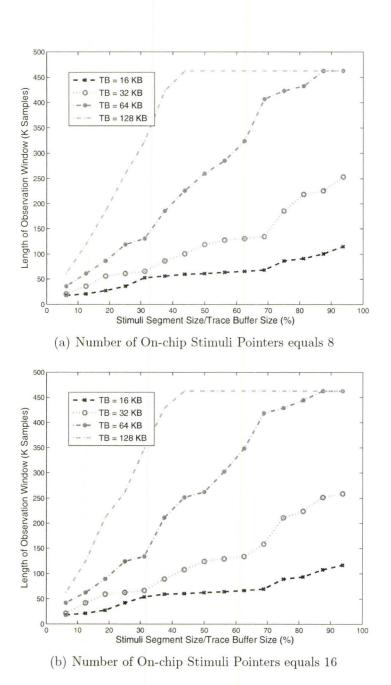

| 5.11 | The Length of the Observation Window (k Samples) versus Stimuli        |     |

|      | Segment Size Ratio without using Stimuli Data Streaming, and the       |     |

|      | Number of On-chip Stimuli Pointers equals 8 and 16, respectively (Song |     |

|      | = 462.38 k Samples)                                                    | 118 |

## Chapter 1

### Introduction

The continuous advancements in semiconductor manufacturing have enabled the implementation of digital integrated circuits (ICs) with millions of transistors on a single silicon die. The increased design complexity leads to a longer implementation cycle, which is mainly driven by increased design and verification times. To address this problem, the core-based system-on-chip (SoC) design paradigm has emerged at the end of the past decade [61]. In this paradigm, to address the length of the implementation cycle, the system integrators reuse pre-designed and pre-verified intellectual property blocks (or embedded cores) developed by core providers. Nonetheless, given the increase in the number of embedded cores and the growing size of the user defined logic, as well as the shrinking time-to-market cycles, the contribution of verification to the overall implementation time is considerable. As a consequence, pre-silicon verification techniques, such as formal verification using model checking or functional verification through biased-random simulation, have been established as a necessary step to identify design errors (or bugs) before the design is manufactured [70].

Nonetheless, the growing complexity of SoC designs and the limitations in modeling all the physical characteristics of the design, make pre-silicon verification techniques inadequate to guarantee the first-silicon to be error-free. Because finding bugs in a fabricated design will cause a silicon re-spin, which impacts both the product cost and the time-to-market, it is desirable for design bugs to be identified and fixed as soon as the first silicon is available. Consequently, post-silicon validation (or *silicon debug*) [3] has emerged as a necessary step in the implementation cycle of SoC designs.

This introductory chapter is organized as follows. Section 1.1 provides an overview of the design flow and the verification techniques for very large scale integrated (VLSI) circuits. Section 1.2 describes the motivation of this research. Finally, Section 1.3 outlines the main contributions of this research and presents the organization of the dissertation.

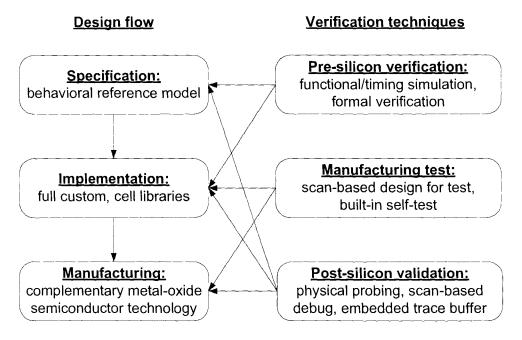

#### 1.1 Design Flow of VLSI Circuits

The design flow of VLSI circuits is comprised of three steps: specification, implementation and manufacturing as shown in Figure 1.1. The specification step typically describes the expected functionality of the VLSI circuits. Design specifications are described in a high-level language such as SystemC [43], or in hardware description languages (HDLs) such as VHDL [79], Verilog [80] or System Verilog [98]. The register transfer level (RTL) abstraction is used in HDLs to describe the circuit's behavior as a set of transfer functions which represent the flow of signals between the registers, and the logical operations performed on those signals [39]. The process of transforming the circuit model from a higher (or less detailed) abstraction level to lower (or more detailed) abstraction level is called synthesis. The logic synthesis performs the translation of the HDL design into the generic library of components followed by optimization and mapping into the gate-level components [32].

The subsequent step in the design flow is to synthesize a circuit description into a gate-level netlist that represents the logical functionality of the circuit (i.e., implementation). As shown in Figure 1.1, the design can be implemented based on different design methodologies either full custom or semi-custom. In the full custom design methodology, the designer creates the layout of the circuit and the interconnections between the circuit components in order to maximize the performance of the circuit, and minimize its area. On the other hand, in the semi-custom design methodology, the implementation is performed using standard cell libraries or gate arrays through

Figure 1.1: Design Flow and Verification Techniques of VLSI Circuits

computer-aided design (CAD) tools. These tools transform the design from the RTL abstraction level into the gate level structural netlist and perform the translation from the gate level netlist into a physical layout [18].

The final step in the design flow of VLSI is the process of creating the integrated circuit (i.e., manufacturing). The fabrication process is a multiple-step sequence of photographic and chemical processing steps during which the integrated circuits are gradually created on a wafer made of semiconducting material based on the specific transistor technology (e.g., 90 nm) [34]. Silicon is the most commonly used semiconductor material in VLSI circuits and complementary metal-oxide semiconductor (CMOS) is the main type of transistors. The increasing complexity of VLSI design makes pre-silicon verification, manufacturing test and the validation of the first silicon a bottleneck in the design flow.

#### 1.1.1 Pre-Silicon Verification

As the complexity of SoC designs increases, the shrinking time-to-market makes design verification one of the major challenges in the implementation flow. As a consequence, pre-silicon verification techniques such as formal verification and simulation are used extensively to identify design errors before the design is manufactured [70]. The purpose of these pre-silicon verification techniques is to verify the implemented design against its specification.

Simulation techniques are used to verify the circuit behavior at various levels of abstraction. For example, the design can be simulated at a higher behavioral level that does not contain detailed timing information. The more detailed information the circuit model has (e.g., logic-level netlist), the more time will be needed to verify its functional correctness. Thus, exhaustive simulation for complex VLSI designs is practically infeasible. Formal verification, as a complementary technique to simulation, is the process of mathematically proving or disproving the correctness of the design with respect to a certain formal specification or property [62]. There are two main approaches to formal verification: equivalence checking and property (also known as model) checking. The purpose of equivalence checking is to ensure that two given designs are functionally identical by comparing one design called the reference model with the targeted design. These designs may be given on different levels of abstraction, i.e., register transfer level or gate level [35]. Property (or model) checking is used to check a given design for the satisfaction of its properties which are formulated in a dedicated verification language. Model checking is a commonly used approach in formal verification of finite state concurrent systems, where exhaustive exploration of all states and transitions in the circuit model can be performed through efficient techniques that reduce computing time [28].

Formal verification has proven its significance in identifying the logic bugs during pre-silicon verification of the Intel processor [16]. Nevertheless, due to the inherent trade-off between state coverage and verification time, as well as the limitations in modeling all the physical characteristics of the design, pre-silicon verification techniques have become insufficient to guarantee the first-silicon to be error-free.

Figure 1.2: Basic Principle of VLSI Circuits Testing

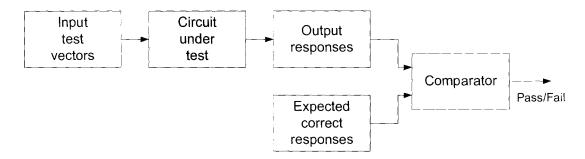

#### 1.1.2 Manufacturing Test

Manufacturing test has become an essential step in the implementation flow of the VLSI circuits to ensure that the functionality of the manufactured circuits matches its implementation [24]. It is used to identify the physical defects that lead to faulty behaviors in the fabricated circuits. Figure 1.2 shows the basic principle of manufacturing test. The entire test process is typically controlled by a powerful test instrument called automatic test equipment (ATE). Circuit under test (CUT) is the entire chip or part of the chip to which the input test vectors are applied. The input test vectors are binary patterns applied to the input of the circuit. These test vectors are obtained using automatic test pattern generation (ATPG) algorithms [24]. The circuit is identified as a fault-free circuit if the observed output responses match the expected correct responses. If the circuit failed the test, the fault diagnosis process will be started to diagnose and identify the root cause of the failure.

The circuit under test can be tested using functional or structural test. Functional test requires a complete set of the test patterns to verify every entry of the truth table (e.g., for a circuit with n inputs, the number of input test vectors will be  $2^n$ ). For example, for exhaustively testing a 64-bit ripple-carry adder,  $2^{129}$  input test vectors are needed. If the ATE operates at  $1 \ GHz$ , it would take  $2.158 \times 10^{22}$  years to apply the complete test set [24]. Therefore, complete functional testing leads to extremely long testing time, which makes it practically infeasible for testing complex integrated circuits. On the other hand, structural testing depends on the netlist structure of the

Figure 1.3: Basic Principle of BIST

design. In this technique, the defects are usually modeled at a certain level of design abstraction for the purpose of efficient testing (e.g., gate level or transistor level) [24]. Some typical fault models are stuck-at fault model, open fault model and path delay fault model. The most commonly used fault model is the single stuck-at fault model where a single node in the structural netlist of the logic network is assumed to have a fixed logic value and hence it is stuck-at either 0 or 1. When using the stuck-at model for the 64-bit ripple-carry adder, only 1728 stuck-at faults would need to be excited with 1728 input test patterns [24].

Achieving high fault coverage during manufacturing test is obtained through the inclusion of design for testability (DFT) circuitry that enhances the controllability and observability of the circuit's internal nodes. Scan based DFT is the most commonly used DFT methodology, in which all or part of the sequential elements (i.e., flip flops) of the circuit are replaced with scanned flip-flops (SFFs). In the test mode, these SSFs form one or more long shift registers called scan chains. The input test patterns are applied serially to the input of these scan chains which are connected to the primary inputs of CUT. The states of these SFFs are observed by shifting out the contents of the shift registers whose outputs are connected to the primary outputs of CUT [24].

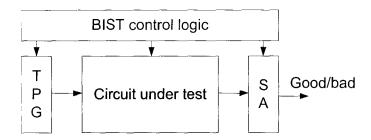

Another DFT method is the built-in self-test (BIST). BIST can be used as a low cost testing approach when compared to ATE-based testing. In ATE-based testing, test stimuli are applied to the chip pins from the ATE and test responses are shifted out and compared with the correct responses stored in the ATE memory. Due to the large memory and bandwidth requirements for testing state-of-the-art SoCs, BIST

Figure 1.4: Deterministic BIST with Multiple Scan Chains Architecture

can be used as an alternative approach to external test for complex VLSI circuits. As shown in Figure 1.3, a test pattern generator (TPG) generates a set of test stimuli and a signature analyzer (SA) analyzes the test responses and makes the decision of good/bad chip. The BIST control block controls the test sequence. In BIST approach, a linear feedback shift register (LFSR) can be used as the TPG, and a single input signature analyzer (SISR) or a multiple input signature analyzer (MISR) can be used as the SA [13]. BIST methods can be classified into pseudo-random BIST and deterministic BIST. Applying only pseudo random test stimuli cannot guarantee sufficiently high fault coverage because the majority of the circuits are not completely random testable. Thus, the pseudo-random test-patterns can be extended with deterministic test patterns using more sophisticated pattern generators in order to achieve high fault coverage [26, 105, 120]. The pseudo-random BIST can be combined with deterministic BIST methodology to generate the scan inputs of the circuit under test for multiple scan chains architecture.

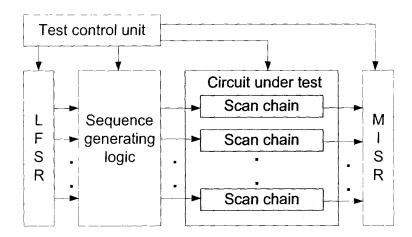

Figure 1.4 shows scan-based BIST architecture that supports deterministic BIST pattern generation. The test pattern generator consists of an LFSR and sequence generating logic (SGL). The purpose of SGL is to modify the pseudo-random patterns generated from the LFSR into deterministic ones by changing certain bit positions [63, 64]. The deterministic patterns are then applied to the CUT via scan chains.

The outputs of the scan chains are compacted into a signature stored in a multiple input shift register (MISR) to be compared with the correct expected signature.

By cost-effectively inspecting whether the implemented design is identical to the fabricated one, manufacturing test has become a key enabling technology that accelerates yield ramp-up and guarantees product quality. Nonetheless, manufacturing test is concerned only with fabrication defects and it relies on the circuit netlist as a golden reference. Therefore, to make sure the product does not contain any design bugs (which are present in the netlist and hence affect every fabricated device), manufacturing test must be complemented by post-silicon validation (or silicon debug) in order to identify the design errors that have not been caught by pre-silicon verification.

#### 1.1.3 Post-Silicon Validation

The purpose of post-silicon validation is to identify and fix design bugs that are present in the fabricated circuit. These bugs can be classified into functional (logic) bugs where the circuit does not correctly match its specified function, or electrical bugs where the circuit does not meet the correct behavior over the entire operating region of its voltage, temperature or frequency [57]. The limited observability of the internal circuit signals is the major concern during post-silicon validation. To address this problem, physical probing techniques have emerged to improve the ability to probe internal circuit nodes and hence find the root cause of the electrical bugs [75, 97]. Probing techniques such as time resolved photoemission [33] and laser voltage probing [85] provide essential debug information that aids in the localization of the electrical bugs. Given the importance of physical probing techniques and the increasing complexity of SoC designs, a localization step, which we denote as logic probing, that compares the simulation data with the information observed in silicon. is required to identify a subset of circuit nodes that need to be physically probed [107]. Consequently, logic probing techniques have emerged as a complementary approach to physical techniques not only to aid in finding the electrical bugs but also to help in identifying the functional bugs that have escaped pre-silicon verification.

Reusing the scan chains, which are present in the circuit for manufacturing test. is one of the most commonly used logic probing techniques during post-silicon validation [30, 118]. In this scan-based debug approach, the circuit response is captured after the occurrence of a specific trigger event and, subsequently, the captured response is transferred to the debug software (this process is called scan dump). The debug software communicates with the circuit under debug (CUD) either through scan channels when debugging on the automatic test equipment (ATE), or through a low bandwidth interface (e.g., Boundary Scan [53]) when debugging on the target application board. The captured circuit response can be analyzed off-chip using post-processing algorithms, such as latch divergence analysis [29] or failure propagation tracing [25], to identify the first failing state elements.

The limitation of scan-based debug lies in the fact that halting the execution during scan dump may destroy the system's state. Thus, capturing debug data in consecutive clock cycles can not be achieved by using only the available scan chains. Although the use of shadow scan latches, (which may incur a substantial area penalty [58]), can avoid the destructive nature of the scan dump, a new capture cannot occur until the scan dump has been completed. Because capturing debug data in consecutive clock cycles is essential for identifying the timing related bugs, complementary techniques to scan-based method have been developed to provide real-time observability of a limited set of internal signals during post-silicon validation.

The debug data of a subset of internal signals can be acquired off-chip in real-time through dedicated chip pins [112]. The limitation of this debug technique for the state-of-the-art SoCs lies not only in the difficulty to drive high internal clock frequencies onto external chip pins but also in the limited pin counts allocated for debug. Consequently, embedded logic analysis methods that rely on on-chip trace buffers have emerged as a complementary approach to scan-based methods to enable real-time and at-speed observation of a limited set of internal signals [71]. The captured data is subsequently transferred, via a low bandwidth interface, from the internal debug module to the external debug software for post-processing. Trace buffer-based techniques have been recently used for debugging microprocessors [38, 46, 86, 95, 99], SoC designs [48, 71], and designs mapped to field programmable gate arrays [5, 100, 122].

#### 1.2 Dissertation Motivation

The focus of this dissertation is to develop design-for-debug (DFD) architectures and methods that facilitate the identification of the functional bugs, when the validation is performed at-speed and in-system, i.e., on prototype application board. Although they have been validated for functional bugs, the proposed architectures and methods can be used also as a front end to physical probing techniques to assist in electrical bugs validation. As explained next, they are motivated by the limited real-time observability, as well as by the difficulty of dealing with blocking bugs during post-silicon validation.

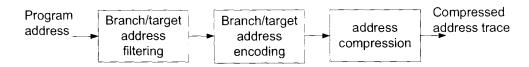

The amount of debug data that can be captured into an on-chip trace buffer during embedded logic analysis is limited by the trace buffer width, which constrains the number of signals to be probed, and its depth, which limits the number of samples to be stored. To extract as much data as possible from a given debug experiment, i.e., to increase its observation window, without increasing the area of the on-chip trace buffer, compression can be employed. The existing compression methods can be categorized into special-purpose methods for microprocessors [46, 52, 60, 99] and generic methods for custom SoC designs [6, 7, 48, 67, 123]. The special-purpose methods rely on trace reduction or on lossless compression techniques. Trace reduction techniques are based on sampling (or filtering out) data at specific intervals, using programmable start/stop flags or by recording only program counter changes or branch addresses. In the lossless compression techniques, the compression can be accomplished by eliminating the redundant temporal information on data or address busses (e.g., through differential compression) [46].

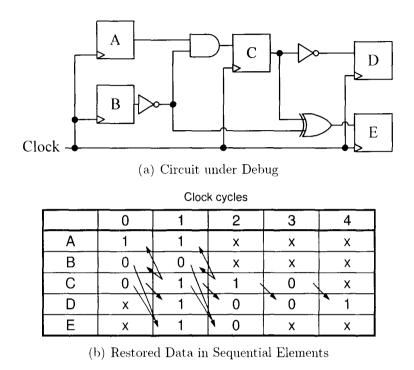

For custom SoC designs, the compression techniques are currently emerging. For example, the compression can be achieved by analyzing the design and identifying a subset of essential signals which, after being captured on-chip, would then be expanded in the debug software using the knowledge of the design data [48, 67]. We refer to this method as a width compression technique where the length of the observation window remains the same and compression is achieved by re-constructing the values of more signals from the ones that are captured in the trace buffer. To

capture as many samples as possible while running a long debug experiment, one can employ also depth compression. It is important to note that the two main directions for compressing debug data for custom SoC designs (width and depth compression) are orthogonal to each other. In this dissertation we focus only on depth compression, which to the best of our knowledge has not been covered in the public domain (other than the prior works by the authors [6, 7]). Moreover, a new debug technique has been recently proposed in [123], as a follow up to our research work presented in [6]. The key differences between the debug technique introduced in [123] and our work will be discussed in Chapter 4.

Because of the presence of *blocking bugs* in one erroneous module inhibits the search for bugs in other parts of the chip that process data received from the erroneous module, it is important to bypass its erroneous behavior. In this dissertation, we address this problem by developing an embedded debug architecture that enables a hierarchical event detection mechanism in order to provide stimuli from an on-chip trace buffer, for the purpose of replacing the erroneous behavior caused by the blocking bugs [8].

#### 1.3 Dissertation Organization and Contributions

The rest of this dissertation is organized as follows. Chapter 2 provides the background and a review of related work in post-silicon validation.

Chapter 3 introduces a novel debug architecture for embedded logic analysis that enables real-time lossless data compression. The proposed debug technique extends the depth of the observation window of a debug experiment. To quantify the performance gain from using lossless compression in embedded logic analysis, we present a new compression ratio metric that measures the trade-off between the area overhead and the increase in the observation window. We use this metric to quantify the performance gain of three dictionary-based lossless compression algorithms. The proposed architecture is based on one pass scheme algorithms which do not require re-running the debug experiment. Thus, the proposed architecture is particularly useful for in-field debugging on application boards which have non-deterministic input

sources, such as asynchronous interfaces.

Chapter 4 presents a novel architecture for at-speed silicon debug based on lossy compression. In order to accelerate the identification of the design errors, we have developed a new debug method where the designer can iteratively zoom only in the intervals that contain erroneous samples. By extending the silicon debug observation window using a short sequence of debug sessions, the proposed approach is useful in aiding the identification of hard-to-detect functional bugs that occur intermittently over a long period of time [57], which is computationally-infeasible to be simulated during pre-silicon verification. When compared to increasing the size of the trace buffer, the proposed architecture has a small impact on silicon area, while significantly reducing the number of debug sessions. The proposed method is applicable to both automatic test equipment-based debugging and in-field debugging on application boards, so long as the debug experiment can be reproduced synchronously.

Chapter 5 introduces a novel embedded debug module architecture for bypassing blocking bugs that occur intermittently over a long execution time. This architecture facilitates the validation of the other parts of the chip that process data received from the erroneous module. The proposed approach enables a hierarchical event detection mechanism to provide correct stimuli from an embedded trace buffer, in order to replace the erroneous samples caused by the blocking bugs.

Chapter 6 summarizes the contributions of this research and provides directions for future work.

## Chapter 2

## Background and Related Work

This chapter provides the background and a review of related work on post-silicon validation. We first introduce an overview of post-silicon validation in Section 2.1. The scan-based debug technique is described in Section 2.2. The basic principle of embedded logic analysis and the trace buffer-based debug techniques are introduced in Section 2.3. The recent advancements in the design for debug techniques for improving the observability of the internal circuit's nodes are described in Section 2.4. Finally, Section 2.5 concludes this chapter.

#### 2.1 Overview of Post-silicon Validation

As outlined in the previous chapter, due to the growing complexity of system-on-chip (SoC) designs and the ever increasing demand of time-to-market, pre-silicon verification techniques such as simulation and formal verification [70] have become insufficient to guarantee the first-silicon to be error-free. Furthermore, many electrical bugs (e.g., leakage, charge sharing, noise coupling between interconnect lines or drive fights) cannot be screened without the existence of the fabricated IC [57]. Given the escalating mask costs, it is imperative that the design bugs are identified and fixed as soon as the first silicon is available. As a consequence, structured post-silicon validation techniques have emerged to reduce the time required to find design bugs, the number of silicon spins, and hence the time-to-market [112].

The design bugs that can be identified during post-silicon validation can be classified as either functional bugs or electrical bugs, as described in Chapter 1. These design bugs types are analyzed and debugged differently according their validation plans [58]. For functional validation, validation patterns are applied to circuit under debug (CUD) in order to ensure its functional correctness. For electrical validation, validation patterns are used to ensure functional correctness of the CUD across the entire operation region of voltage, temperature and frequency. A characterization window is used to specify the range of voltage and frequency across which the circuit is guaranteed to work [58]. In order to identify the electrical bugs, a two dimensional plot (also referred to as shmoo plot) is used to show how the circuit performs against the variation of the voltage and the frequency [11]. It should be noted that the debug process which targets different types of bugs depends on the underlying debug environment and the design-for-debug (DFD) features implemented in the CUD to facilitate the identification of design bugs.

#### 2.1.1 Debug Environments

There are two main types of environments for debugging prototype silicon: digital IC testers (also referred to as ATE) and prototype application boards. Digital IC testers are used in manufacturing test to screen the circuit for manufacturing defects. The importance of the tester environments lies in the capability to apply the input stimuli and compare the responses on the circuit I/O pins against the expected responses. Part of electrical validation is performed on the tester because of the ability to precisely control the voltage and frequency. Due to the limitation of tester storage and the necessity to cover the functional correctness of the CUD, ATEs may not be sufficient for debug, e.g., to replay several minutes of digital video [112]. Therefore, in-system debugging (on application boards) is usually used as a complementary approach to ATE-based debug. For in-system debug approach, no extensive stimuli and responses storage are needed as in the case of ATE-based debug but the controllability and observability are less straightforward. The debug engineer can chose between the debug environments based on the validation objectives.

#### 2.1.2 Post-silicon Validation Techniques

The main challenge in post-silicon validation is the limited observability of the internal circuit's signals. To address this problem, physical probing techniques have emerged to improve the ability to probe internal circuit's nodes and hence find the root cause of the electrical bugs [33, 75, 85, 97]. However, despite the recent advancements in the physical probing techniques, the complexity of state-of-the-art devices requires a localization step to precede the destructive IC failure analysis. This step, which we denote as logic probing, correlates the simulation data to what is observed in the silicon (either on the (I/Os) or on the internal signals) in order to identify a subset of circuit nodes that need to be physically probed [107]. This is achieved by adding DFD hardware for the purpose of improving the internal observability and accelerating the debug process. The DFD techniques are not only useful in finding the electrical bugs but they are also essential for locating the functional bugs.

In order to identify the design bugs during post-silicon validation, DFD infrastructure is employed to enable capturing and accessing the internal state of the CUD. Two DFD complementary techniques have been used to provide the observability of the system's state: scan chain debug technique based on run-control debug approach, and embedded logic analysis based on real-time trace approach. These debug techniques are essential to narrow down the search for design bugs by pinpointing both temporally (when) and spatially (where) a bug occurs.

#### 2.2 Scan-based Observability

The scan methodology is the most commonly used technique in manufacturing test for the purpose of allowing the observation of internal circuit's full state. Scan chains have been used extensively for debugging complex digital ICs [12, 14, 30, 44, 59, 69, 72, 89, 108, 111, 115, 117, 118]. To distinguish between the usage of scan chains in manufacturing test and post-silicon validation, we first illustrate their functionality during the manufacturing test process.

Figure 2.1: A Single Scan Chain Architecture

#### 2.2.1 Scan-based DFT Methodology

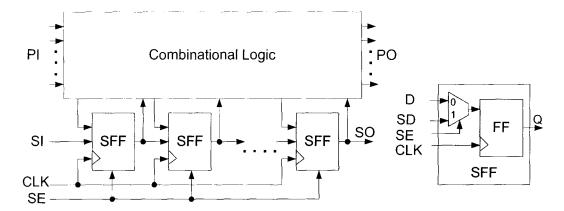

When employing scan chains in scan-based DFT, the sequential elements (i.e., flip-flops, latches) are connected in such a manner that allows two modes of operation. In the test mode, the scanned flip-flops are reconfigured as one or more shift registers (known as scan chains). The input test vectors are serially loaded to the CUT. Once a vector is loaded, the CUT is allowed to work in its normal mode where the circuit response is captured in the flip-flops. Thereafter, the captured response is shifted out and compared versus the expected response [24].

Figure 2.1 illustrates the architecture of a single scan chain. Each scanned flip-flop (SFF) is composed of a D flip-flop and a 2-to-1 multiplexer. A scan enable signal SE selects between two data inputs: the original data input D, and the scan-data input SD. The primary inputs/outputs (PI/PO) are connected directly to the combinational logic. The scan chain is constructed by connecting the data output Q of one SFF to the SD signal of the following SFF, as illustrated in the Figure 2.1. The scan-based DFT procedure during the test process can be explained as follows: (i) assert scan enable signal (i.e., SE is set to 1), and load the test vector through the scan input (SI); (ii) de-assert scan enable signal (i.e., SE is set to 0), and apply one clock cycle in order to capture the circuit response from the combinational logic outputs in SFFs; and (iii) re-assert scan enable signal (i.e., SE is set to 1), and scan out the test

responses. While the test response is shifted out, a new test vector is simultaneously shifted in. The length of the scan chain and the number of test patterns are the two contributing factors that influence the test time. To reduce the test application time, multiple scan chains can be used. Each scan chain usually has its dedicated SI and SO pins and hence the test data/response can be shifted in/out in parallel. It is important to note that most blocks of a SoC are designed with full-scan capability, where all internal sequential elements are replaced by SFFs, in order to achieve high fault coverage [24].

#### 2.2.2 Scan-based Debug Methodology

In the scan-based debug approach, the circuit response is captured after the occurrence of a specific trigger event and subsequently, the captured response is transferred to the debug software (this process is called scan dump). The debug software communicates with the circuit under debug either through scan channels when debugging on the automatic test equipment (ATE), or through a low bandwidth interface (e.g., boundary scan IEEE 1149.1 standard interface [53]) when debugging on an application board. To control the debug process, DFD hardware (i.e., debug module) is integrated with scan chains to enable start, stop, resume or single-step the program execution [116]. This approach obviously provides high observability and controllability of the circuit behavior and hence facilitates the identification of the error-capturing scan cells. For example, scan-based techniques rely on stopping the functional test program when a failure is observed on an output and subsequently, by re-running the debug experiment with different trigger points, it can scan dump the state before and after the observed failure point. Thereafter, post-processing algorithms, such as latch divergence analysis [29] or failure propagation tracing [25], can be used to analyze the scan dumps and identify the first failing state elements.

To support scan-based debug, two essential features have to be enabled by the DFD infrastructure: breakpoint mechanism (i.e., trigger conditions detector) and execution control. Breakpoints (or trigger conditions) determine the points in time at which the system execution is stopped. Once the circuit is stopped, the internal

state is transferred to debug software to be compared with the obtained correct state from simulation. The breakpoint circuitry can be reprogrammed to specify a different trigger condition to get an insight in the actual behavior of the CUD. The process of stopping the circuit at a certain time and observing its internal state can be repeated in a sequence of debug experiments (or sessions) until the bug is identified.

The operations, that control the execution of the CUD during a debug session, can be explained as follows [112]:

- Reset: to reset the chip and its environment to a known state;

- Run: to start the application;

- Stop: to stop the on-chip clocks once the trigger condition occurred;

- Scan out: to dump the content of the scan chains;

- Single step: to step through the execution of the chip, one clock cycle at a time; and

- Continue: to resume operation after execution has previously been stopped.

These functions require an on-chip clock reset circuitry and a clock controller that provides stop, scan, continue, and single-step operations.

The controlled execution of the circuits's internal functions is similar to the process of software debug. During software debug, the debug engineer iteratively sets custom breakpoints to stop the program and then examines the state of the application. Various breakpoints configurations and single step operations can be performed iteratively until the bugs are identified. During post-silicon validation, an on-chip breakpoint module is programmed to stop the CUD at a specific point in time. Thereafter, the contents of all flip-flops (i.e., scan chains) can be transferred off-chip via a low bandwidth interface to be analyzed.

#### Example of a Breakpoint Debug Module

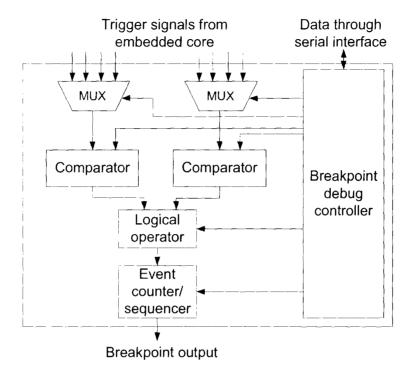

Figure 2.2 shows an example of a breakpoint module, which is connected to several trigger signals from an embedded core. The selection of targeted trigger signals, that

Figure 2.2: Example of Breakpoint Debug Module

debug engineer wants to trigger on, is uploaded to the breakpoint debug controller through the serial interface, e.g., boundary scan IEEE 1149.1 standard interface [53]. The capability of the breakpoint module for detecting a certain trigger condition is essential in the identification of design bugs. Thus, the breakpoint debug module contains comparators which are used to compare the selected trigger signals against preprogrammed breakpoint registers existing in the breakpoint debug controller. The targeted comparison operations (e.g., less than, greater than or equal) are selected based on the control information uploaded in the breakpoint controller.

As shown in Figure 2.2, two trigger signals can be selected using two multiplexes (MUXs) and these signals can be compared against the loaded values of the two comparators. A logical operation can be performed on the output of the two comparators such as OR, XOR, or AND operation. The output of the logical operator is connected to an event counter/sequencer. The event counter is used to determine

a certain event that occurred a pre-defined number of times. The event sequencer is used to determine multiple different events that occurred in a pre-defined order. The debug configuration that specifies the breakpoint condition can be uploaded to the breakpoint debug controller at run-time through the serial interface. When the targeted trigger condition occurs, the output of the breakpoint debug module triggers the clock controller that provides stop, scan, and single-step functions. It is important to note that the breakpoint module can contain more levels of logic than the ones shown in Figure 2.2. For example, bitwise operators can be inserted to precede the comparison operators to perform bitwise operation between a selected trigger signal and a pre-defined constant value uploaded in the breakpoint controller.

To facilitate the inclusion of breakpoint modules during the design stage of the chip, a novel approach has been proposed to automatically generate breakpoints modules using breakpoint description language (BDL) [116]. BDL allows the designer to write the description that captures the specification of the breakpoint module. A BDL compiler tool then reads this description and generates the hardware implementation of the corresponding breakpoint module. However, the area of the generated breakpoints using BDL can be larger than their custom implementations. This area increase is because the generated breakpoints do not share common resources (i.e., comparators) [116].

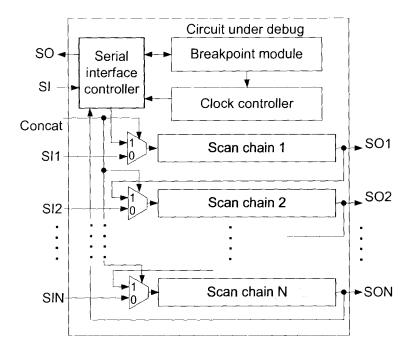

#### Scan-based Debug Architecture

Figure 2.3 illustrates the scan-based architecture for post-silicon validation [93]. Note that the surrounding combinatorial logic, associated with each scan chain, is not shown in this figure. There are two modes of operation: the test (or debug) mode on ATE and the debug mode on prototype target application board. In the test mode, the concat signal is set to 0 (i.e., Concat = 0) and the scan is configured for manufacturing test on ATE, where the scan chains are accessed in parallel through the functional pins. As mentioned earlier, part of electrical validation is performed on the ATE because of the ability to precisely control the voltage and frequency. In the debug mode where the CUD is debugged in-system, once the breakpoint debug module detects the trigger event, the clock controller stops all on-chip clocks. Thereafter, the

Figure 2.3: Scan-based Debug Architecture [93]

concat signal is set to 1 (i.e., Concat = 1) and hence the multiplexers concatenate all scan chains into one long shift register. The content of the scan chain is then shifted out via the SO pin through the serial interface (e.g., JTAG [53]). The received data can be applied to the chip via the SI pin during shifting out scan chains data. This procedure is repeated until all internal scan chains have been scanned out. After comparing the circuit's complete state against the expected one, the debug engineer can reprogram the breakpoint debug module to specify another trigger condition in order to capture and analyze the chip's state at another particular event. Upon observing a mismatch, the engineer tries iteratively to zoom in on the time and location of the error's occurrence by setting another trigger condition and analyzing the captured data. This process is continued until the root cause of bugs is identified. Then, the bug is fixed in the original design and new silicon is manufactured. Figure 2.4 shows the iterative debug flow during post-silicon validation as described above. It is important to note that stopping a system with multiple clock domains may lead

Figure 2.4: Debug Flow during Post-silicon Validation

to data invalidation where some clock domains might use data from clock domains that have already stopped because the on-chip clocks do not stop simultaneously [41]. A novel data invalidation detector has been proposed in [41] to identify the scan elements (i.e., flip-flops) that capture invalid data, and hence the content of these elements will not be used for the comparison with the simulation model.

The clock controller can enable other control functions such as single step and continue operations. The single step operation is implemented as an extension to the debug scan-out operation, where the circuit is allowed to work in the normal mode and the scan enable on the scannable flip-flops is not activated. The continue operation is achieved by deactivating the breakpoint mechanism that releases the gating on the clocks, so that chip operation can resume. It is important that the phases and frequencies of the on-chip clocks are the same as at the moment the chip was stopped; otherwise, the resumed operation will not be the same as in the case of a chip that has not been stopped [31].

Because halting the execution during scan dump may destroy the system's state, capturing debug data in consecutive clock cycles can not be achieved by using only

the available scan chains. As hard-to-detect functional bugs appear in circuit states which may be exercised billions of cycles apart [57], it is desirable to maintain the circuit operation during scan dumps. Although the use of shadow scan latches, which may incur a substantial area penalty [58], can avoid the destructive nature of the scan dump, a new capture cannot occur until the scan dump has been completed. Because capturing debug data in consecutive clock cycles is essential for finding timing-related bugs, new debug methods have been developed to provide real-time observability of a limited set of internal signals.

Real-time observation of a subset of internal signals off-chip, can be achieved by using dedicated chip pins to output the debug data to on-board acquisition buffers [112]. The limitation of this approach for state-of-the-art SoCs lies in the limited number of pins used for debug, as well as in the difficulty to drive internal data at high rates onto the board. As a consequence, *embedded logic analysis* methods that rely on on-chip trace buffers have emerged as a complementary approach to scanbased methods in order to enable real-time and at-speed sampling of a limited set of internal signals [71, 78].

## 2.3 Embedded Logic Analysis

Embedded logic analysis is a DFD technique used for improving the observability of internal signals of SoC design by acquiring debug data on-chip into embedded trace buffer. This is achieved through a DFD event detection mechanism that can be configured to a specific trigger event at which the acquisition process starts or stops.

## 2.3.1 Basic Principle of Embedded Logic Analysis

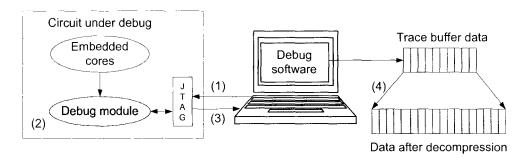

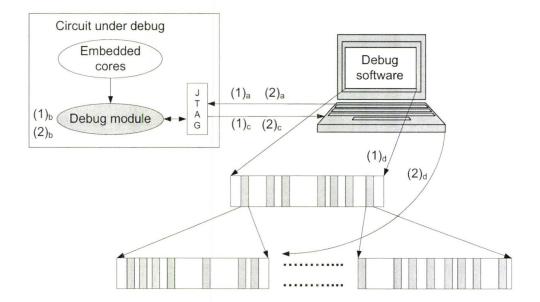

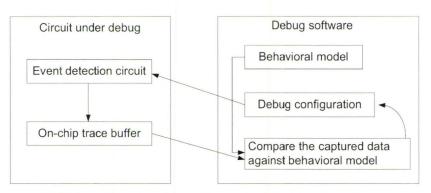

Figure 2.5 illustrates the basic principle of an embedded logic analysis debug framework. In this framework, the off-chip debug software communicates with the embedded debug module through a serial interface such as the Boundary Scan interface (i.e., JTAG [53]). The embedded debug module contains an embedded trace buffer to provide real-time observability for a subset of internal signals. As shown in Figure

Figure 2.5: Debug Framework of Embedded Logic Analysis

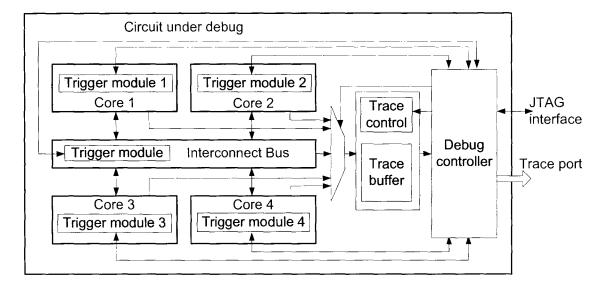

Figure 2.6: Circuit under Debug with Centralized Debug Module

2.6, a centralized embedded debug module monitors a limited set of internal signals coming from embedded cores and the interconnect bus of the CUD. The concept of a centralized debug module has been used in debugging multi-core processor design [91]. The debug flow during embedded logic analysis is explained as follows.

A debug experiment (or session) starts by uploading the embedded debug module with the debug configuration (Step (1)). This configuration contains debug control information such as the trigger condition that specifies the point in time at which the acquisition of debug data starts, and the control data that specifies the selection of nodes that need to be probed. Once the trigger condition occurs during the execution of the on-chip application, the debug module will start capturing the selected signals

Figure 2.7: Embedded Debug Module Architecture

behavior into an on-chip trace buffer (Step (2)). The debug experiment is completed by transferring the trace buffer's content to debug software, where the captured data is analyzed (Step (3)). The debug experiment can be iteratively repeated with different debug configuration until the design bugs are identified.

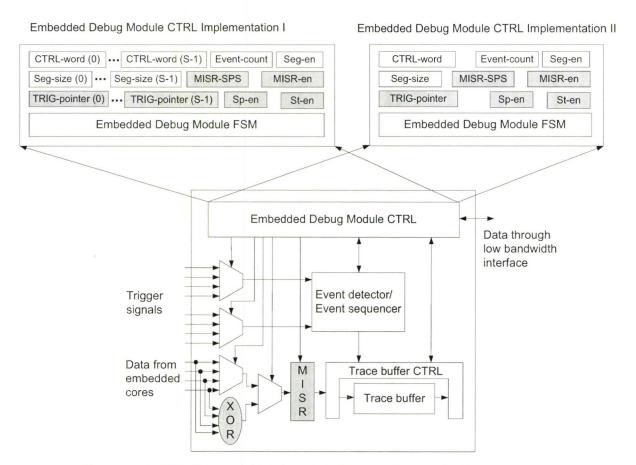

## 2.3.2 Embedded Debug Module Architecture

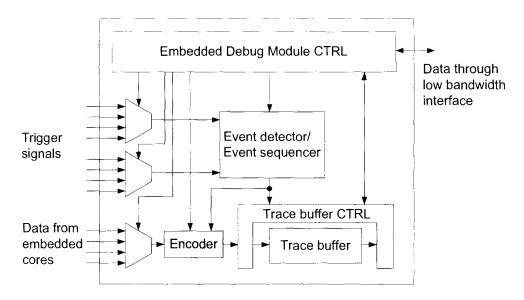

The key feature of an embedded debug module is to capture the behavior of selected internal signals upon the occurrence of a certain triggering condition (i.e., trigger event). This is achieved using an event detector that monitors a group of trigger signals to determine when the debug data is captured in the trace buffer, as shown in Figure 2.7. The trigger condition can be performed based on bitwise, comparison or logical operations between a certain selected trigger signal and a specified constant value stored into a control register which exists in the embedded debug module control. To further enhance the detection ability of the debug module, the event detector is augmented by an event sequencer to monitor a specified sequence of events. The

Figure 2.8: Triggering Conditions Flow with Segmented Trace Buffer

configuration of the trigger signal selection, the trigger conditions, and the choice of the signals that need to be probed are uploaded to the embedded debug module control through the low bandwidth interface (e.g., JTAG [53]). It is important to note that the event detector/sequencer functionality used in the embedded debug module is similar to the one used in the breakpoint module of scan-based debug architecture described in Section 2.2.2.

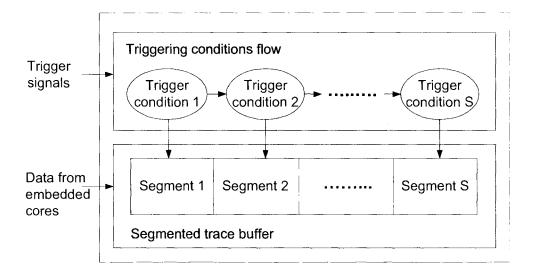

The embedded trace buffer can allow flexible acquisition by employing it as a segmented buffer. Figure 2.8 shows the segmented trace buffer with S segments. Each segment captures the data upon the occurrence of the corresponding triggering condition, e.g., Segment 1 starts the acquisition upon the occurrence of trigger condition 1. Once the first trigger condition occurred, the event detector circuit is configured to monitor the second trigger condition. The event detection circuit is sequentially updated with the control information that specifies the required triggering condition until the last triggering condition is reached. Each segment size can be configured to work as a circular buffer segment and thus in this case the triggering condition can be used to stop the data acquisition. The feature of a segmented trace buffer described above has been used in debugging FPGA designs [5].

Figure 2.9: Multi-core Debug Architecture with Centralized Trace Buffer

#### 2.3.3 Embedded Logic Analysis Related Work

While scan-based debug concepts have emerged from the manufacturing test research, trace buffer-based debug has been influenced by software debugging used in real-time embedded systems [76]. Real-time systems, centered around embedded processors or micro-controllers, have been traditionally debugged using in-circuit emulator (ICE) devices. ICEs are constructed using bond-out chips, which connect internal nodes to additional device I/Os in order to make them visible off-chip to external instruments. The limitation of using ICEs for state-of-the-art SoC devices lies not only in the increasing gap between the on-chip and off-chip frequencies, but also in a large footprint of the bound-out chips caused by the additional I/Os used only for debug. As a consequence, for SoC designs there has been a trend toward placing the instrumentation on-chip, thus enabling at-speed sampling through embedded logic analysis [5, 71, 100, 122].

The trace buffer-based debug methods can be broadly classified as: special-purpose (i.e., specific to embedded processors) [47, 49, 77, 91, 95, 99] or generic (i.e., applicable to any type of custom SoCs) [1, 2, 48, 71, 90]. In order to concurrently monitor

Figure 2.10: Multi-core Debug Architecture with Multiple Trace Buffers

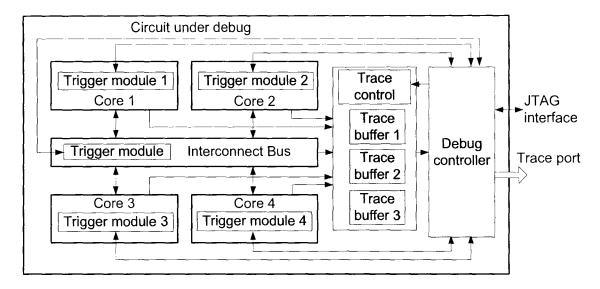

signals behavior from different cores in complex SoCs, distributed trigger modules are allocated in multi-core architecture [46]. Moreover, two approaches can be used to support data tracing from embedded cores either: centralized or distributed trace. In the centralized trace approach, one trace buffer is employed for the entire SoC, where the trace data is selected through a multiplexer network [2]. Figure 2.9 shows the multi-core debug architecture with central trace buffer. The centralized trace buffer approach has been used in debugging the Cell processor which contains nine processing cores [91]. Due to the limited speed and bandwidth of the serial interface, high speed trace port can be used for streaming the data that is captured into the trace buffer [36, 46]. Thus, the trace port can facilitate the debug process by offloading the trace buffer contents while running the on-chip application and hence allowing more data to be captured on chip. Nonetheless, due to the growing complexity of SoCs and the increasing number of embedded cores [109], the capacity and bandwidth of a single trace buffer used in the centralized trace approach limit the observability when signals from different cores need to be concurrently acquired. To address this problem, distributed trace buffers can be used to improve the real-time observability of the multi-core architecture. In distributed tracing approach, multiple trace buffers

are allocated to multiple cores, where the data can be acquired simultaneously from different cores during the debug process [66, 71]. In order to efficiently utilize the available on-chip trace buffers, they can be dynamically allocated based on the trigger conditions that may occur consecutively over a short interval from different cores [66]. For example, in Figure 2.10, three trace buffers can be shared in such a manner, data can be captured simultaneously from three different sources, e.g., three cores or two cores and the interconnect bus.

In summary, the event detection capability described previously and the embedded trace buffer are the two main essential features in embedded logic analysis. The event detection mechanism helps the debug engineer to specify the trigger condition which starts and/or stops the capturing process of the debug data into trace buffer. The capacity of the embedded trace buffer limits the amount of data that can be captured during a debug session and hence can lengthen the debug process. In order to enhance the event detection capability and extract more data than the one that is captured on-chip, a number of debug techniques have been proposed to address these issues.

## 2.4 Recent Advancements in DFD Techniques

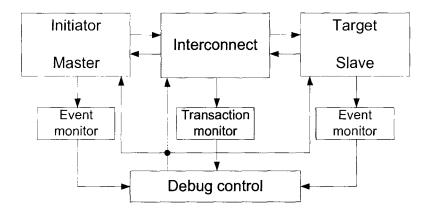

As stressed earlier the event detection mechanism used in the DFD infrastructure of both scan-based debug methodology and embedded logic analysis, and the capacity of on-chip trace buffer employed in the embedded logic analysis are two essential features in identifying design bugs during post-silicon validation. In this section, we describe the debug techniques that have been recently developed to address these features and thus improve the observability during post-silicon validation. First, we describe the assertion-based debug technique which has been recently used as a detection mechanism for identifying the violation of design properties, and thus it facilitates the localization of the root cause of a faulty execution behavior in the circuit under debug. Second, we present a new detection mechanism based on transaction-level debug techniques for debugging designs that contain complex on-chip communication infrastructures. Third, we introduce the emerging techniques to address the limited capacity of the on-chip trace buffers used in embedded logic analysis.

#### 2.4.1 Assertion-based Debug

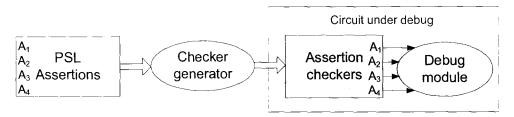

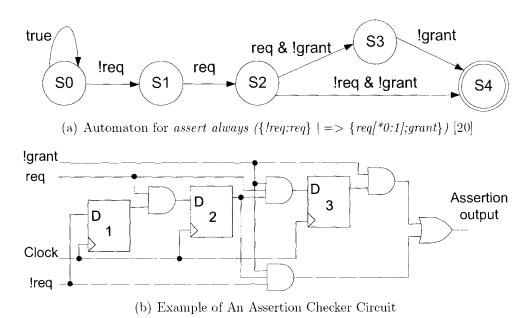

Assertion-based verification (ABV) is widely used to shorten the pre-silicon verification process in the design flow [37]. An assertion is a statement that describes a design's intended behavior (also referred to as a property), which must be satisfied in an error-free design. For example, an assertion may state that a FIFO buffer overflow should never occur. i.e., If the data is written into a full FIFO buffer, the assertion will be fired to indicate the occurrence of a faulty behavior which caused the FIFO overflow. Assertions describe the intended circuit functionality using hardware verification language such as System Verilog [54] or Property Specification Language (PSL) [4, 55]. The following example illustrates how an assertion is written in PSL to express a certain property of a bus arbiter:

assert always  $(\{!req;req\} \mid => \{req[*0:1];grant\})$

In this example, the bus arbiter assertion states that the bus should give a bus grant within two clock cycles when the request signal goes from low to high and the request signal remains high until the grant is received. The  $| = \rangle$  operator is a temporal implication (the preconditions and the post-conditions represent its left and right arguments respectively), the [\*low:high] operator specifies a range of repetition, and the semicolon ";" represents temporal concatenation. Upon the occurrence of the preconditions ({!req;req}), if any of post-conditions ({req[\*0:1]:grant}) is not satisfied, the assertion will be asserted to indicate an error. The distinguished benefit of ABV methodology lies in improving the observability within the design by revealing any unexpected behavior caused by a bug that leads to an assertion violation (or failure). Thus, an assertion failure is used as a beginning step for the debugging process of identifying design errors and hence accelerates the error localization.

Assertions have been used extensively in formal verification and simulation techniques during pre-silicon verification [51, 70]. In formal verification, assertions are used to indicate if the design properties are proven correct. Nonetheless, the growing complexity of SoC designs makes proving the correctness of properties computationally impractical. On the other hand, assertions are used in simulation in such a manner that the actual circuit responses obtained during simulation can be checked

Figure 2.11: Basic Principle of Assertion-based Debug

dynamically by the simulator against the specified properties. When any of the specified assertion rules is violated, a report containing information such as when and where the violation occurs is generated so that the debug engineer can study and fix the corresponding error. It is essential to note that the existence of no assertion failure is not an indication that the design is error-free. This indicates only that the design properties specified by the assertions are satisfied.