# NOISE CHARACTERIZATION AND MODELING OF MOSFETS FOR RF IC APPLICATIONS

By

CHIH-HUNG CHEN, B.A.Sc., M.A.Sc.

#### A Thesis

Submitted to the School of Graduate Studies

in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

McMaster University

<sup>©</sup> Copyright by Chih-Hung Chen, September 2002

# NOISE CHARACTERIZATION AND MODELING OF MOSFETS FOR RF IC APPLICATIONS

BY

CHIH-HUNG CHEN B.A.Sc., M.A.Sc.

DOCTOR OF PHILOSOPHY (2002) (Electrical Engineering)

McMaster University Hamilton, Ontario

TITLE: Noise Characterization and Modeling of MOSFETs for RF IC Applications

AUTHOR: Chih-Hung (James) Chen, B.A.Sc. (Elec. Eng.)

(National Central University)

M.A.Sc. (Elec. Eng.)

(Simon Fraser University)

SUPERVISOR: M. Jamal Deen

Professor, Electrical and Computer Engineering

Department

B.Sc. (University of

Guyana)

M.S. (Case Western Reserve University)

Ph.D. (Case Western Reserve University)

NUMBER OF PAGES: xviii, 200

#### **ABSTRACT**

This thesis develops a systematic and self-consistent framework for the RF noise characterization, modeling and simulation of deep sub-micron MOSFETs. The techniques and procedures developed in this thesis are general and can be applied to the high-frequency noise characterization of any active device. In general, there are five topics presented in this research work. First, a systematic calculation method that can directly calculate the noise parameters - minimum noise figure  $NF_{min}$ , equivalent noise resistance  $R_{n}$ , optimized source resistance  $R_{opt}$  and reactance  $X_{opt}$  - of an active device using matrix computation is presented. This method is general and can calculate the noise parameters of any noisy two-port network including correlated noise sources.

Second, a new de-embedding procedure based on a cascade configuration to remove the parasitic effects of the probe pads and the metal connections from the measured noise and s-parameters is developed. Two "THRU" dummy structures are proposed in the new de-embedding procedure and no equivalent circuit models for the probe pads and the interconnections are required. From theory, it has no frequency limitation (or it is valid to the frequency at which the discontinuity effect has to be taken into account) and works for any geometry of interconnection designed without introducing more dummy structures.

Third, two extraction methods to obtain the spectral densities of the channel noise, induced gate noise and their noise correlation from the intrinsic noise parameters as a function of frequency and bias condition are presented. The extracted noise spectral

densities of desired noise sources will serve as a direct target for the verification of any proposed noise model developed.

Fourth, new physics-based channel noise models to predict the channel noise, induced gate noise and their noise correlation are developed and verified with the extracted noise sources. The impact of the channel-length modulation (CLM) effect, the hot electron effect, and the velocity saturation effect on the desired noise sources in the deep sub-micron MOSFETs are discussed in detail.

Lastly, the design strategies of a low noise amplifier based on the developed noise models and extracted noise information are presented as a guide line to choose the device size and bias condition of the transistors. The impact of the model accuracy on the simulated noise performance of a two-stage low noise amplifier is also presented.

#### **ACKNOWLEDGMENTS**

It is my pleasure to acknowledge the thoughtful guidance provided by Dr. M J. Deen, my senior supervisor, during the course of this thesis, and for affording me the opportunity for academic advancement. Without his careful supervision, encouragement, assistance and feedback, this thesis would not be completed. I also thank the following members of Professor Deen's Microelectronics Research Laboratory - Dr. Nikhil R. Das, Dr. Mehdi Kazemeini, Dr. Guennadi Kouzaev, Dr. Ognian Marinov, Dr. Yegao Xiao, Dr. Jiansheng Xu, Sasan Naseh, Rizwan Murji, Yasser El-Batawy, Zhenwen Wang, Jessica Lam, Kamruzzaman Mollah and Kalyan Bhattacharyya - for their support, comments and assistance during the course of this research.

I wish to thank Dr. Peter Smith of Electrical & Computer Engineering, Dr. Alex Berezin and Dr. Daniel Cassidy of Engineering Physics, Dr. Shiping Zhu of Materials Science & Engineering for acting as members of my thesis examining committee, Dr. Ed Younglai of Pathology & Molecular Medicine to chair my thesis defence, Dr. Yuhua Cheng of Skyworks Solutions, Inc., Newport Beach, CA, Dr. J. Zheng, of Conexant Systems Inc., Newport Beach, CA, and Dr. Michael Matloubian of Mindspeed Technologies, Newport Beach, CA for their assistance in the device fabrication and RF noise measurements. I would like to thank Dr. Fujiang Lin and some members of the RF circuit design team of Microtune, San Diego, CA for their comments and suggestions in the design of low noise amplifiers, and the Canadian Microelectronics Corporation (CMC) for arranging the

fabrication of the test chips. I would also like to thank R. Kok and Prof. J. Tauritz of the Microwave Group, DIMES, Delft University of technology for a preliminary description of parts of the ATN noise system, Dr. Michael Schroter of University of Technology Dresden, Germany and Dr. Christian Enz of Centre Suisse d'Electronique et de Microtechnique SA, Neuchatel, Switzerland for their personal discussions about the research work.

I am also grateful to Micronet, a Federal Center of Excellence in Microelectronics, Mitel, Nortel, the Natural Sciences and Engineering Research Council (NSERC), Ontario Graduate Scholarship (OGS), Meena and Naresh Sinha Ontario Graduate Scholarship in Science and Technology (OGSST), and the McMaster University Graduate Fellowship program for various financial support of this research.

Last, but not least, I would like to thank my parents and my wife Sharon for their encouragement and continuing support in my academic pursuits.

## TABLE OF CONTENTS

| ABSTRACT                                              | iii   |

|-------------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                      | v     |

| TABLE OF CONTENTS                                     | vii   |

| LIST OF FIGURES                                       | x     |

| LIST OF TABLES                                        | xviii |

| Chapter 1 INTRODUCTION                                | 1     |

| 1.1. Noise                                            | 1     |

| 1.2. Features of Modern MOSFETs                       | 3     |

| 1.3. Noise Modeling of MOSFETs                        | 4     |

| 1.4. Objectives                                       | 5     |

| 1.5. Major Contributions                              | 6     |

| 1.6. Thesis Organization                              | 7     |

| Chapter 2 NOISE AND RF MEASUREMENTS                   | 12    |

| 2.1. What Does Noise Look Like                        | 12    |

| 2.2. Noise in Semiconductor Devices                   | 15    |

| 2.2.1. Thermal noise (Nyquist noise or Johnson noise) | 15    |

| 2.2.2. Shot noise                                     | 16    |

| 2.2.3. Generation-recombination noise                 | 16    |

| 2.2.4. Flicker noise (1/f noise)                      | 17    |

| 2.3. Scattering and Noise Parameter Measurements      | 17    |

| 2.3.1. System setup                                   | 18    |

| 2.3.2. System setting                                 | 22    |

| 2.3.3. System calibration                             | 25    |

| Chapter 3 NOISE PARAMETER CALCULATION                               | 29          |

|---------------------------------------------------------------------|-------------|

| 3.1. Introduction                                                   | 29          |

| 3.2. Theory of Noisy Two-Port Networks                              | 30          |

| 3.3. Noise Parameter Calculation                                    | 34          |

| 3.3.1. Direct matrix analysis                                       | 34          |

| 3.3.2. Circuit simulator analysis                                   | 37          |

| Chapter 4 PARAMETER DE-EMBEDDING                                    | 40          |

| 4.1. Noise Parameter De-embedding                                   | 40          |

| 4.2. De-embedding Algorithm                                         |             |

| 4.3. Measurements and Discussions                                   | 48          |

| Chapter 5 NOISE SOURCE EXTRACTION                                   | 58          |

| 5.1. Extraction of Channel Noise                                    | 58          |

| 5.1.1. Extraction algorithm                                         | 59          |

| 5.1.2. Measurements and discussions                                 | 64          |

| 5.2. Extraction of Induced Gate Noise                               | <b>71</b>   |

| 5.2.1. Extraction algorithm                                         | . 72        |

| 5.2.2. Measurements and discussions                                 | , <b>77</b> |

| Chapter 6 PHYSICS-BASED RF NOISE MODEL OF MOSFETS                   | 96          |

| 6.1. Channel Noise in MOSFETs                                       | . 96        |

| 6.1.1. Derivation of the channel noise in MOSFETs                   | . 97        |

| 6.1.2. Measurements and discussions                                 | 102         |

| 6.2. Induced Gate Noise                                             | 107         |

| 6.3. Correlation Noise                                              | 110         |

| 6.4. Review of Noise Models for Short-Channel MOSFETs               | 111         |

| 6.4.1. Modeling of channel noise                                    | 111         |

| 6.4.2 Induced gate noise and its correlation with the channel noise | 115         |

| 6.4.3. Measurements and discussions                                    |

|------------------------------------------------------------------------|

| Chapter 7 DESIGN OF LOW NOISE AMPLIFIERS123                            |

| 7.1. Design Consideration for Low Noise Circuits                       |

| 7.1.1. Selection of bias conditions                                    |

| 7.1.2. Consideration of device geometry - multi-finger gate designs127 |

| 7.2. Design of Low Noise Amplifiers130                                 |

| 7.2.1. Models of passive components                                    |

| 7.2.2. Impact of noise models on the design of an LNA                  |

| Chapter 8 CONCLUSIONS AND RECOMMENDATIONS138                           |

| 8.1. Conclusions                                                       |

| 8.2. Recommendations142                                                |

| References                                                             |

| Appendix A DC Current Model of MOSFETs                                 |

| Appendix B Discussion of Noise Calculation                             |

| Appendix C Derivation of Channel Thermal Noise                         |

| Appendix D Derivation of Induced Gate Noise                            |

| Appendix E MATLAB Program for Parameter De-embedding 170               |

| Appendix F MATLAB Program for Noise Source Extraction 185              |

| Appendix G MATLAB Program for Noise Calculation194                     |

## LIST OF FIGURES

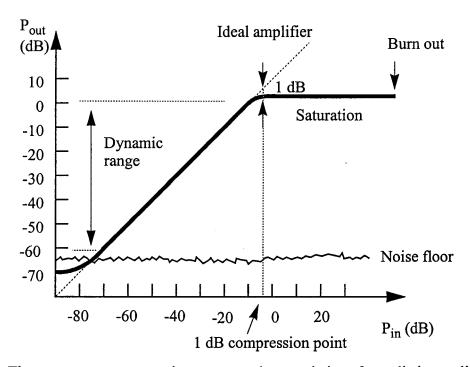

| 1.1 | The output power versus input power characteristics of a realistic amplifier 2                                                                                                                                                                                                                                                                            |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

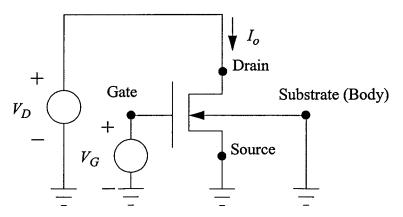

| 2.1 | An n-type MOSFET biased at a common source configuration                                                                                                                                                                                                                                                                                                  |

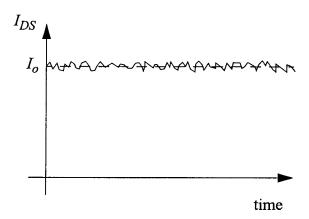

| 2.2 | Drain current as a function of time at a fixed bias voltages                                                                                                                                                                                                                                                                                              |

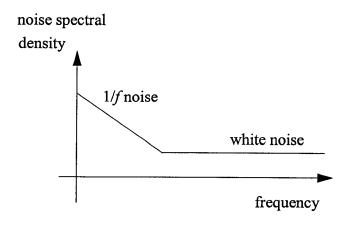

| 2.3 | Noise spectral density of the random fluctuation in drain current                                                                                                                                                                                                                                                                                         |

| 2.4 | Cross-section of an n-type MOSFET biased at a common source configuration 14                                                                                                                                                                                                                                                                              |

| 2.5 | ATN NP5B measurement system for noise and s-parameter measurements 19                                                                                                                                                                                                                                                                                     |

| 3.1 | Different representations of a noisy two-port network                                                                                                                                                                                                                                                                                                     |

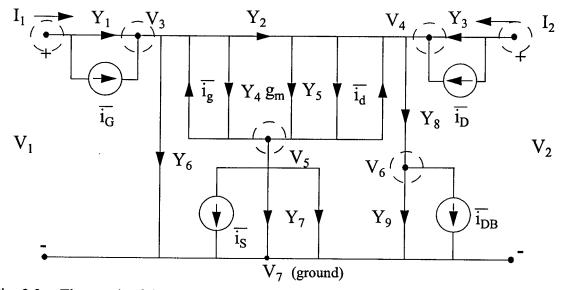

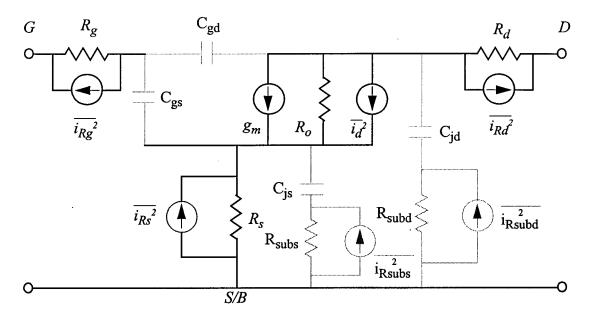

| 3.2 | RF noise model of an intrinsic MOSFET that is suitable for high-frequency circuit applications                                                                                                                                                                                                                                                            |

| 3.3 | The graph of the equivalent noise circuit model of DUT                                                                                                                                                                                                                                                                                                    |

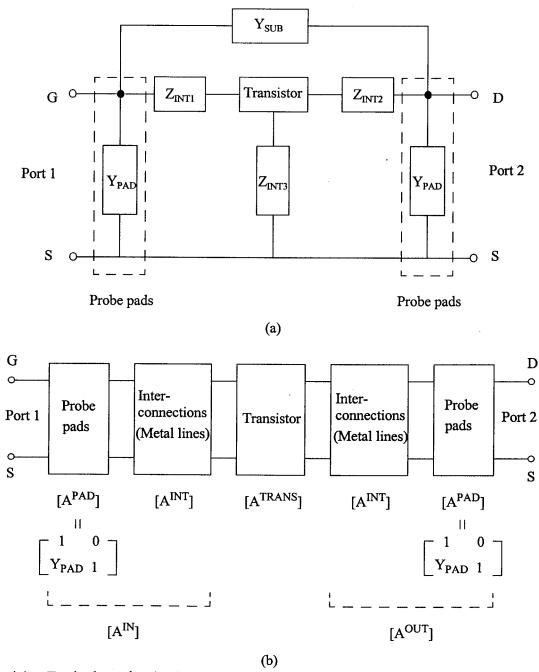

| 4.1 | Equivalent circuit diagram representing the structure of a DUT which includes probe pads, metal interconnections and a transistor modeled in (a) parallel-series and (b) cascade configurations                                                                                                                                                           |

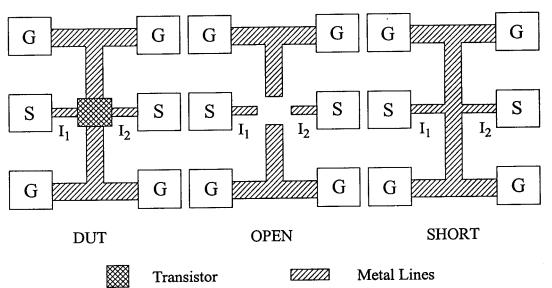

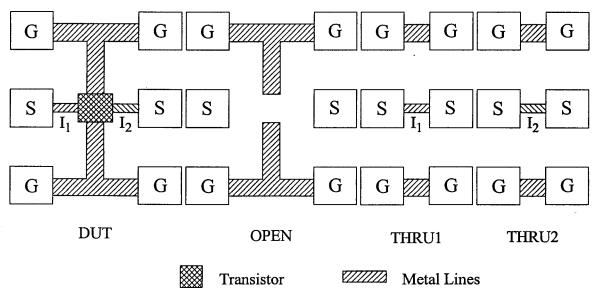

| 4.2 | A device-under-test (DUT) and its corresponding "OPEN" and "SHORT" dummy structures for the DUT modeled in the parallel-series configuration                                                                                                                                                                                                              |

| 4.3 | A device-under-test (DUT) and its corresponding "OPEN", "THRU1" and "THRU2" dummy structures for the DUT modeled in the cascade configuration                                                                                                                                                                                                             |

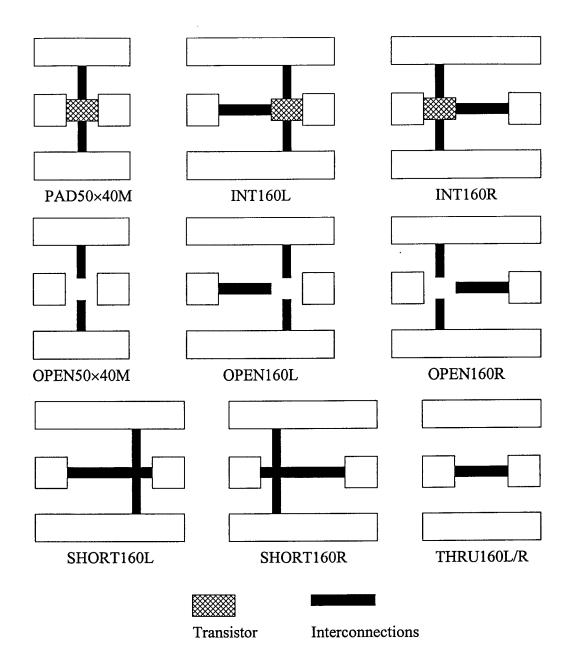

| 4.4 | Layouts of the test DUTs and their corresponding dummy structures used in the de-<br>embedding method based on the parallel-series configuration and the proposed<br>method based on the cascade configuration for the verification of the proposed de-<br>embedding method                                                                               |

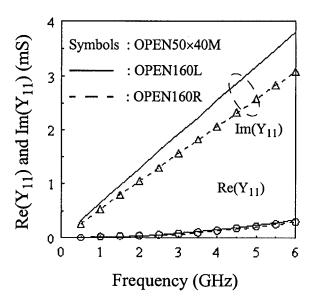

| 4.5 | Measured Y <sub>11</sub> vs. frequency characteristics of three "OPEN" dummy structures. 50                                                                                                                                                                                                                                                               |

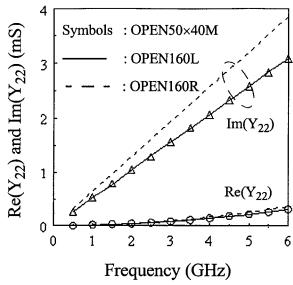

| 4.6 | Measured Y <sub>22</sub> vs. frequency characteristics of three "OPEN" dummy structures. 51                                                                                                                                                                                                                                                               |

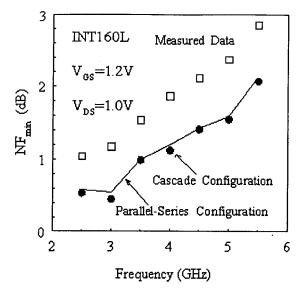

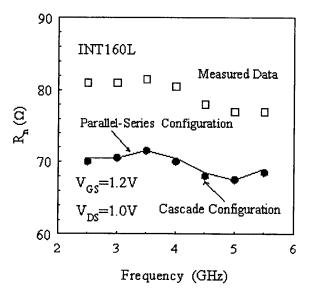

| 4.7 | Measured (squares) and de-embedded minimum noise figure ( $NF_{min}$ ) vs. frequency characteristics of an INT160L with an n-type MOSFET (L = 0.35 $\mu$ m and W = 12 × 10 $\mu$ m) biased at V <sub>DS</sub> = 1.0V and V <sub>GS</sub> = 1.2V (I <sub>DS</sub> = 7.8mA) based on the cascade (solid circles) and parallel-series configurations (lines) |

| 4.8  | Measured (squares) and de-embedded equivalent noise resistance ( $R_n$ ) versus frequency characteristics of an INT160L with an n-type MOSFET (L = 0.35 $\mu$ m and W = 12 × 10 $\mu$ m) biased at V <sub>DS</sub> = 1.0V and V <sub>GS</sub> = 1.2V (I <sub>DS</sub> = 7.8mA) based on the cascade (solid circles) and parallel-series configurations (lines) 52                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

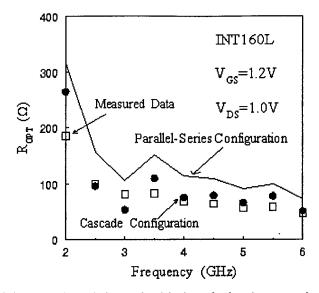

| 4.9  | Measured (squares) and de-embedded optimized source impedance ( $R_{OPT}$ ) versus frequency characteristics of an INT160L with an n-type MOSFET (L = 0.35 $\mu$ m and W = 12 × 10 $\mu$ m) biased at V <sub>DS</sub> = 1.0V and V <sub>GS</sub> = 1.2V (I <sub>DS</sub> = 7.8mA) based on the cascade (solid circles) and parallel-series configurations (lines) 54                                                                      |

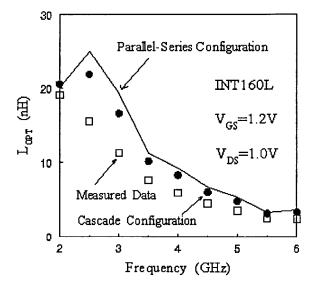

| 4.10 | Measured (squares) and de-embedded optimized source inductance ( $L_{OPT}$ ) versus frequency characteristics of an INT160L with an n-type MOSFET (L = 0.35 $\mu$ m and W = 12 × 10 $\mu$ m) biased at V <sub>DS</sub> = 1.0V and V <sub>GS</sub> = 1.2V (I <sub>DS</sub> = 7.8mA) based on the cascade (solid circles) and parallel-series configurations (lines) 54                                                                     |

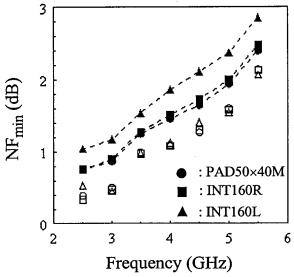

| 4.11 | Measured (dashed lines with symbols) and de-embedded (symbols) minimum noise figure ( $NF_{min}$ ) versus frequency characteristics of PAD50×40M (circles), INT160L (triangles) and INT160R (squares) with an n-type MOSFET (L = 0.35 $\mu$ m and W = 12 × 10 $\mu$ m) biased at V <sub>DS</sub> = 1.0V and V <sub>GS</sub> = 1.2V (I <sub>DS</sub> = 7.8mA) based on the cascade configuration                                           |

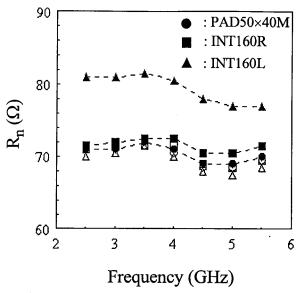

| 4.12 | Measured (dashed lines with symbols) and de-embedded (symbols) equivalent noise resistance ( $R_n$ ) vs. frequency characteristics of PAD50×40M (circles), INT160L (triangles) and INT160R (squares) with an n-type MOSFET (L = 0.35 $\mu$ m and W = 12×10 $\mu$ m) biased at V <sub>DS</sub> = 1.0V and V <sub>GS</sub> = 1.2V (I <sub>DS</sub> =7.8mA) based on the cascade configuration                                               |

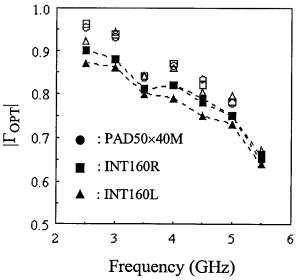

| 4.13 | Measured (dashed lines with symbols) and de-embedded (symbols) magnitude of optimized source reflection coefficient ( $ \Gamma_{OPT} $ ) vs. frequency characteristics of PAD50×40M (circles), INT160L (triangles) and INT160R (squares) based on the cascade configuration                                                                                                                                                               |

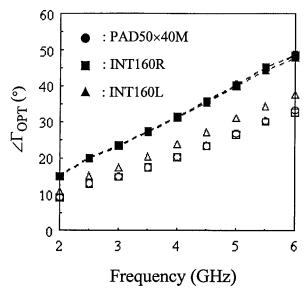

| 4.14 | Measured (dashed lines with symbols) and de-embedded (symbols) angles of optimized source reflection coefficient ( $\angle\Gamma_{OPT}$ ) versus frequency characteristics of PAD50×40M (circles), INT160L (triangles) and INT160R (squares) with an n-type MOSFET (L = 0.35 $\mu$ m and W = 12 × 10 $\mu$ m) biased at V <sub>DS</sub> = 1.0V and V <sub>GS</sub> = 1.2V (I <sub>DS</sub> = 7.8mA) based on the cascade configuration 57 |

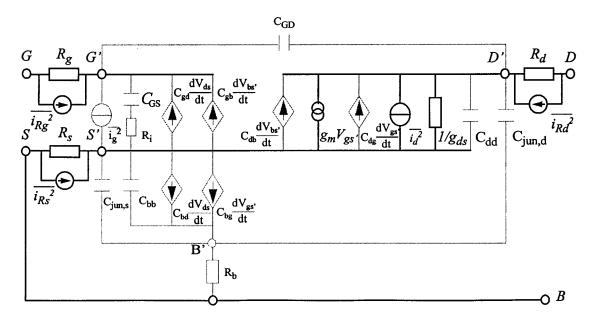

| 5.1  | BSIM3v3 RF noise model and its simplified noise equivalent circuit (parts with thicker lines) at DC or low frequencies                                                                                                                                                                                                                                                                                                                    |

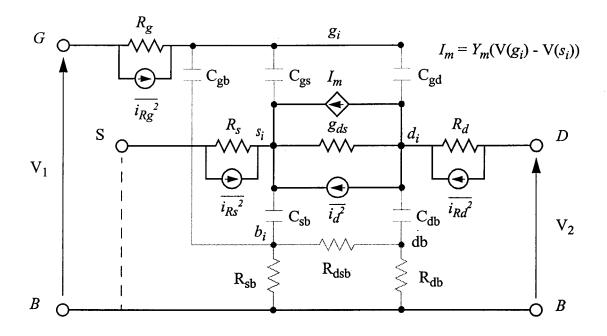

| 5.2  | Philips MOS 9 noise model and its simplified noise equivalent circuit (parts with thicker lines) at DC or low frequencies                                                                                                                                                                                                                                                                                                                 |

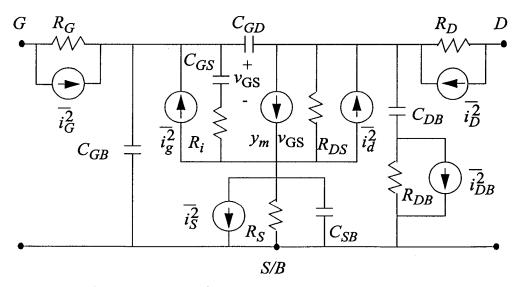

| 5.3  | EKV noise model and its simplified noise equivalent circuit (parts with thicker lines)                                                                                                                                                                                                                                                                                                                                                    |

|      | at DC or low frequencies                                                                                                                                                                                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

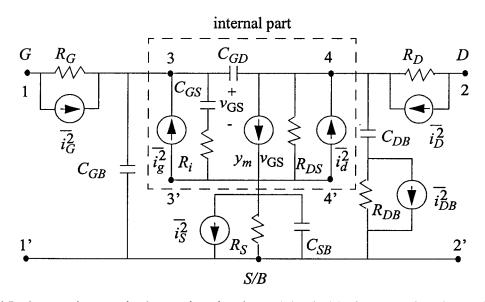

| 5.4  | A complete equivalent noise circuit model suitable for RF noise simulation with $y_m = g_m \times (1-j\omega\tau)$                                                                                                                                                                          |

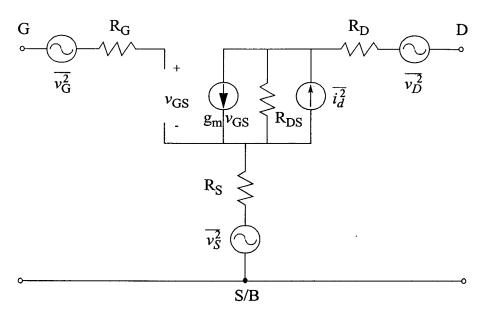

| 5.5  | Simplified equivalent noise circuit model at DC or lower frequency assuming all the capacitors are open-circuited and inductors are open-circuited 62                                                                                                                                       |

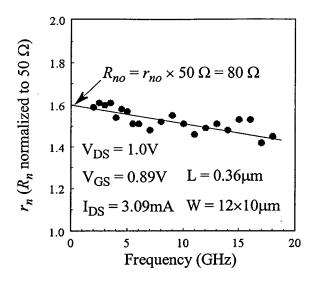

| 5.6  | Extraction of $R_{no}$ from the measured equivalent noise resistance vs. frequency characteristics                                                                                                                                                                                          |

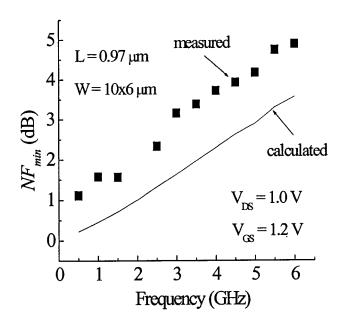

| 5.7  | Measured and simulated minimum noise figure $NF_{min}$ versus frequency characteristics of a 0.97 $\mu m$ n-type MOSFET                                                                                                                                                                     |

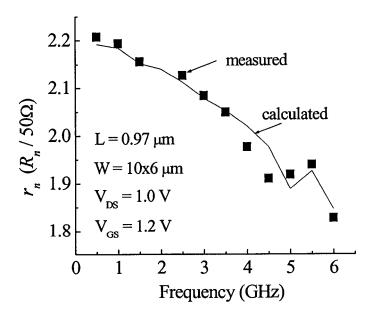

| 5.8  | Measured and simulated normalized equivalent noise resistance $r_n$ versus frequency characteristics of a 0.97 $\mu$ m n-type MOSFET                                                                                                                                                        |

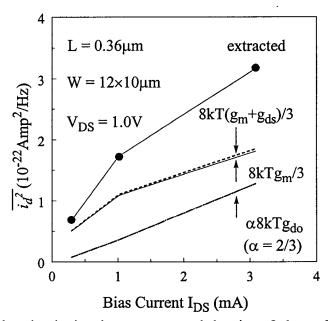

| 5.9  | Measured and calculated power spectral density of channel noise vs. bias current of a 0.36 μm n-type MOSFET                                                                                                                                                                                 |

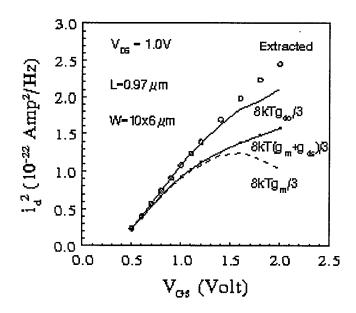

| 5.10 | Extracted and calculated for the DUT with L = 0.97 $\mu m$ and W = 10 $\times$ 6 $\mu m$ biased at $V_{DS}$ = 1.0 $V_{CS}$                                                                                                                                                                  |

| 5.11 | Extracted and calculated for the DUT with L = 0.18 $\mu m$ and W = 10×6 $\mu m$ biased at $V_{DS}$ = 1.0 V                                                                                                                                                                                  |

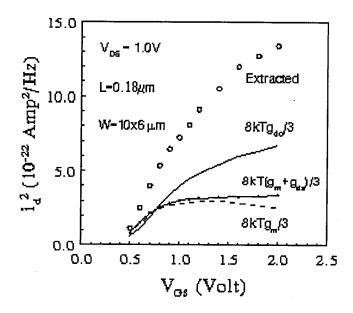

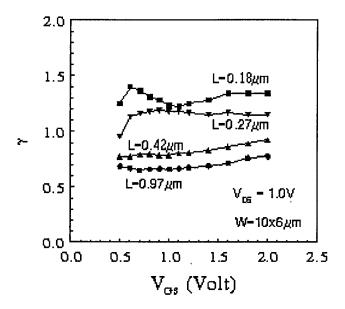

| 5.12 | Extracted $\gamma$ $(\overline{i_d^2}/\Delta f = \gamma 4kTg_{do})$ as a function of $V_{GS}$                                                                                                                                                                                               |

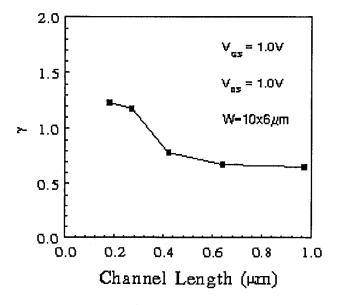

| 5.13 | Extracted $\gamma$ $(\overline{i_d^2}/\Delta f = \gamma 4kTg_{do})$ as a function of different channel lengths 70                                                                                                                                                                           |

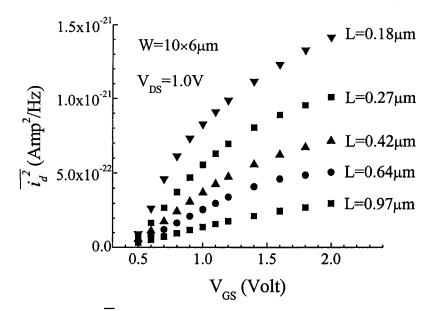

| 5.14 | Extracted channel noise as a function of $V_{GS}$ for different channel length 71                                                                                                                                                                                                           |

|      | A complete equivalent noise circuit model suitable for RF noise simulation with $y_{\rm m} = g_m \times (1-j\omega\tau)$                                                                                                                                                                    |

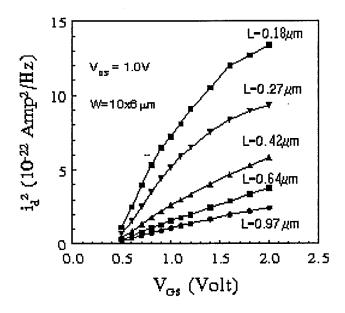

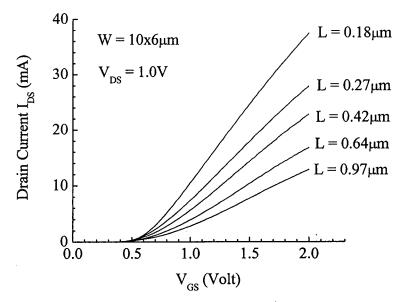

| 5.16 | Drain current ( $I_{DS}$ ) versus gate voltage $V_{GS}$ characteristics for the n-type MOSFETs with channel width W = $10 \times 6$ $\mu m$ and lengths L = $0.97$ $\mu m$ , $0.64$ $\mu m$ , $0.42$ $\mu m$ , $0.27$ $\mu m$ and $0.18$ $\mu m$ , respectively, biased at $V_{DS} = 1.0$ V |

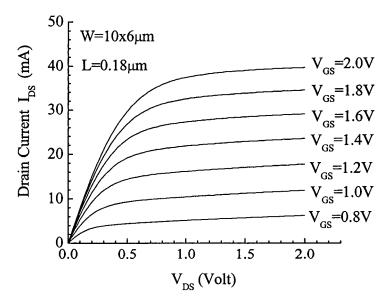

| 5.17 | Drain current ( $I_{DS}$ ) versus drain voltage $V_{DS}$ characteristics for the n-type MOSFETs with channel width $W=10\times 6~\mu m$ and lengths $L=0.18~\mu m$ biased at gate voltage $V_{GS}=0.8~V,1.0~V,1.2~V,1.4~V,1.6~V,1.8~V$ and $2.0~V,respectively.\ldots78$                    |

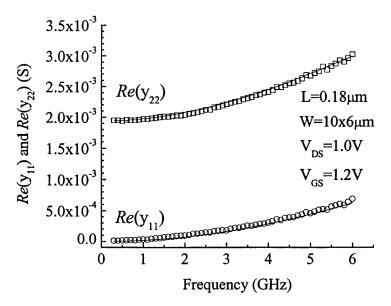

| 5.18 | Measured (symbols) and simulated (lines) real parts of $y_{11}$ and $y_{22}$ versus frequency characteristics for the n-type MOSFET with the channel width $W=10\times 6~\mu m$ and length $L=0.18~\mu m$ biased at $V_{DS}=1.0~V$ and $V_{GS}=1.2~V$                                       |

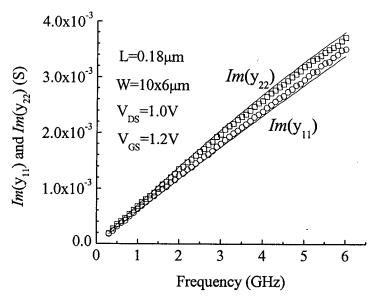

| 5.19 | Measured (symbols) and simulated (lines) imaginary parts of $y_{11}$ and $y_{22}$ versus frequency characteristics for the n-type MOSFET with the channel width $W = 10 \times 6$ $\mu$ m and length $L = 0.18$ $\mu$ m biased at $V_{DS} = 1.0$ V and $V_{GS} = 1.2$ V 80                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

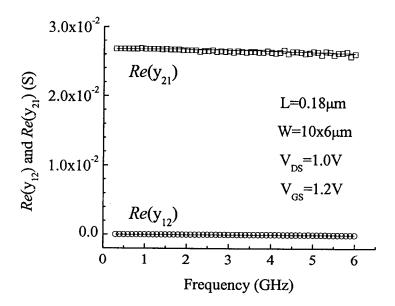

| 5.20 | Measured (symbols) and simulated (lines) real parts of $y_{12}$ and $y_{21}$ versus frequency characteristics for the n-type MOSFET with the channel width $W=10\times 6~\mu m$ and length $L=0.18~\mu m$ biased at $V_{DS}=1.0~V$ and $V_{GS}=1.2~V$ 80                                                                                                        |

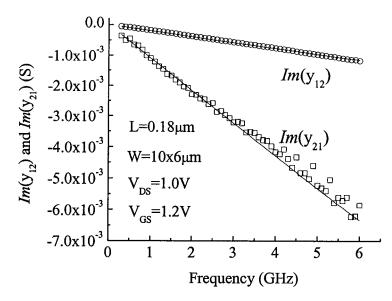

| 5.21 | Measured (symbols) and simulated (lines) imaginary parts of $y_{12}$ and $y_{21}$ versus frequency characteristics for the n-type MOSFET with the channel width $W=10\times 6$ $\mu m$ and length $L=0.18$ $\mu m$ biased at $V_{DS}=1.0$ V and $V_{GS}=1.2$ V 81                                                                                               |

| 5.22 | Transconductance $(g_m)$ versus $V_{GS}$ characteristics obtained from the measured $Re(y_{21})$ at low frequencies for the n-type MOSFETs with $W=10\times 6~\mu m$ and lengths $L=0.97~\mu m$ , 0.64 $\mu m$ , 0.42 $\mu m$ , 0.27 $\mu m$ and 0.18 $\mu m$ , respectively, biased at $V_{DS}=1.0~V$                                                          |

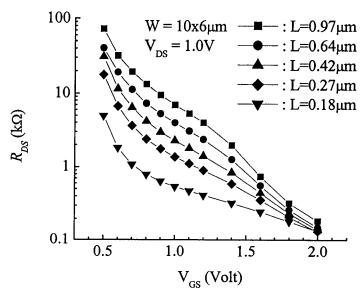

| 5.23 | Output resistance ( $R_{DS}$ ) versus $V_{GS}$ characteristics obtained from the measured $Re(y_{22})$ at low frequencies for the n-type MOSFETs with $W=10\times 6~\mu m$ and lengths $L=0.97~\mu m$ , $0.64~\mu m$ , $0.42~\mu m$ , $0.27~\mu m$ and $0.18~\mu m$ , respectively, biased at $V_{DS}=1.0~V$                                                    |

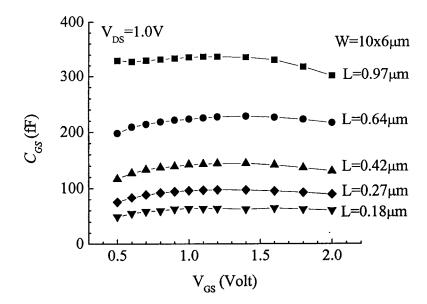

| 5.24 | Gate-to-source capacitances ( $C_{GS}$ ) versus $V_{GS}$ characteristics extracted from the $Im(y_{11})$ at low frequencies for the n-type MOSFETs with $W=10\times 6~\mu m$ and lengths $L=0.97~\mu m$ , $0.64~\mu m$ , $0.42~\mu m$ , $0.27~\mu m$ and $0.18~\mu m$ , respectively, biased at $V_{DS}=1.0~V$                                                  |

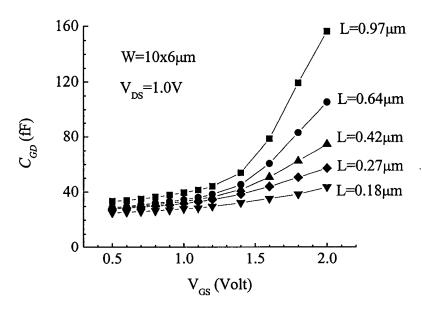

| 5.25 | Gate-to-drain capacitances ( $C_{GD}$ ) versus VGS characteristics extracted from the $Im(y_{12})$ at low frequencies for the n-type MOSFETs with W = $10 \times 6$ $\mu$ m and lengths L = $0.97$ $\mu$ m, $0.64$ $\mu$ m, $0.42$ $\mu$ m, $0.27$ $\mu$ m and $0.18$ $\mu$ m, respectively, biased at $V_{DS}$ = $1.0$ V                                       |

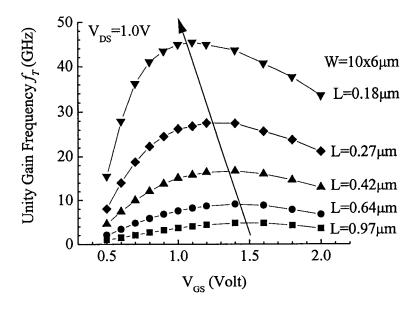

| 5.26 | Unity gain frequency ( $f_T$ ) versus $V_{GS}$ characteristics obtained from the measured intrinsic $ h_{2I} $ at 0 dB for the n-type MOSFETs with channel width W = $10 \times 6 \mu m$ and lengths L = $0.97 \mu m$ , $0.64 \mu m$ , $0.42 \mu m$ , $0.27 \mu m$ and $0.18 \mu m$ , respectively, biased at $V_{DS} = 1.0 \text{ V}$ .                        |

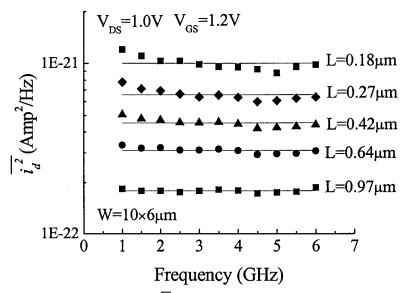

| 5.27 | Extracted channel noise $(\overline{i_d^2})$ versus frequency characteristics for the n-type MOSFETs with channel width W = $10 \times 6$ µm and lengths L = $0.97$ µm, $0.64$ µm, $0.42$ µm, $0.27$ µm and $0.18$ µm, respectively, biased at $V_{DS} = 1.0$ V and $V_{GS} = 1.2$ V. The solid lines are the extracted channel noise based on the method in 85 |

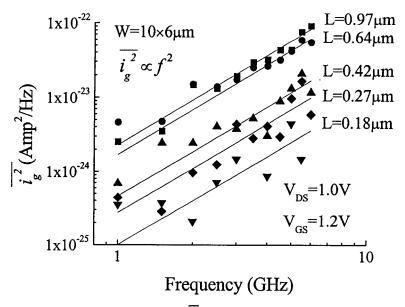

| 5.28 | Extracted induced gate noise $(\overline{i_g^2})$ versus frequency characteristics for the n-type MOSFETs with W = $10 \times 6$ µm and lengths L = $0.97$ µm, $0.64$ µm, $0.42$ µm, $0.27$ µm and $0.18$ µm, respectively, biased at $V_{DS} = 1.0$ V and $V_{GS} = 1.2$ V                                                                                     |

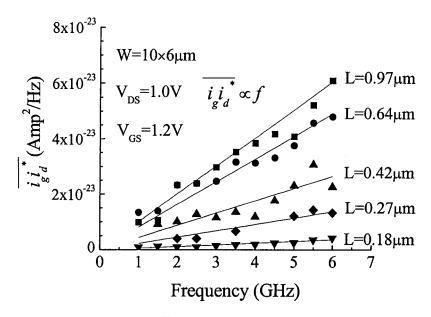

| 5.29 | The correlation between $i_g^2$ and $i_d^2$ ( $i_g i_d^*$ ) versus frequency characteristics for the n-type MOSFETs with W = $10 \times 6$ µm and lengths L = 0.97 µm, 0.64 µm, 0.42 µm, 0.27 µm and 0.18 µm, respectively, biased at $V_{DS} = 1.0$ V and $V_{GS} = 1.2$ V 87                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

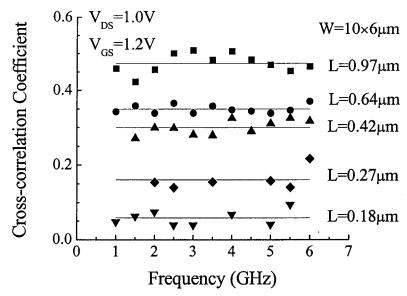

| 5.30 | The cross-correlation coefficient $c$ versus frequency characteristics for the n-type MOSFETs with W = $10 \times 6~\mu m$ and lengths L = $0.97~\mu m$ , $0.64~\mu m$ , $0.42~\mu m$ , $0.27~\mu m$ and $0.18~\mu m$ , respectively, biased at $V_{DS}$ = $1.0~V$ and $V_{GS}$ = $1.2~V$ 88                      |

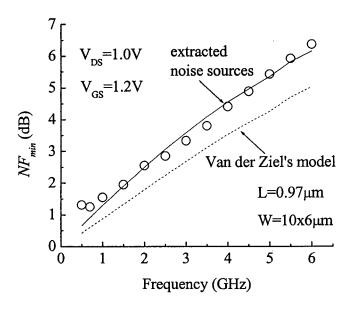

| 5.31 | Measured (symbols) and simulated (lines) minimum noise figure ( $NF_{min}$ ) versus frequency characteristics for the n-type MOSFET with the channel width W = $10 \times 6$ $\mu$ m and length L = $0.97$ $\mu$ m biased at $V_{DS}$ = $1.0$ V and $V_{GS}$ = $1.2$ V 89                                         |

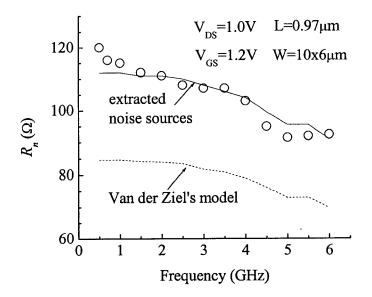

| 5.32 | Measured (symbols) and simulated (lines) equivalent noise resistance ( $R_n$ ) versus frequency characteristics for the n-type MOSFET with the channel width W = $10 \times 6$ $\mu$ m and length L = 0.97 $\mu$ m biased at $V_{DS} = 1.0$ V and $V_{GS} = 1.2$ V 90                                             |

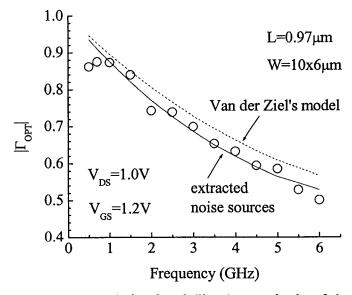

| 5.33 | Measured (symbols) and simulated (lines) magnitude of the optimized source reflection coefficient ( $ \Gamma_{OPT} $ ) versus frequency characteristics for the n-type MOSFET with the channel width W = $10 \times 6$ µm and length L = $0.97$ µm biased at $V_{DS}$ = $1.0$ V and $V_{GS}$ = $1.2$ V            |

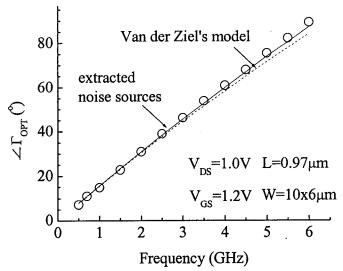

| 5.34 | Measured (symbols) and simulated (lines) angle of the optimized source reflection coefficient ( $\angle\Gamma_{OPT}$ ) versus frequency characteristics for the n-type MOSFET with the channel width W = 10 × 6 $\mu$ m and length L = 0.97 $\mu$ m biased at V <sub>DS</sub> = 1.0 V and V <sub>GS</sub> = 1.2 V |

| 5.35 | Channel noise $(\overline{i_d^2})$ versus bias characteristics for the n-type MOSFETs with channel width W = $10 \times 6$ µm and lengths L = $0.97$ µm, $0.64$ µm, $0.42$ µm, $0.27$ µm and $0.18$ µm, respectively, biased at $V_{DS} = 1.0$ V92                                                                |

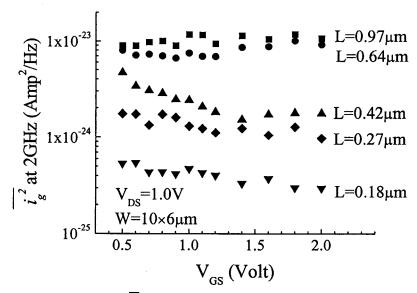

| 5.36 | Induced gate noise $(\overline{i_g^2})$ versus bias characteristics for the n-type MOSFETs with channel width W = $10 \times 6$ µm and lengths L = 0.97 µm, 0.64 µm, 0.42 µm, 0.27 µm and 0.18 µm, respectively, biased at $V_{DS} = 1.0 \text{ V}$                                                               |

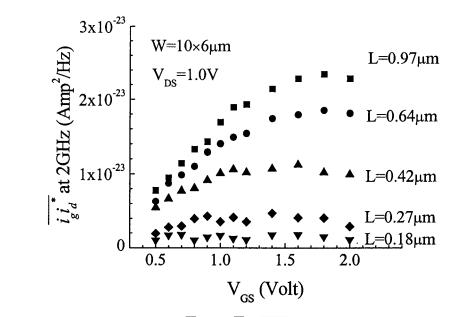

| 5.37 | The correlation between $i_g^2$ and $i_d^2$ ( $i_g i_d^*$ ) versus bias characteristics for the n-type MOSFETs with channel width W = $10 \times 6$ µm and lengths L = $0.97$ µm, $0.64$ µm, $0.42$ µm, $0.27$ µm and $0.18$ µm, respectively, biased at $V_{DS} = 1.0$ V 93                                      |

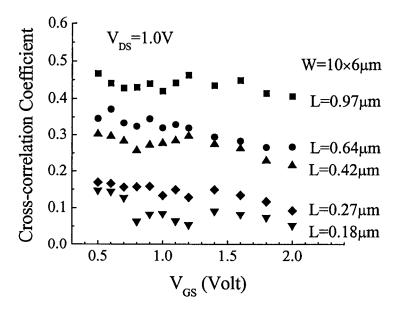

| 5.38 | The cross-correlation coefficient $c$ versus bias characteristics for the n-type MOSFETs with channel width W = $10 \times 6$ µm and lengths L = $0.97$ µm, $0.64$ µm, $0.42$ µm, $0.27$ µm and $0.18$ µm, respectively, biased at $V_{DS} = 1.0$ V 93                                                            |

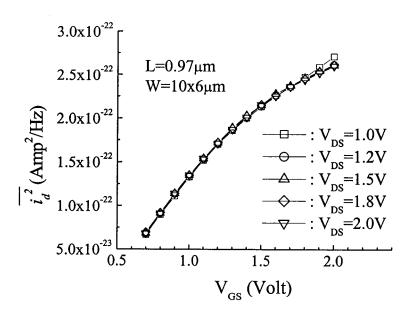

| 5.39 | Channel noise $(\overline{i_d^2})$ versus $V_{GS}$ characteristics for the n-type MOSFET with channel width $W = 10 \times 6 \mu m$ and length $L = 0.97 \mu m$ biased at $V_{DS} = 1.0 \text{ V}$ , 1.2 V, 1.5 V, 1.8 V and 2.0 V, respectively                                                                  |

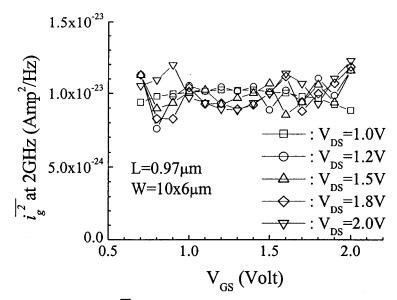

| 5.40 | Induced gate noise $(\overline{i_g^2})$ versus $V_{GS}$ characteristics for the n-type MOSFET with channel width $W = 10 \times 6 \mu m$ and length $L = 0.97 \mu m$ biased at $V_{DS} = 1.0 \text{ V}$ , 1.2 V, 1.5 V, 1.8 V and 2.0 V, respectively                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

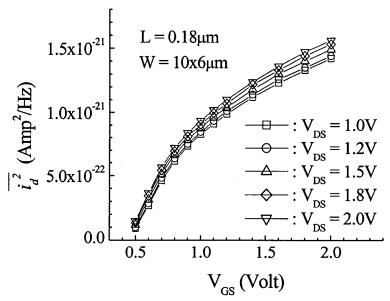

| 5.41 | Channel noise $(\overline{i_d^2})$ versus $V_{GS}$ characteristics for the n-type MOSFET with channel width $W = 10 \times 6 \mu m$ and length $L = 0.18 \mu m$ biased at $V_{DS} = 1.0 \text{ V}$ , $1.2 \text{ V}$ , $1.5 \text{ V}$ , $1.8 \text{ V}$ and $2.0 \text{ V}$ , respectively                                                                                                                         |

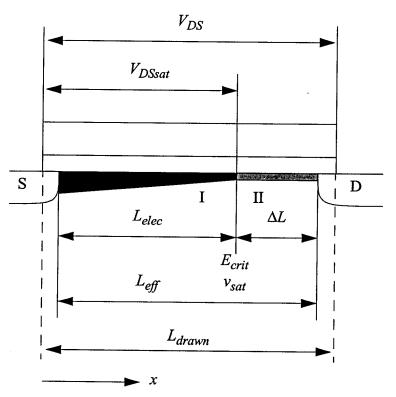

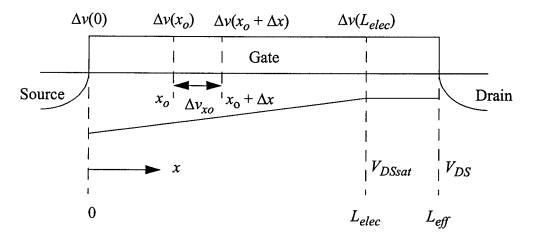

| 6.1  | Cross section of a MOSFET channel divided into a gradual channel region (I) and a velocity saturation region (II)                                                                                                                                                                                                                                                                                                   |

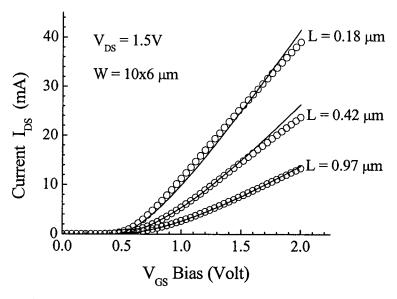

| 6.2  | Measured (symbols) and simulated (lines) DC current $I_{DS}$ versus $V_{GS}$ characteristics of n-type MOSFETs with channel width $W=10\times 6~\mu m$ and channel lengths $L=0.97~\mu m$ , 0.42 $\mu m$ and 0.18 $\mu m$ , respectively biased at $V_{DS}=1.5~V.$ 103                                                                                                                                              |

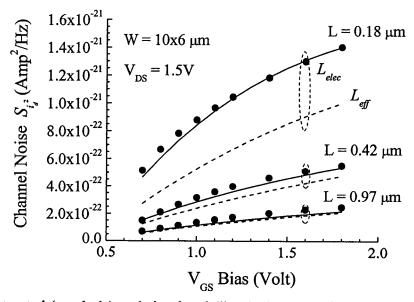

| 6.3  | Extracted (symbols) and simulated (lines) channel noise versus $V_{GS}$ characteristics of n-type MOSFETs with channel width $W=10\times 6~\mu m$ and channel lengths $L=0.97~\mu m$ , 0.42 $\mu m$ and 0.18 $\mu m$ , respectively biased at $V_{DS}=1.5~V$ with $\delta=0.\ldots.103$                                                                                                                             |

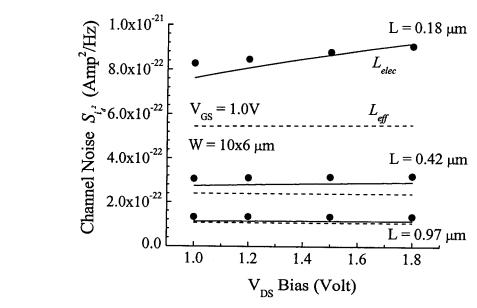

| 6.4  | Extracted (symbols) and simulated (lines) channel noise versus $V_{DS}$ characteristics of n-type MOSFETs with channel width W = 10 $\times$ 6 $\mu m$ and channel lengths $L=0.97$ $\mu m$ , 0.42 $\mu m$ and 0.18 $\mu m$ , respectively biased at $V_{GS}$ = 1.0 V with $\delta$ = 0 105                                                                                                                         |

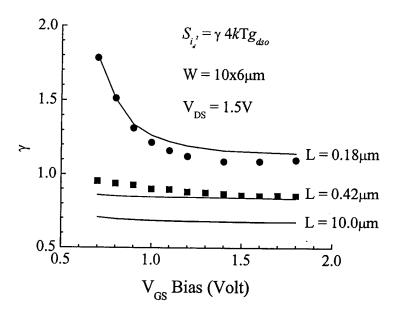

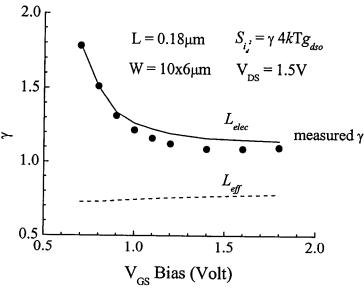

| 6.5  | Extracted (symbols) and simulated (lines) g versus $V_{GS}$ characteristics of n-type MOSFETs with channel width W = $10 \times 6~\mu m$ and channel lengths L = $10~\mu m$ , 0.42 $\mu m$ and 0.18 $\mu m$ , respectively biased at $V_{DS}$ = 1.5 V with $\delta$ = 0 106                                                                                                                                         |

| 6.6  | Extracted (symbols) and simulated (lines) $\gamma$ versus $V_{GS}$ characteristics of n-type MOSFETs with channel length L = 0.18 $\mu$ m and width W = 10 × 6 $\mu$ m and biased at $V_{DS}$ = 1.5 V with $\delta$ = 0                                                                                                                                                                                             |

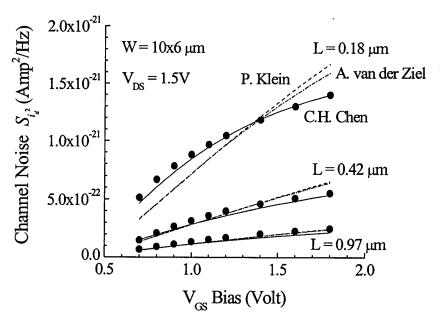

| 6.7  | Extracted (symbols) and simulated (lines) spectral density of the channel noise versus $V_{GS}$ characteristics for the n-type MOSFETs with channel width W = 10 $\times$ 6 $\mu m$ and channel lengths L = 0.97 $\mu m$ , 0.42 $\mu m$ and 0.18 $\mu m$ , respectively biased at $V_{DS}$ = 1.5V including the hot electron effects                                                                                |

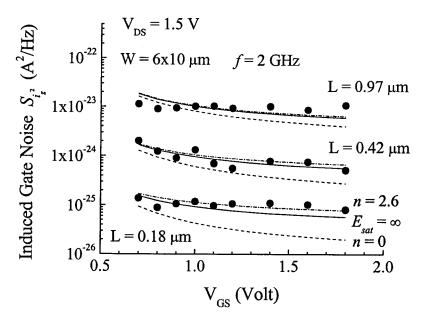

| 6.8  | Extracted (symbols) and simulated (lines) spectral density of the induced gate noise versus $V_{GS}$ characteristics for the n-type MOSFETs with channel width $W=10\times6$ $\mu m$ and channel lengths $L=0.97$ $\mu m$ , 0.42 $\mu m$ and 0.18 $\mu m$ , respectively biased at $V_{DS}=1.5$ V based on the proposed noise model in [35] with/without the velocity saturation effect and the hot electron effect |

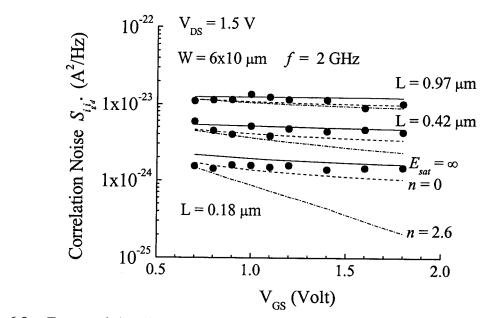

| 6.9  | Extracted (symbols) and simulated (lines) spectral density of the correlation noise versus $V_{GS}$ characteristics for the n-type MOSFETs with channel width $W=10\times6$ $\mu m$ and channel lengths $L=0.97$ $\mu m$ , 0.42 $\mu m$ and 0.18 $\mu m$ , respectively biased at                                                                                                                                   |

|      | V <sub>DS</sub> = 1.5 V based on the proposed noise model in [35] with/without the velocity saturation effect and the hot electron effect                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

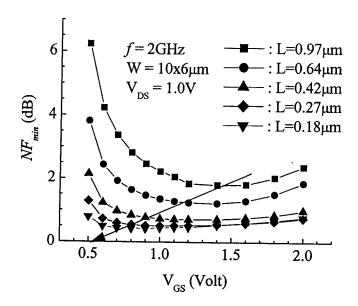

| 7.1  | Simulated intrinsic minimum noise figure ( $NF_{min}$ ) versus $V_{GS}$ characteristics for the n-type MOSFETs with channel width $W=10\times 6~\mu m$ and lengths $L=0.97~\mu m$ , 0.64 $\mu m$ , 0.42 $\mu m$ , 0.27 $\mu m$ and 0.18 $\mu m$ , respectively, biased at $V_{DS}=1.0~V$ using new noise models presented in Chapter 6 |

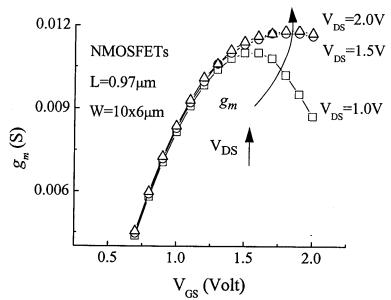

| 7.2  | Measured intrinsic transconductance $(g_m)$ versus $V_{GS}$ characteristics extracted from the measured $Re(y_{21})$ at the low frequency region for the n-type MOSFETs with channel width $W = 10 \times 6 \mu m$ and lengths $L = 0.97 \mu m$ biased at $V_{DS} = 1.0 \text{ V}$ 1.5 V and 2.0 V, respectively                       |

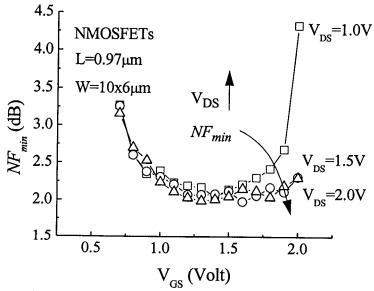

| 7.3  | Measured intrinsic minimum noise figure ( $NF_{min}$ ) versus $V_{GS}$ characteristics for the n-type MOSFETs with channel width $W=10\times 6~\mu m$ and lengths $L=0.97~\mu m$ biased at $V_{DS}=1.0~V~1.5~V$ and $2.0~V$ , respectively                                                                                             |

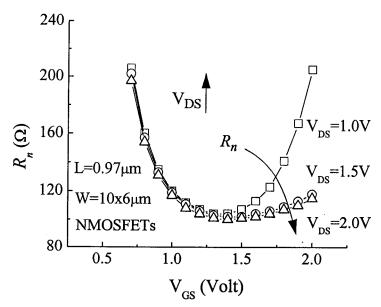

| 7.4  | Measured intrinsic equivalent noise resistance $(R_n)$ versus $V_{GS}$ characteristics for the n-type MOSFETs with channel width $W = 10 \times 6 \mu m$ and lengths $L = 0.97 \mu m$ biased at $V_{DS} = 1.0 \text{ V}$ 1.5 V and 2.0 V, respectively                                                                                 |

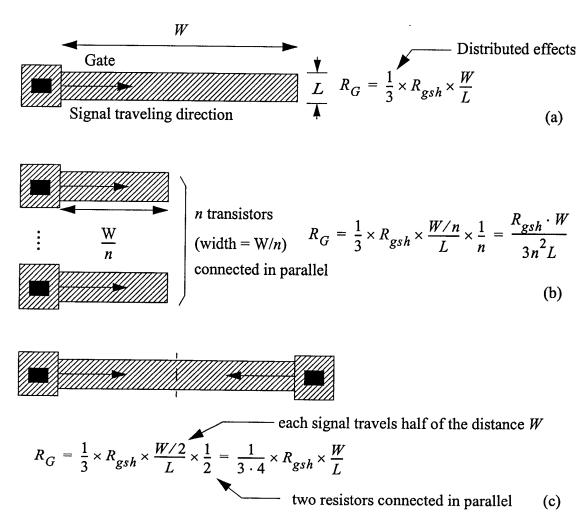

| 7.5  | Effective gate resistance $(R_G)$ of (a) a single finger design with the input signal from one side of the transistor, (b) a multi-finger design with the input signal from one side of the transistor and (c) a single finger design with the input signal from both sides of the transistor                                          |

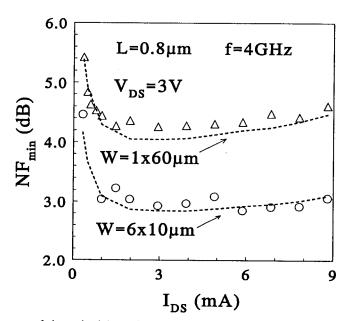

| 7.6  | The measured (symbols) and calculated (dashed lines) $NF_{min}$ of a single 60 $\mu$ m transistor (triangle) and a multi-finger gate design (circle) with six 10 $\mu$ m wide transistors connected in parallel                                                                                                                        |

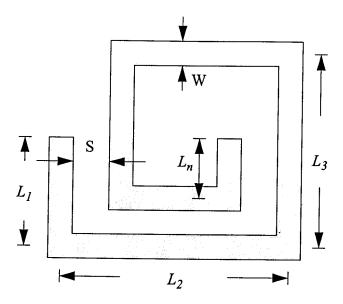

| 7.7  | Example of microstrip rectangular inductor (1 1/2-turn)                                                                                                                                                                                                                                                                                |

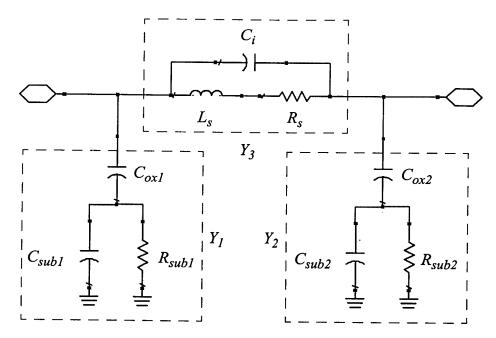

| 7.8  | Equivalent circuit of a spiral inductor on silicon substrate                                                                                                                                                                                                                                                                           |

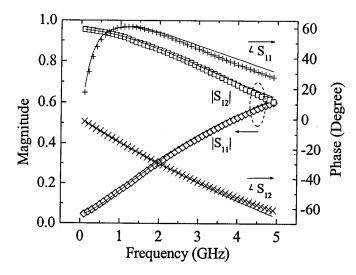

| 7.9  | Measured (symbols) and simulated (lines) S <sub>11</sub> and S <sub>12</sub> of inductor 1 (Ind1) based on the equivalent circuit model shown in fig. 7.8 and the element values shown in Table 7.2                                                                                                                                    |

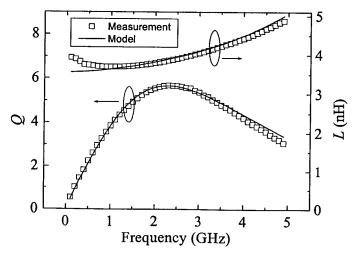

| 7.10 | Measured (symbols) and simulated (lines) quality factor $Q$ and the inductance $L$ of 2 2.5-turn inductor (Ind1) based on the equivalent circuit model shown in fig. 7.8 and the element values shown in Table 7.2                                                                                                                     |

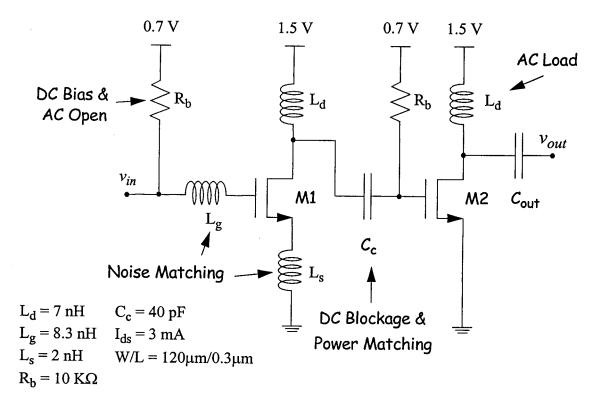

| 7.11 | Two-stage low noise amplifier to verify the impact of noise models on the simulated noise figure                                                                                                                                                                                                                                       |

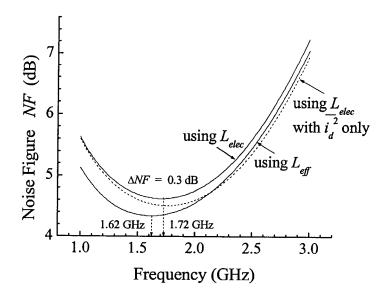

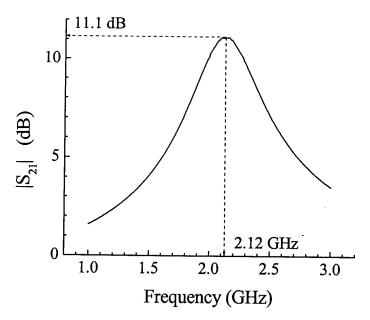

| 7.12 | Simulated noise figure (NF) versus frequency characterization for the circuit shown in fig. 7.11 based on the noise model using $L_{elec}$ , $L_{eff}$ (solid lines) and $L_{elec}$ without the induced gate noise and the correlations (dashed line) |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.13 | Simulated magnitude of the power gain $S_{21}$ for the design of the low noise amplifier shown in fig. 7.11                                                                                                                                           |

| 7.14 | Simulated phase of the power gain $S_{21}$ for the design of the low noise amplifier shown in fig. 7.11                                                                                                                                               |

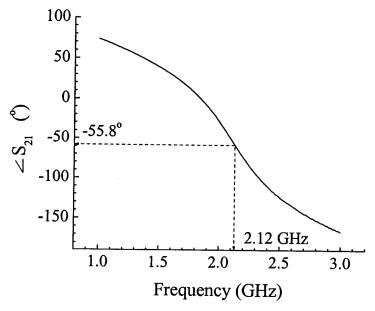

| B.1  | Equivalent circuit model of two resistors with noise voltage source connected in series                                                                                                                                                               |

| D.1  | Cross-section of a MOSFET channel                                                                                                                                                                                                                     |

## LIST OF TABLES

| 6.1 | Summary of the channel noise equations used in the model verification 118 |

|-----|---------------------------------------------------------------------------|

| 7.1 | Geometrical parameters of 2.5 turn spiral inductor                        |

| 7.2 | Extracted element values of the 2.5 turn square spiral inductor           |

## Chapter 1

## **INTRODUCTION**

#### 1.1 NOISE

Noise is some unwanted fluctuation that, when added to a signal, reduces its information content. In a communication system, noise can be classified into two broad categories depending on its source -- internal noise and external noise. Noise generated by components within a communication system, such as resistors, electron tubes, and solid-state active devices is referred to as *internal noise* (or *electronic noise*). The second category, *external noise*, results from sources outside a communication system, including atmospheric, man-made and extraterrestrial sources. The "static" heard in a radio, the "snowy screen" of a television, and the fluctuation of a DC signal around its expected value are all examples of electronic noises, and this is the kind of noise of interest to us in this research.

Electronic noise in a communication system defines the lowest limit of a signal that can be detected. Fig. 1.1 shows the output power versus input power characteristics of a realistic amplifier with a gain of 10 dB. It is shown that if the power of any input signal is smaller than the noise floor of the amplifier, the signal would be "drowned out" by the background noise generated within the amplifier. Therefore, electronic noise directly

affects the accuracy of measurements and the minimum power of a signal that can be used in a circuit to transmit information.

Fig. 1.1: The output power versus input power characteristics of a realistic amplifier.

Since noise is random in nature, it is represented as a time varying random variable X(t) in noise theory. The mean value,  $\overline{X}$ , and the variance,  $\overline{\Delta X^2}$ , of X(t) are two important parameters for characterizing the random variable X(t). Another important characteristic of a random signal is its power spectral density function (PSDF) that describes how a signal distributes its power at different frequencies. By definition, PSDF represents the time averaged noise power over a one Hertz bandwidth at any given frequency f. White noise is a particular kind of noise which has a PSDF that is constant for

all frequencies. Thermal noise generated from a resistor and the shot noise generated in a bipolar junction transistor are examples of white noise.

Noise always exists in electronic signals due to the current or voltage fluctuation in a circuit. A DC current I(t) or voltage V(t) is actually the sum of an ideal DC component and a fluctuating AC component. The PSDFs of a DC current I(t) and voltage V(t) are represented by  $S_I(f)$  and  $S_V(f)$ , and abbreviated as their "noise power spectra". These noise spectra describe how their noise powers distribute at different frequencies. The noise voltage generator  $v_n(f) = \sqrt{S_V(f)}$  and noise current generator  $i_n(f) = \sqrt{S_I(f)}$  are defined such that the total noise power of a circuit can be evaluated by applying AC circuit theory to these quantities.

#### 1.2 FEATURES OF MODERN MOSFETS

Metal-Oxide-Semiconductor (MOS) technology is the dominant technology for very large-scale integrated (VLSI) circuits. The main driving force of submicrometer MOS technology is digital VLSI. However, as the speed and circuit complexity increase, it is often desirable to incorporate high-frequency analog circuits on the same chip. Radio frequency (RF) designs are increasingly taking the advantages of the advanced MOS technology that makes possible the integration of a complete communication system. As an example, global positioning system (GSP) receivers employ extensive digital signal processing to perform acquisition, tracking, and decoding functions. The use of the MOS technology for implementation of the front end electronics in a GPS system is therefore attractive because of the promise of integrating the whole system onto a single chip. In

addition to the high levels of integration of the CMOS process, many high-speed or RF integrated-circuits are likely to be implemented in CMOS technology since very high unity-gain frequencies ( $f_T$ ) of deep sub-micron MOSFETs of more than 100 GHz have already been achieved [1],[2]. Therefore, high-frequency characterization and modeling of Metal-Oxide-Semiconductor Field Effect Transistors (MOSFET) are becoming more important with the growth in high-frequency analog applications.

#### 1.3 NOISE MODELING OF MOSFETS

As mentioned above, MOSFET are increasing used to implement analog functions at high frequencies. However, when working at high frequencies, the effect of the noise generated within the device itself will play an increasingly important role in the overall system sensitivity characteristics, dynamic range and signal-to-noise ratio [3],[4],[5]. Therefore it is crucial to understand the noise mechanisms in sub-micron MOSFETs. Due to the long turn-around time and the expensive cost of actual fabrication of an analog circuit, noise simulation of an analog circuit becomes a realistic alternative to determine whether the overall noise performance of a circuit would be good enough to allow the circuit to function properly [6],[7]. In order to perform accurate noise simulation, an appropriate physics-based noise model that can predict accurately the noise performance of transistors over a wide range of operating conditions is urgently needed.

#### 1.4 OBJECTIVES

The goal of this thesis is to develop a systematic and self-consistent framework for the RF noise characterization, modeling and simulation of MOSFETs. The techniques and procedures developed in this thesis are general and can be applied to the high-frequency noise characterization of any active device. In general, there are five objectives of this research work. First, at high frequencies, the noise parameters -- minimum noise figure  $NF_{min}$ , equivalent noise resistance  $R_n$ , optimized source resistance  $R_{opt}$  and reactance  $X_{opt}$  -- of an active device are usually measured, instead of the noise spectral densities. In addition, in order to predict the high-frequency characteristics of MOSFETs, the complexity of the AC and noise equivalent circuit model has been increased tremendously. Therefore, how to calculate the four noise parameters based on any sophisticated noise equivalent circuit model is the first objective of this research work.

Second, in order to conduct the RF noise measurements, probe pads and metal interconnections are required to access the devices. These probe pads and interconnections will not affect the device characterization at DC or low frequencies. However, at high frequencies, the coupling of the probe pads and interconnections through the lossy substrate to ground will contribute some parasitics which will affect the measured scattering and noise parameters. Therefore, the second object of this research is to find out how to deembed the parasitic effects from the probe pads and interconnections and to obtain the intrinsic noise and s-parameters of the transistors.

Third, in order to develop physics-based noise models for wireless applications, the spectral densities of the desired high-frequency noise sources in MOSFETs -- channel

noise, induced gate noise and their correlation as a function of frequency and bias -- have to be obtained from the intrinsic noise parameters. Therefore, how to obtain the noise spectral densities of desired noise sources as a direct target for the verification of any proposed noise model developed latter on is the third objective of this research.

Fourth, the physics-based noise model to be built in a compact device model for circuit simulation is the key objective of this research work. Therefore, after obtaining the spectral densities of the desired noise sources, the fourth objective is to develop physics-based noise models for RF wireless communication applications.

Lastly, when designing the low noise circuits, how to choose the device size, how to bias the devices and how to draw the layout of the transistors are the frequently asked questions by circuit designers. Therefore, the fifth object of this research work is to find out the design strategies of low noise circuits based on the developed noise models and extracted noise information.

#### 1.5 MAJOR CONTRIBUTIONS

There are five main contributions in this thesis and they are listed as follows.

- 1. A systematic procedure to calculate the noise parameters of MOSFETs based on any sophisticated noise equivalent circuit model [8],[9],[13].

- 2. A general procedure and design of new dummy structures for the noise and sparameter de-embedding to obtain the intrinsic noise and high-frequency performance of transistors [14],[15].

3. Two noise source extraction methods to obtain the spectral density of the channel noise, induced gate noise and their correlation directly from the intrinsic RF noise parameters [5], [16], [17], [18], [19], [20].

7

- 4. New analytical noise models to calculate the channel noise, induced gate noise and their correlation for RF wireless applications [21],[22].

- 5. Design strategies of a low noise amplifier (LNA) for RF wireless communication applications [23].

#### 1.6 THESIS ORGANIZATION

The thesis consists of eight chapters. Chapter 1 describes the motivation and the objectives of the research work, followed by a description on the contribution of the work and the organization. Chapter 2 will present what the noise in MOSFETs looks like, different kinds of noise sources in semiconductor devices and the high-frequency noise and s-parameter measurement system.

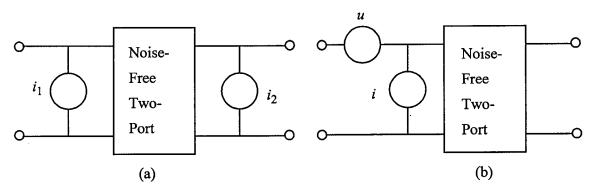

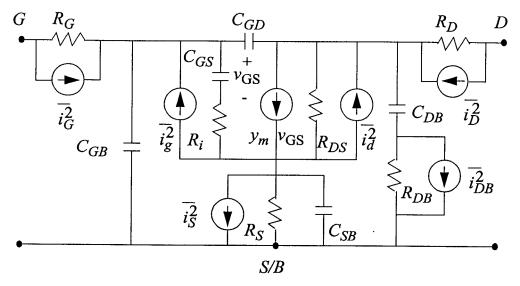

In Chapter 3, a general noise theory for a noisy two-port network and the definition of the four noise parameters of a noisy two-port network -- minimum noise figure  $(NF_{min})$ , equivalent noise resistance  $(R_n)$ , optimized source resistance  $(R_{opt})$  and optimized source reactance  $(X_{opt})$  -- are presented in detail. A technique for direct calculation of these four noise parameters based on matrix computations for any equivalent noise circuit model is also presented. In addition, circuit simulators are often used by circuit designers and they might want to verify the noise model based on the compact model in the circuit simulator.

Therefore, another calculation method using circuit simulators to obtain the noise parameters based on compact models is also presented in Chapter 3.

Parasitics of the probe pads and interconnections in the test chip become an important issue for both RF and noise characterization [24], [25], [26]. With the continuous downscaling of the device dimensions, the impact of the surrounding parasitics on a transistor's characteristics has gained importance in the RF domain. In [8] and [27], a noise de-embedding method based on a parallel-series configuration was presented. This configuration assumes that the capacitive effect of metal interconnections between the probe pads and the transistor can be lumped into the probe pads and the inductive and resistive effects are modeled in series with the transistor at the frequencies of interest. However, this might not be true for designs with long (or wide) interconnections, or at operating frequencies of several tens of GHz. Therefore, the DUT has to be modeled as probe pads, interconnections and the transistor connected in a cascade configuration. The method presented in [28] is based on a cascade configuration, but it requires specific equivalent circuit models for both probe pads and the metal interconnections. This means that the de-embedding results rely on the accuracy of the equivalent circuit models and the element values used in the calculation. In addition, this procedure is not easy to automate since the parasitic elements in the equivalent circuit model are both technology and design dependent. In Chapter 4, a new de-embedding method based on the cascade configuration is presented in detail.

Verification of the noise model has always been challenging for RF noise modeling of MOSFETs. Presently, models of the channel noise that are physics-based are

confirmed by the measured minimum noise figure ( $NF_{min}$ ) of devices through the help of a device simulator or the device's small-signal model [29],[30]. However, the accuracy of the small-signal model, the values of model parameters used in simulation and the noise model itself affect the simulated noise parameters. These factors make the confirmation of noise models more difficult, even when accurate noise parameters were measured. In addition, when transistors operate in the GHz range, the random potential fluctuations in the channel resulting in the channel noise will be coupled to the gate terminal through the gate oxide capacitance and will cause the induced gate noise, which is usually correlated with the channel noise.

Because of the difficulties in the extraction of the induced gate noise and its correlation with the channel noise, several noise models [31],[32] and simulation results [33] have been presented, but they could not be verified directly with the noise parameters obtained from RF noise measurements for deep sub-micron MOSFETs. Therefore, to have the proper topology of an equivalent noise circuit suitable for RF modeling, to obtain the element values of the equivalent noise circuit directly from the measured s-parameters (or y-parameters), and to get the channel noise, induced gate noise and their correlation directly from RF noise measurements are crucial for the high-frequency noise modeling of deep sub-micron MOSFETs.

Chapter 5 presents a systematic procedure to extract the spectral densities of induced gate noise  $(S_{i_g^2})$ , channel noise  $(S_{i_d^2})$  and their cross-correlation  $(S_{i_g^i d}^*)$  directly from the s-parameter and RF noise parameter measurements. With the help of the direct calculation technique described in Chapter 3, the extracted noise currents are fed back to

the equivalent noise model to calculate the noise parameters --  $NF_{min}$ ,  $R_n$  and optimized source reflection coefficient ( $\Gamma_{opt}$ ) -- and to compare the calculations to the measured data for the verification of the extracted noise sources. After that, the extracted noise currents of the deep sub-micron MOSFETs fabricated in a 0.18  $\mu$ m CMOS process as a function of frequency, bias condition and channel length are presented and discussed.

After obtaining the spectral densities of the channel noise, induced gate noise and their correlation, the next step is to verify the noise models in the literature and develop new noise models if the traditional noise models fail to predict the noise performance of deep sub-micron MOSFETs. To date, it is observed that the channel noise generated from the short-channel devices is higher than that expected from the conventional channel noise theory for long-channel MOSFETs [34],[35]. Several approaches in the literature have been proposed to explain the discrepancy by introducing extra channel noise from the velocity saturation through either the hot-electron effect [34] or the diffusion noise [36],[37]. The noise from the saturation region proposed in these models is either not physical or not proven by the measured noise data of deep sub-micron MOSFETs. In Chapter 6, a new analytical noise model using the channel length modulation (CLM) effect to calculate the channel noise of deep sub-micron MOSFETs is presented and verified by the measured data obtained using the direct extraction method described in Chapter 5. In addition, the hot electron effect and the velocity saturation effect are also discussed. The noise models published in the literature for the channel noise, induced gate noise and their correlation are also reviewed and verified either by theories or experiments.

Chapter 1: Introduction

Based on the extracted AC and noise parameters, Chapter 7 presents some considerations for the design of low-noise circuits and shows the impact of the noise models on the circuit simulation. Chapter 8 will conclude the thesis and have some discussion on the future research work for the noise modeling of MOSFETs.

## Chapter 2

## NOISE AND RF MEASUREMENTS

#### 2.1 WHAT DOES NOISE LOOK LIKE

If we take an n-type MOSFET biased in a common source configuration as shown in fig. 2.1 with a positive drain bias  $V_D$  and a gate bias  $V_G$  greater than the threshold voltage  $V_{TH}$ , it is expected that there is a constant current  $I_o$  as a function of time flowing through the transistor, which is the dashed line in fig. 2.2. However, if we monitor the DC current with an oscilloscope, the actual drain current fluctuates randomly as a function of time with an average value  $I_o$ , which is the solid line in fig. 2.2. The undesired random fluctuation in the drain current will set the lowest detectable ACAC signal, and is therefore called "noise".

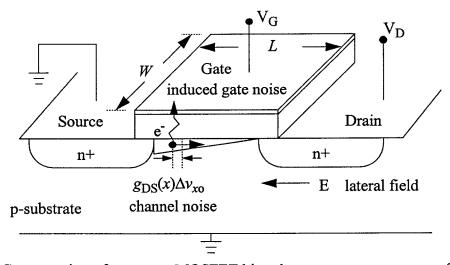

Fig. 2.1: An n-type MOSFET biased at a common source configuration.

Fig. 2.2: Drain current as a function of time at a fixed bias voltages.

Since the current fluctuation is random and unpredictable in the time domain, it is often represented by its spectral density in frequency domain, as shown in fig. 2.3. In the low frequency region, the noise spectral density is inversely proportional to the frequency. However, at high frequencies, the noise spectral is almost frequency independent, and it is also called "white noise".

Fig. 2.3: Noise spectral density of the random fluctuation in drain current.

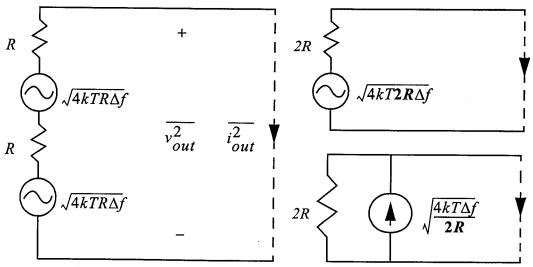

After knowing what the noise looks like, the next question is what is the physical mechanism that generates the noise. Fig. 2.4 shows a cross-section of an n-type MOSFET biased in a common source configuration. Consider an electron traveling along the channel, then because of the collision of the electron with the lattice due to the thermal vibration of the lattices, there is a small voltage fluctuation  $\Delta v_{xo}$  generated at  $x_0$  in the channel. Because of the non-zero output conductance  $g_{DS}(x_0)$  at  $x_0$ , the small voltage fluctuation will be detected at the drain terminal through the current fluctuation, and this is called "channel noise". Channel noise occurs at all frequencies, and it consists of noise sources generated from different noise mechanisms which will be discussed in next section. This thesis will only focus on the channel noise at high frequencies.

Fig. 2.4: Cross-section of an n-type MOSFET biased at a common source configuration.

At high frequencies, the gate oxide has a finite impedance and the current fluctuation caused by the voltage fluctuation  $\Delta v_{xo}$  will also be detected at the gate terminal -- this is termed the "induced gate noise". Because the physical origins of the channel noise

and the induced gate noise come from the same source  $\Delta v_{xo}$ , therefore they are usually correlated. A detailed discussion and extraction techniques for the channel noise, induced gate noise and their correlation will be discussed in Chapter 5. The physics-based noise models for these noise sources will be discussed in Chapter 6. A brief discussion of different noise sources in semiconductor devices will be presented in the next section.

#### 2.2 NOISE IN SEMICONDUCTOR DEVICES

The noise discussed in this thesis is the electronic noise which is caused by the small voltage (or current) fluctuations generated within the device. The most important noise sources in a device are thermal noise, shot noise, generation-recombination noise and flicker noise.

#### 2.2.1 Thermal Noise (Nyquist Noise or Johnson Noise)

Thermal noise is caused by the random changes in the motions of the carriers due to their collisions with the vibrating atoms. In general, the spectral density of the short-circuit current fluctuation  $S_{I,T}$ , in A<sup>2</sup>/Hz, can be expressed by [38]

$$S_{I,T} = 4 \cdot \left[ \frac{1}{2} h f + \frac{h f}{\exp(h f / k T) - 1} \right] / R$$

(2.1)

where h is Planck's constant, k is Boltzmann's constant, f is the frequency, T is the absolute lattice temperature, and R is the resistance of the sample. For hf/kT << 1,  $S_{I,T}$  can be reduced to the widely used expression

$$S_{I,T} = \frac{4kT}{R}. (2.2)$$

#### 2.2.2 Shot Noise

Shot noise is generated when carriers (electrons or holes) cross potential barriers independently and at random. It is present in diodes and bipolar transistors. The external DC current I, which appears to be a steady current, is in fact composed of a large number of random independent current pulses. The physical origin of the shot noise is the fluctuation of the emission rate of carriers. For operating frequency lower than the reciprocal of the transit time, the short-circuit spectral density ( $A^2/Hz$ ) of the shot noise  $S_{I,s}$  is white [38] and is expressed as

$$S_{IS} = 2qI \tag{2.3}$$

where q is the electronic charge  $(1.6 \times 10^{-19} \text{C})$  and I is the DC current through the sample.

#### 2.2.3 Generation-Recombination Noise

Generation-recombination noise (g-r noise) is caused by the fluctuation of the conductance. Because of the traps and recombination centers in semiconductors, the random trapping and detrapping of carriers results in the fluctuation in the number of free carriers N per unit time, causing the conductance of the device to fluctuate. The power spectral density of g-r noise is given by [38]

$$S_N(f) = \langle \Delta N^2 \rangle \cdot \frac{4\tau}{1 + (2\pi f \tau)^2}$$

(2.4)

where  $<\Delta N^2>$  is the variance of N, f is the frequency, and the  $\tau$  is the lifetime of the carriers.

#### 2.2.4 Flicker Noise (1/f Noise)

The origin of the flicker noise is still actively researched. Because the spectrum varies as  $1/f^n$ , with n close to unity, flicker noise is often called 1/f noise. In general, two major models have been proposed to account for the origin of flicker noise -- the carrier number fluctuation model [39] and the mobility fluctuation model [40]. In the first model, the flicker noise is attributed to the random trapping and de-trapping processes of charges, for example in the oxide traps near Si-SiO<sub>2</sub> interface in MOSFETs. The charge fluctuations result in fluctuations of the surface potential, which in turn modulate the channel mobile carrier density. It is assumed that the channel can exchange charges with the interfacial oxide traps through tunneling. The second model considers that the flicker noise results from the bulk mobility fluctuation on the basis of an empirical hypothesis. In general, its short-circuit spectral density is given by the empirical expression [40]

$$S_I(f) = \frac{\alpha}{f^n N} \tag{2.5}$$

where  $\alpha$  is the Hooge's constant with value between  $10^{-7}$  and  $10^{-3}$  depending on the device, N is the total number of charges, and n is a constant close to unity.

#### 2.3 SCATTERING AND NOISE PARAMETER MEASUREMENTS

If the dimension of the components of circuits is comparable to the wavelength of the voltage and current waves (i.e. distributed circuits), we can not neglect the effect of the phase changes in the waves traveling along the circuit elements. In addition, a practical problem exists when trying to measure voltages and currents at microwave frequencies because direct measurements usually involve the magnitude (inferred from power) and the phase of a wave traveling in a given direction. A representation that is in accord with direct measurements, and with the ideas of incident, reflected, and transmitted waves, is given by the scattering matrix. Therefore, s-parameters are most commonly used in characterizing the high frequency performance of devices and circuits. In addition, to characterize the AC and the noise characteristics of DUT at the same time, the s-parameter and noise parameters of transistors have to be measured successively. Therefore, the measurement system should combine the s-parameter measurement system and noise measurement system together and have the bias-T with variable input impedance for measuring the optimized source impedance. The NP5B Noise Parameter System and S-Parameter Measurement software manufactured by ATN microwave is employed for this purpose. This system is a solid-state tuner based, turn-key solution for complete small-signal device characterization. In conjunction with a network analyzer and noise receiver, it provides noise parameter and sparameter measurements, equivalent models, and can be used for detailed characterization versus bias or frequency. All details, such as system setup, system calibration, and power level setting will be described in the following sections.

# 2.3.1 System Setup

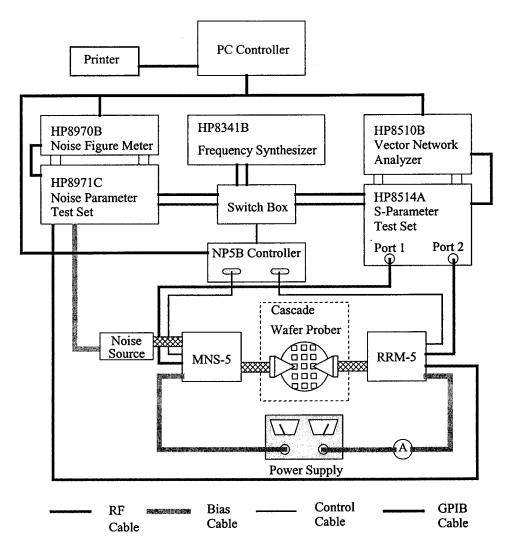

The complete S-Parameter and Noise Parameter Measurement System for high-frequency noise and s-parameter measurements is shown in fig. 2.5.

Fig. 2.5: ATN NP5B measurement system for s-parameter and noise parameter measurements.

The system basically consists of three sub-systems -- an ATN NP5B wafer prober test set, a HP8510 vector network analyzer system (VNA), a HP8970 noise measurement system, and other peripheral devices such as a printer, a computer, and a microwave probe station. The NP5B mainframe works as a switch for switching between the HP8510B for

the s-parameter measurements and the HP8970 for the noise measurements of two-port networks.

## • NP5B wafer prober test set

The ATN NP5B Wafer Prober Test Set is comprised of a main controller unit which drives the externally connected Mismatch Noise Source (MNS5) and the Remote Receiver Module (RRM5). The MNS5 contains a solid state electronic tuner (ET) with a built-in bias-T and RF switches which alternately connect the VNA and the noise source to the DUT while the output of the DUT is connected via the RRM5 unit to either port 2 of the VNA or to the HP8970B noise figure meter via the built in low noise amplifier of the RRM5. The low noise amplifier in the RRM5 can lower system noise figure and therefore reduce the measurement uncertainty. The RRM5 also contains a bias-T and the necessary switching circuitry. The switch box in fig. 2.5 is used to pass the RF signal from the HP8341B frequency synthesizer to either the s-parameter measurement system or the noise measurement system if there is only one frequency synthesizer available for different measurement modes [41].

## • S-parameter measurement system

The s-parameter measurement systems contains the HP8510B vector network analyzer (VNA) and HP8514A s-parameter test set to measure the scattering and gain parameters of linear two port networks. In the s-parameter measurement mode, the HP8510B controls the RF source (HP8341B) and two kinds of measurements are made - reflection and transmission. An incident signal generated by the RF source is applied to the

DUT and compared with the signal reflected from or transmitted through the DUT. Reflection measurements are made by comparing the reflected signal to the incident signal. This provides measurement data on reflection characteristics of the DUT such as return loss, standing wave ratio (SWR), reflection coefficient ( $S_{11}$  or  $S_{22}$ ) and impedance. Transmission measurements are made by comparing the transmitted signal to the incident signal. This results in measurement data on transmission characteristics of the network such as insertion loss, transmission coefficient ( $S_{21}$ ), electrical delay (from which electrical length can be obtained), deviation from linear phase and group delay. By applying the incident signal to the output port of DUT, the reverse characteristics, output impedance and reverse transmission coefficient ( $S_{12}$ ) can be measured.

The HP8514A s-parameter test set separates the RF signal into an incident signal sent to the DUT and a reference signal to which the transmitted or reflected signals are later compared. It also routes the transmitted and reflected signals from DUT to the receiver for later processing. Internal attenuation from 0 to 90 dB, in 10 dB increments, are available to control the incident stimulus level at the DUT input without causing a change in the reference level.

#### Noise measurement system

The noise measurement system consists of the HP8970B Noise Figure Meter and HP8971C Noise Parameter Test Set to measure the noise parameters and gain of DUT. The HP8970B can be tuned between 10 and 1,600 MHz and can also be swept over all or any part of that range. The HP8971C extends the frequency range of the noise figure meter from 1,600 MHz to 26,500 MHz.

# • Other peripheral devices

Other peripheral devices are a dual DC voltage power supply for biasing the DUT, a current meter to monitor the drain current, a microwave probing station, a switch box used for passing the RF signal from the synthesizer to either the s-parameter measurement system or the noise measurement system depending on the measurement mode, a computer for instrument control and data collection, and a printer for printing the measurement results.

### 2.3.2 System Setting

After all the instruments are properly set up, we turn on the power switch of each instrument in the following order: s-parameter measurement system or noise measurement system, and then NP5B main control unit. When turning on the power of the s-parameter measurement system, one should follow the following power-on sequence: frequency synthesizer, s-parameter test set, system peripheral devices if there is any, and network analyzer.

To achieve the maximum measurement accuracy, the power level of the RF signal generated by the HP8341B synthesizer should be as high as possible without overloading the test set. According to the HP8510 *Network Analyzer Operating and Programming Manual* (p. 55-6), the source power between 0 to 10 dBm is optimal. However, when measuring a highly non-linear device such as MOSFETs, we must ensure the power applied to the device is sufficiently low to avoid non-linear distortion and gain compression. Attenuators included in the ports 1 and 2 signal paths of the s-parameter measurement test

set provide a way of reducing the actual power supplied to the device. The attenuators can be set from 0 to 90 dB in 10 dB increments.

At low frequencies, the drain current  $I_D$  varies approximately as  $(V_{GS} - V_{TH})^2$ , where the threshold voltage,  $V_{TH}$ , is ~ 0.5V for the 0.18  $\mu$ m CMOS technology. The small-signal model of the transistor is only valid when the ACAC voltage is small compared to the DC voltages i.e.  $\Delta V/V \ll 1$ . However, if the power level is too small, the measured s-parameters will appear noisy. On the other hand, if the power level is too large, the measured s-parameters will again be reduced because of gain compression, as shown in fig. 1.1. In addition, the measured s-parameters should remain constant over a range of intermediate power levels. For greatest measurement accuracy, we set the power level to a value in the middle of dynamic range of DUT. The procedure must be repeated for both ports 1 and 2.

Since the output of the MOSFETs is not as non-linear as the input, less attenuation is required at port 2. In our measurements, the power level is set to 5 dBm (at the starting frequency of 0.5 GHz) with 30 dB attenuation at port 1 and 10 dB attenuation at port 2. Taking into account about 2 dB loss in the cables, there will be about -27 dBm at port 1 and -7 dBm at port 2.

The optimal power levels vary with frequency. At higher frequencies, more power is lost in the test set, cabling and bias-T. In addition, the input and output impedance of the DUT vary with frequency. In order to compensate for the change in the optimal source power, the HP8510B provides a Power Slope setting which allows the source power to

either increase or decrease with frequency. In our measurement, the power slope is set to 0.2 dB/GHz.